# OPERATING AND MAINTENANCE MANUAL

### OPERATING AND MAINTENANCE

#### MANUAL

STEP-2: 1977 to June 1980

STEP-3: July, 1980

Copyright 1980 by Step Engineering, Inc. 757 North Pastoria Ave., Sunnyvale, Ca. P.O. Box 91166, Telephone: (408) 733-7837 TWX: (910) 339-9506

All rights reserved. Printed in U.S.A.

Specifications subject to change without notice.

#### WARRANTEE

Your Step instrument has been thoroughly inspected and tested prior to shipment. It is guaranteed to be free from defects in material and workmanship. Before applying power to the unit, inspect the unit for any signs of shipping damage. Any such damage should be reported immediately to the freight carrier and an appropriate claim filed with the carrier.

CAUTION: This unit is designed for operation from:

115V + 10% 40-440 Hz AC power source only, U. S. Versions; or 220V  $\frac{1}{7}$  10% 40-440 Hz European versions.

Connection to any other power source may cause permanent damage.

All products manufactured by Step Engineering, Inc. are warranted to be free from defects, material and workmanship for a period of 180 days from date of shipment to the original purchaser. Under this warrantee, the obligation of Step Engineering, Inc. is limited to servicing any equipment returned to the factory for that purpose and restoring the equipment to its original specifications.

Step Engineering's liability is limited to the repair or replacement at our option of any defect of the product and shall in no event include incidental or consequential damages of any kind. If, in our opinion, the product must be returned to the factory, Step will issue a Return Material Authorization, RMA, for the repair. No return will be accepted without such an authorization.

<u>NOTE</u>: The RMA number must appear on all correspondence and paperwork. Freight must be prepaid and insured. After repairs, the instru-

i

ment will be returned to you freight prepaid and insured. If a failure is caused by misuse, operation, or environment exceeding specifications, or unauthorized modification by the customer, a cost estimate will be submitted and repairs performed and billed upon request. Out of warranty repairs will be handled in the same manner. This quarantee is void if the serial number is removed.

#### PREFACE

This manual is designed both as a guide for the first-time user and as a reference book.

Topics include:

- How to unpack and test a new instrument

- How to organize the WCS memory

- How to connect the instrument to the system being developed

- How to enter STEP-N commands and interpret CRT displays

How to trouble shoot the STEP-N instrument when it is not operating properly

A detailed discussion of any particular application or processor design technique is beyond the scope of this manual.

<u>NOTE</u>: This manual is useful with either Step-2 or its successor instrument, Step-3. Step-3 is exactly a super-set of Step-2 functionally but has added features, improved design, and some mechanical changes.

In the text, the usages "Step-N" and "Step Instrument" refer to features found in both Step-2 and Step-3.

# TABLE OF CONTENTS

| SECTION I  | CHECKOUT AND OPERATING YOUR NEW STEP INSTRUMENT      |

|------------|------------------------------------------------------|

| 1.1        | UNPACKING1-2                                         |

| 1.2        | GROUNDING1-3                                         |

| 1.3        | OPERATION AND CHECKOUT1-5                            |

| 1.4        | QUICK INTERCONNECT TO TARGET1-16                     |

| 1.5        | COMMAND SUMMARY CHART1-30                            |

| SECTION I  | I OPERATING COMMANDS                                 |

| 2.1        | COMMAND DESCRIPTION2-2                               |

| 2.2        | INSTRUMENT COMMANDS                                  |

| 2.3        | EDITOR COMMANDS                                      |

| 2.4        | MONITOR COMMANDS2-26                                 |

| 2.5        | I/O COMMANDS2-57                                     |

| SECTION II | II HARDWARE INTERCONNECT                             |

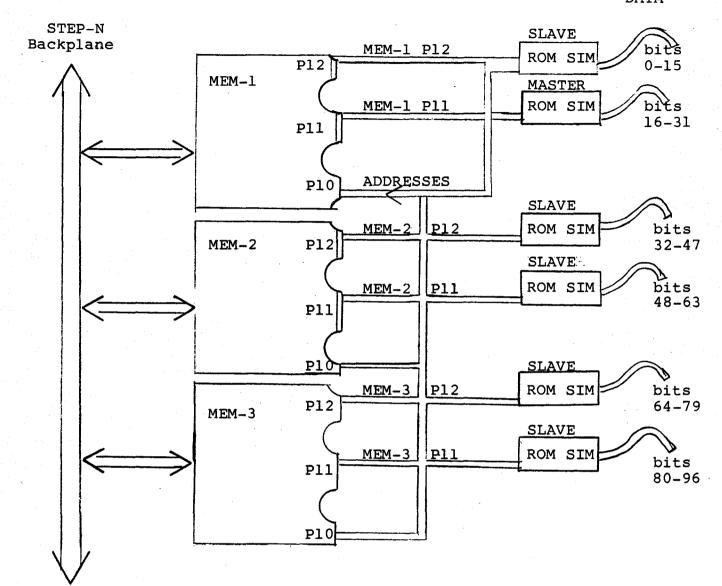

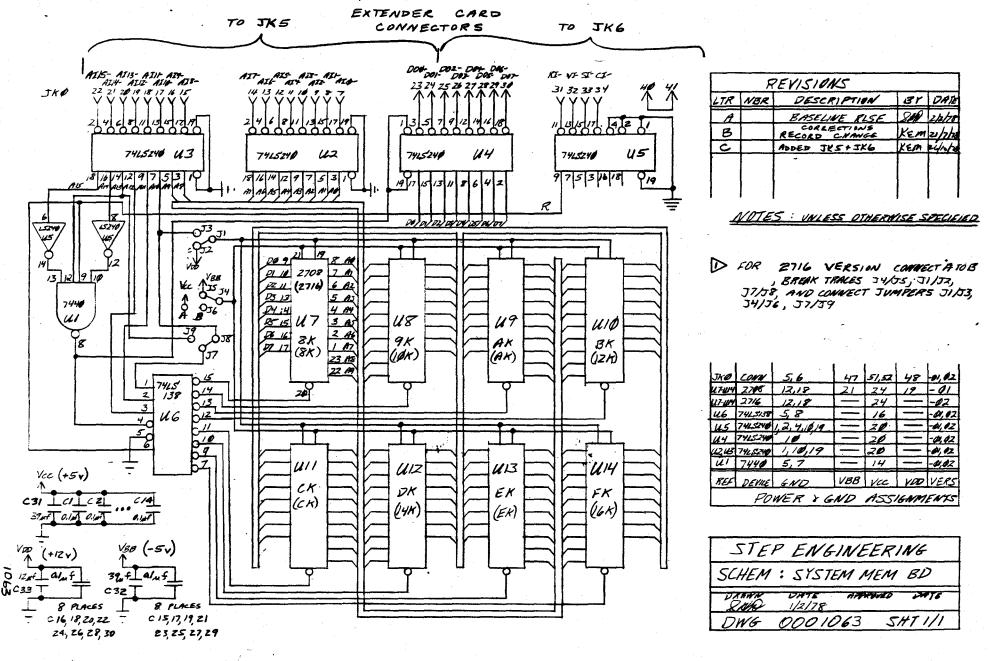

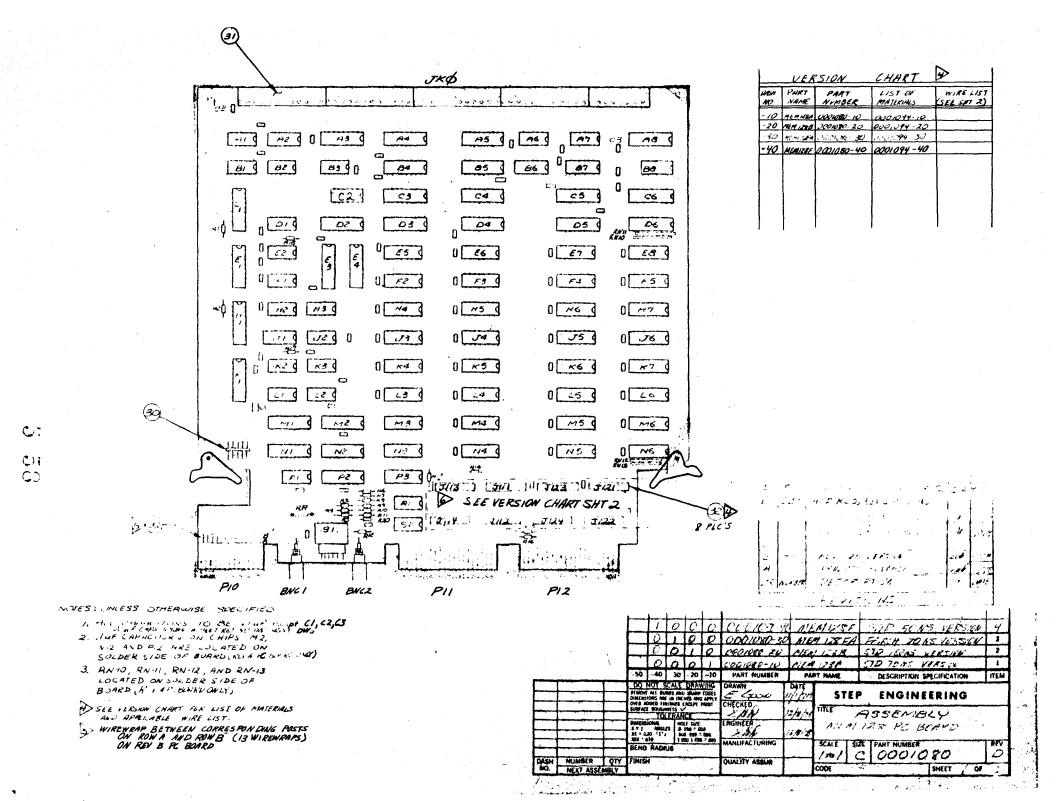

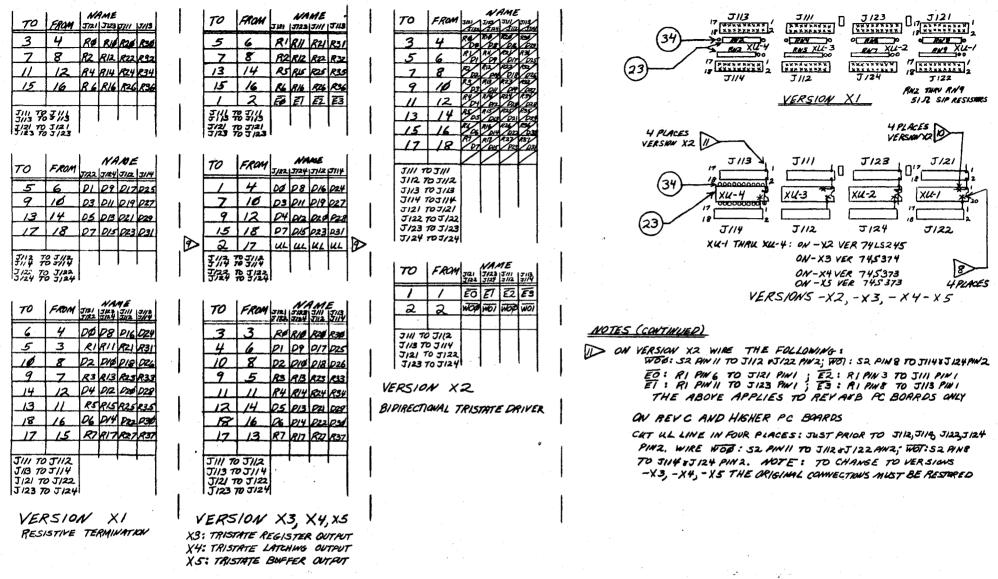

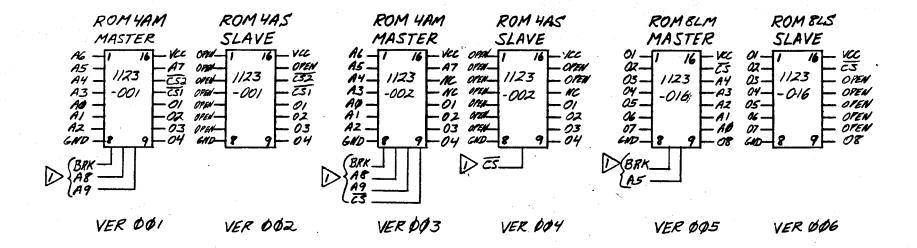

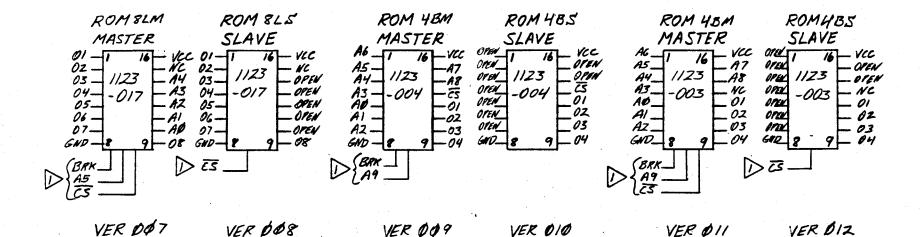

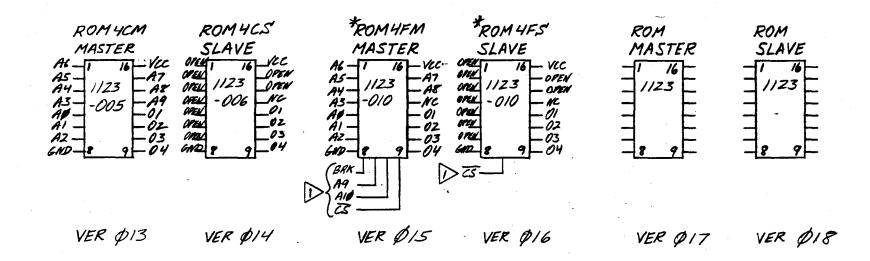

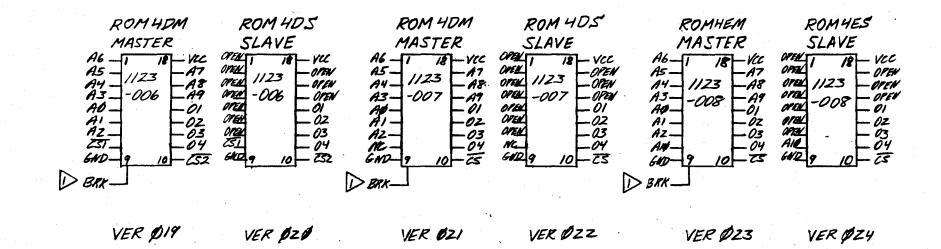

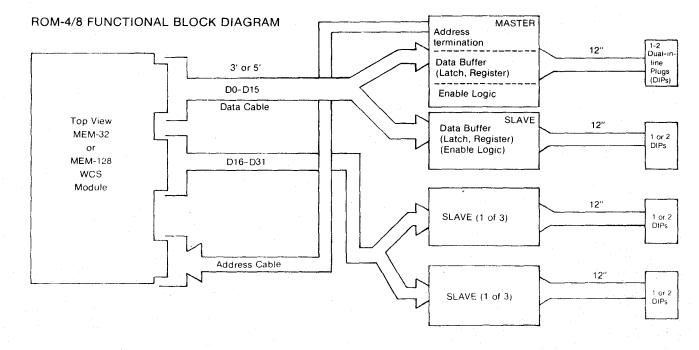

| 3.1        | WRITABLE CONTROL STORE MODULES                       |

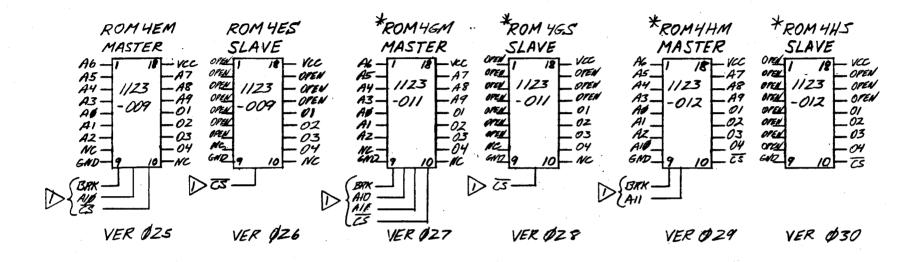

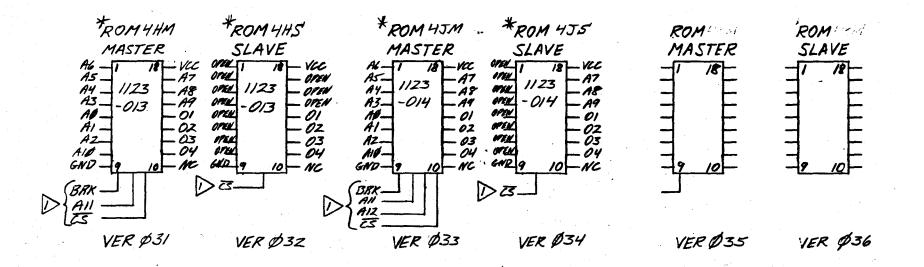

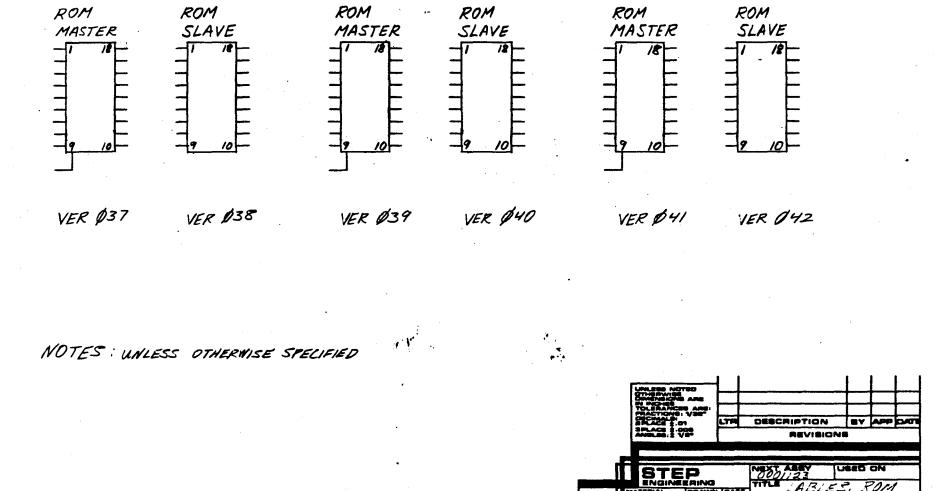

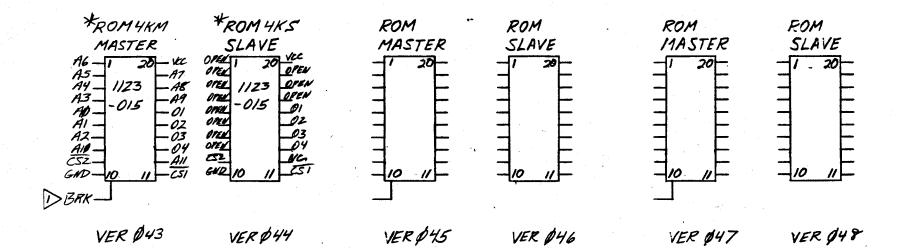

| 3.2        | ROM SIMULATION CABLE SETS                            |

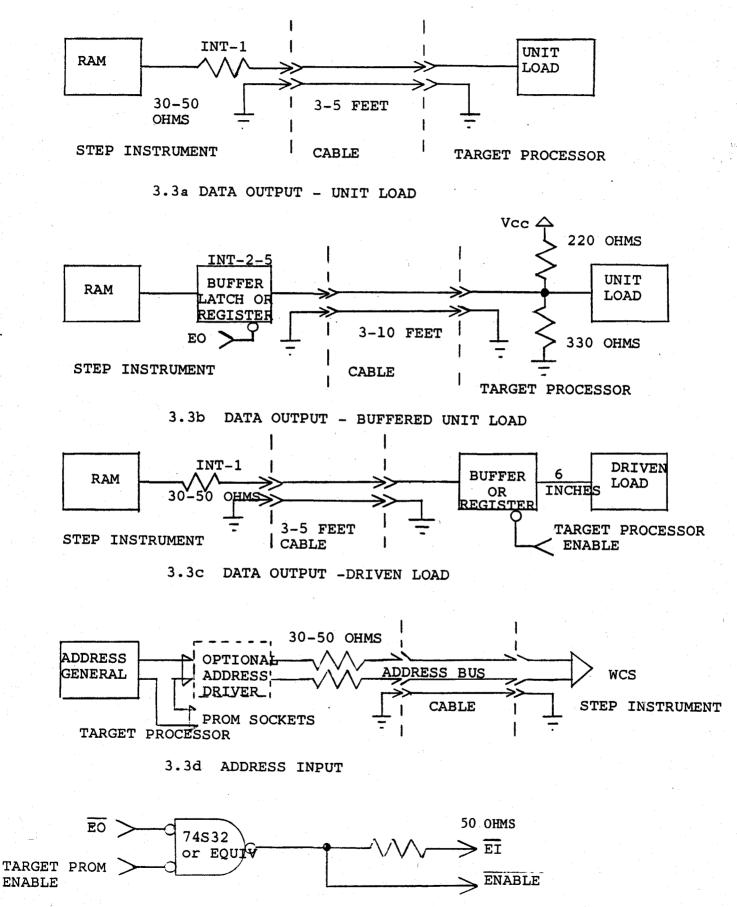

| 3.3        | DIRECT WCS INTERCONNECT (WITHOUT ROM SIMULATION)3-43 |

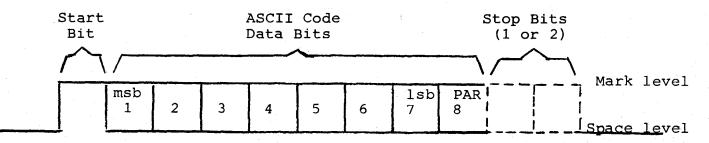

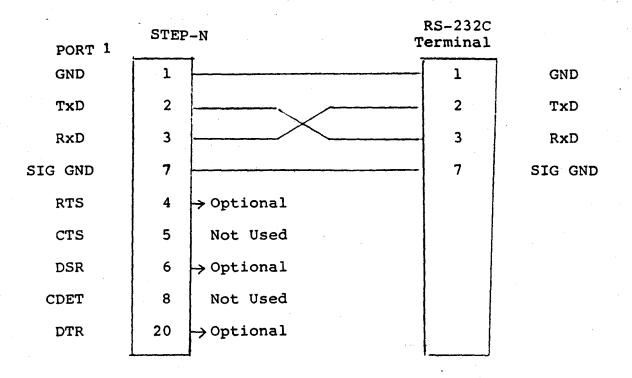

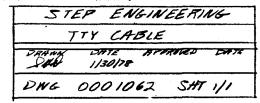

| 3.4        | SERIAL I/O INTERCONNECT                              |

| 3.5        | CLOCK CONTROL                                        |

| 3.6        | TRACE HOOKUP                                         |

| 3.7        | MAINFRAME                                            |

| 3.8        | STEP STANDARD OBJECT FILE FORMATS                    |

| 3.9        | SPEED TEST HARDWARE INTERCONNECT                     |

| 3.10       | MAXIMUM CONFIGURATION                                |

| SECTION IN | MAINTENANCE AND TROUBLE SHOOTING                     |

| 4.0        | GENERAL                                              |

| 4.1        | ROUTINE CHECKS AND PREVENTIVE MAINTENANCE4-2         |

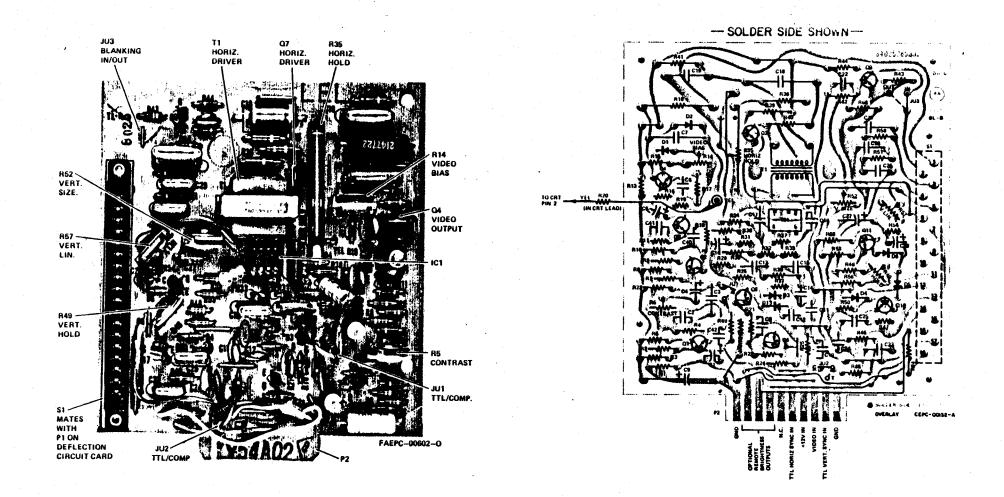

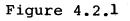

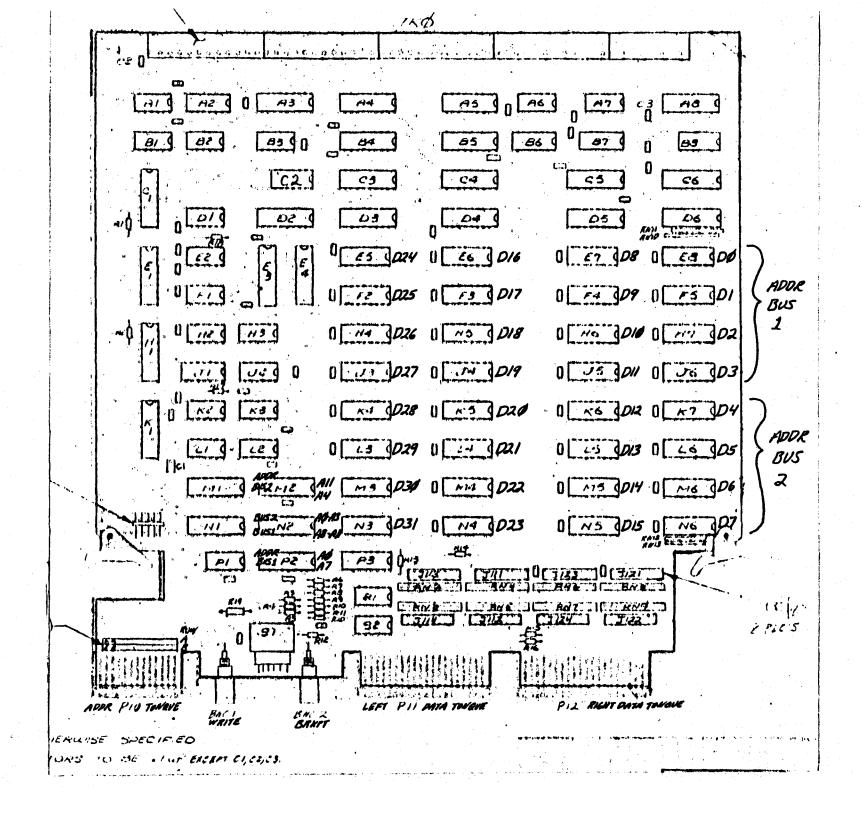

| 4.2        | MAINFRAME TROUBLE SHOOTING4-3                        |

| 4.3        | I/O PORT TROUBLE SHOOTING4-8                         |

| 4.4        | WCS TROUBLE SHOOTING4-10                             |

| 4.5        | TRACE TOUBLE SHOOTING4-14                            |

| 4.6        | GENERAL DIFFICULTIES4-17                             |

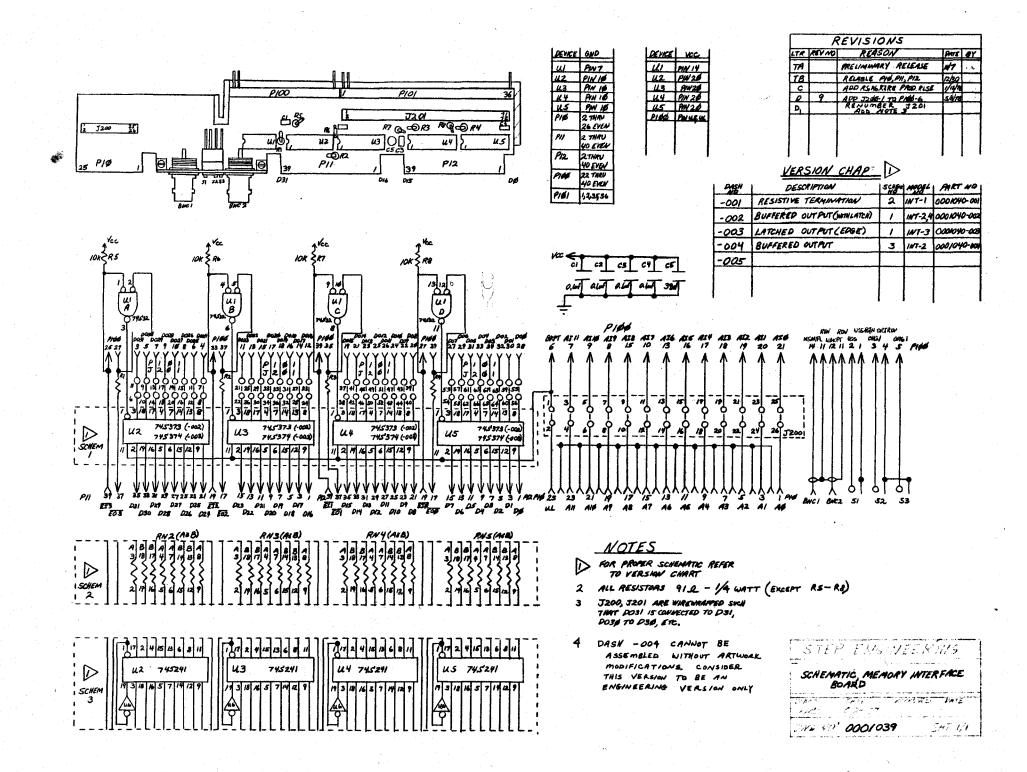

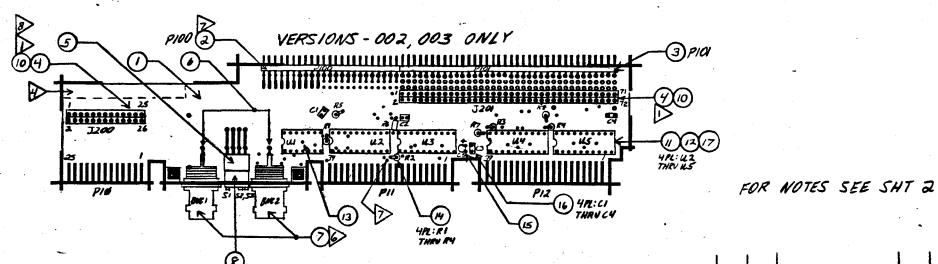

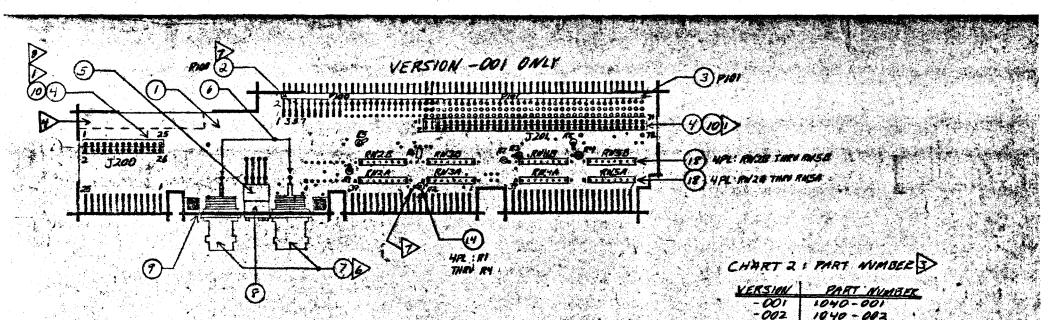

| SECTION V  | DETAILED LOGIC DRAWINGS                              |

| 5.0        | LIST OF DRAWINGS                                     |

| 5.1        | LIST OF PROPRIETARY DRAWINGS                         |

Ĵ

| SECTION | VI APPENDICES                |      |

|---------|------------------------------|------|

| A       | DATA SHEETS                  | 6-2  |

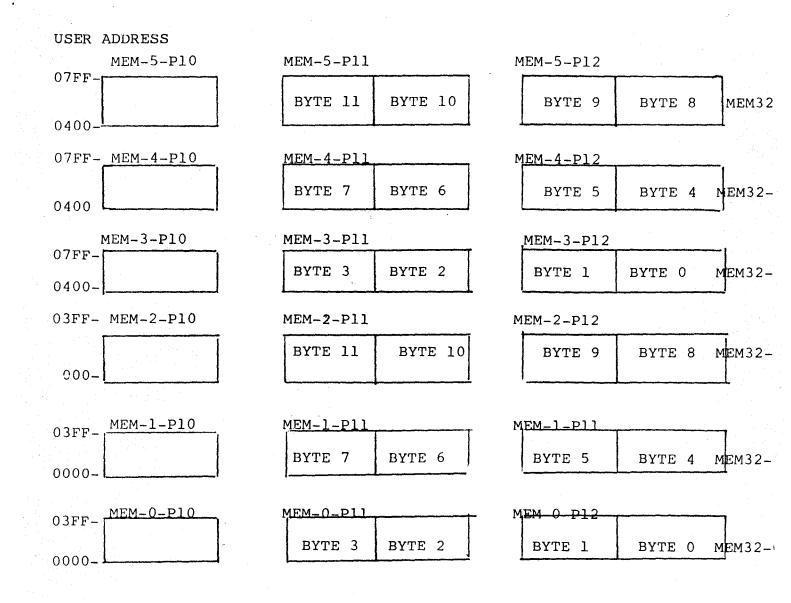

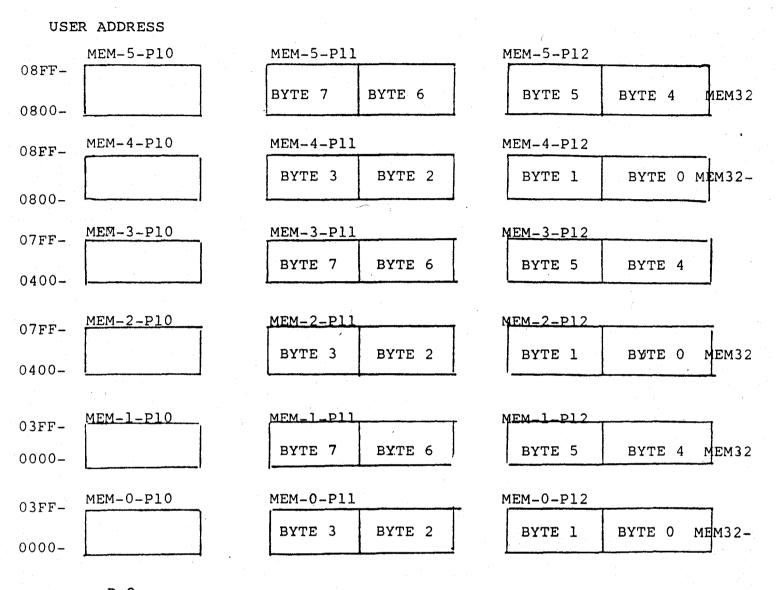

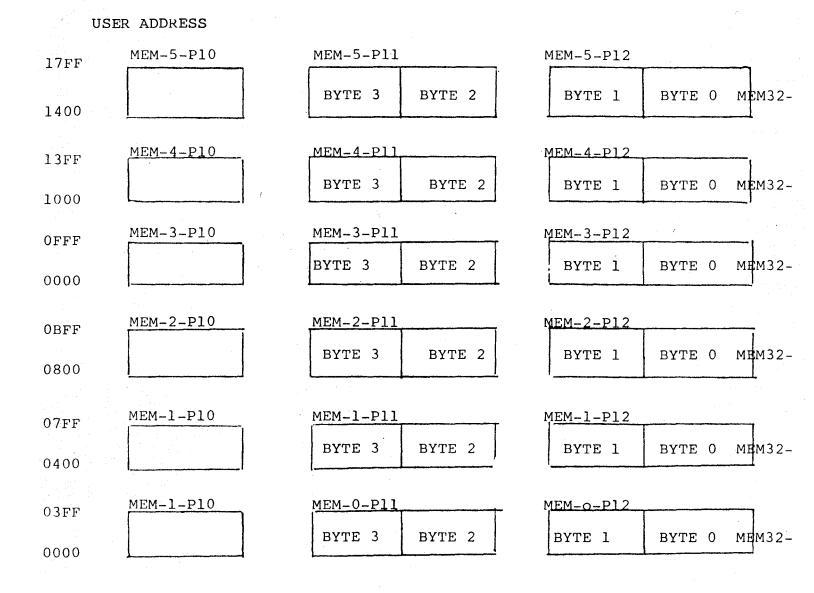

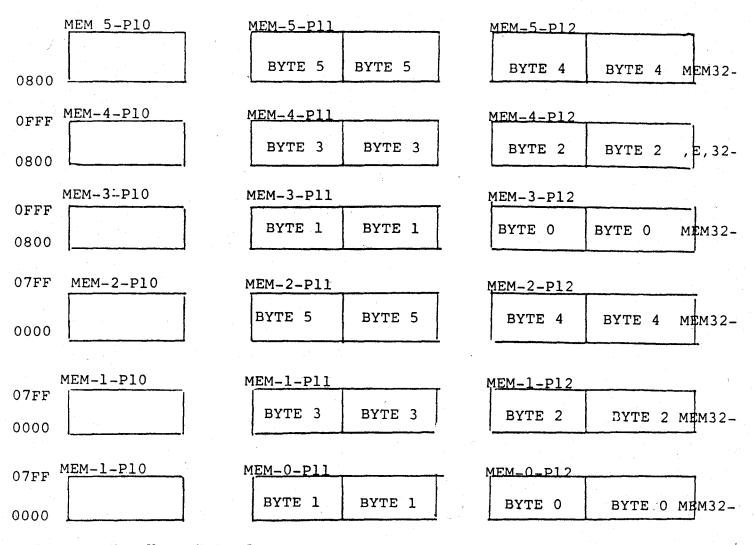

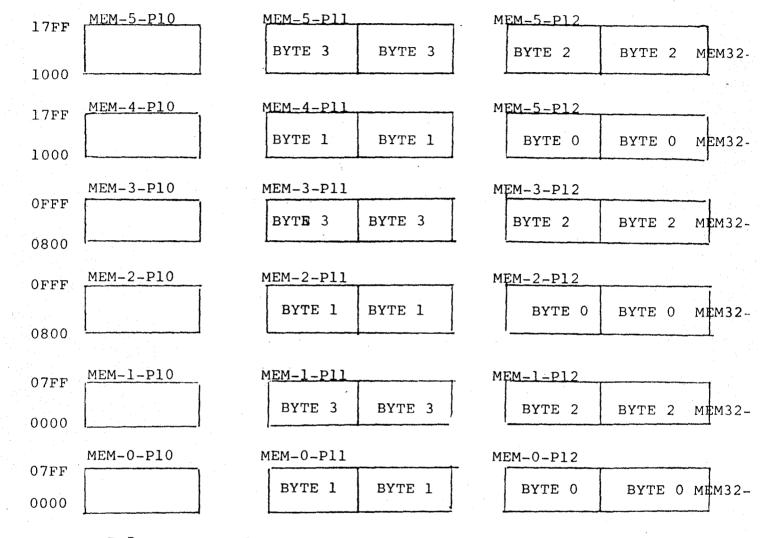

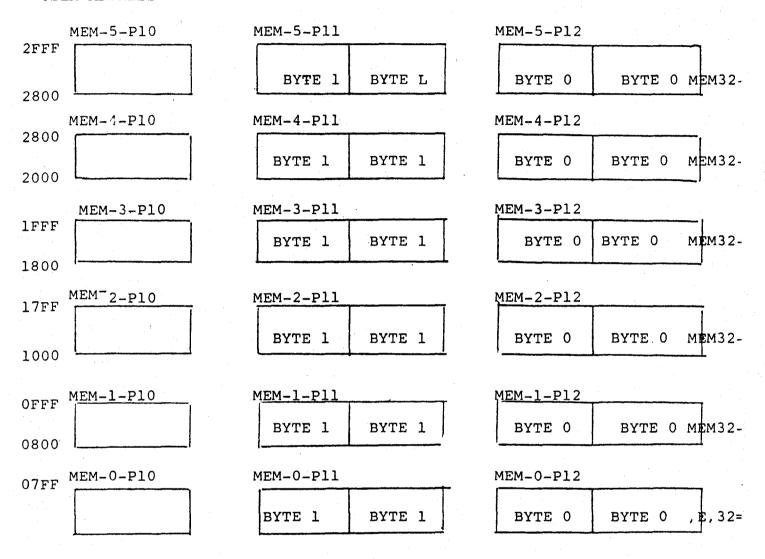

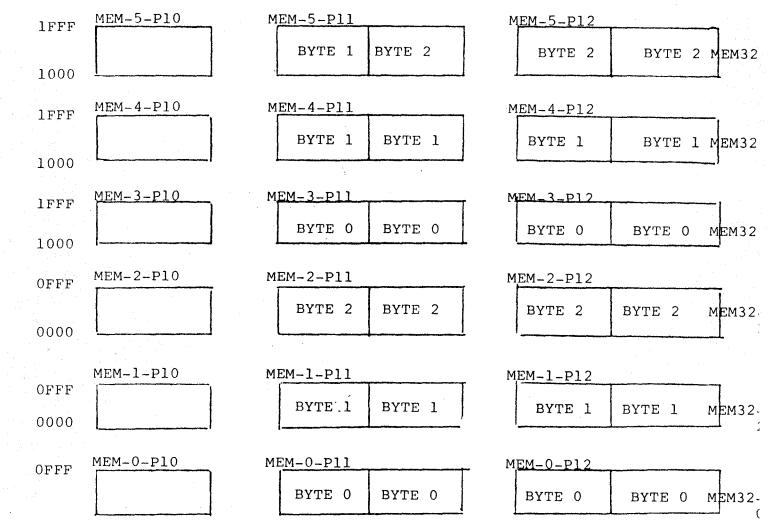

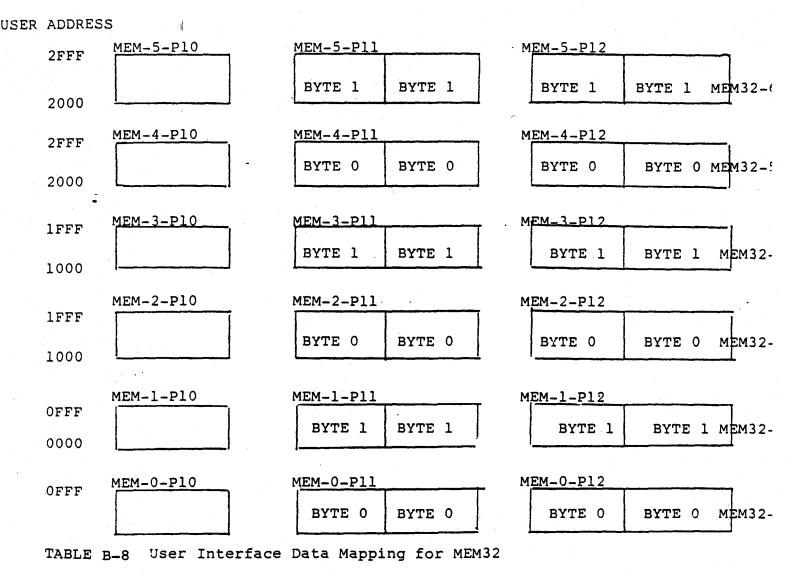

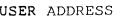

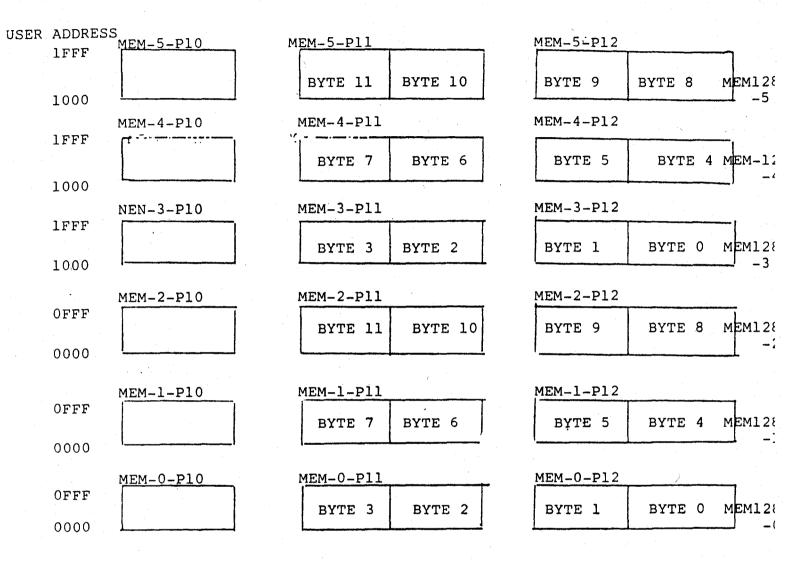

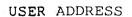

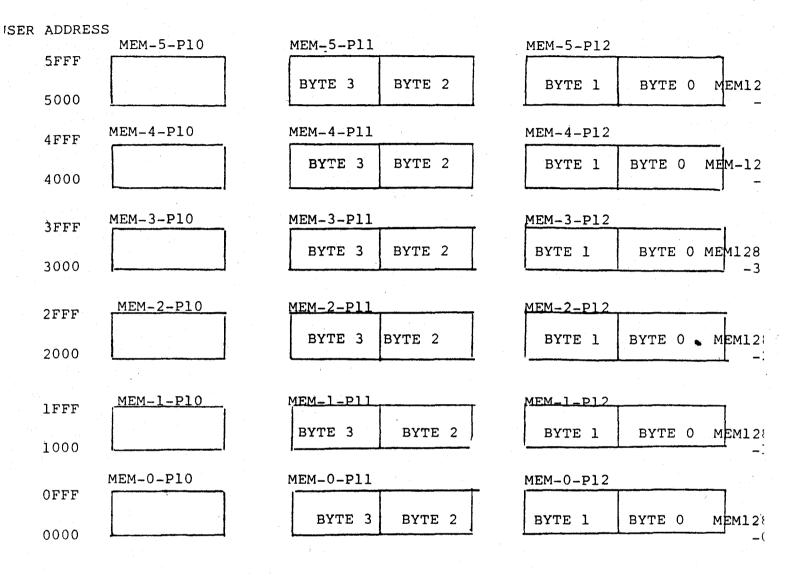

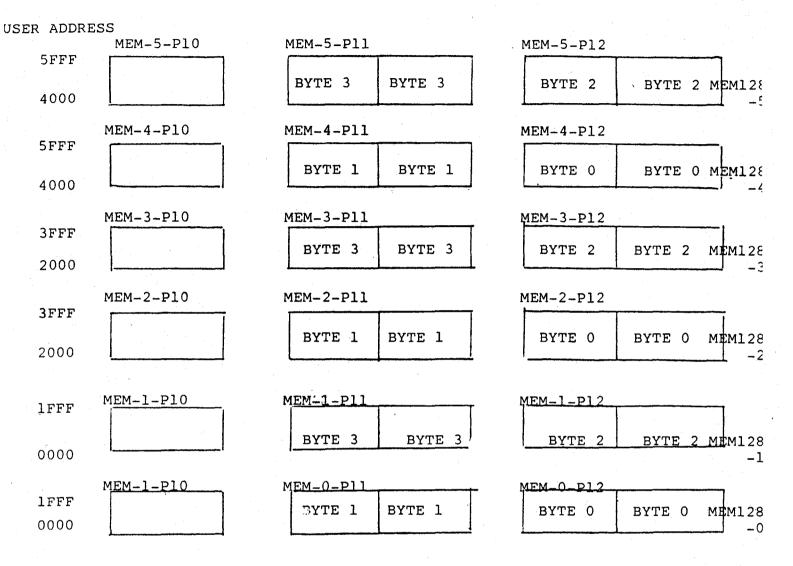

| В       | MEMORY ORGANIZATIONS         | 6-3  |

| C       | ERROR MESSAGES               | 6-19 |

| D       | ASCII TABLES                 | 6-29 |

| E       | TECHTRAN USAGE               | 6-34 |

| F       | OLD MEM-32 OPERATION         | 6-38 |

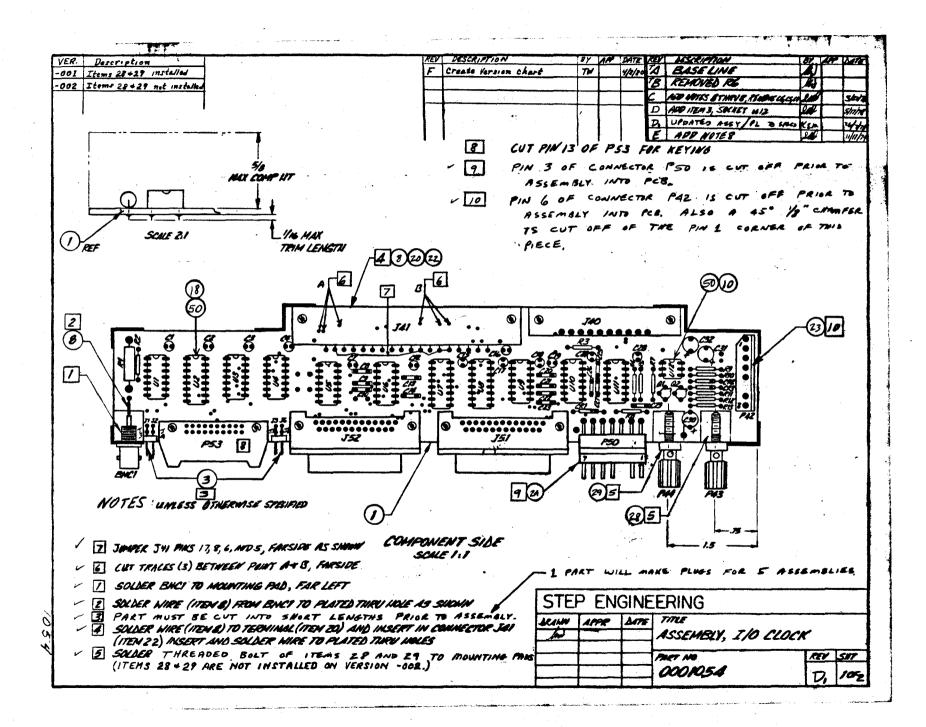

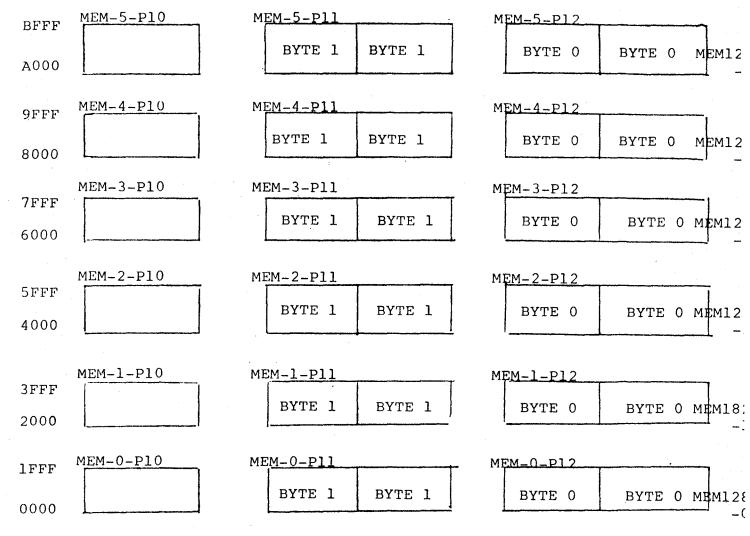

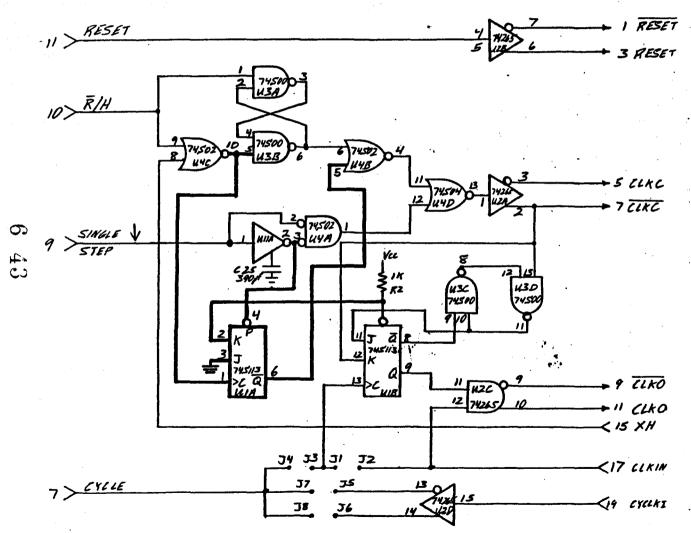

| G       | I/O CLOCK BOARD MODIFICATION | 6-42 |

# SECTION I

# CHECKOUT AND OPERATING YOUR NEW STEP INSTRUMENT

- 1,1 UNPACKING

- 1.2 GROUNDING

- 1.3 OPERATION AND CHECKOUT

- 1.4 QUICK INTERCONNECT TO TARGET

- 1.5 COMMAND SUMMARY CHART

#### UNPACKING

No special instructions are required for unpacking the STEP instrument. Use proper carton-opening devices and due care in opening the carton. If the shipping container has been damaged, request that the carrier's agent be present while the instrument is being unpacked and inspected. Inspect the mainframe for damaged I/O connectors, bent or broken case housing, and for any apparent external damage.

Your unit may have several ROM Simulation modules in sealed plastic containers. These modules should be carefully inspected for broken housings and bent or broken pins on the cable terminals (DIP plug).

Place the STEP-N instrument on a clean work surface with adequate space around the chassis to allow free air flow for cooling. Before turning on the instrument, remove the side panel and check to make sure that all boards are securely plugged into the backplane, and properly seated in the card cage. Also check to make sure that IC's are firmly seated in their sockets. Connect the STEP-N instrument to: a 115 volt AC power source with the power cord provided - U. S. versions; a 220 volt AC power source with the power cord provided - European versions. The unit is now ready for operation.

1.1

$1 \ 2$

#### GROUNDING

It is important that the STEP-N logic ground always be connected to chassis ground at <u>only one point</u> in the system, so that ground loops are avoided. STEP is usually grounded <u>via</u> the target processor.

Before connecting STEP-N to any other equipment, make sure that STEP's grounds are properly interconnected. This is accomplished by means of the banana jacks on the side of the STEP-2 unit. Two jacks are provided, one for logic ground, a black jack, and one for chassis ground, a white jack. Chassis ground is directly connected to the 3rd wire ground of the STEP power cord. When the unit is shipped, the chassis jacks are connected together by means of a shorting wire, but the <u>wire should be removed</u> for use.

In the STEP-3 instrument, the jacks are located on the rear of the unit. Black is logic ground and green is chassis ground and earth ground. A shorting bar ties them, <u>until</u> actual use.

#### 1.2.1 CONNECTION TO THE TARGET MACHINE

Connection should be made in the following manner:

Connect the black STEP-N jack, logic ground, to the logic ground of the target processor system using a heavy cable or strap. This insures that the logic grounds to the two systems remain firmly tied together even when other parts of STEP are being connected to the system. It avoids any possibility of shock damage to either piece of equipment.

2) Determine whether the target processor has its own <u>earth</u> chassis ground tied into logic ground. If chassis ground and logic ground are tied together on the target processor, or on the power supply of the target processor, <u>remove the connection</u> between the STEP chassis and logic ground on the two jacks on STEP-N.

# 1.2 (contiuned)

<u>CAUTION:</u> To avoid ground loops and possible equipment failure, chassis ground must be tied into the system at only one point. If chassis ground is not tied to logic ground at at least one point in the system, logic ground may float with respect to chassis ground causing a shock hazard.

# **OPERATION & CHECKOUT**

1.3.1 SETUP

1.3

Due to its versatility, STEP-N permits over 200 different instrument organizations. The following setup procedure is a nominal case:

- 1) Determine number of memory boards and memory types: MEM128 or MEM32. If you are not sure what memory boards are installed in your instrument, check the configuration sheet shipped with the unit. The checkout parameters to be used are shown on chart 1.3.1, Checkout Parameters.

- 2) Set the switches properly on the side of each memory board as follows:

|                            |               | <u>s1</u> | <u>S2</u> | <u></u> | <u>S4</u> | <u>s5</u> | S6         |

|----------------------------|---------------|-----------|-----------|---------|-----------|-----------|------------|

| six (6)<br>Switch Memory   |               | OFF       | ON        | ON      | ON        | OFF       | ON         |

| *four (4)<br>Switch Memory |               | OFF       | OFF       | ON      | ON        |           |            |

| *(obsolescent)             | <u>NOTE</u> : | OFF       | = down, O | N = up, | See mark  | ings on s | ide panel. |

# 1.3.2 OPERATION

NOTE 1: Nomenclature: A standard alphanumeric key is represented by a number or capital letter. A special key has a ( ) around it. Example: CR would be the C key followed by an R key, while (CR) would stand for the Carriage Return key labeled "CR" on the keyboard.

1

CHART

1.3.1

# CHECKOUT PARAMETERS

|   | NU<br>MEM                                      | MBER OF<br>COMPOSED             | OF                              | NUMBER<br>OF                                        | ARRAY                                  | I                               | ARRAY                                  | 2                                    |     |

|---|------------------------------------------------|---------------------------------|---------------------------------|-----------------------------------------------------|----------------------------------------|---------------------------------|----------------------------------------|--------------------------------------|-----|

|   | BOARDS                                         | MEM 32                          | MEM 128                         | ARRAYS                                              | WIDTH                                  | DEPTH, d                        | WIDTH                                  | DEPTH, d                             |     |

|   | 1<br>1                                         | 1<br>0                          | 0<br>1                          | 1<br>1                                              | 32 Bits<br>32                          | 1k words<br>4                   | X<br>X                                 | X<br>X                               |     |

|   | 2<br>2<br>2                                    | 2<br>0<br>1                     | 0<br>2<br>1                     | 1<br>1<br>2                                         | 64<br>64<br>32                         | 1<br>4<br>1                     | X<br>X<br>32 Bits                      | x<br>x<br>4 k wa                     | ord |

| - | 3<br>3<br>3<br>3                               | 3<br>0<br>2<br>1                | 0<br>3<br>1<br>2                | 1<br>1<br>2<br>2                                    | 96<br>96<br>64<br>32                   | 1<br>4<br>1<br>1                | X<br>X<br>32<br>64                     | X<br>X<br>4<br>4                     |     |

|   | → 4<br>4<br>4                                  | 4<br>0<br>3<br>2                | 0<br>4<br>1<br>2                | 1<br>1<br>2<br>2                                    | 64<br>64<br>96<br>64                   | 2<br>8<br>1<br>1                | X<br>X<br>32<br>64                     | X<br>X<br>4<br>4                     |     |

|   | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5           | 1<br>5<br>0<br>4<br>3<br>2<br>1 | 3<br>0<br>5<br>1<br>2<br>3<br>4 | 2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2 | 32<br>96<br>96<br>64<br>96<br>64<br>32 | 1<br>4<br>2<br>1<br>1<br>1<br>1 | 96<br>64<br>64<br>32<br>64<br>96<br>64 | 4<br>1<br>4<br>4<br>4<br>4<br>4<br>8 |     |

|   | 6<br>6<br>6<br>6<br>6<br>6<br>6<br>6<br>6<br>6 | 6<br>0<br>5<br>4<br>3<br>2<br>1 | 0<br>6<br>1<br>2<br>3<br>4<br>5 | 1<br>1<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2 | 96<br>96<br>32<br>64<br>96<br>64<br>32 | 2<br>8<br>5<br>2<br>1<br>1<br>5 | X<br>X<br>32<br>64<br>96<br>64<br>32   | X<br>X<br>4<br>4<br>4<br>8<br>20     |     |

|   |                                                |                                 |                                 |                                                     |                                        |                                 |                                        |                                      |     |

#### 1.3.2 OPERATION (cont)

- NOTE 2: Underlined Characters: If an input has one or more underlined characters, those alone are sufficient. Example: <u>H</u>EX (CR) indicates that H carriage return is sufficient for the input.

- NOTE 3: *Examples:* The example shown below is for an instrument with either two MEM32 Writable Control Stores or three MEM128 WCS. Use chart 1.3.lto enter the proper information for NUMBER OF ARRAYS, WIDTH, AND DEPTH. A superscript "1" stands for 64 bit organization. A superscript "2" stands for 96 bit organization.

- <u>NOTE</u>: Board Locations: In all cases, insert all the MEM-32 boards if any below the MEM-128 boards if any. The two families cannot be mixed in one array. The STEP firmware prefers MEM-32s to dedicate to array 1.

The following is a step-by-step checkout procedure which, when completed successfully, verifies all machine functions.

We recommend that this checkout be performed when the instrument is first received. This will familiarize the user with its operation as well as check the functions prior to one-line use.

Rapid verification of instrument function in an on-line environment can be achieved using the <u>TEST</u> command. Expanded memory check ability is possible with the optional speed test hardware. The test command is explained in section 2.2.4.

1

| <ul> <li>Coptionally, test routines can be run at the powerpy time. These are STRP-3's built-in self-test routines. See section 2.2 for description.)</li> <li>1.3.2.1 SETUP COMMAND</li> <li>STEP-N has the capability of simulating 2 independent memory yarays. This enables the instrument to be used simultaneously for: two projects; adual processor project; microcode and macrocode; microcode and mapping ROMs. The following tests are nominal case prechart One array is used unless two are required for Checkour, e.g. unless both REM-32 and MEM-128 are used.</li> <li>Data may be displayed in either Hexadocimal or Octal. Demo routines are in HEX.</li> <li>Com STEP-N can configure memory to start at any arbitrary address from 8 to 96 bits in each array and may be different for each array. See note 3.</li> <li>Depth is given in increments of 1024 words: 1 is 1k, 21 s 2k etc Designers utilizing memory depths of less than 1k can use the extra memory to aid code debug. Minisum depth is "1"</li> <li>If the physical memory configuration does not match the values entered during spiration, is will show on the CKT and all the user does is to enter the correct value. Use (UEL) key to correct mispellings, etc</li> <li>NUMBER ARAYS = 1 (CR)</li> <li>Data may be different for each array. See note 3.</li> <li>Depth is given in increments of 1024 words: 1 is 1k, 21 s 2k etc Designers autilizing memory depths of less than 1k can use the extra memory to aid code debug. Minisum depth is "1"</li> <li>If the physical memory configuration does not match the values entered during sportation, is vill show on the CKT and all the user does is to enter the correct value. Use (UEL) key to correct mispellings, etc</li> <li>Note the top Line of the display. It always shows configure memory depined memory configured memory has been set and metantion and metantion does not match the values entered during sportation, is will show on the CKT and al</li></ul>                                                                                                                      |          | COMMENTS                                                                                                                                                                                                                                                                                       | DISPLAY                               | OPERATION                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------------------------------|

| <ul> <li>1.3.2.1 SETUP COMMAND</li> <li>STEP-N has the capability of simulating 2 independent memory arrays. This enables the instrument to be used simultaneously for: two projects; a dual processor project; microcode and mapping ROMs. The following tests are nominal case per chart One array is used unless two are required for checkout, e.g. unless both MEM-32 and MEM-128 are used.</li> <li>Data may be displayed in either Hexadecimal or Octal. Demo routines are in HEX.</li> <li>STEP-N can configure memory to start at any arbitrary address from 0 to 7FFF (Hex).</li> <li>The word width can be from 8 to 96 bits in each array, and may be different for each array. See note 3.</li> <li>Depth is given in increments of 1024 words: 1 is IK, 2 is 2k etc Designers utilizing memory depths of less than Ik can use the extra memory depths of less than Ik can use the extra memory depths of less than Ik can use the extra memory depths of less than Ik can use the extra memory depths of less than Ik can use the extra memory util be flagged and parameters must be re-entered.</li> <li>1.3.2.2 ERROR CORRECTION</li> <li>Step operation, is vill show on the CRT and all the user does is to enter the correct value. Use (DEL) key to correct misspellings, etc</li> <li>Note the top line of the display. It always shows</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          | up time. These are STEP-3's built-in self-test                                                                                                                                                                                                                                                 |                                       |                                                               |

| <ul> <li>STEP-N has the capability of simulating 2<br/>independent memory arrays. This enables the<br/>instrument to be used simultaneously for: two<br/>projects; a dual processor project; microcode<br/>and macrocode; microcode and mapping ROMS. The<br/>following tests are nominal cases per chart<br/>One array is used unless both MEN-128 are<br/>used.</li> <li>Data may be displayed in either Hexadecimal or<br/>Octail. Demo routines are in HEX.</li> <li>STEP-N can configure memory to start at any<br/>arbitrary address from 0 to 7FFF (Hex).</li> <li>The word width can be from 8 to 96 bits in each<br/>array and may be different for each array.<br/>See note 3.</li> <li>Depth is given in increments of 1024 words:<br/>1 is Ik, 2 is 2k etc Designers utilizing<br/>memory depths of less than Ik can use the extra<br/>memory to sid code debug. Minimum depth is "!"</li> <li>I.3.2.2</li> <li>ERROR CORRECTION<br/>Step operation, it will show on the CRT and all<br/>the user does is to enter the correct value. Use<br/>(NEL) key to correct misspelling, etc</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |                                                                                                                                                                                                                                                                                                |                                       |                                                               |

| <ul> <li>independent memory arrays. This enables the instrument to be used simultaneously for: two projects; a dual processor project; microcode and mapping ROMs. The following tests are nominal case per chart. One array is used unless two are required for checkout, e.g. unless both MEM-32 and MEM-128 are used.</li> <li>Data may be displayed in either Hexadecimal or Octal. Demo routines are in HEX.</li> <li>STEP-N can configure memory to start at any arbitrary address from 0 to 7FFF (Hex).</li> <li>The word width can be from 8 to 96 bits in each array. See note 3.</li> <li>Depth is given in increments of 1024 words: 1 is 1k, 2 is 2k etc Designers utilizing memory to aid code debug. Minimum depth is "1" If the physical memory configuration does not match the values entered during SETUP, an error will be flagged and parameters must be re-entered.</li> <li>1.3.2.2 ERROR CORRECTION</li> <li>Step operation, it will show on the CRT and all the user does is to enter the correct value. Use (UEL) key to correct mispelling, etc</li> <li>Note the top line of the display. It always shows</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1.3.2.1  | SETUP COMMAND                                                                                                                                                                                                                                                                                  |                                       |                                                               |

| →       Data may be displayed in either Hexadecimal or Octal. Demo routines are in HEX.       DATA =       HEX (CR)         ∞       STEP-N can configure memory to start at any arbitrary address from 0 to 7FFF (Hex).       STARTING ADDR =       0 (CR)         ∞       The word width can be from 8 to 96 bits in each array. See note 3.       Depth is given in increments of 1024 words:       WIDTH =       64 (CR) <sup>1</sup> 0       Depth is given in increments of 1024 words:       I is 1k, 2 is 2k etc Designers utilizing memory to sid cless than 1k can use the extra memory to aid code debug. Minimum depth is "1"       DEPTH =       1 (CR) <sup>2</sup> 1.3.2.2       ERROR CORRECTION       Step operation is failsafe. If an error is made during operation, it will show on the CRT and all the user does is to enter the correct value. Use (DEL) key to correct misspellings, etc       Note the top line of the display. It always shows       Note the top line of the display. It always shows                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          | independent memory arrays. This enables the<br>instrument to be used simultaneously for: two<br>projects; a dual processor project; microcode<br>and macrocode; microcode and mapping ROMs. The<br>following tests are nominal case per chart<br>One array is used unless two are required for | NUMBER ARRAYS =                       | 1 (CR)                                                        |

| <ul> <li>arbitrary address from 0 to 7FFF (Hex).</li> <li>The word width can be from 8 to 96 bits in each array and may be different for each array. See note 3.</li> <li>Depth is given in increments of 1024 words: <ol> <li>is Ik, 2 is 2k etc Designers utilizing memory depths of less than Ik can use the extra memory to aid code debug. Minimum depth is "1"</li> <li>If the physical memory configuration does not match the values entered during SETUP, an error will be flagged and parameters must be re-entered.</li> </ol> </li> <li>1.3.2.2 ERROR CORRECTION Step operation is failsafe. If an error is made during operation, it will show on the CRT and all the user does is to enter the correct value. Use (DEL) key to correct misspellings, etc Note the top line of the display. It always shows WIDTH = 64 (CR)<sup>1</sup>/96 (CR)<sup>2</sup> 96 (CR)<sup>2</sup> 96 (CR)<sup>2</sup> 96 (CR)<sup>2</sup> 96 (CR)<sup>2</sup> 96 (CR)<sup>2</sup> 97 (CMND (indicates Step-N is ready for any command) 1.3.2.2 ERROR CORRECTION Step operation is failsafe. If an error is made during operation, it will show on the CRT and all the user does is to enter the correct value. Use (DEL) key to correct misspellings, etc Note the top line of the display. It always shows</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -        | Data may be displayed in either Hexadecimal or                                                                                                                                                                                                                                                 | DATA =                                | HEX (CR)                                                      |

| <ul> <li>array and may be different for each array.<br/>See note 3.</li> <li>Depth is given in increments of 1024 words: <ol> <li>is lk, 2 is 2k etc Designers utilizing</li> <li>memory depths of less than lk can use the extra</li> <li>memory to aid code debug. Minimum depth is "1"</li> <li>If the physical memory configuration does not</li> <li>match the values entered during SETUP, an error</li> <li>will be flagged and parameters must be re-entered.</li> </ol> </li> <li>1.3.2.2 ERROR CORRECTION Step operation is failsafe. If an error is made during operation, it will show on the CRT and all the user does is to enter the correct value. Use (DEL) key to correct misspellings, etc Note the top line of the display. It always shows DEPTH = 96 (CR)<sup>2</sup> 1 (CR)<sup>2</sup> 4 (CR)<sup>2</sup> 4 (CR)<sup>2</sup> 5 (CR)<sup>2</sup> 5 (CR)<sup>2</sup> 5 (CR)<sup>2</sup> 9 (CR)<sup>2</sup> 5 (CR)<sup>2</sup> 6 (CR)<sup>2</sup> 9 (CR)<sup>2</sup> 6 (CR)<sup>2</sup> 9 (CR)<sup>2</sup></li></ul> | $\infty$ | STEP-N can configure memory to start at any arbitrary address from 0 to 7FFF (Hex).                                                                                                                                                                                                            | STARTING ADDR =                       | 0 (CR)                                                        |

| <ul> <li>1 is 1k, 2 is 2k etc Designers utilizing memory depths of less than 1k can use the extra memory to aid code debug. Minimum depth is "1"</li> <li>If the physical memory configuration does not match the values entered during SETUP, an error will be flagged and parameters must be re-entered.</li> <li>1.3.2.2 ERROR CORRECTION</li> <li>Step operation is failsafe. If an error is made during operation, it will show on the CRT and all the user does is to enter the correct value. Use (DEL) key to correct misspellings, etc</li> <li>Note the top line of the display. It always shows</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          | array and may be different for each array.                                                                                                                                                                                                                                                     | WIDTH =                               | $\begin{array}{c} 64 & (CR)^{1} \\ 96 & (CR)^{2} \end{array}$ |

| If the physical memory configuration does not<br>match the values entered during SETUP, an error<br>will be flagged and parameters must be re-entered.(indicates Step-N<br>is ready for any<br>command)1.3.2.2ERROR CORRECTIONStep operation is failsafe. If an error is made<br>during operation, it will show on the CRT and all<br>the user does is to enter the correct value. Use<br>(DEL) key to correct misspellings, etcNote the top line of the display. It always shows                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          | l is lk, 2 is 2k etc Designers utilizing<br>memory depths of less than lk can use the extra                                                                                                                                                                                                    | DEPTH =                               | $ \begin{array}{c} 1 & (CR)^{l} \\ 4 & (CR)^{2} \end{array} $ |

| Step operation is failsafe. If an error is made<br>during operation, it will show on the CRT and all<br>the user does is to enter the correct value. Use<br>(DEL) key to correct misspellings, etc<br>Note the top line of the display. It always shows                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          | If the physical memory configuration does not<br>match the values entered during SETUP, an error                                                                                                                                                                                               | (indicates Step-N<br>is ready for any |                                                               |

| during operation, it will show on the CRT and all<br>the user does is to enter the correct value. Use<br>(DEL) key to correct misspellings, etc<br>Note the top line of the display. It always shows                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1.3.2.2  | ERROR CORRECTION                                                                                                                                                                                                                                                                               |                                       |                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          | during operation, it will show on the CRT and all<br>the user does is to enter the correct value. Use                                                                                                                                                                                          |                                       |                                                               |

| configuration, current command and allay.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          | Note the top line of the display. It always shows configuration, current command and array.                                                                                                                                                                                                    |                                       |                                                               |

| #         | COMMENTS                                                                                                                                                                                                                                                                                                                        | DISPLAY                                                              | OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.3.2.3   | EDITOR                                                                                                                                                                                                                                                                                                                          |                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|           | The following sequence demonstrates the use of STEP-N's editor.                                                                                                                                                                                                                                                                 | ENTER COMMAND                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1.3.2.3.1 | ENTER COMMAND                                                                                                                                                                                                                                                                                                                   |                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|           | Start with the main editing command, ENTER.<br>Note that memory has random data-memory contents not<br>altered during STEP-N operation even when "Reset" key<br>is pressed. The contents of memory is altered only .<br>through user command. Locations 0,1,2 and 3 are dis-<br>played.                                         | (Random WCS<br>contents of add-<br>ress locations<br>O thru 3).      | <u>enter</u> (CR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | Pick a convenient memory address. Four memory lines<br>are displayed starting with the current address (in<br>this case 1FE). Use the cursor Up/Down keys to<br>increment, decrement, or scroll through memory.                                                                                                                 | ADDRESS =                                                            | ADDR (CR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|           | To modify the contents of memory, push the "ENTER"<br>key. This moves cursor to data field. Enter some<br>data in memory. Use cursor left and right keys to<br>position cursor within the data. Note the binary                                                                                                                 |                                                                      | Cursor $\checkmark \uparrow$ keys to address IFO<br>(ENTER) key<br>0123 4567 89AB CDEF <sup>1,2</sup> FEDC BA98 <sup>2</sup><br>111 111 1111 1111, 2 FEDC BA98 <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1 9       | representation of the first five digits beginning<br>with the cursor (always 5 digits or less regardless<br>of word width). Note binary duplicates the Hex.                                                                                                                                                                     |                                                                      | 1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111       1111 |

|           | The line above the data contains the following<br>information: The current address at cursor location,<br>the current bit position of the most significant bit<br>at the cursor location starting with bit "O" as LSB<br>on the right, and the binary expansion field, which<br>scrolls through the word, under cursor control. | AAA PP BBBB BBBB<br>    BINARY<br>  BIT POSITION<br>ADDRESS          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|           | When entering data, note the auto scroll feature.<br>However wide the microcode word, one line is one<br>word. The data has a one line buffer and is not<br>entered into memory until (CR) key is pressed.                                                                                                                      | 0123 4567 89AB                                                       | At the address containing:<br>0 1 2 3enter<br>"F F F F F F F F" Do <u>not</u> hit (CR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           | Use the (DEL) and (CLEAR) keys to restore mistakes, a<br>character or line at a time, respectively. Use the<br>Cancel and Home; (C & H) key to leave the data field.<br>Quit the ENTER mode and go to top command level by<br>typing Q (CR).                                                                                    | FFFF FFF7 89AB<br>FFFF FF67 89AB<br>FFFF F567 89AB<br>0123 4567 89AB | Press (DEL) key<br>Press (DEL) key<br>Press (CLEAR) key                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|           | *Or (HOME) on STEP-3.                                                                                                                                                                                                                                                                                                           | (cursor to line 3)<br>ENTER COMMAND                                  | Press (C & H) key<br><u>Q</u> UIT (CR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

#### 1.3.2.3.2

11

MOVE COMMAND

The following sequence demonstrates the use of the Move command, the second of the four editing commands. Move is non-destructive, like a "copy".

The Move command is used to 1) Save a subroutine in an unused portion of memory prior to temporary modification. 2) To insert new lines of code into a subroutine by moving a block of data up or down several lines to free space for new code. Since this wipes out existing code, and could change reference locations, care should be taken when using this command. NOPs should be placed within the code and between subroutines during debug to allow room for new code.

The following routine moves the previously entered code which starts at Source Address 1FO (see 1.3.2.1.3) to destination Address 1. The NUMBER of LOCATIONS specifies in decimal the length of the block to be moved. By using the Enter command the results of the move can be accessed at both address 0 and address 1FO. Notice that the STEP-N command is like a "copy" instruction, in that the source remains unchanged.

Address of display window Contents of location 0000 Contents of location 0001 Contents of location 0002 Contents of location 0003

#### SEARCH COMMAND

The following sequence demonstrates the use of the Search command, the third of the four editing commands. The Fill command, the last editing command, is demonstrated when checking memory contents. SOURCE ADDRESS =

ENTER COMMAND

DESTINATION ADDRESS = NUMBER LOCATIONS = CMND 0000 XXXX XXXX XXXX... 0123 4567 89AB... 1111 1111 ...

2222

CMND

2222 2222...

ENTER (CR)

MOVE (CR)

1 (CR)

3 (CR)

QUIT (CR)

1FO (CR) (assumed address containing 0123...)

1.3.2.3.3

| #          | COMMANDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DISPLAY                                                                                                                  | OPERATION                                                                                                                                                                                                                       |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                          |                                                                                                                                                                                                                                 |

| 1.3.2.3.3  | SEARCH COMMAND (CONT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CMND                                                                                                                     |                                                                                                                                                                                                                                 |

| 1.3.2.4    | The Search command is used to find all instructions<br>with certain fixed fields. A memory block, field<br>contents, and don't care bits may be specified. In<br>this example all locations between START ADDRESS =<br>0 and END ADDRESS = 300 Hex will be examined.<br>The memory block will be searched for a data word<br>of 012XX Every time the "CR" key is pressed, the<br>search will continue from the last word found.<br>To abort Search, use the (C & H), Cancel and<br>Home key. (X or don't care calls for 0 in the mask)<br>USING THE RS232 LINK SETUP<br>The following sequence demonstrates the ease of | ENTER COMMAND<br>START ADDRESS =<br>END ADDRESS =<br>DATA =<br>DON'T CARE =<br>MATCH AT ADDR =<br>NO MATCH FOUND<br>CMND | SEARCH<br>0 (CR)<br>300 (CR)<br>0123 4567 0000(argument)<br>FFF0 0000 0000(mask)<br>(CR) (CR)<br>(CR)<br>(To create a SEARCH example with<br>more "HITS" or matches, use fewer<br>1's (fewer F's) in the mask.)                 |

| 1.3.2.4.1  | establishing communication between STEP-N and an<br>external device such as a Prom Programmer or<br>Computer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                          |                                                                                                                                                                                                                                 |

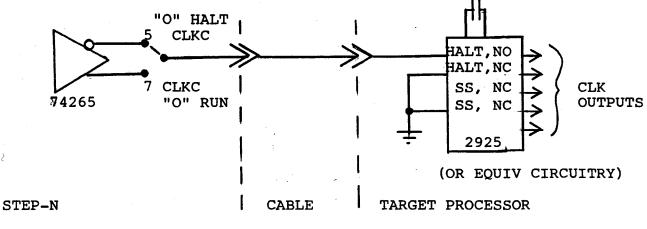

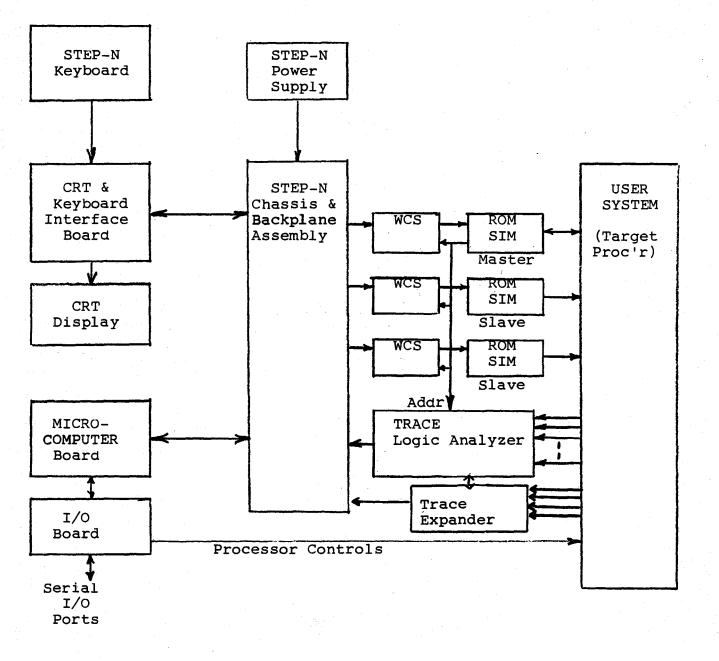

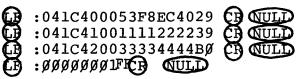

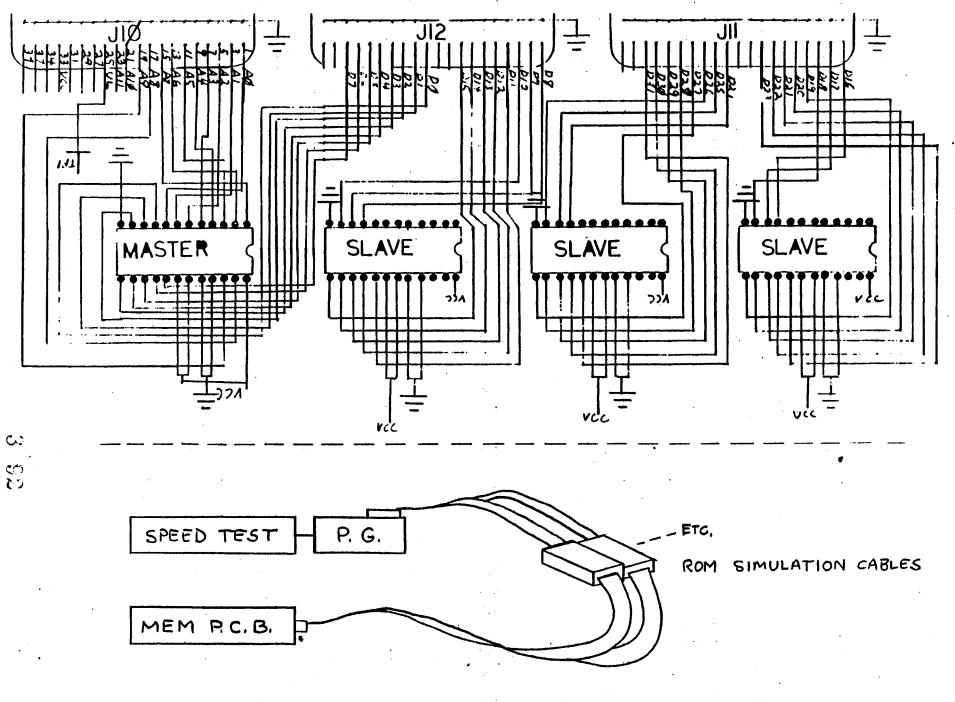

| ⊢ <b>⊸</b> | DUMP<br>DUMP instructs STEP-N that memory contents will be<br>transferred from STEP-N WCS to an external device.<br>The format picked is STEP's Microword <sup>TM</sup> format.<br>Other formats include ASCII HEX SPACE, BPNF, and<br>GENPROM. <sup>TM</sup> For a complete list of formats see<br>Section 2. <sup>5</sup> .                                                                                                                                                                                                                                                                                           | ENTER COMMAND<br>Format =<br>Start addr =                                                                                | DUMP (CR)<br>O (CR)<br>O (CR) (hex - like <u>all</u> data and<br>addresses)                                                                                                                                                     |