## PACIFIC ELECTRO DATA, INC

PACIFIC ELECTRO DATA

PED-4001

DATA ACQUISITION AND EMULATION MODULE

USER'S MANUAL

board design information

PACIFIC ELECTRO DATA, INC. 14 HUGHES STREET, B205 IRVINE, CA 92718 (714) 770-3244

#### HARDWARE WARRANTY

WARRANTY: Pacific Electro Data, Inc. ("PED")

warrants the PED-4001 Data Acquisition and

Emulation Module to be free of defects in

materials and workmanship for a period of one

year from the date of purchase. PED reserves

the right to make changes in the hardware

described herein without notice.

#### LIMITATIONS OF LIABILITY:

- A. The previous express warranty is the only warranty made by PED. PED grants no implied warranties, including warranties of merchantability or fitness and no other express warranties. The express obligation stated above is in lieu of all liabilities or obligations of PED for damages including, but not limited to, consequential damages arising out of or in connection with the delivery, use, or performance of PED test devices.

- B. The buyer further agrees that PED will not be liable for any lost profits or for any claim or demand against the buyer by any other party, except a claim for patent, copyright, and trademark infringement as provided herein.

- C. In no event will PED be liable for special, indirect, or consequential damages even if PED has been advised of the possibility of such damages. The risk of loss or damage for any products supplied by buyer to PED will be borne exclusively by the buyer.

### NOTICE

This test equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instructions in this manual, may cause interference to radio communications. Operation of this test equipment may cause interference in which case the user at his own expense will be required to take whatever measures required to correct the interference.

#### INFORMATION TO USER

If this equipment does cause interference to radio or television reception which can be determined by turning the equipment on and off, the user is encouraged to try to correct the interference by one or more of the following measures:

- o reorient the receiving antenna

- o relocate the computer with respect to the receiver

- o move the computer away from the receiver

- o plug the computer into a different outlet so that the computer and receiver are on different circuits.

If necessary, the user should consult the dealer or experienced radio/television technician for additional suggestions. The user may find the following booklet prepared by the Federal Communications Commission helpful:

"How to Identify and Resolve Radio and Television Interference Problems"

This booklet is available from the U.S. Government Printing Office, Washington, D.C. 20402, Stock Number 004-000-0345-4.

This manual is for information purposes only and is subject to change without notice. Pacific Electro Data, Inc. assumes no responsibility for any errors which may appear in the manual.

IBM and IBM PC are registered trademarks of International Business Machines Corporation.

# TABLE OF CONTENTS

| SECTION 1. GENERAL OVERVIEW                        |   |   |   | 1          |

|----------------------------------------------------|---|---|---|------------|

| 1.1 BRIEF DESCRIPTION                              |   |   |   | 1          |

| 1.2 PURPOSE and SCOPE                              |   |   |   | 1          |

| 1.3 DOCUMENTATION                                  |   |   |   | 2          |

|                                                    |   |   |   |            |

| SECTION 2. PRINCIPALS OF PASSIVE STATE ANALYSIS    | _ | _ | _ | <b>5</b> 3 |

| 2.1 TRANSITION TIME STATE RECORDING                |   |   |   | Š,         |

| 2.2 STATE CHANGE QUALIFICATION                     |   |   |   | 6          |

| 2.3 TIME TAG                                       |   |   |   | 24         |

| 2.3.1 Data Word                                    | • | • | • | <b>9</b> 4 |

| 2.3.2 Time Word                                    |   |   |   | 3)<br>- 3) |

|                                                    |   |   |   |            |

|                                                    | • | • | • | 2          |

| 2.5 SEQUENCE CONTROL PROGRAM                       | • | • | • | 4          |

| ARAMIAN 2 ANNONEOUS PROPERTIES                     |   |   |   |            |

| SECTION 3. FUNCTIONAL DESCRIPTION                  | • | • | • |            |

| 3.1 SCSI BUS and EXTERNAL INPUTS DATA LATCHES      |   |   |   | 10         |

| 3.2 ACQUISITION MEMORY AND DATA MULTIPLEXER        |   |   |   |            |

| 3.3 CHANGE COMPARE LOGIC AND QUALIFIER MEMORY      | • | • | • | 1          |

| 3.4 STATE MASK MEMORY AND COMPARE LOGIC            |   |   | • | 12         |

| 3.5 COUNTER LOGIC                                  | • |   | • | 13         |

| 3.6 TIMER LOGIC                                    |   |   |   | 14         |

| 3.7 SEQUENCE CONTROL MEMORY and LOGIC              |   | • |   | 14         |

| 3.7.1 Sequence Control Memory                      |   |   |   | 14         |

| 3.7.2 Sequence Control Logic                       |   | _ |   | 15         |

| 3.7.2.1 Acquisition Memory Control                 |   | - |   | 15         |

| 3.7.2.2 Next-Address and Counter Control           | i |   |   | 18         |

| 3.8 SCSI PROTOCOL CONTROL (SPO) LOGIC              |   | • | • | 19         |

| 3 8 1 Data Registers                               | • | • | • | 20         |

| 3.8.1 Data Registers                               | • | • | • | 20         |

| 3 9 3 Mode Pagister                                | • | • | • | 22         |

| 3.8.3 Mode Register                                | • | • | • | 24         |

| 3.8.5 Current SCSI Bus Status                      | • | • | • | 25         |

|                                                    |   |   |   |            |

| 3.8.6 Select Enable Register                       | • | • | • | 28         |

| 3.8.7 Bus and Status Register                      | • | • | • | 28         |

| 3.8.8 DMA Registers                                | • | • | • | 28         |

| 3.8.9 Interrupts                                   | • | • | • | 28         |

| 3.8.10 Data Transfers                              | • | • | • | 31         |

| 3.9 HOST INTERFACE, LOAD and CLOCK CONTROL LOGIC   |   | • | • | 32         |

|                                                    |   |   |   |            |

| APPENDIX A. MODULE ASSEMBLY                        |   |   |   |            |

| APPENDIX B. MODULE PARTS LIST                      |   |   |   |            |

| APPENDIX C. GLOSSARY OF KEY STATE ANALYZER SIGNALS |   | • |   | C-1        |

| ADDRIGHT D. DED AGGA CONTRADERS                    |   |   |   | n 1        |

# LIST OF TABLES

| Table 1          | . :        | 32-Bit Data Word Format                         | . 6  |

|------------------|------------|-------------------------------------------------|------|

| Table 2          | 2. 1       | Time Word                                       | . 7  |

| Table 3          | 3. (       | Change Compare Logic Truth Table                | . 12 |

| Table 4          | ١. ٤       | SCSI Bus Input DDn                              | . 13 |

| Table 5          | 5. 5       | State Mask Logic Truth Table for Bit n          | . 13 |

| Table 6          | i. S       | SCSI and EXTERN Input, DDn                      | . 14 |

| Table 7          | '. '       | "Next Address" Control Signal Logic             | . 19 |

| Table 8          | 3. 5       | 5380 Registers                                  | . 20 |

| Table 9          | ). 5       | SCSI Information Transfer Phases                | . 25 |

| Table 1          | .0. 1      | Interrupt Select Jumpers                        |      |

| Table 1          |            | 5380 DMA Select Jumpers                         |      |

| Table 1          | .2. h      | Module I/O Address Define Constants             | . 31 |

| Table 1          |            | Register/RAM Timed Strobes                      | . 34 |

| Table 1          | .4.        | /MSKSTB Outputs                                 | . 34 |

| Table 1          | .5. /      | /AMISTB Outputs                                 | . 34 |

| Table 1          | .6. /      | /QALSTB Outputs                                 | . 35 |

| Table B          | 3-1. I     | Parts List                                      | B-1  |

| Table C          | :-1. (     | Glossary of Key Signals                         | C-1  |

|                  |            |                                                 |      |

|                  |            | LIST OF FIGURES                                 |      |

|                  |            |                                                 |      |

|                  | N-         |                                                 |      |

| Figure           |            | Data Analysis Module Functional Block Diagram.  |      |

| Figure           |            | Acquisition Memory Data/Timer Write Timing.     |      |

| Figure           |            | Sequence Controller "Next Address" Logic Timing |      |

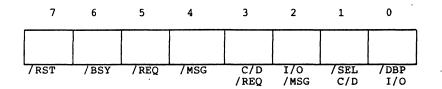

| Figure<br>Figure |            | Target Command Register                         |      |

|                  |            | Current Bus Status Register                     |      |

| Figure<br>Figure |            | Set Enable Register                             |      |

| rigure           | <i>'</i> . | bumper brock Locations on the module            | . 30 |

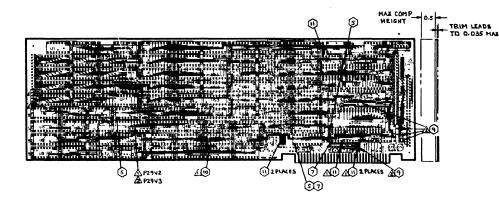

| Figure           | A-1.       | PED-4001 Module Assembly                        | A-1  |

#### SECTION 1. GENERAL OVERVIEW

#### 1.1 BRIEF DESCRIPTION

The PED-4001 Small Computer System Interface (SCSI) State and Emulation module is a high-performance 'third party' state analyzer and SCSI controller developed specifically to support the Small Computer System Interface. The module occupies a single, full-length expansion slot of a PC or compatible and attaches to the SCSI bus via a 50 pin connector.

The module is a passive observer of bus activity during state analysis. Captured state vectors are stored in a high-speed, 2048-word acquisition memory. Each state vector includes the binary state of the 18 SCSI signals, 5 external signals and elapsed time from previous state vector capture. State vectors are written to memory only at specific state changes as defined by 16 edge qualifiers. The capture process is controlled by high-speed, user-programmable sequence control logic, 16-state masks and four 16-bit counters.

Emulation of a SCSI initiator or target device is done using an LSI SCSI protocol controller, and the host PC memory and DMA controller:

### 1.2 PURPOSE and SCOPE

This document describes the hardware design and operating characteristics of the PED-4001 module. It is intended for hardware and software designers, programmers, engineers and interested persons who need to understand the hardware and operation of the module. Readers should understand the concepts of logic design and controller programming. Familiarity with the IBM PC and the Small Computer System Interface is desirable.

This document contains the latest information available at the time of publication. Every effort has been made to ensure its accuracy. However, PED cannot be responsible for inadvertent errors and reserves the right to modify the contents at any time.

#### 1.3 DOCUMENTATION

The following documents contain information the reader might find helpful in understanding the module.

Intel Component Data Catalog, Intel Corporation, Santa Clara, CA.

IBM Personal Computer Hardware Technical Reference Manual, IBM Corporation, Boca Raton, FL.

The TTL Data Book, Vol. 1, 2 and 3, Texas Instruments, Dallas, TX.

Programmable Logic Handbook, Monolithic Memories, Santa Clara, CA.

NCR 5380 SCSI Interface Chip Design Manual, NCR Corporation,

BSR X3.131-1986 Small Computer System Interface,

American National Standards Institute

### 1.4 NOTATION

The following symbols, abbreviations, and notations are used throughout this manual.

Parentheses () indicate an acronym or technical equivalent for the term preceding it. For example, "ACK (port 2, bit 1)" means that the signal ACK is assigned to bit 1 of port 2.

Square Brackets [] indicate that the preceding signal or part has a number of lines or signals comprising it. For instance, "DB[7-0]" means that the data bus DB is comprised of eight different signals ranging from DB7 through DB0.

Forward Slash / preceding an acronym indicates this is a signal that is at a low voltage when in its active, asserted state. An exception to this are the signals "C/D" and "I/O" where the initial signal prefix / has usually been excluded to avoid confusion.

#### SECTION 2. PRINCIPALS OF PASSIVE STATE ANALYSIS

The module acts as a passive 'third-party' observer during analysis operations. Captured data is stored in the 2048 word acquisition memory during state analysis. A captured state vector is made up of the 18 SCSI signals, 5 external signals and a 8- or 32-bit time tag.

The on-board timer is incremented every 100 nsec by the 10 MHz clock. Transition time state recording writes a state vector into acquisition memory, including a record of elapsed time from the previous write during specific state changes. This technique greatly conserves acquisition memory space while maintaining a constant time resolution of 100 nsec.

Saved state times are determined by 16 edge qualifiers. Either or both edges of the 18 SCSI signals can be selected in combination in each edge qualifier. The capture sequence is controlled by the acquisition program, the 16 state masks and four 16-bit counters in response to events occurring on the SCSI and external inputs.

This section describes in detail operating features of the PED-4001 module used to maximize its effectiveness in passive state analysis.

### 2.1 TRANSITION TIME STATE RECORDING

Most high-speed timing analyzers store samples of data at a selectable but fixed clock rate, with each sample using one word of the analyzer's total depth of the acquisition memory. At the high sampling frequencies necessary for good time resolution, several consecutive memory locations are often filled with the same information. Transition Time State Recording stores a new data sample only when there is a change. Along with the new data sample, a time tag is stored providing a measure of the time elapsed from the previous sample.

In operation, state data is sampled every 100 nanoseconds. Each sample is compared with the previous sample. If they are identical, the 32-bit timer is incremented. If they are different, the counter's value and the latest state data is stored into memory and the counter is reset to zero.

This method allows recording short bursts of activity separated by long intervals of inactivity, which parallels the operation of many electro-mechanical peripherals using the SCSI protocol.

## 2.2 STATE CHANGE QUALIFICATION

Even with efficient transition time state recording, capturing each state change of the 18 SCSI bus signals can rapidly fill the memory with superfluous data. It is desirable, therefore, to save only states involving the change of key "clock" (time significant) signals.

The SCSI has no single clock signal. While in an asynchronous information phase, information bytes are transferred across the SCSI bus using the two handshake semaphore signals request (REQ) and acknowledge (ACK). While in a synchronous data transfer phase, data bytes are transferred with a single "clock": REQ during a DATA IN phase and ACK during a DATA OUT phase. During the non-information phases, BUS-FREE, ARBITRATION, and (RE) SELECTION, or during the RESET condition, individual bus control signals have both state and timing significance. Examples of such signals are reset (RST), busy (BSY), and select (SEL). Even the individual data bits, D7 through D0, have time significance as the SCSI device ID during the ARBITRATION process.

To cope with the variety of situations outlined above, the analyzer has the ability to specify the edge of the SCSI signal to be used as a "clock" in capturing state data. The analyzer can use the rising edge, the falling edge or both edges of the eighteen SCSI bus signals in any combination as qualifying edges.

### 2.3 TIME TAG

The time tag is attached to each new state vector in the acquisition memory. The time tag contains the count in 100 nanosecond increments occurring between that state and the previous state vector. The time tag can be attached to the state data either horizontally, by extending the width of memory, or vertically, by extending the depth and bandwidth of the memory. Both methods are inefficient but at opposite ends of the frequency range. With horizontal attachment, considerable width must be added to handle the case of widely separated events. With vertical attachment, the memory bandwidth must be at least twice the maximum data capture rate. To overcome this inefficiency, the PED-4001 uses a combination of horizontal and vertical packing.

#### 2.3.1 Data Word

Appended to the state data fields of each acquisition memory word is an eight-bit time field. This horizontal attachment of time information is sufficient to save up to 256 counts, or 25.6 microseconds of time, between consecutive events.

The format of this 32-bit DATA WORD is illustrated below with a definition of each bit of the 32-bit word.

DATA WORD bits 31 through 00 3 3222222 21111 00000000 2 1 1 1 1 0 0 09876543 2 09876 4 3 2 9 76543210 1 1 0 TTTTTTTT R EEEEE В S Α М С DDDDDDDDD, D Ι R Α 0 65432107 S Т 76543210 S Ρ 43210 E S / E С Т EXTRN Y L N G D 0 K DATA TIME 0

Table 1. 32-Bit Data Word Format.

## where the bit assignment is as follows:

0: Always '0' to identify the memory word as a DATA word.

TIME: Least significant byte of time with a bias of

minus 1. (Zero value implies +1 count). Note that the most significant bit of the time byte (T7) is assigned as

DATA word bit 23.

RST: SCSI control signal RST.

DP: Parity bit of the SCSI data byte signals (ninth data bit).

EXTRN: Five external input bits EX4 through EX0.

BSY: SCSI control signal Busy

SEL: SCSI control signal Select

ATN: SCSI control signal Attention

MSG: SCSI phase control bit Message

C/D: SCSI phase control bit Command/Data

I/O: SCSI phase control bit Input/Output

REQ: SCSI data Request strobe

ACK: SCSI data Acknowledge strobe

DATA: 8 bit SCSI data byte, excluding parity bit

(bits D7 through D0).

#### :.3.2 Time Word

he eight-bit time field of the DATA word overflows after 56 counts. If two consecutive events are separated by more han the 25.6 microseconds, a second word of the acquisition emory is used to store the upper 24 bits of a 32-bit time ord. This second word is formatted as illustrated below.

Table 2. Time Word.

| TIME                     | WORD bits 31 through 00                              |

|--------------------------|------------------------------------------------------|

| 33222222<br>10987654     | 222211111111110000000000<br>321098765432109876543210 |

| 11111111<br>TIME<br>FLAG | TTTTTTTTTTTTTTTTTTTTTTTTTTTTTTTTTTTTTT               |

there the bits are assigned as follows:

IME FLAG: an eight bit field of all '1's identifying

the memory word as a TIME word

JPPER TIME: most significant three bytes (24 bits) of time (T31 through T08). Upper time byte

field is biased by a minus 256. A value of

zero represents 256 counts or 25.6

microseconds.

### 2.4 INDEX OPERATION

The Index operation allows the user to save time and state lata around some key Index event. The operation is analogous to the pre-/post-trigger counter and trigger mask operation of the universal logic analyzer. As in a logic analyzer, the capture operation is halted after a specified number of writes to the acquisition memory following the Index, thereby protecting saved lata on either side of the Index.

When the analyzer is capturing data, time and state information is written into the Acquisition Memory, starting at address 000. At each write, the memory address register is incremented by 1. The total Acquisition Memory is 2048 words in length.

After data is written into word 2047, the address returns to the beginning of the memory space and the next data is written into address 000, writing over what was previously stored in memory. This overwriting process continues with the 2048 words most recently written to residing in memory.

The Index operation controls the capture process using the following procedure. The Index command loads the Index counter with the Index count value, from 1 to 2047 and forces a state vector write to the acquisition memory. In addition, the Index command causes the Index counter to increment after every write to the Acquisition Memory. When the counter reaches the maximum count of 2048, the capture operation is automatically stopped. The analyzer can be re-indexed any number of times before automatically stopping. Re-indexing causes the analyzer to reset the Index counter to its initial value.

## 2.5 SEQUENCE CONTROL PROGRAM

The state capture process is controlled by the sequence control program in the 32-byte acquisition program memory. The program consists of one- or two-byte commands. All one-byte commands execute in one system clock period (100 nsec) while all two-byte commands execute in two system clock periods (200 nsec). The commands can be broadly categorized into two groups: operation commands and flow-control commands. The majority of the commands fall into the latter group.

The operation commands are: Save, Skip, Sync, Index and NoOp. The Save command puts the analyzer in a state capture mode, saving all new states entered as the result of a state change qualified by the selected edge qualifier. The Skip command suspends the state capture mode until it is invoked again by another Save command. The Sync command causes a 100 nsec. pulse at the SYNC signal output. The Index operation was described in detail in section 2.4. The Index command initiates the Index process. The NoOp command is a "do-nothing" command.

The flow-control commands are made up of several conditional jump commands plus Load Counter commands. The Load Counter command is used to initialize one of the three general purpose 16-bit event counters. The Index command is a special case of the Load Counter command involving the Index counter, CO, which is dedicated to the Index operation.

Two conditional jump commands are of the "increment counter and test for end-count" type, allowing jumps conditioned on whether or not one of three counters has reached its end-count. Two other conditional jump commands allow testing the present state input against one of sixteen state masks and make the jump whether or not there is a match between the two. If the condition for the jump is met, the next command is accessed from the jump-to address of the program contained in the command. If the condition is not met, the next command is accessed from the next consecutive address. There is also an unconditional jump command which always accesses the next command from the jump-to address.

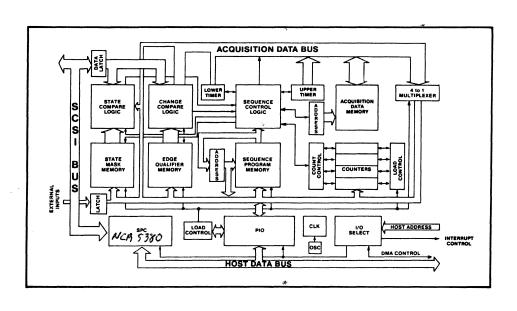

## SECTION 3. FUNCTIONAL DESCRIPTION

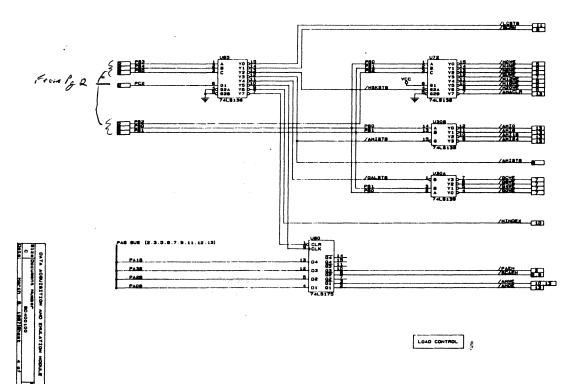

A functional block diagram of the PED-4001 module is shown in Figure 1. The logic design and operation of each functional block is described in the following paragraphs. The circuitry making up each block is identified by component reference designation and schematic sheet number (refer to Appendix D).

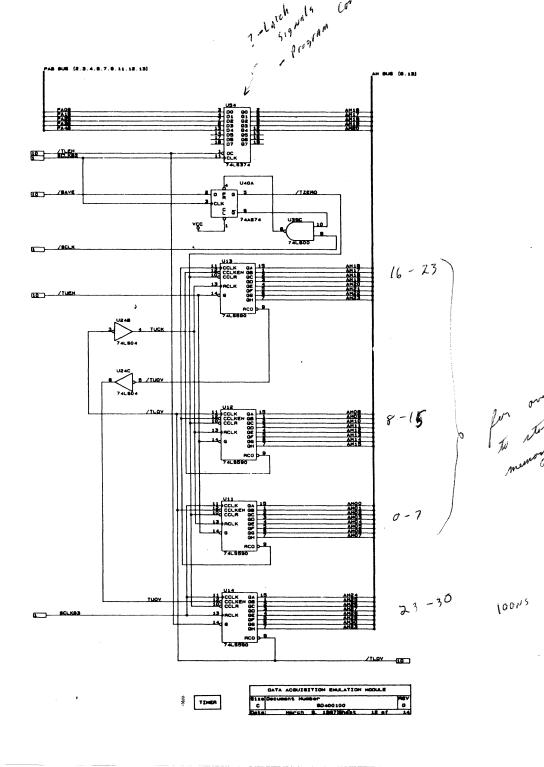

## 3.1 SCSI BUS and EXTERNAL INPUTS DATA LATCHES

Schematic sheet 14 is of the sampled data latch for the SCSI bus signals and of the external inputs buffer. The "wire-OR" for each of the 18 SCSI signals from the J2 and J3 connectors are sampled every 100 nsec and saved in three 74LS174 Hex D-type Flip Flops, U91 through U93. Each IC is clocked by the buffered system clock SCLK1B. The external inputs from the J1 connector are buffered by the 74LS365 Hex Three-state Buffer, U90. The buffered outputs are enabled to the PA[4-0] bus with the signal /EXTENT The SYNC output to J1-2 is also from U90.

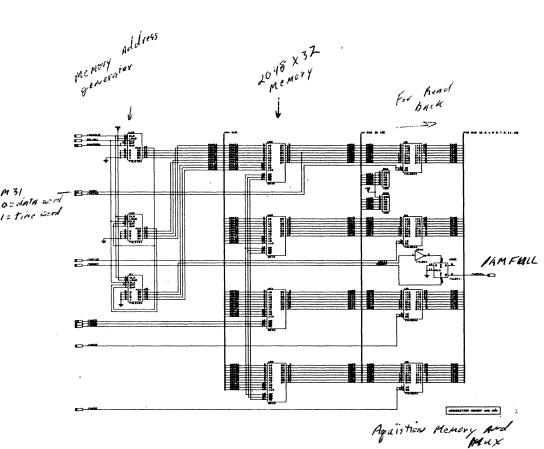

### 3.2 ACQUISITION MEMORY AND DATA MULTIPLEXER

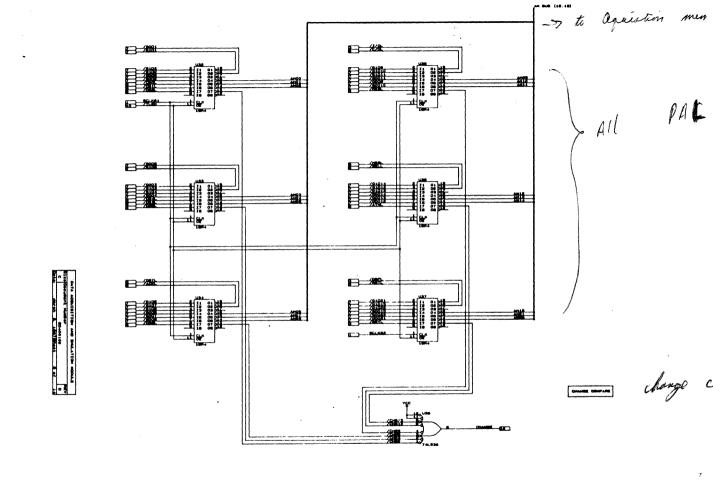

Sheet 13 of the schematic shows the acquisition memory and data multiplexer logic. The 2048-word-by-32-bit acquisition memory is implemented with four TMM2018D 2048x8 static RAM NMOS ICs, U20 through U23, each connected as 8 bits of the 32-bit wide acquisition data bus. A common output enable, /AMOE, write enable, /AMWE, and chip select, /AMCS, drive the four RAM devices.

Three TTL 74LS161 4-bit synchronous counters, U1, U10, U19, are cascaded to form the 11-bit acquisition memory address register. The register is cleared to zero with /AMACLR. The register is incremented each time a data word or a time word is written to memory by AMACKEN and SCLKB1. The counter rolls over from address 2047 to 0000. The twelfth bit is used to set a RS latch AMFULL, U88B and U24A, to signify that all addresses of the memory have been written to at least once.

Four 74LS244 octal buffers, U2 through U5, are used to multiplex the 32-bit acquisition memory bus (AM[31-00]) down to the 8-bit PA[]B bus, readable by the host PC. The buffer outputs are individually enabled by /AMI0, /AMI8, /AMI16 and /AMI24.

Figure

Data

Analysis

Module

Functional

Block Diagram.

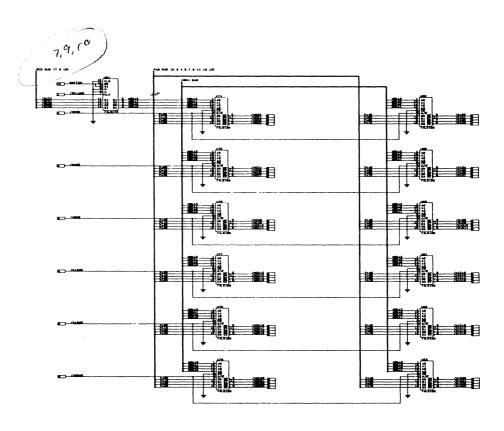

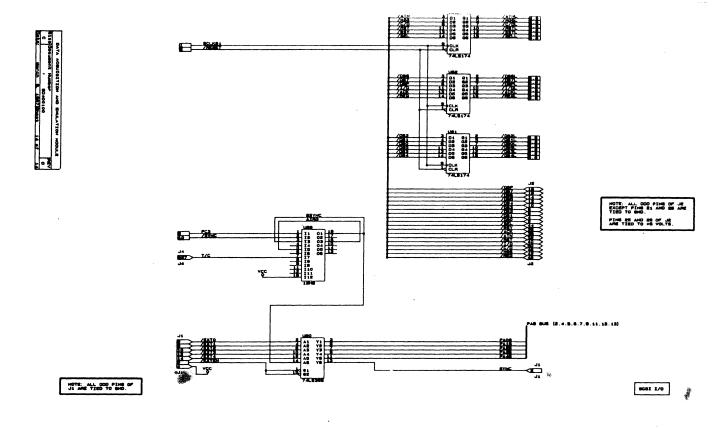

## 3.3 CHANGE COMPARE LOGIC AND QUALIFIER MEMORY

The sixteen-word-by-36-bit edge qualifier memory is diagrammed on schematic sheet 7. The edge qualifier memory is implemented with nine 74LS189 16x4 static RAM ICs, U41 through U44 and U49 through U53. A 74LS376 transparent latch contains the address of the edge qualifier selected by /SAVEN. The latch is driven by the sequence controller data bits 3 through 0 (SCD3-SCD0)\* Two bits of the edge qualifier memory (/Q1Dn and /Q0Dn) are used to identify either the rising, falling, both or neither edges of each of the eighteen SCSI bus signals resulting in a qualified state change.

The change compare logic is on sheet 8 of the schematic. Six PAL16R4 ICs, U32 through U37, and a 74S30 NAND gate implement the change compare logic. The truth table of the compare logic for a single SCSI bus signal is provided below. In the table "n" takes all consecutive values from 0 to 15 plus 21 and 22. Q1Dn and Q0Dm are two bits from the edge qualifier memory corresponding to signal "n". DDn represents the present sampled state of the input signal "n". The name of the input signal assigned each value of "n" is listed in Table 3. Amn is the previous state sampled for the same input. If the change compare logic output CHNG is "1" for one or more of the eighteen SCSI signals and save-enable (SAVEN) is TRUE, the present sampled state will be written to the acquisition memory after being latched into the AM register, U31 through U37.

Table 3. Change Compare Logic Truth Table

|   | eng grave | 701 6506 |     | da    | to on |  |

|---|-----------|----------|-----|-------|-------|--|

|   | Q1Dn      | Q0Dn     | AMn | DDn " | CHNG  |  |

| Γ | 0         | 0        | х   | х     | 0     |  |

| 1 | 0         | 1        | 0   | X     | 0     |  |

| 1 | 0         | 1        | 1   | 1     | 0     |  |

| 1 | 0         | 1        | 1   | 0     | 1     |  |

| 1 | 1         | 0        | 1   | Х     | 0     |  |

|   | 1         | 0        | 0   | 0     | 0     |  |

| 1 | 1         | 0        | 0   | 1     | 1     |  |

| 1 | . 1       | 1        | 0   | 0     | 0     |  |

| 1 | 1         | 1        | 0   | 1     | 1     |  |

| 1 | 1         | 1        | 1   | 0     | 1     |  |

| 1 | 1         | 1        | 1   | 1     | 0     |  |

|   |           |          |     |       |       |  |

for n from 0 to 15, 21 and 22. where X signifies "don't care."

Table 4. SCSI Bus Input DDn.

| DDn | Input  | DDn | Input | DDn | Input |

|-----|--------|-----|-------|-----|-------|

| 0   | DB0L   | 6\  | DB6L  | 12  | MSGL  |

| 1   | DB1L · | 7   | DB7L  | 13  | ANTL  |

| 2   | DB2L   | 8   | ACKL  | 14  | SELL  |

| 3   | DB3L   | 9   | REQL  | 15  | BSYL  |

| 4   | DB4L   | 10  | I/OL  | 21  | DBPL  |

| 5   | DB5L   | 11  | C/DL  | 22  | RSTL  |

#### 3.4 STATE MASK MEMORY AND COMPARE LOGIC \*\*

Sixteen state mask words are stored in the state mask memory implemented with 12 74LS189A 16x4 RAM ICs, U58 through U63 and U74 through U79, as illustrated on sheet 5 of the schematic. The 74LS173 Quad Latch, U64, is loaded from SCD[3-0] with the 4-bit address of the selected state mask stored in the 74LS189 RAMs. Each state mask is 48 bits long, with two bits (/MODn and /M1Dn) assigned to each of the 18 SCSI signal, 5 buffered PA bus lines (PA[4-0]B) and a data parity odd/even signal (PEVEN).

The state compare logic, given on sheet 6 of the schematic, is implemented using five PAL16C1 ICs, U65 through U70, a 74S280 9-input comparator and a 74S30 8-input NAND gate. A truth table for a single bit 'n' of the state mask logic is shown in Table 5. Table 6 pairs each of the 24 input signals, DDO through DD23, with the specific analyzer signal. For a state mask compare operation to be TRUE all 24 MTCH outputs must be '1'.

Table 5. State Mask Logic Truth Table for Bit n.

| M1Dn                  | . <del>M</del> ODn    | DDn                        | мтсн                  |

|-----------------------|-----------------------|----------------------------|-----------------------|

| 0<br>0<br>0<br>1<br>1 | 0<br>1<br>1<br>0<br>0 | X<br>0<br>1<br>0<br>1<br>X | 0<br>1<br>0<br>0<br>1 |

for n from 0 to 23 and where X signifies "don't care."

Table 6. SCSI and EXTERN Input, DDn.

|   | DDn 0 1 2 3 4 5 | DBOL<br>DB1L<br>DB2L<br>DB3L<br>DB4L<br>DB5L<br>DB6L | DDn  8 9 10 11 12 13 | ACKL<br>REQL<br>I/OL<br>C/DL<br>MSGL<br>ATNL<br>SELL | DDn  16 17 18 19 20 21 22 | PAOB<br>PA1B<br>PA2B<br>PA3B<br>PA4B<br>DBPL<br>RSTL | Exter<br>Sisse |

|---|-----------------|------------------------------------------------------|----------------------|------------------------------------------------------|---------------------------|------------------------------------------------------|----------------|

|   | 5               | DB5L                                                 | 13                   | ATNL                                                 | 21                        | DBPL                                                 | ŀ              |

| ĺ | 6               | DB6L                                                 | 14                   | SELL                                                 | 22                        | RSTL                                                 |                |

|   | 7               | DB7L                                                 | 15                   | BSYL                                                 | 23                        | PEVEN                                                |                |

| į |                 |                                                      |                      |                                                      |                           |                                                      | Į.             |

ے در 119

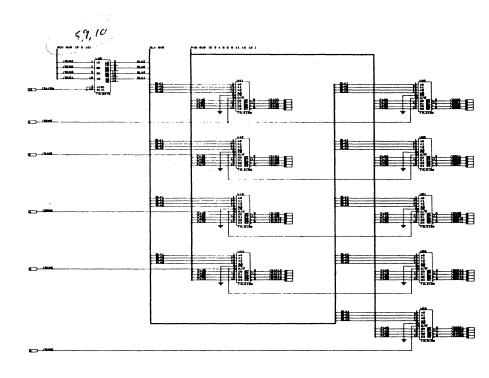

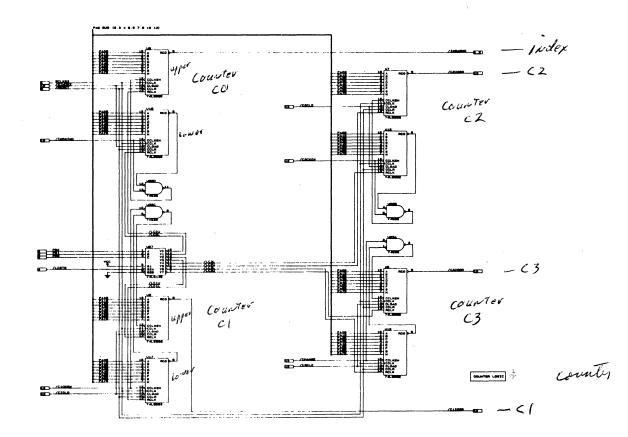

### 3.5 COUNTER LOGIC

The logic for the four 16-pit counters is shown on sheet 11 of the schematic. Each counter is implemented with two 74LS592 8-bit binary counters and one quarter of a 74S32 quad 2-input AND The 74LS592 consists of a parallel input, 8-bit storage register feeding an 8-bit binary counter. All storage registers are driven by the PA[7-0]B bus. Each of the eight 74LS592 storage register clocks are driven by an output of an 74LS138 1-of-8 demultiplexer which in turn is driven by PB[2-0] and /LCSTB. All storage registers and counters are cleared with /RESET. All counter clock inputs are driven by SCLKB2.

The counter load control of counter CO, the Index counter, consisting of U9, U18 and U25D, is driven by the signal /SINDEX. The counter increment enable is driven by /INDXINC. The signal /INDXEND becomes active low when the count reaches FF00H.

The load control of counter C1, consisting of U8, U17 and U25C, is driven by the signal /CICLD. Similarly, the load control of counters C2 and C3, consisting respectively of U7, U16, U6, U15, and sections A and B of U25, are driven by /C2CLD and /C3CLD respectively. The counter increment enables for C1 and C2 are driven by /C1CKEN and /C2CKEN. The counter increment enable for C3, the edge counter, is driven by /CHANGE. The signals /C1ZERO, /C2ZERO, and /C3ZERO go active low when the count of each associated counter, C1 through C3, reaches FF00h.

#### 3.6 TIMER LOGIC

The 32-bit timer is shown on sheet 12 of the schematic. It is implemented with four cascaded 74LS590 8-bit binary counters, U11 through U14. Each of these devices contain an 8-bit counter that feeds an 8-bit output register. A counter clear signal, /TZERO, common to all counter stages, is active each time a data word is written to the acquisition memory. TZERO is output from the latch-gate combination of U48A and U39C, sections of a 74LS74 D-type Flip Flop, and a 74LS00 NAND gate driven by the signal /SAVE.

At every occurrence of the buffered 10MHz system clock /SCLKB3, the contents of the lower stage counter, U14, are transferred to the output register and the counter itself is incremented by one. An occurrence of the overflow signal from the lowest stage, /TLOV, transfers the contents of the upper stage counters to the output registers and, 100 nsec later, the upper stage counter is incremented. At that same time, the contents of the upper stage output registers, U11-U13, are placed on the AM[23-00] bus with output enable signal /TUEN and written to acquisition memory.

If the upper stage were to reach the maximum count, the lower counter is inhibited, freezing the count at this maximum value. This is done by the signal TUOV.

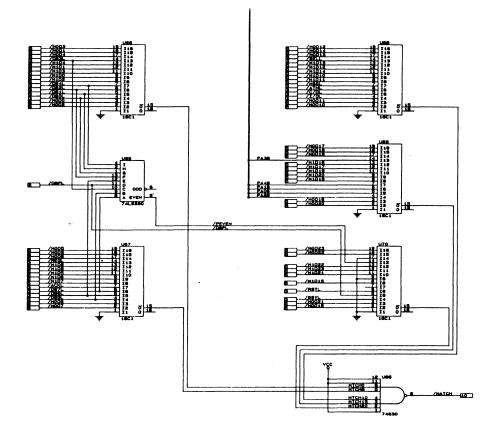

### 3.7 SEQUENCE CONTROL MEMORY and LOGIC

This section provides a description of all sequence control memory and logic operations performed by the PED-4001 module.

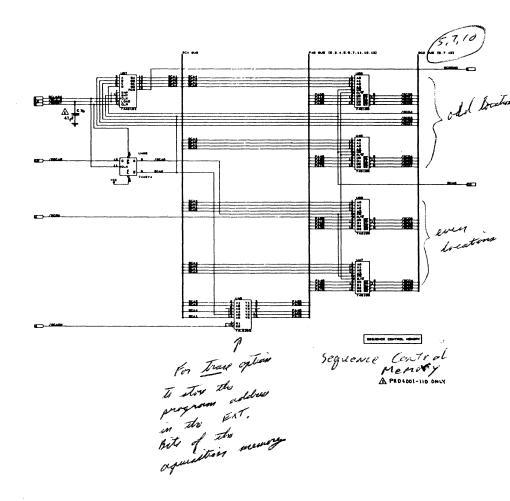

## 3.7.1 Sequence Control Memory

The logic diagram for the sequence control memory is on sheet 9 of the schematic. The memory is made up of four 74S189 16x4, inverted output RAMS, U46, U47, U55, and U56, organized as a 32-byte memory. Of the 32 bytes, only 29 are usable without restriction. The use of the first two bytes is restricted because of the possibility that the first operating clock period may be short. The last byte of RAM is not usable for reasons discussed in 3.7.2. The data inputs of each RAM is driven by a nibble of the PA[7-0]B bus. The write enable (/SCRW) signal is common to the four RAMS. The active low data outputs form the Sequence Controller Data bus, SCD[7-0].

A 74AS161 4-bit synchronous binary counter, U57, and a section of a 74AS74 D-type FF, U40B, are used for the 5-bit sequence controller address register. The D-type Flip Flop forms the least significant address bit with its Q output (SCAO) driving the chip selects of U46 and U55 and the increment enable input of U57 while the /Q output drives the chip selects of U47 and U56. The outputs of U57, SCA[4-1] drive the address inputs of the four RAMs. The address register is driven by the sequence controller memory outputs /SCD[4-0]\*

The state of the signal /SCALD controls the next address of the sequence controller; either the present address is incremented by one or the next address is specified by the inputs /SCD[4-0]. The output SCREND becomes active high when the address reaches 1Fh. SCREND immediately stops the system clock. This last memory location is not usable for program code.

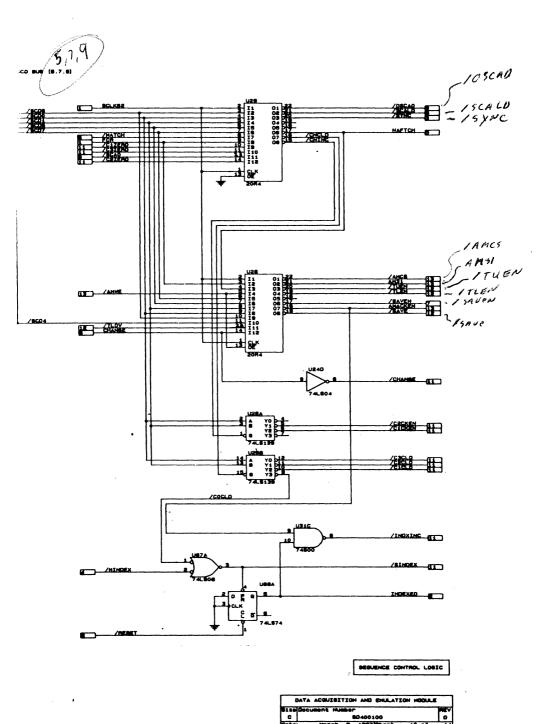

## 3.7.2 Sequence Control Logic

Sheet 10 of the schematic contains the sequence control logic. The core of the sequence control logic is implemented with two 20R4B PALs, U28 and U29. U28 is programmed to control the writing to the acquisition memory. It functions independently from the sequence controller "next address" and counter control logic which is implemented using U29 and a 74LS139 dual 1-of-4 demultiplexer, U26. Both U28 and U29 share as common inputs SCD \$7-5,1,0], FCR, and buffered system clock /SCLKB2.

### 3.7.2.1 Acquisition Memory Control

In addition to the inputs listed above, the signals /SCD4 /AMWE, and CHANGE are inputs to the acquisition memory controller, U28. The output signal /AMCS is the chip select for the acquisition memory. When this signal is active low, the memory is written to or read from memory depending on the states of /AMWE and /AMOE. If /AMWE is active low, /AMCS is active at each occurrence of /SAVE (see the discussion below) or at the overflow of the lower stage of the timer (/TLOV).

Output AM31 is the acquisition memory flag bit, identifying a data word if '0' or a time word if '1'. Active low outputs /TLEN and /TUEN serve to enable either the data word or the time word, respectively, to the acquisition memory bus, AM[30-0].

The save enable output signal, /SAVEN, is set active by the sequencer Save command and reset low by the Skip command. The /SAVEN signal is used internally by U28 as well as for clocking the edge qualifier address latch U46. The /SAVE signal is active each time a new data word is to be written

to the acquisition memory, because CHANGE occurs while SAVEN is active, an unconditional save is specified by an active /SCD4 /SCD4, or by the Index command. /SAVE is used by the timer logic.

The output signal /AMACKEN enables the incrementing of the acquisition memory address register.

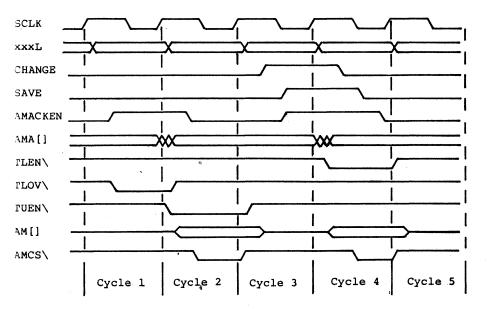

Figure 2. Acquisition Memory Data/Timer Write Timing.

Acquisition memory data and time word write timing is given in Figure 2. Five cycles of the 10 MHz system clock are shown with /AMWE and SAVEN assumed active. Cycle 1 occurs 256 SCLKs after a data write to acquisition memory, resulting in the assertion of /TLOV. Because this is the first lower-timer overflow (/TLOV) since a data word write, AMACKEN becomes active causing the AMA[] register to be incremented. /AMCS causes the write to acquisition memory in Cycle 2 with /TUEN enabling the time word to the AM[] bus. During Cycle 3 a qualified data CHANGE is detected which sets SAVE and AMACKEN followed in Cycle 4 with /TLEN and /AMCS. These signals enable the data word to the AM[] bus which is written to acquisition memory. No activity occurs during Cycle 5. Note that if Cycle 1 were not the first

overflow of the lower timer, AMACKEN would not be asserted and the AMA[] register would not be incremented. The new time word would be written over the old value during Cycle 2.

The only input to U28 not yet mentioned is the next address fetch signal, NAFTCH. This signal is only active when the "next address" is on the /SCD[] bus. U28 ignores the /SCD[] lines during NAFTCH.

## 3.7.2.2 Next-Address and Counter Control

The "next address" and counter logic of U29 and U26 have five inputs in addition to those common with U28. They will be identified in the following discussion of each U29 and U26 output.

NAFTCH was introduced in the discussion of U28. This output is active during the sequence control "next address" fetch cycle. Any sequencer command byte with a one as its MSB will be followed by a "next address" byte.

The signal /CNCLD, along with /SCD[1-0], drive U26B to generate counter load strobes /C1CLD, /C2CLD, and /C3CLD. These strobes cause the contents of the input register of C1 through C3 to be transferred to their respective counter. The fourth output of U26B (which occurs if the Index counter, C0, is selected) is OR'ed with the manual index signal (/MINDEX) to form /SINDEX. /SINDEX sets the INDEXED latch [U88A] and causes the contents of the input register of the Index counter to be transferred to the counter proper. The /CNCLD signal is generated whenever the Load Counter command (001ixxcc) is decoded by U29.

The signal /CNINC, along with /SCD[1-0], drives U26A to generate the counter increment enables /C1INC and /C2INC. These enables cause their respective counters to be incremented by one count. The /CNINC signal is generated by U29 whenever either the Jump Fero (100ixxcc) or Jump Not Zero (101ixxcc) commands are decoded. If INDEXED is TRUE, the signal /AMACKEN causes /INDXINC which increments the Index counter, C0.

The SYNC output of U29 is generated whenever the Sync command (000i0000) is decoded.

The last two outputs of U29 control the sequence control address register, SCA[]. The signals are /DSCAO and /SCALD. /DSCAO is the input to the D-type Flip Flop U40B whose outputs are SCAO and /SCAO. /SCALD controls the load/increment operation of the SCA[4-1] counter.

Table 7 provides a summary of the logic operation. In the table, (t) and (t+1) refer to the signal state at clock time "t" and the clock time immediately following. Note that the upper four bits of the "next address" byte, /SCD[4-1], are logically inverted. Therefore, bits 4 through 1 of the "next address" must be complemented prior to being written to the acquisition memory during program load.

Table 7. "Next Address" Control Signal Logic.

| COMMAND                                                                     | CONDITION | SCA0(t+1) | SCALD | SCA[4-1](t+1)       |

|-----------------------------------------------------------------------------|-----------|-----------|-------|---------------------|

| Jump Zero Jump Zero Jump Not Zero Jump Not Zero Jump On Match Jump No Match | CnZERO=1  | /SCAO(t)  | FALSE | SCA[4-1](t)+SCA0(t) |

|                                                                             | CnZERO=0  | SCDO      | TRUE  | /SCD[4-1]           |

|                                                                             | CnZERO=1  | SCDO      | TRUE  | /SCD[4-1]           |

|                                                                             | CnZERO=0  | /SCAO(t)  | FALSE | SCA[4-1](t)+SCA0(t) |

|                                                                             | MATCH=1   | SCDO      | TRUE  | /SCD[4-1]           |

|                                                                             | MATCH=0   | /SCAO(t)  | FALSE | SCA[4-1](t)+SCA0(t) |

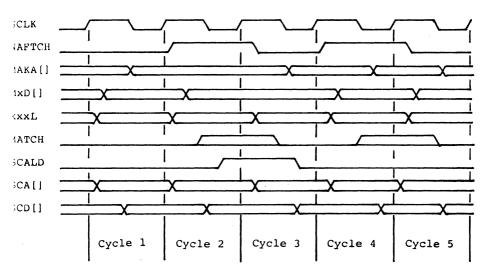

igure 3 is a signal timing diagram of the "next address" control ogic.

Figure 3. Sequence Controller "Next Address" Logic Timing.

Cycle 1 of the timing diagram depicts a jump command operation code access cycle. During this cycle, bits /SCD[3-0] are transferred to the MAKA[] register on the falling edge of SCLK. Cycle 2 is a "next address" access cycle, as identified by NAFTCH. During this cycle, the contents of the sampled input data latch (xxxL) is compared with the state mask memory output (MxD[]). This comparison logic generates the MATCH signal.

MATCH is tested per the operation code of the previous cycle and SCALD becomes active, causing SCD[4-0] to be transferred to the SCA[] register at the next SCLK (the beginning of Cycle 3). Cycle 3 represents conditional jump operation code access cycle in which the jump was not taken since no SCALD was generated.

### 3.8 SCSI PROTOCOL CONTROL (SPO) LOGIC

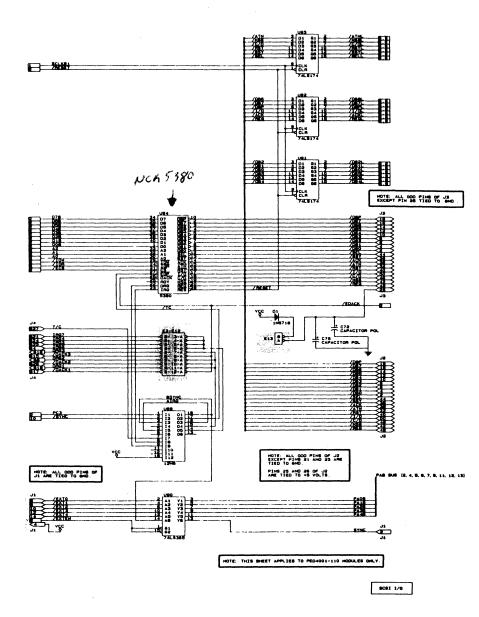

Sheet 3 of the schematics shows the NCR 5380 SCSI interface device, U94. This is a 40-pin NMOS device designed to accommodate the SCSI. The device operates in both initiator and target roles. It supports arbitration, including reselection. Special high-current open collector output devices, capable of sinking 48 mA at 0.5 V, allow for direct connection to the single-ended SCSI bus.

The NCR 5380 SCSI device appears as a set of eight registers to the host PC. By reading and writing the appropriate registers, the PC can initiate any SCSI bus activity or sample and assert any signal on the SCSI bus. This allows the user to implement all or parts of the SCSI protocol in software. Table 8 shows the 5380 possible registers, their addresses, and names.

|     | Addı | cess |      |                             |

|-----|------|------|------|-----------------------------|

| A 2 | A1   | A0   | Туре | Name                        |

| O   | 0    | 0    | R    | Current SCSI Data           |

| 0   | 0    | 0    | W    | Output Data                 |

| 0   | 0    | 1    | R/W  | Initiator Command           |

| 0   | 1    | 0    | R/W  | Mode                        |

| O   | 1    | 1    | R/W  | Target Command              |

| 1   | 0    | 0    | R    | Current SCSI Bus Status     |

| 1   | 0    | 0    | W    | Select Enable               |

| 1   | 0    | 1    | R    | Bus and Status              |

| 1   | 0    | 1    | W    | Start DMA Send              |

| 1   | 1    | 0    | R    | Input Data                  |

| 1   | 1    | 0    | W    | Start DMA Target Receive    |

| 1   | 1    | 1    | R    | Reset Parity/Interrupts     |

| 1   | 1    | 1    | W    | Start DMA Initiator Receive |

Table 8. 5380 Registers.

### 3.8.1 Data Registers

Three data registers are used to transfer SCSI commands, data, status, and message bytes between the host PC data bus and the SCSI bus. The current SCSI data register is a read-only register allowing the PC to read the active SCSI data bus. If parity checking is enabled, the SCSI bus parity is checked at the beginning of the read cycle. This register is used during a programmed I/O data read or during arbitration to check for higher priority arbitrating devices. Parity is not guaranteed during arbitration.

The Output Data Register is a write-only register used to send data to the SCSI bus, either using a normal I/O write, or under DMA control. This register is also used to assert the proper ID bits or the SCSI bus during the arbitration and selection phases.

The Input Data Register is a read-only register used to read latched data from the SCSI bus. Data is latched either during a DMA Target receive operation when /ACK goes active, or during a DMA Initiator receive when /REQ goes active. The DMA Mode bit (port 2, bit 1) must be set before data can be latched in the Input Data Register. This register may be read under DMA control. Parity is optionally checked when the Input Data Register is loaded.

### 3.8.2 Initiator Command Register

The Initiator Command Register is a read/write register used to assert certain SCSI bus signals, to monitor those signals, and to monitor the progress of bus arbitration. Many of these bits are significant only when being used as an Initiator; however, most can be used during Target operation.

The following discussion explains all bits used in the Initiator Command Register.

### Bit 7 ASSERT /RST

Whenever a one is written to bit 7 of the Initiator Command Register, the /RST signal (pin 16) is asserted on the SCSI bus. The /RST signal will remain asserted until this bit is reset or until an external /RESET (pin 28) occurs. After this bit is set to one, IRQ (pin 23) goes active and all internal logic and control registers are reset (except for the interrupt latch and the ASSERT /RST bit). Writing a zero to bit 7 de-asserts the /RST signal. Reading this register simply reflects the status of the bit.

## BIT 6 AIP (Arbitration in Progress - read bit)

This bit is used to determine if arbitration is in progress. For this bit to be active, the ARBITRATE bit (port 2, bit 0) must have been set previously. It indicates that a bus free condition has been detected, the chip has asserted BSY (pin 13), and the contents of the Output Data Register (port 0) are on the SCSI bus. AIP remains active until the ARBITRATE bit is reset.

### BIT 6 TEST MODE (write bit)

This bit may be written during a test to disable all output drivers, effectively removing the 5380 from the circuit. Resetting this bit returns the part to normal operation.

### BIT 5 LA (Lost Arbitration - read bit)

When active this bit indicates the 5380 has detected a bus free condition, has arbitrated for use of the bus by asserting /BSY (pin 13), placed its ID on the data bus, and lost arbitration due to assertion of /SEL (pin 12) by another bus device. For this bit to be active, the ARBITRATE bit (port 2, bit 0) must be active.

### BIT 4 ASSERT / ACK

This bit is used by the bus initiator to assert /ACK (pin 14) on the SCSI bus. In order to assert /ACK, the TARGETMODE bit (port 2, bit 6) must be false. Writing a zero to this bit resets /ACK on the SCSI bus. Reading this register simply reflects the status of the bit.

### BIT 3 ASSERT /BSY

Writing a one into this bit position asserts /BSY (pin 13) onto the SCSI bus. Conversely, a zero resets the /BSY signal. Asserting /BSY indicates a successful select or reselection has taken place and resetting this bit creates a bus disconnect condition. Reading this register simply reflects the status of this pit.

### BIT 2 ASSERT /SEL

Writing a one into this bit position asserts /SEL (pin 12) onto the SCSI bus. /SEL is normally asserted after arbitration is completed. /SEL may be de-asserted by resetting this bit to zero. A read of this register simply reflects the status of the bit.

#### BIT 1 ASSERT /ATN

/ATN (pin 15) may be asserted on the SCSI bus by setting this bit to a one if the TARGETMODE bit (port 2, bit 6) is false. /ATN is normally asserted by the initiator to request a Message Out bus phase. Since ASSERT /SEL and ASSERT /ATN are located in the same register, a select with /ATN can be implemented with one MPU write. /ATN can be de-asserted by resetting this bit to zero. A read of this register simply reflects the status of the bit.

### BIT 0 ASSERT DATA BUS

When set, the ASSERT DATA BUS bit enables the contents of the Output Data Register as chip outputs on the signals DB[0-7]. Parity is also generated and asserted on DBP.

When connected as an Initiator, the outputs are only enabled if the TARGETMODE bit (port 2, bit 6) is false, the received signal I/O (pin 17) is false, and the phase signals (C/D, I/O, and MSG) match the contents of the ASSERT C/D, ASSERT I/O, and ASSERT MSG in the Target Command Register.

This bit should also be set during DMA send operations.

### 3.8.3 Mode Register

The Mode Register is used to control the operation of the 5380. This register determines whether the chip operates as an initiator or target, whether DMA transfers are being used, whether parity is checked, and whether interrupts are generated on various external conditions. This register may be read to check the value of these internal control bits.

The following discussion explains the operation of these control bits.

## BIT 7 BLOCK MODE DMA

The BLOCK MODE DMA bit controls the characteristics of the DMA DRQ/DACK handshake. This bit must be reset (0) when the DMA MODE bit is active (1). The DMA handshake uses the normal interlocked handshake and the rising edge of /DACK (pin 26) indicating the end of each byte being transferred.

### BIT 6 TARGETMODE

The TARGETMODE bit allows the 5380 to operate as either an SCSI bus initiator, when the bit is reset (0), or as an SCSI bus target device, when the bit is set (1). In order for the signals /ATN (pin 15) and /ACK (pin 14) to be asserted on the SCSI bus, the TARGETMODE bit must be reset (0). In order for the signals C/D, I/O, /MSG, and /REQ to be asserted on the bus, the TARGETMODE bit must be set (1).

#### BIT 5 ENABLE PARITY CHECKING

The ENABLE PARITY CHECKING bit determines whether parity errors are ignored or saved in the parity error latch. If this bit is reset (0), parity is ignored. If this bit is set (1), parity errors are saved.

## BIT 4 ENABLE PARITY INTERRUPT

The ENABLE PARITY INTERRUPT bit, when set (1), causes an interrupt (IRQ) to occur if a parity error is detected. A parity interrupt is only generated if the ENABLE PARITY CHECKING bit (bit 5) is also enabled (1).

### BIT 3 ENABLE EOP INTERRUPT

When set (1), the ENABLE EOP INTERRUPT causes an interrupt to occur when DMA controller logic issues an /EOP (End of Process) signal (pin 27).

## BIT 2 MONITOR BUSY

When true (1), the MONITOR BUSY bit causes an interrupt to be generated for any unexpected loss of BSY (pin 13). When the interrupt is generated because of the loss of BSY, the lower 6 bits of the Initiator Command Register are reset (0) and all signals are removed from the SCSI bus.

#### BIT 1 DMA MODE

The DMA MODE bit is normally used to enable a DMA transfer and must be set (1) before writing ports 5 through 7. Ports 5 through 7 are used to start DMA transfers. The TARGETMODE bit (port 2, bit 6) must be consistent with writes to port 6 and 7 (i.e. set for a write to port 6 and reset for a write to port 7). The control bit ASSERT DATA BUS (port 1, bit 0) must be true (1) for all DMA send operations. In the DMA mode, /REQ (pin 20) and /ACK (pin 14) are automatically controlled.

The DMA MODE bit is not reset on the receipt of an /EOP signal. Any DMA transfer may be stopped by writing a zero into this bit location; however, care must be taken not to cause /CS or /DACK to become active simultaneously.

#### 3IT 0 ARBITRATE

The ARBITRATE bit is set (1) to start the arbitration process. Before setting this bit, the Output Data Register should contain the proper SCSI device ID value. Only one data bit should be active for SCSI bus arbitration. The 5380 waits for a bus free condition before entering the arbitration phase. The results of the arbitration phase can be determined by reading the status bits LA and AIP (port 1, bits 5 & 6, respectively).

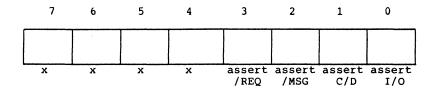

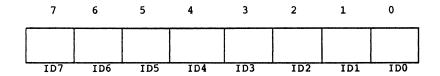

## 3.8.4 Target Command Register

when connected as a target device, the Target Command Register enables the PC to control the SCSI bus information transfer phase and/or to assert /REQ (pin 20) simply by writing this register. The TARGETMODE bit (port 2, bit 6) must be true (1) for bus assertion to occur. The SCSI bus phases are described in Table 9.

| Table 9. SCSI Information Transfer Phase: | Table | 9. | SCSI | Information | Transfer | Phases |

|-------------------------------------------|-------|----|------|-------------|----------|--------|

|-------------------------------------------|-------|----|------|-------------|----------|--------|

| Bus Phase   | bit 0<br>assert<br>I/O | bit 1<br>assert<br>C/D | bit 2<br>assert<br>MSG |  |

|-------------|------------------------|------------------------|------------------------|--|

| Data Out    | 0                      | 0                      | 0                      |  |

| Unspecified | 0                      | 0                      | 1                      |  |

| Command     | 0                      | 1                      | 0                      |  |

| Message Out | 0                      | 1                      | 1                      |  |

| Data In     | 1                      | 0                      | 0                      |  |

| Unspecified | 1                      | 0                      | 1                      |  |

| Status      | 1                      | 1                      | 0                      |  |

| Message In  | 1                      | 1 .                    | 1                      |  |

When connected as an Initiator with DMA Mode true, and if the phase lines (I/O, C/D, and MSG) do not match the phase bits in the Target Command Register, a phase mismatch interrupt is generated when /REQ (pin 20) goes active. In order to send data as an Initiator, the ASSERT /I/O, ASSERT /C/D, and ASSERT /MSG bits must match the corresponding bits in the current SCSI Bus Status Register (port 4). The ASSERT /REQ bit (bit 3) has no meaning when operating as an Initiator.

Figure 4. Target Command Register.

### 3.8.5 Current SCSI Bus Status

The Current SCSI Bus Status register is a read-only register used to monitor seven SCSI bus control signals plus the data bus parity bit. For example, an Initiator device can use this register to determine the current bus phase and poll /REQ for pending data transfers. This register can also be used to determine why a particular interrupt occurred.

Figure 5. Current Bus Status Register.

## 3.8.6 Select Enable Register

The Select Enable Register is a write-only register used as a mask to monitor a single ID during a selection attempt. The simultaneous occurrence of the correct ID bit, /BSY false, and /SEL true causes an interrupt. This interrupt can be disabled by resetting all bits in this register. If the ENABLE PARITY CHECKING bit (port 2, bit 5) is active (1), parity is checked during selection.

Figure 6. Set Enable Register.

### 3.8.7 Bus and Status Register

The Bus and Status Register is a read-only register used to monitor the remaining SCSI control signals not found in the Current SCSI Bus Status Register (/ATN & /ACK) as well as six other status bits. The following discussion explains each bit of the Bus and Status Register individually.

### BIT 7 END OF DMA TRANSFER

The END OF DMA TRANSFER bit is set if /EOP (pin 27), /DACK (pin 26), and either /IOR (pin 24) or /IOW (pin 29) are simultaneously active for at least 100 nsec. Since the /EOP signal can occur during the last byte sent to the Output Data Register (port 0), the /REQ and /ACK signals should be monitored to insure the last byte has been transferred. This bit is reset when the DMA MODE bit is reset (0) in the Mode Register (port 2).

### BIT 6 DMA REQUEST

The DMA REQUEST bit enables the MPU to sample the output pin /DRQ (pin 22). DRQ can be cleared by asserting /DACK (pin 26) or by resetting the DMA MODE bit (bit 1) in the Mode Register (port 2). The DRQ signal does not reset when a phase mismatch interrupt occurs.

## BIT 5 PARITY ERROR

This bit is set if a parity error occurs during a data receive or a device selection. The PARITY ERROR bit can only be set (1) if the ENABLE PARITY CHECK bit (port 2, bit 5) is active (1). This bit may be cleared by reading the Reset Parity/Interrupt Register (port 7).

### BIT 4 INTERRUPT REQUEST ACTIVE

This bit is set if an enabled interrupt condition occurs. It reflects the current state of the IRQ (pin 23) output and can be cleared by reading the Reset Parity/Interrupt Register (port 7).

#### BIT 3 PHASE MATCH

The SCSI signals /MSG, /C/D, and /I/O (pins 19, 18, and 17 respectively) represent the current information transfer phase. The PHASE MATCH bit indicates whether the current SCSI bus phase matches the lower three bits of the Target Command Register. PHASE MATCH is continuously updated and is only significant when operating as a bus initiator. A Phase Match must be active for data transfers to occur on the SCSI bus.

#### BIT 2 BUSY ERROR

The BUSY ERROR bit is active if an unexpected loss of the /BSY signal (pin 13) has occurred. This latch is set whenever the MONITOR BUSY bit (port 2, bit 2) is true and /BSY is false. An unexpected loss of /BSY disables any SCSI outputs and resets the DMA MODE bit (port 2, bit 1).

#### BIT 1 ATN

This bit reflects the condition of the SCSI bus control signal /ATN (pin 15). This signal is normally monitored by the target device.

### BIT 0 ACK

This bit reflects the condition of the SCSI bus control signal /ACK (pin 14). This signal is normally monitored by the target device.

## 3.8.8 DMA Registers

Three write-only registers are used to initiate all DMA activity. They are Start DMA Send (port 5), Start DMA Target Receive (port 6), and Start DMA Initiator Receive (port 7). Simply by writing to these registers starts the DMA transfer. Data presented to the 5380 on signals D[0-7] during the register write is meaningless and has no effect on the operation. Prior to writing these registers, the BLOCK MODE DMA bit (bit 7), the DMA MODE bit (bit 1), and the TARGETMODE bit (bit 6) in the Mode Register (port 2) must be appropriately set. The individual registers are briefly discussed below.

The Start DMA Send register is written to initiate a DMA send from the DMA to the SCSI bus, for either initiator or target operations. The DMA MODE bit (port 2, bit 1) must be set before writing to this register.

e Start DMA Target Receive register is written to initiate a A receive from the SCSI bus to the DMA for target operations aly. The DMA MODE bit (bit 1) and the TARGETMODE bit (bit 6) in the Mode Register (port 2) must both be set (1) before writing to a register.

Le Start DMA Initiator Receive register is written to initiate a 4A receive from the SCSI bus to the DMA for initiator operations aly. The DMA MODE bit (bit 1) must be true (1) and the ARGETMODE bit (bit 6) must be false (0) in the Mode Register port 2) before writing to this register.

## .8.9 Interrupts

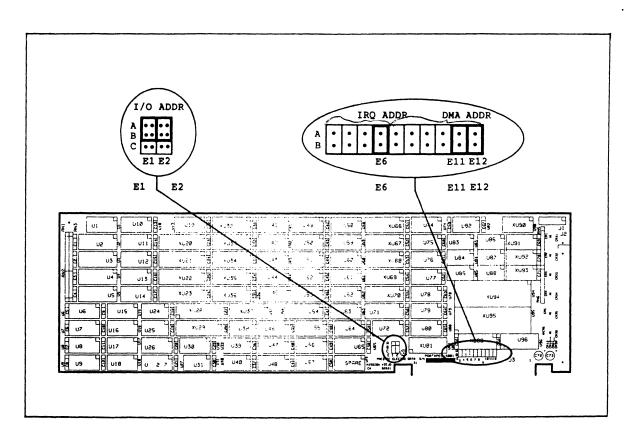

ne 5380 provides an interrupt output (IRQ) to indicate a task ompletion or an abnormal bus occurrence. Choose from four ossible IRQ assignments on the host PC: IRQ7, IRQ4, IRQ3, or RQ2, corresponding to jumpers E3 through E6 respectively (see able 10). Refer to Figure 7 for the location of the jumper ins.

Table 10. Interrupt Select Jumpers

| Jumpers | Interrupt |

|---------|-----------|

| E3      | IRQ7      |

| E4      | IRQ4      |

| E5      | IRQ3      |

| E6      | IRQ2      |

Jse of interrupts is optional and can be disabled by resetting the appropriate bits in the Mode Register (port 2) or the Select Enable Register (port 4).

when an interrupt occurs, the Bus and Status Register and the Current SCSI Bus Status Register must be read to determine which condition created the interrupt. IRQ (pin 23) can be reset simply by reading the Reset Parity/Interrupt Register (port 7) or by an external chip reset (/RESET active for 200 nsec).

An interrupt can be generated if any of these six conditions exists.

- 1. The chip is selected or reselected.

- 2. An /EOP signal occurs during a DMA transfer.

- 3. An SCSI bus reset occurs.

- 4. A parity error occurs during a data transfer.

- 5. A bus phase mismatch occurs.

- 6. An SCSI bus disconnection occurs.

The 5380 can generate a Selection/Reselection interrupt if /SEL (pin 12) is true (1), its device ID is true (1), and /BSY (pin 13) is false (0) for at least a bus settle delay (400 ns). If /I/O (pin 17) is active, this should be considered a reselect interrupt. The correct ID bit is determined by a match in the Select Enable Register (port 4). Only a single bit match is required to generate an interrupt. This interrupt may be disabled by writing zeros into all bits of the Select Enable Register.

An End of Process signal (/EOP at pin 27) is derived from the nost PC bus terminal count signal (T/C). This signal sets the END OF DMA status bit (port 5, bit 7) and optionally generates an interrupt if the ENABLE EOP INTERRUPT bit (port 2, bit 3) is true. The /EOP pulse is not recognized (END OF DMA bit set) unless /EOP, /DACK, and either /IOR or /IOW are concurrently active for at least 100 nsec. DMA transfers can still occur if /EOP is not asserted at the correct time. This interrupt can be disabled by resetting the ENABLE EOP INTERRUPT bit.

The 5380 generates an interrupt when the /RST signal (pin 16) changes to true. The device releases all bus signals within 800 nsec of this change. This interrupt also occurs after setting the ASSERT /RST bit (port 1, bit 7). This interrupt cannot be disabled. The /RST signal is not latched in bit 7 of the Current SCSI Bus Status Register and may not be active when this port is read. Given this situation, the Bus Reset interrupt is determined by default.

An interrupt is generated for a received parity error if the ENABLE PARITY CHECK (bit 5) and the ENABLE PARITY INTERRUPT (bit 4) bits are set (1) in the Mode Register (port 2). Parity is checked during a read of the Current SCSI Data Register (port 0) and during a DMA receive operation. A parity error can be detected without generating an interrupt by disabling the ENABLE PARITY INTERRUPT bit and checking the PARITY ERROR flag (port 5, bit 5).

The SCSI phase lines are comprised of the signals I/O, C/D, and MSG. These signals are compared with the corresponding bits in the Target Command Register: ASSERT I/O (bit 0), ASSERT C/D (bit 1), and ASSERT MSG (bit 2). Comparisons are made continuously and are reflected in the PHASE MATCH bit (bit 3) of the Bus and Status Register (port 5). If the DMA MODE bit (port 2, bit 1) is active and a phase mismatch occurs when /REQ (pin 20) changes from false to true, an interrupt (IRQ) is generated.

A phase mismatch prevents the recognition of /REQ and removes the chip from the bus during an initiator send operation. /DB[0-7] and /DBP cannot be driven even though the ASSERT DATA BUS port (port 1, bit 0) is active. This interrupt is only significant when connected as an Initiator and can be disabled by resetting the DMA MODE bit. This interrupt can occur when connected as a Target if another device is driving the phase lines to a different state.

If the MONITOR BUSY bit (bit 2) in the Mode Register (port 2) is active, an interrupt will be generated if the /BSY signal (pin 13) goes false for at least 400 nsec. This interrupt may be disabled by resetting the MONITOR BUSY bit.

#### 3.8.10 Data Transfers

Data can be transferred between SCSI bus and the host PC in one of two ways: Programmed I/O and Normal DMA. The following discussion describes these modes in detail.

Programmed I/O is the most primitive form of data transfer. The /REQ (pin 20) and /ACK (pin 14) handshake signals are individually monitored and asserted by reading and writing the appropriate register bits.

An Initiator Send operation would begin by setting the C/D, I/O, and /MSG bits in the Target Command Register to the correct state so that a phase match exists. In addition to the phase match condition, it is necessary for the ASSERT DATA BUS bit (port 1, bit 0) to be true and the received I/O signal to be false for the 5380 to send data.

For each byte transferred, the data is loaded into the Output Data Register (port 0) during an output operation, or the data is read from the Input Data Register (port 6) during an input operation.

Direct memory access (DMA) transfer is accomplished by way of the host PC DMA channel 1, 2, or 3 as selected by jumpers E7 through E12. Jumpers settings are defined in Table 11. Refer to Figure 7 for the location of the jumper pins.

Table 11. 5380 DMA Select Jumpers

| Jumpers | DMA Channel |

|---------|-------------|

| E7, E8  | 3           |

| E9, E10 | 2           |

| E11,E12 | 1           |

The SCSI chip outputs a DMA request (DRQ from pin 22) whenever it is ready for a byte transfer. The host DMA controller uses this DRQ signal to generate /DACK and an /IOR or an /IOW pulse to the 5380. DRQ goes inactive when /DACK is asserted and /DACK goes inactive sometime after the minimum read or write pulse width. This process is repeated for every byte transferred.

For all data transfer operations, /DACK and /CS should never be active simultaneously.

### 3.9 HOST INTERFACE, LOAD and CLOCK CONTROL LOGIC

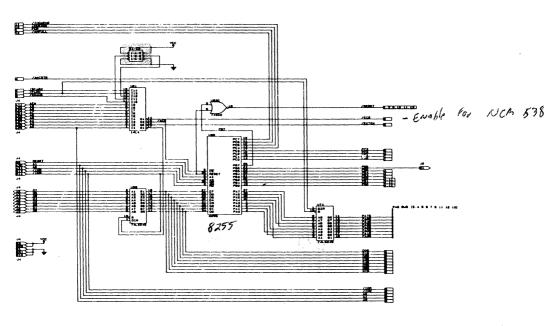

The host computer communicates with the PED-4001 module through a 8255 Programmable Peripheral Interface device, U95, and the 5380 SCSI Protocol Controller device, U94. The two devices are mapped in the I/O space of the host. The host I/O address bus, A[9-2], and address enable, AEN, is decoded by U81, a PAL14L4. Jumpers E1 and E2 feed U81 to allow for the selection of different module address paragraph assignments.

The three paragraph segments are listed in Table 12 along with their value and jumper settings. Read the jumper setting "A-to-B" to mean the jumper should be placed across terminals A and B of the E pins. Refer to Figure 7 for the location of the jumper pins.

Table 12. Module I/O Address Define Constants.

| E2 J  | graph<br>umper &<br>umper / | C | -t  | 30<br>o-B<br>o-B | 1 | A-t | 33<br>:o-B<br>:o-B | ı | A· | -to | 38<br>o-B<br>o-B |

|-------|-----------------------------|---|-----|------------------|---|-----|--------------------|---|----|-----|------------------|

| Regi  | ster                        | A | ddi | ress             |   | Add | iress              |   | A  | ddı | ress             |

|       | Current/Output Data         |   |     | 300              |   |     | 330                |   | 0  |     | 380              |

| 5380  |                             | 0 |     | 301              |   |     | 331                |   | 0  |     | 381              |

|       | Mode                        | 0 |     | 302              |   |     | 332                |   | 0  |     | 382              |

|       | Target Command              | 0 | Х   | 303              |   | 0 > | 333                |   | 0  | Х   | 383              |

| 5380  | Current Status/             |   |     |                  |   |     |                    |   |    |     |                  |

|       | Select Enable               | - |     | 304              |   |     | 334                |   | -  |     | 384              |

|       | Status/DMA Send             | 0 | Х   | 305              | ( | 0 > | 335                |   | 0  | X   | 385              |

| 5380  | Input Data/                 |   |     |                  |   |     |                    |   |    |     |                  |

|       | DMA Receive                 | 0 | Х   | 306              | - | 0 λ | 336                |   | 0  | X   | 386              |

| 5380  | Interrupts/                 | _ |     |                  |   | _   |                    |   | _  |     |                  |

|       | Initiator DMA               | - |     | 307              |   |     | 337                |   | 0  |     | 387              |

|       | Port A                      | 0 |     | 308              |   |     | 338                |   | 0  |     | 388              |

|       | Port B                      | 0 |     | 309              |   | -   | 339                |   | 0  |     | 389              |

|       | Port C                      | 0 |     | 30A              |   |     | : 33A              |   | 0  |     | 38A              |

|       | Control                     | 0 |     | 30B              |   |     | : 33B              |   | 0  |     | 38B              |

|       | Port A                      | 0 |     | 30C              |   | -   | : 33C              |   | 0  |     | 38C              |

|       | Port B                      | 0 |     | 30D              |   | -   | : 33D              |   | 0  |     | 38D              |

|       | Port C                      | 0 |     | 30E              |   |     | 33E                |   | 0  |     | 38E              |

| 8,255 | Control                     | 0 | X   | 30F              | ( | ) х | : 33F              |   | 0  | x   | 38F              |

Lower host address lines go directly to both devices to select one of four addressable registers of the 8255 or one of eight addressable registers of the 5380. The host data bus is buffered by a 74LS245 (U96). A 74S08 NOR gate, U83C, creates the module /RESET signal by OR'ing the host I/O bus RESET and Port B bit 7 of the 8255 (PB7).

The three ports of the 8255 are partitioned as follows. The upper half of Port C, PC[7-4], is configured as an input port to monitor four module status signals /AMFULL, FCR, INDEXED and /INDXEND. The lower half of Port C PC[3-0], is configured as an output port and is used for module clock and strobe control. Port B is configured as an output port output PB[7] enables the host PC to reset the module under software control. Output PB[6] is used to select the PED-4010 differential interface adapter when it is installed at the J2 SCSI interface connector. The lower 6 bits of port B PB[5-0], select the several registers and memory devices on the module. Port A, configured as a bi-directional port, drives U71, a 74LS245 which connects to the 8-bit internal data bus of the module, PA[7-0]B. PA[7-0]R serves as the data pathway over the entire module.

The PB[5-3] bits drive the binary select inputs of U65 a 74LS138 1-of-8 decoder. PC2 drives the enable input of the same IC. The outputs of U65 serve as timed strobes in selecting registers and memory on the module. They are listed individually in Table 13.

Four outputs drive the enable input of other decoders. /LCSTB drives U27, a 74LS138 on sheet 11 of the schematic, which selects the counter input registers (/CnCLD). /MSKSTB drives the enable input of U72, another 74LS138, which uses PB[2-0] to select one of the module RAM write enable strobes or /AMACLR as shown in Table 14. /AMISTB drives the enable input of U38B, one half of a 74LS139 dual 1-of-4 decoder, which uses PB1-0] to select the AM[] bus byte enable strobes as shown in Table 15. /QALSTB drives the enable input of the other half of the 74LS139, U38A, which with PB[1-0], generate the write enable strobes for the Edge Qualifier Memory as shown in Table 16. U80 a 74LS175 latch, is the module mode register loaded and cleared by /MODSTB and /MODCLR, respectively. The inputs to the 4-bit latch are driven by the PA[3-0]B bus.

Table 13. Register/RAM Timed Strobes

| PB<br>543 Output                                                                                                  | Function                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000 /LCSTB<br>001 /SCRW<br>010 /MSKSTB<br>011 /AMISTB<br>100 /QALSTB<br>101 /MINDEX<br>110 /MODSTB<br>111 /MODCLR | Load Counter Strobe Sequence Control Memory Write Enable State Mask Memory Write Timing Strobe Acquisition Memory Multiplexer Timing Strobe Edge Qualifier Memory Write Timing Strobe Manual Index Command Module Mode Latch Load Strobe Module Mode Latch Clear |

Table 14. /MSKSTB Outputs.

Port B

| PB<br>210 | Output | PB<br>210 | Output  |                |

|-----------|--------|-----------|---------|----------------|

| 000       | /MOWE  | 100       | /M12WE  |                |

| 001       | /M4WE  | 101       | /M16WE  |                |

| 010       | /M8WE  | 110       | /M20WE  | - Clear Memory |

| 011       | /QUWE  | 111       | /AMACLR | Address        |

Table 15. /AMISTB Outputs.

Port B But 140

| PB<br>10 | Output |

|----------|--------|

| 00       | /AMI0  |

| 01       | /AMI8  |

| 10       | /AMI16 |

| 11       | /AMI24 |

Table 16. /QALSTB Outputs.

| PB<br>10 | Output |

|----------|--------|

| 00       | /Q0WE  |

| 01       | /Q4WE  |

| 10       | /Q8WE  |

| 11       | /QCWE  |

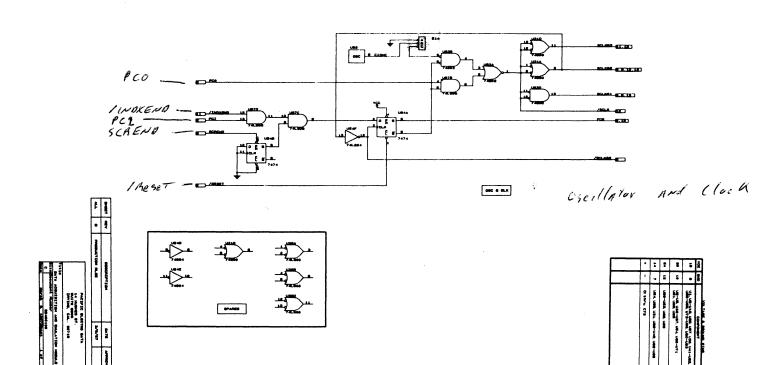

The module clock control logic is shown on sheet 1 of the schematic. U82, a 10.000MHz hybrid clock oscillator, is the source of the internal "run" clock for the module. Whenever the signal FCR is high, C10MC is gated to /SCLK via the AND/OR gates U83A, U83B and U87B. The buffered clocks SCLK1B, SCLK2B and SCLK3B are derived from /SCLK. If FCR is low, PCO becomes the clock source for the module. The host generates SCLKs by toggling 8255 output PCO. FCR is the output from the D-type Flip Flop U84A. The FF is cleared by /RESET, selecting PCO as SCLK. C10MC is selected by PC1. If the signals /INDXEND or SCREND become active, FCR is set LOW on the next SCLK.

#### NOTE:

- 1 ASSEMBLE PER WSM 04000 2 COMPONENT SIDE SHOWN

- COMPONENTS IDENTIFIED BY REFERENCE

DESIGNATOR IN MATERIAL LIST ML 400100

OBSERVE ORIENTATION ON ALL ICS AND

- SOCKETS. PIN & IDENTIFIED BY SQUARE PAD

- (3) COMPONENT PIN & ORIENTATED AT LOWER LEFT

- 6 OBSERVE POLARITY ON CAPACITORS CTS

THRU CTS AND DIODE CR!

5 SOCKETTED COMPONENT

- IC COMPONENTS ARE ELECTROSTATIC SENSITIVE.

ALL HANDLING, ASSEMBLY, TEST OPERATIONS

TO BE DONE AT PROTECTED WORK STATION

- AND U94 OMITTED. COMPONENT HOLES

- AND TO BE CLEAR OF SOLDER.

TO

- 12 PART DASH NUM, REU LETTER AND SERIAL NUMBER IN BLACK INK, CLEARLY LEGIBLE

- ASSEMBLY SHALL BE TESTED PER T3400125

- IN REFERENCE SCHEMATIC STADOLOG

**▲ PED-4001-110 ONLY ▲** PED-4001-120 ONLY

Hosa I/o

DATA ACQUISITION AND EMALATION MODULE

Site|Decument Number | DEV

C | DOI: North S. AMEZZENERS | DOI: NO.

STATE MASK MEMORY

INTO DESCRIPTION OF BRANCH PARK

BOOKS AND DESCRIPT

DATA ACRUTETTON AND ENGLATTON HOOLE

STEP COMMENT NAMED PROPERTY OF THE PROPERT

STATE COMPARE

5

rsh 8. 1867 Sheet

C BOARDAN AMERICAN AND BRAIL THE REPLACE OF THE PROPERTY OF TH

NOTE: THIS SHEET APPLIES TO PED4001-180 HODULES ONLY.

## APPENDIX B. MODULE PARTS LIST.

Table B-1 includes all components and parts making up the PED-4001 Dat Analyzer Module. Parts are listed by item type, item description, manufacturer, schematic reference number, and quantity.

Table B-1. Parts List.

| ITEM | DESCRIPTION  | MFG | NOTE           | REFERENCE       | QUAN                                           |

|------|--------------|-----|----------------|-----------------|------------------------------------------------|

| 1    | IC, 74S00    | ті  |                | U31             | 1                                              |

| 2    | IC, 74LS00   | TI  |                | U39             | 1                                              |

| 3    | IC, 74S02    | TI  |                | U83             | 1                                              |