#### cover-letter.text >schnorr>distribution V: (1)

#### SYMBOLICS, INC.

This document is COMPANY CONFIDENTIAL. It contains extremely sensitive and proprietary information. Reasonable and appropriate care should be taken to protect this information. Copies of this document are individually numbered with the recipient's name recorded. You are responsible for your copy of this document. As newer versions of this document are created, older versions will be collected for centralized destruction. Under no circumstances is this document to be copied. If you need to have someone added to the distribution list or if more copies of this document are needed, contact Linda Birch (Birch or x7605).

Document Number

# I-Machine Architecture Specification

**Revision 2**

# Company Confidential

Symbolics, Inc.

ü

## Symbolics, Inc.

# Table of Contents

| •        | <br> | 아이는 것 같은 것 같은 것이 있는 것 같은 것 같은 것 같이 많이 많이 많이 많이 없다.        | Page |

|----------|------|-----------------------------------------------------------|------|

| 1.       | Lisp | -Machine Data Types                                       | 1    |

|          | 1.1  | Introduction to Lisp-Machine Objects                      | 2    |

| :<br>· . |      | 1.1.1 Memory Words                                        | 2    |

|          |      | 1.1.2 Classes of Stored Object Representations            | 3    |

|          |      | 1.1.3 Components of Stored Representations                | 6    |

|          |      | 1.1.4 Operand-Reference Classification                    | 12   |

|          | 1.2  | Data-Type Descriptions                                    | 13   |

| •        |      | 1.2.1 Representations of Symbols                          | 13   |

| •        | • •  | 1.2.2 Representations of Instances and Related Data Types | 14   |

|          | •    | 1.2.3 Representation of Characters                        | 17   |

|          |      | 1.2.4 Representations of Numbers                          | 19   |

|          |      | 1.2.5 Representations of Lists                            | 24   |

|          |      | 1.2.6 Representations of Arrays and Strings               | 30   |

| •        |      | 1.2.7 I-Machine Array Registers                           | 36   |

|          |      | 1.2.8 Representations of Functions and Closures           | 40   |

|          |      | 1.2.9 Instruction Representation                          | 43   |

|          |      | 1.2.10 Program-Counter Representations                    | . 46 |

|          |      | 1.2.11 Representation of Locatives                        | 46   |

|          |      | 1.2.12 Representation of Physical Addresses               | 46   |

|          | 1.3  | Data-Type Code Assignments                                | 48   |

|          |      | 1.3.1 Headers, Special Markers, and Forwarding Pointers   | 48   |

|          |      | 1.3.2 Number Data Types                                   | 48   |

|          | . •  | 1.3.3 Instance Data Types                                 | 49   |

|          |      | 1.3.4 Primitive Data Types                                | 49   |

|          |      | 1.3.5 Special Marker for Garbage Collector                | 50   |

| · · ·    |      | 1.3.6 Data Types for Program Counter Values               | 50   |

|          |      | 1.3.7 Full-Word Instruction Data Types                    | 51   |

|          |      | 1.3.8 Half-Word Instruction Data Types                    | 51   |

|          | 1.4  | Appendix: Comparison of 3600-Family and I-Machine Data    | 52   |

|          |      | Representations                                           |      |

|          |      | 1.4.1 Array Differences                                   | 54   |

|          |      | 1.4.2 Compiled Function Differences                       | 56   |

| 2.       | Men  | nory Layout and Addressing                                | 57   |

| •        | 2.1  | Address Space                                             | 57   |

|          | -    | 2.1.1 Virtual Addresses                                   | 57   |

iii

| Symbolic | s, Inc. |

|----------|---------|

|----------|---------|

|    | 이 가지 않는 것 같은 것 같                      |            |

|----|---------------------------------------------------------------------|------------|

|    | 2.1.2 Ephemeral Addresses                                           | 58         |

|    | 2.1.3 Unmapped Addresses                                            | 58         |

|    | 2.1.4 Wired Addresses                                               | 59         |

|    | 2.1.5 Pages                                                         | 59         |

|    | 2.2 GC Support                                                      | 59         |

|    | 2.3 Address Translation                                             | 60         |

| •  | 2.3.1 Page Hash Table                                               | 60         |

|    | 2.3.2 PHT Lookup Algorithm                                          | 63         |

|    | 2.3.3 Translation Algorithm                                         | 66         |

|    | 2.4 Appendix: Comparison of 3600-family and I-machine Memory Layout | 69         |

|    | and Addressing                                                      |            |

|    |                                                                     |            |

| 3. | Macroinstruction Set                                                | <b>73</b>  |

|    | 3.1 Introduction                                                    | 73         |

|    | 3.1.1 Instruction Sequencing                                        | 73         |

|    | 3.1.2 Internal Registers                                            | 75         |

|    | 3.1.3 Explanation of Instruction Definitions                        | 75         |

|    | 3.2 The Instructions                                                | .0<br>91   |

|    | 3.2.1 List-Function Operations                                      | 92         |

|    | 3.2.2 Predicate Instructions                                        | 102        |

|    | 3.2.3 Numeric Operations                                            | 113        |

|    | 3.2.4 Data-Movement Instructions                                    | 141        |

|    | 3.2.5 Field-Extraction Instructions                                 | 149        |

|    | 3.2.6 Array Operations                                              | 154        |

|    | 3.2.7 Block Instructions                                            | 169        |

|    | 3.2.8 Function-Calling Instructions                                 | 175        |

|    | 3.2.9 Binding Instructions                                          | 188        |

|    | 3.2.10 Catch Instructions                                           | 192        |

|    | 3.2.11 Lexical Variable Accessors                                   | 198        |

|    | 3.2.12 Instance Variable Accessors                                  | 201        |

|    | 3.2.13 Subprimitive Instructions                                    | 213        |

|    |                                                                     |            |

| 4. | Function Calling, Message Passing, Stack-Group Switching            | 241        |

|    | 4.1 Stacks                                                          | 241        |

|    | 4.1.1 Control Stack                                                 | 241        |

|    | 4.1.2 Binding Stack                                                 | 244        |

|    | 4.1.3 Data Stack                                                    | 245        |

|    |                                                                     | 245<br>245 |

|    | 4.2 Registers Important to Function Calling and Returning           |            |

|    | 4.3 Function Calling                                                | 249        |

|    | 4.3.1 Starting a Function Call                                      | 249        |

|    | 4.3.2 Pushing the Arguments                                         | 253<br>050 |

|    | 4.3.3 Finishing the Call                                            | 253        |

iv

| · · ·   | 4.4  | Function Entry                                              | 257         |

|---------|------|-------------------------------------------------------------|-------------|

| · · · · |      | 4.4.1 Push-apply-args                                       | 259         |

|         |      | 4.4.2 Pull-apply-args                                       | 261         |

| . •     |      | 4.4.3 Trapping Out of Entry and Restarting                  | 266         |

|         | 4.5  | Function Returning                                          | 266         |

| ÷ .     | ÷    | 4.5.1 Function Return Instructions                          | 266         |

|         |      | 4.5.2 Frame Cleanup                                         | 270         |

|         |      | 4.5.3 Value Matchup                                         | 271         |

|         | 4.6  | Catch, Throw and Unwind-Protect                             | 271         |

|         | 4.7  | Generic Functions and Message Passing                       | 275         |

|         |      | 4.7.1 Flavor                                                | 276         |

|         |      | 4.7.2 Handler Table                                         | 276         |

|         |      | 4.7.3 Calling a Generic Function                            | 277         |

|         |      | 4.7.4 Sending a Message                                     | 278         |

|         |      | 4.7.5 Accessing Instance Variables                          | 278         |

| ÷       | 4.8  | Stack-Group Switching                                       | 280         |

|         |      | Appendix: Comparison of 3600-Family and I-Machine Function- | 282         |

|         |      | Calling                                                     |             |

| .,      |      |                                                             |             |

| 5.      | Exce | ption Handling                                              | 283         |

| • .     | 5.1  | Traps in General                                            | 283         |

| •       | 5.2  | The Extra Stack                                             | 285         |

|         | 5.3  | Trap Modes                                                  | 285         |

|         |      | Trap Vector                                                 | 286         |

|         |      | Exceptions                                                  | 286         |

|         |      | 5.5.1 Error Traps                                           | 286         |

|         |      | 5.5.2 Instruction Exceptions                                | 287         |

|         |      | 5.5.3 Arithmetic Traps                                      | 287         |

|         |      | 5.5.4 Memory Exceptions                                     | 289         |

|         |      | 5.5.5 Stack Overflow                                        | <b>29</b> 0 |

|         |      | 5.5.6 Sequence Breaks                                       | 290         |

|         |      | 5.5.7 Preemption                                            | 291         |

|         |      | 5.5.8 Trace Traps                                           | 292         |

|         |      | 5.5.9 PULL-APPLY-ARGS Exception                             | 293         |

|         |      | 5.5.10 FEP-mode Traps                                       | 293         |

|         |      | 5.5.11 Processor Faults                                     | 293         |

|         | 5.6  | Trap Vector Layout                                          | 294         |

|         | 5.7  | Reset and Init                                              | 295         |

|         | 5.8  |                                                             | 295         |

|         |      | Handling                                                    |             |

|         |      |                                                             |             |

# APPENDIX A. Revision 0 Implementation Features

297

v

| A.0.1 Revision 0 Implementation Memory Features                 | 297 |

|-----------------------------------------------------------------|-----|

| A.0.2 Revision 0 Implementation Instruction Features            | 298 |

| A.0.3 Revision 0 Implementation Function-Calling Features       | 300 |

| A.0.4 Revision 0 Implementation Exception Handling Features     | 300 |

| APPENDIX B. Summary of Omitted 3600 Instructions                | 303 |

| APPENDIX C. Notes on I-Machine Architecture History             | 305 |

| APPENDIX D. Hints for Software Developers                       | 309 |

| D.0.1 Stack Groups on the I Machine                             | 310 |

| APPENDIX E. Notes on Future Implementations of the Ivory Chip   | 315 |

| APPENDIX F. Instruction Classifications for Packed Instructions | 317 |

| F.1 Formats                                                     | 317 |

| F.2 Operand-from-stack Instructions                             | 317 |

| F.3 10-bit-immediate Instructions                               | 319 |

| F.4 Encodings                                                   | 321 |

| Index                                                           | 325 |

# List of Figures

Symbolics, Inc.

| <ul> <li>A supervisition of the second sec<br/>second second sec</li></ul> | 그는 것 같은 것 같                      | 1.1.1.1.1.1.1 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|---------------|

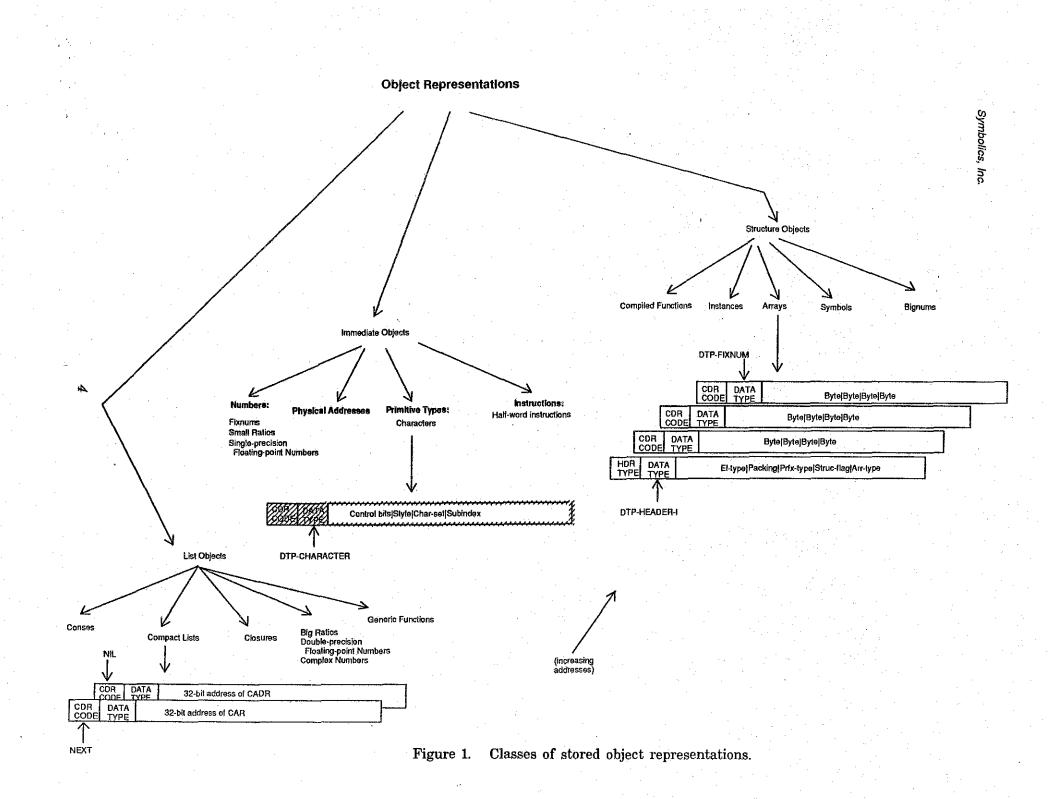

| Figure 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Classes of stored object representations.                      | 4             |

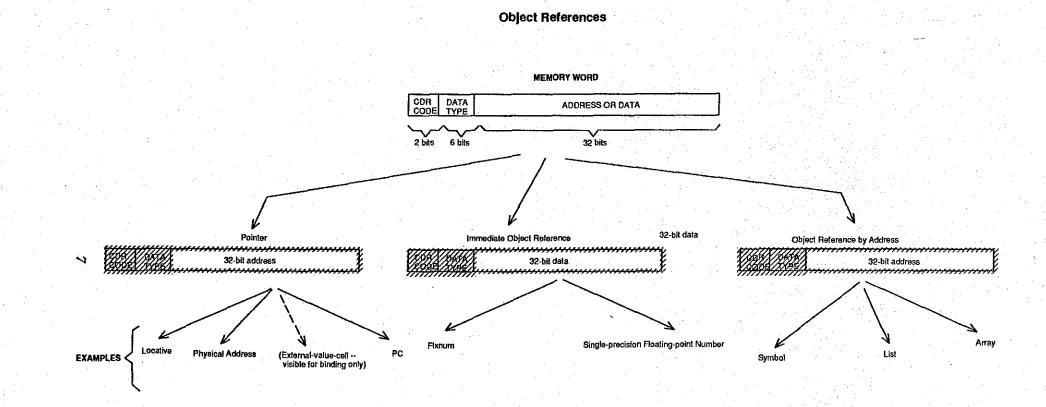

| Figure 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Three types of object references.                              | 7             |

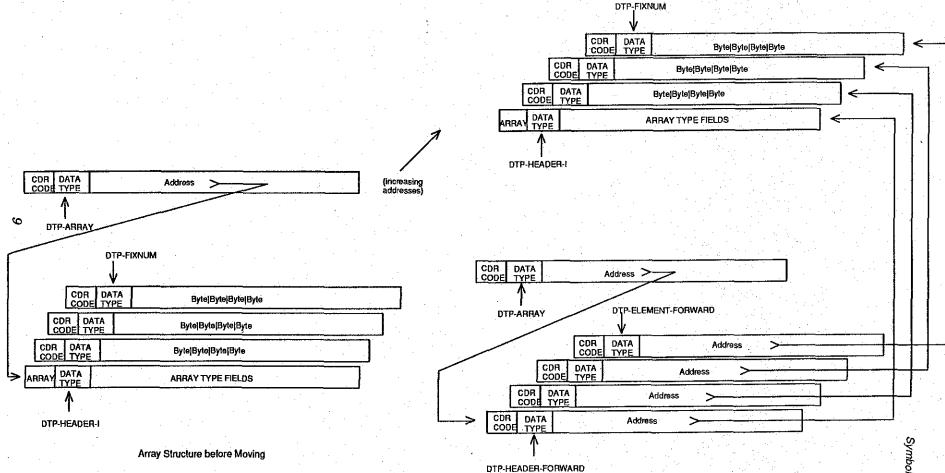

| Figure 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Use of forwarding pointers to move an array.                   | 9             |

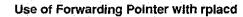

| Figure 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Use of forwarding pointers to expand a cons.                   | 11            |

| Figure 5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Structure of a symbol object.                                  | 15            |

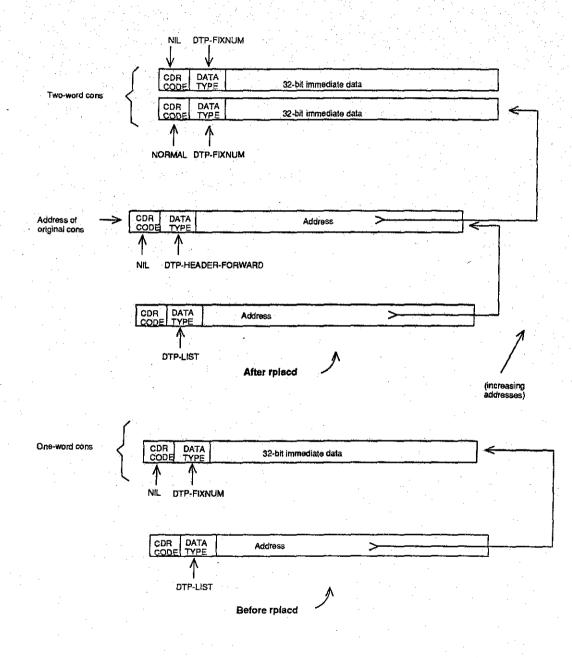

| Figure 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | The structure of an instance.                                  | 18            |

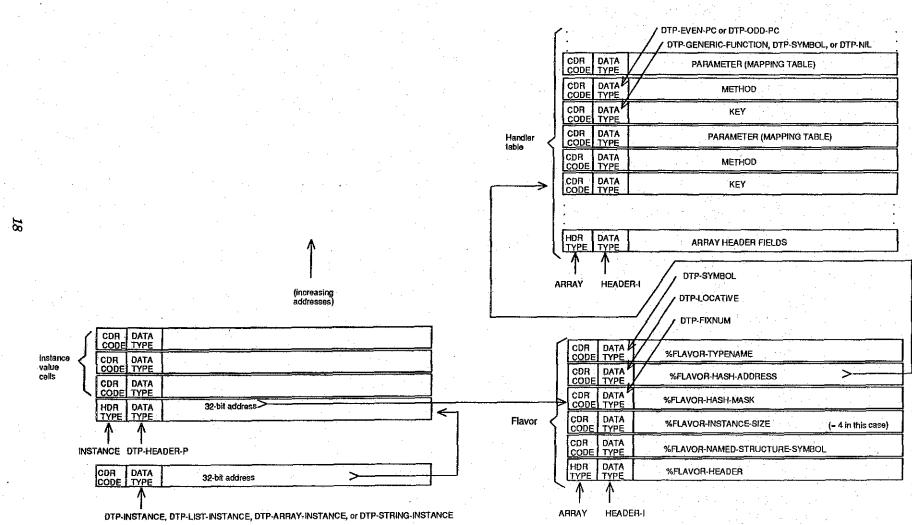

| Figure 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Structure of an object of type dtp-bignum                      | 21            |

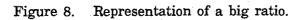

| Figure 8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Representation of a big ratio.                                 | 23            |

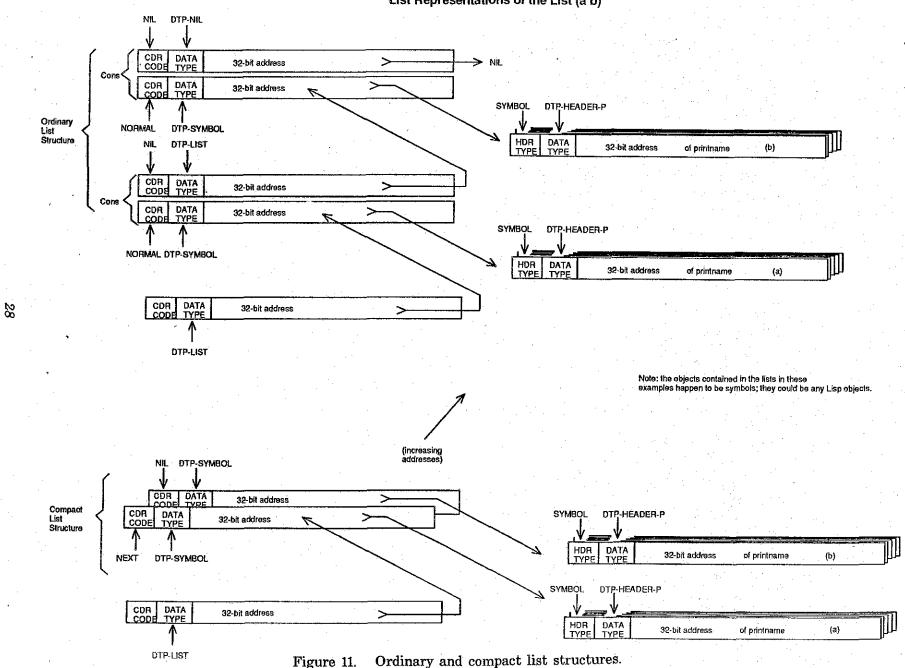

| Figure 9.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Representation of a double-precision floating-point number.    | 25            |

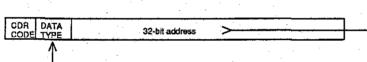

| Figure 10.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Representation of a complex number.                            | 26            |

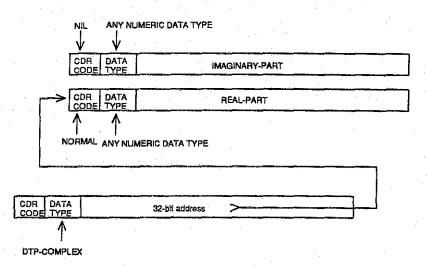

| Figure 11.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Ordinary and compact list structures.                          | 28            |

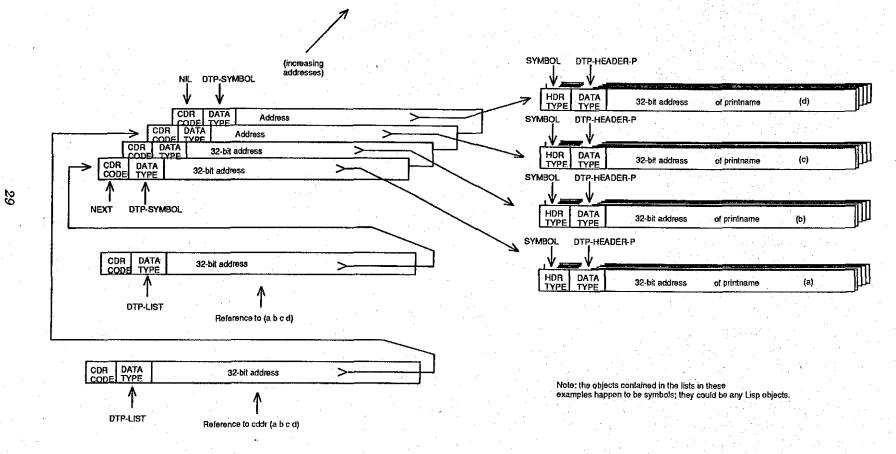

| Figure 12.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | An object reference to the cddr of a list.                     | 29            |

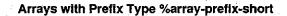

| Figure 13.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Short-prefix arrays with and without leaders.                  | 33            |

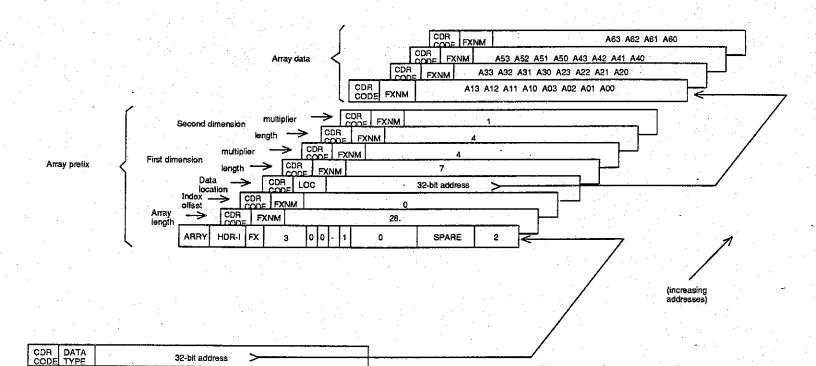

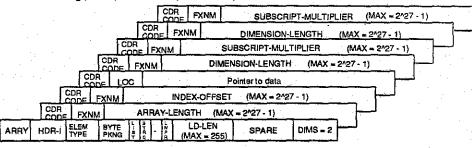

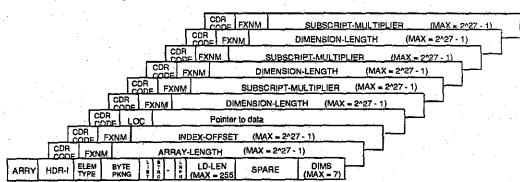

| Figure 14.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | A two-dimensional array.                                       | 35            |

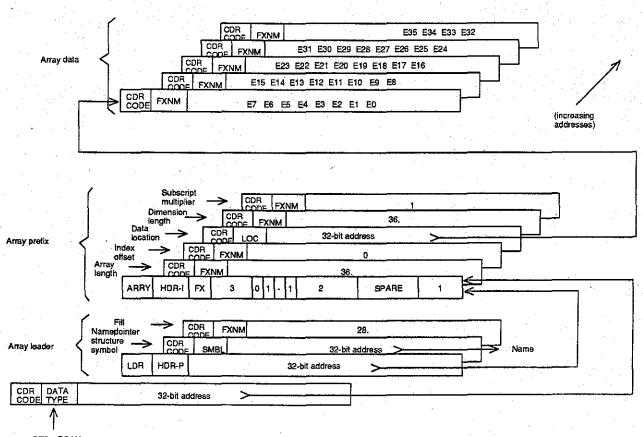

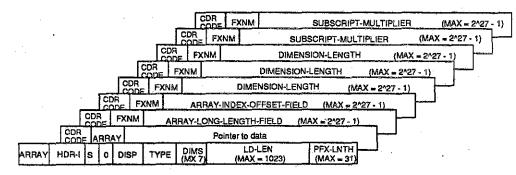

| Figure 15.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | A simple displaced array.                                      | 37            |

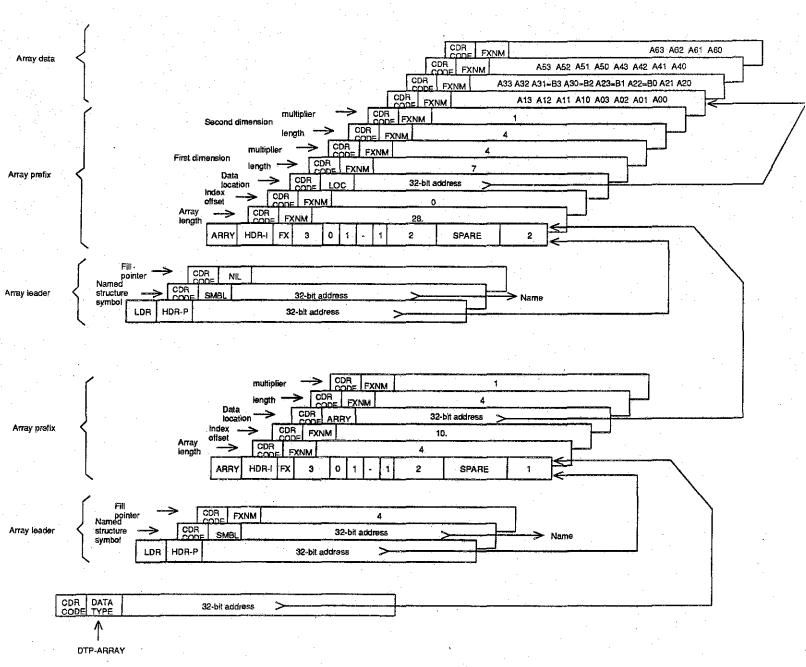

| Figure 16.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | A one-dimensional array indirected to a two-dimensional array. | - 38          |

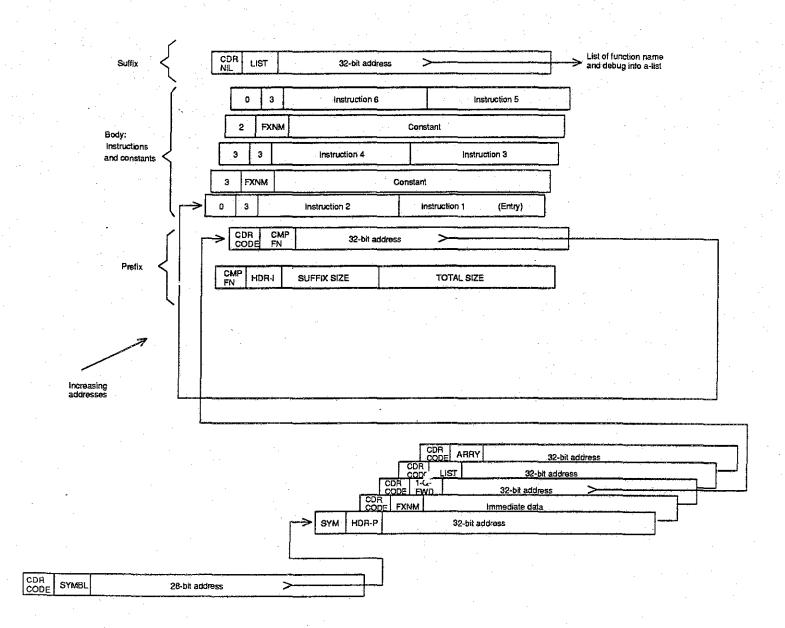

| Figure 17.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | The structure of a compiled function.                          | 42            |

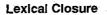

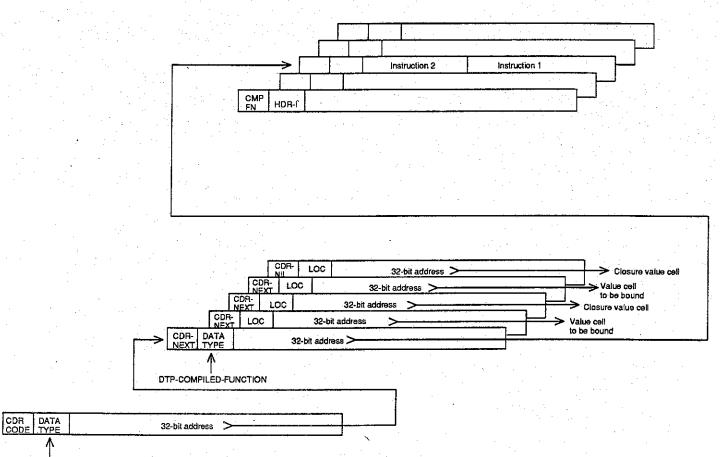

| Figure 18.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | The structure of a lexical closure.                            | 44            |

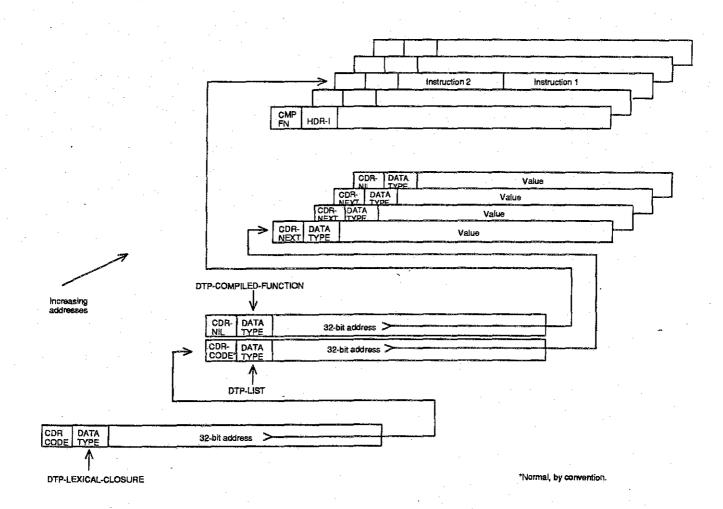

| Figure 19.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | The structure of a dynamic closure.                            | 45            |

| Figure 20.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Comparison of array prefix structures.                         | 55            |

| Figure 21.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | I-machine instruction formats.                                 | 80            |

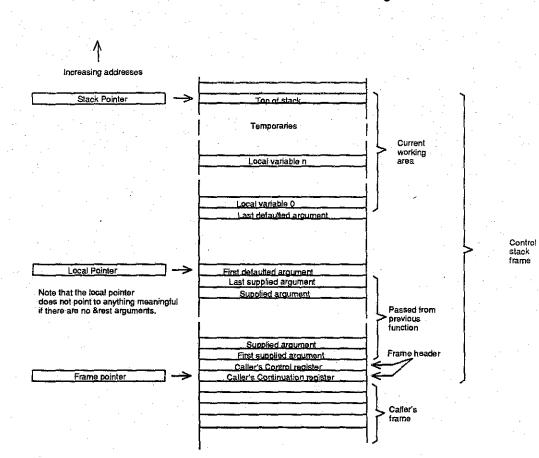

| Figure 22.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | An I-machine control stack frame.                              | 243           |

| Figure 23.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | The stack at the end of a start-call instruction               | 252           |

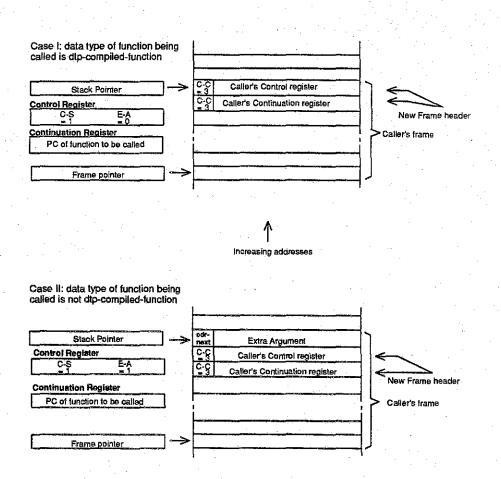

| Figure 24.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | The stack after completion of the finish-call instruction      | 256           |

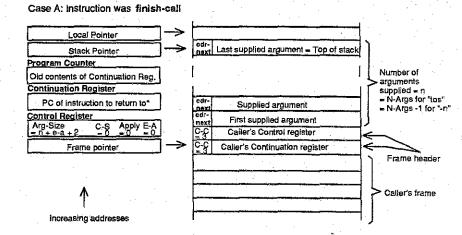

| Figure 25.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | The argument matchup algorithm                                 | 260           |

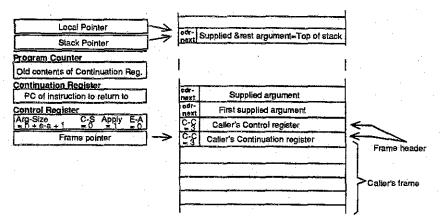

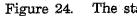

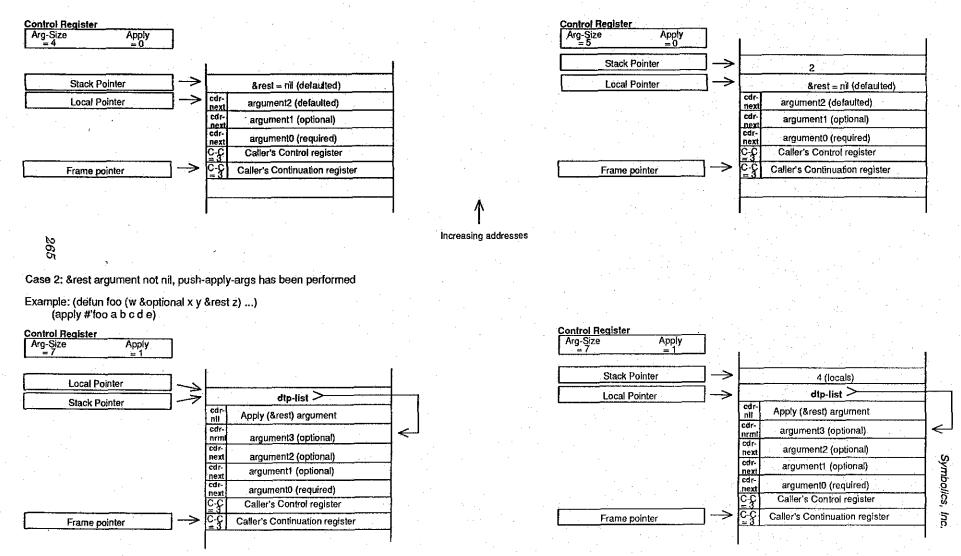

| Figure 26.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | The push-apply-args operation                                  | 262           |

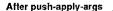

| Figure 27.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | The pull-apply-args operation                                  | 263           |

| Figure 28.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | The effect of the locate-locals instruction                    | 265           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                |               |

# List of Tables

| Table | 1.          | Header Types                              |       |                           |                    |                                          | 8  |

|-------|-------------|-------------------------------------------|-------|---------------------------|--------------------|------------------------------------------|----|

| Table | 2.          | Valid Array Types for Byte-Packing Values |       |                           | ann an th          |                                          | 40 |

| Table | 3.          | Headers, Special Markers, and Forwarding  | Point | ters                      |                    |                                          | 48 |

| Table | 4.          | Number Data Types                         | · · · | · · · ·                   | 1                  | en e | 49 |

| Table | 5.          | Instance Data Types                       |       | to services<br>Production | 5                  | 1999 - A                                 | 49 |