# A Model For Parallel Computer Systems

by

T. H. Bredt

E. J. McCluskey

Technical Report No. 5

April 1970

This work was supported in part by

the Joint Services Electronic Programs

U. S. Army, U. S. Navy, and U. S. Air Force

under Contract N-00014-67-A-0112-0044 and

by the National Aeronautics and Space

Administration under Grant 05-020-337.

**DIGITAL SYSTEMS LABORATORY**

**STANFORD ELECTRONICS LABORATORIES**

**STANFORD UNIVERSITY . STANFORD, CALIFORNIA**

STAN-CS-70-160

SEL -70-014

A MODEL FOR PARALLEL COMPUTER SYSTEMS

T. H. Bredt

E. J. McCluskey

April 1970

Technical Report No. 5

DIGITAL SYSTEMS LABORATORY

Stanford Electronics Laboratories      Computer Science Department

Stanford University

Stanford, California

This work was supported in part by the Joint Services Electronic Programs U. S. Army, U. S. Navy, and U. S. Air Force under Contract N-00014-67-A-0112-0044 and by the National Aeronautics and Space Administration under Grant 05-020-337.

A MODEL FOR **PARALLEL COMPUTER SYSTEMS**

T. H. Bredt

E. J. McCluskey

Digital Systems Laboratory

Stanford Electronics Laboratories

Stanford University, Stanford, California

ABSTRACT

A flow table model is defined for parallel computer systems. In this model, fundamental-mode flow tables are used to describe the operation of system components, which may be programs or circuits. Components communicate by changing the values on interconnecting lines which carry binary level signals. It is assumed that there is no bound on the time for value changes to propagate over the interconnecting lines. Given this delay assumption, it is necessary to specify a mode of operation for system components such that input changes which arrive while a component is unstable do not affect the operation of the component. Such a mode of operation is specified. Using the flow table model, a new control algorithm for the two-process mutual exclusion problem is designed. This algorithm does not depend on the exclusive execution of any primitive operations used in its implementation. A circuit implementation of the control algorithm is described.

TABLE OF CONTENTS

|                                                                                 |           |

|---------------------------------------------------------------------------------|-----------|

| INTRODUCTION . . . . .                                                          | 1         |

| <b>PARALLEL SYSTEMS . . . . .</b>                                               | <b>9</b>  |

| FLOWTABLES . . . . .                                                            |           |

| DELAY ASSUMPTIONS . . . . .                                                     | 18        |

| A FLOW TABLE SOLUTION FOR THE TWO-PROCESS<br>MUTUAL EXCLUSION PROBLEM . . . . . | 19        |

| BASIC COMPONENT STRUCTURE . . . . .                                             | <b>28</b> |

| Pulse Mode and Clocked Circuits . . . . .                                       | 35        |

| Component Operation . . . . .                                                   | 40        |

| A CONTROL CIRCUIT FOR THE TWO-PROCESS<br>MUTUAL EXCLUSION PROBLEM . . . . .     | <b>46</b> |

| CONCLUSIONS . . . . .                                                           | 54        |

| REFERENCES . . . . .                                                            | 55        |

## List of Tables

|     |                                                                                            |    |

|-----|--------------------------------------------------------------------------------------------|----|

| 1.  | Dijkstra's P, V Solution to the Mutual Exclusion Problem . . . . .                         | 4  |

| 2.  | General Form of a Flow Table . . . . .                                                     | 15 |

| 3.  | a) Flow Table Example . . . . .                                                            | 17 |

|     | b) Table Which is Not a Flow Table . . . . .                                               | 17 |

| 4.  | Interpretation of Variable Values<br>for Fig. 3 . . . . .                                  | 21 |

| 5.  | Design of a Flow Table for Process 1 . . . . .                                             | 22 |

| 6.  | Flow Table for Process 2 . . . . .                                                         | 22 |

| 7.  | An Improper State Table . . . . .                                                          | 24 |

| 8.  | Design of the Control Flow Table for<br>the Two-Process Mutual Exclusion Problem . . . . . | 27 |

| 9.  | Flow Tables for the Two-Process Mutual<br>Exclusion Problem . . . . .                      | 29 |

| 10. | Flow Table Example . . . . .                                                               | 33 |

| 11. | Transition Table for the Control Circuit . . . . .                                         | 47 |

| 12. | Excitation Table for the Control Circuit . . . . .                                         | 49 |

## List of Figures

|     |                                                                                                                                      |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.  | System configuration for Dijkstra's mutual exclusion problem solution . . . . .                                                      | 7  |

| 2.  | Typical parallel system configuration . . . . .                                                                                      | 10 |

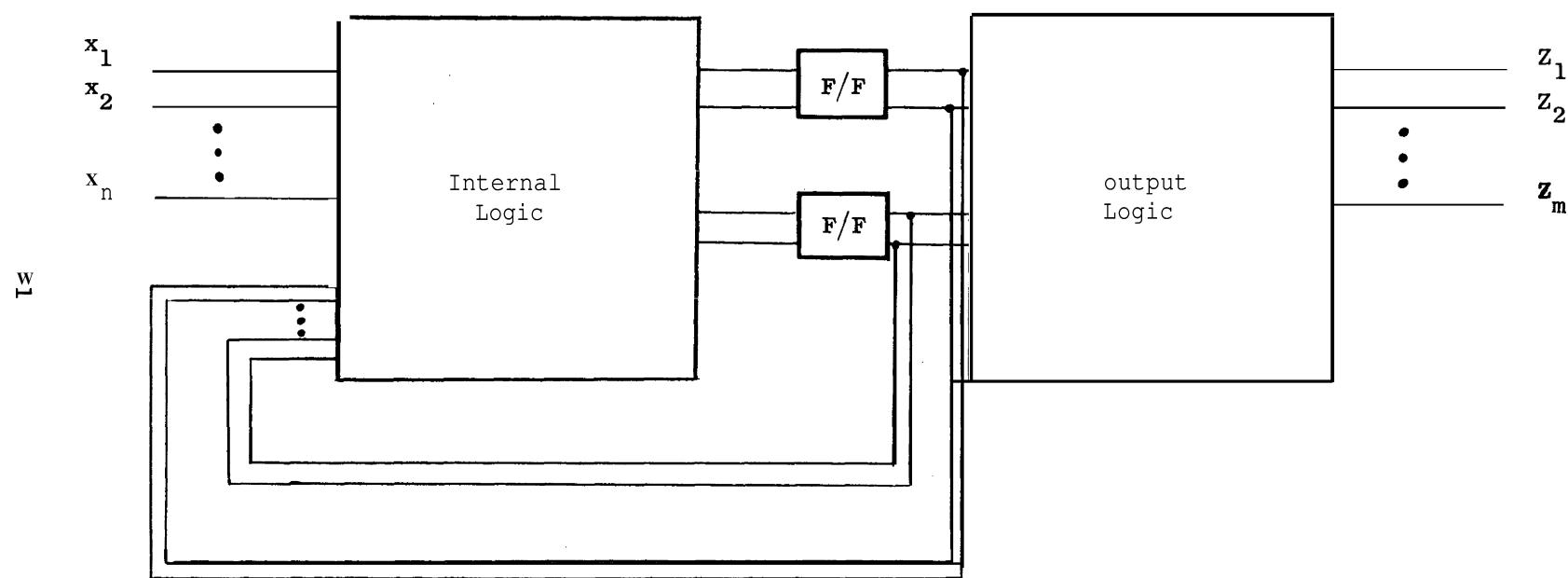

| 3.  | General form of a system component . . . , . . . . .                                                                                 | 12 |

| 4.  | System configuration for the two-process mutual exclusion problem . . . . . . . . .                                                  | 20 |

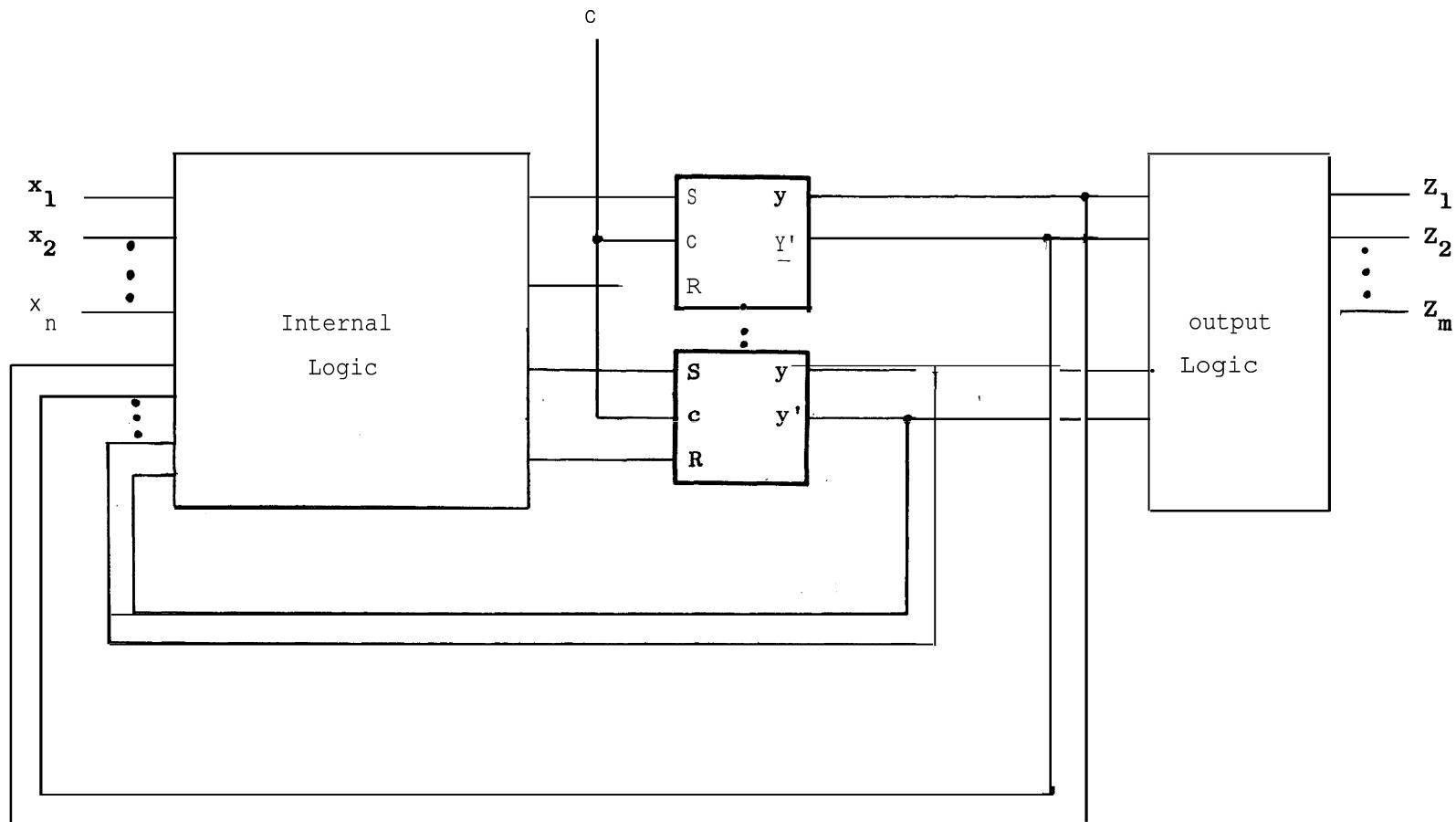

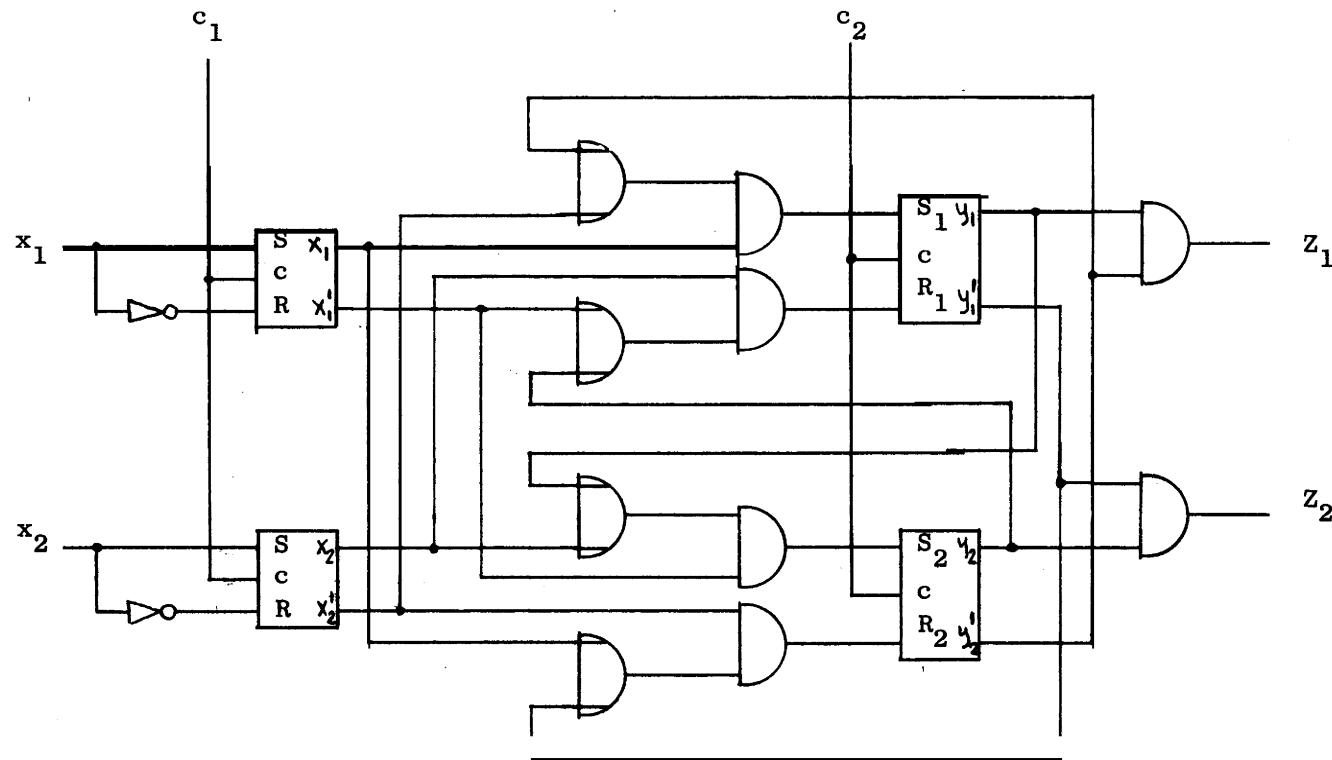

| 5.  | A general form for a sequential circuit using Set-Reset flip-flops. . . . . . . . .                                                  | 31 |

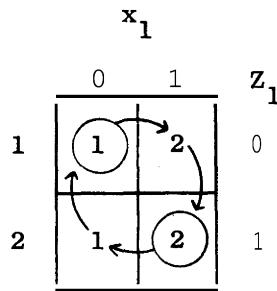

| 6.  | Possible transitions for flow table of Table 9 given input sequence<br>$x_1 x_2: 00 \rightarrow 01 \rightarrow 11$ . . . . . . . . . | 34 |

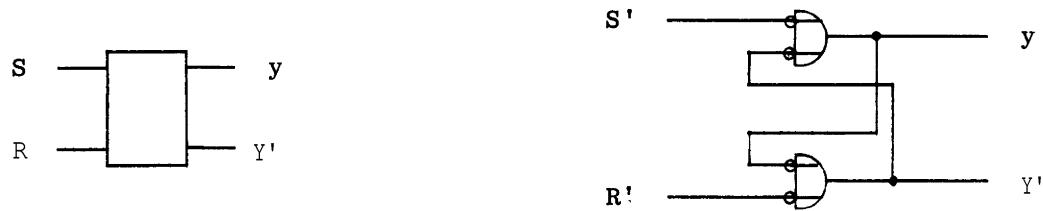

| 7.  | S-R flip-flops . . . . . . . . . . . . . . . . .                                                                                     | 37 |

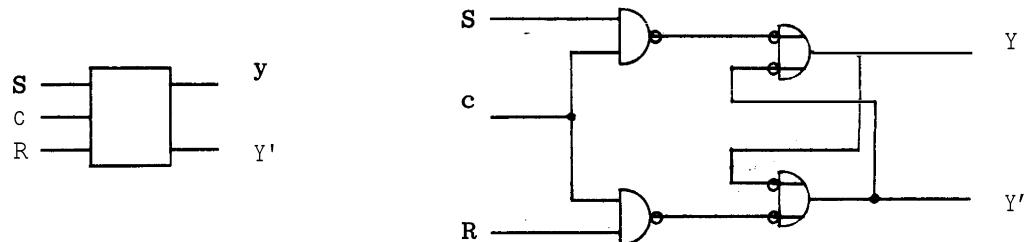

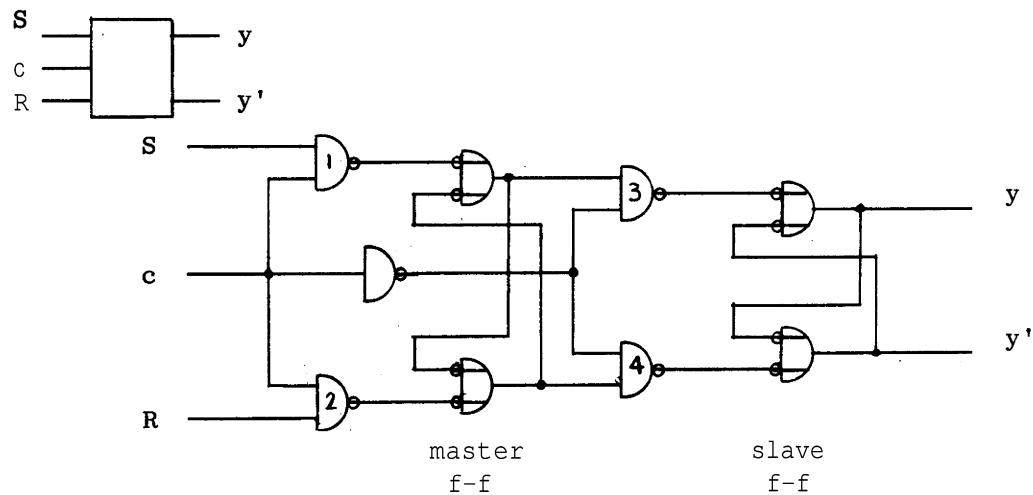

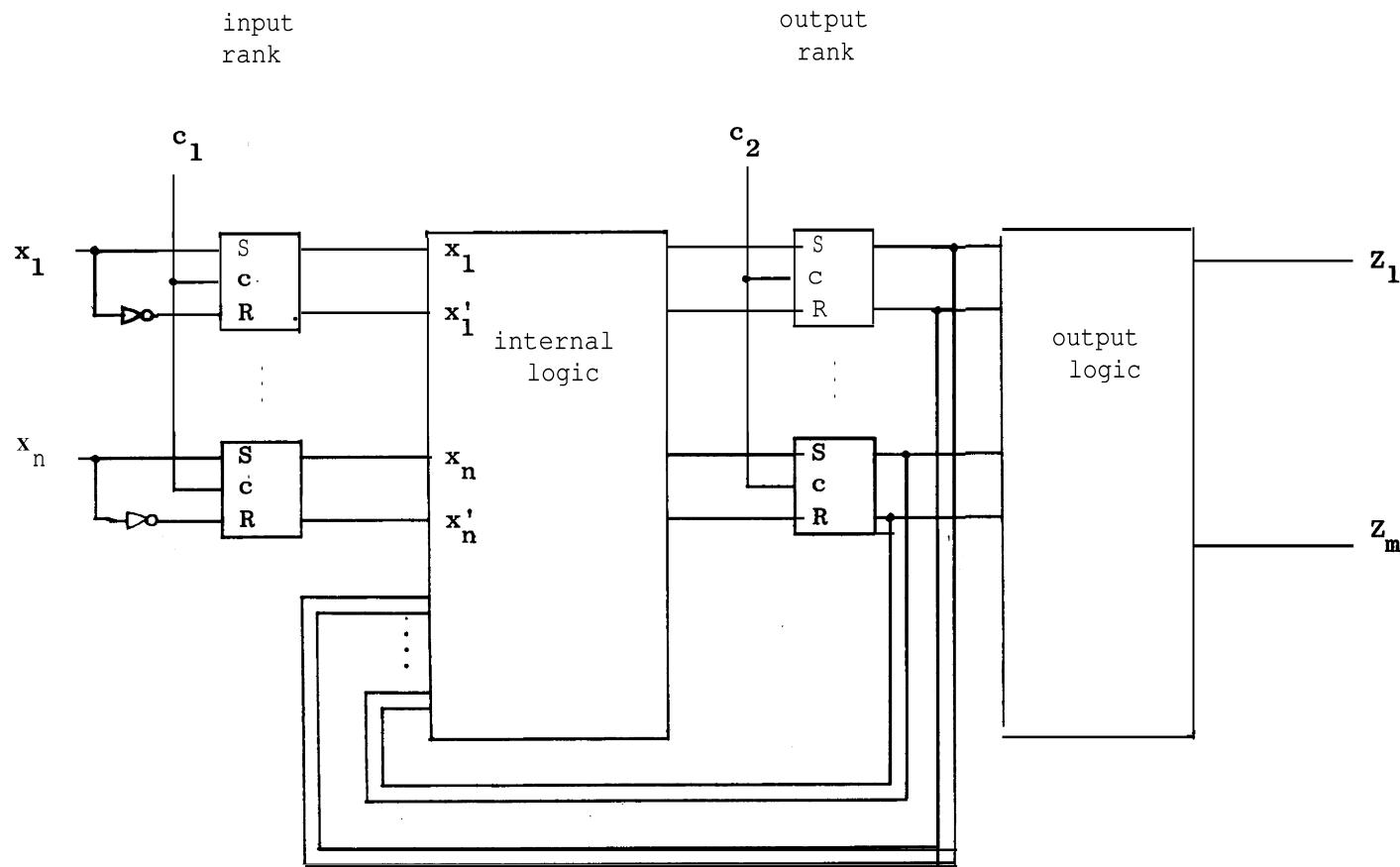

| 8.  | General form for a clocked sequential circuit . . . . . , . . . . .                                                                  | 39 |

| 9.  | General form of a component circuit . . . . . . . . .                                                                                | 41 |

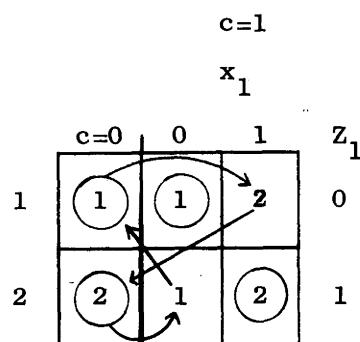

| 10. | Flow tables with and without clock inputs . . . . . . . . . . .                                                                      | 43 |

| 11. | Control circuit for the two-process 'mutual exclusion problem . . . . . . . . .                                                      | 50 |

## INTRODUCTION

A computer system can be viewed as a collection of programs, which are sets of instructions to be executed by processors, and logic circuits, sets of logic gates and flip-flops interconnected by wires. Much effort has been expended on the development of formal design procedures for logic circuits resulting in the body of knowledge known as switching theory. This theory provides procedures for circuit analysis, the determination of what a particular circuit does, and circuit synthesis, the design of a circuit to accomplish some task. Unfortunately, designers of computer systems do not have similar techniques available to them. These techniques would allow programs and circuits to be treated in common framework and would make it possible to analyze a system formally, without expensive testing and debugging, to determine what the system does. They would help a designer decide whether a circuit or program implementation is most appropriate. The ability to consider both hardware and software implementations is particularly important in the design of operating systems where there is often a choice between a program or circuit implementation. In this paper, a model is proposed for parallel computer systems which it is hoped will aid in the fulfillment of these objectives. The model depends on the use of fundamental-mode flow tables, used previously to design sequential **circuits** [ 23 ], to describe the operation of both program and circuit components.

To motivate the need for such a model and to illustrate the difficulties involved in describing the operation of a computer system, let us consider a well known problem which occurs in multi-processor computer systems. This problem, called the mutual exclusion or interlock problem, occurs when two or more processes are active simultaneously. Such processes are called concurrent processes. The use of the term process implies that some component in the system is active, performing a task. The activity of the component distinguishes a process from a processor. A processor is an entity which has the capability of performing a task. A further discussion of the distinction between a process and a processor is given by Dennis and Van Horn [ 5 ], Dijkstra [ 6 , 7 , 8 ], Saltzer [ 26 ], and Lampson [ 19 ]. In the mutual exclusion problem, each process is assumed to contain certain special operations in a portion of the process known as a critical section. The processes usually represent the execution of programs containing infinite loops in which they enter, leave, and then re-enter their critical sections. The mutual exclusion problem requires the specification of a control mechanism to prevent two or more processes from entering their critical sections simultaneously. In addition, it must be guaranteed that, if one process wants to enter its critical section, the process cannot be blocked by other processes entering, leaving, and then re-entering their critical sections. Knuth [ 18 ] has shown that this latter possibility exists in one control algorithm proposed for the mutual exclusion problem. The exact nature or content of a critical section

is not important in the development of a solution to the problem. Typically, critical sections modify common storage files or system tables. A precise statement of the mutual exclusion problem for two processes is given below.

Problem: (Mutual Exclusion)

Given two concurrent processes, each containing a critical section, control these processes so that the following two restrictions are always satisfied.

Restriction 1: At most one process is in a critical section, at any instant.

Restriction 2: If a process wants to enter its critical section, it is eventually allowed to do so.

This problem is slightly different from the one Dijkstra posed. He wanted to ensure that the decision as to which process enters its critical section cannot be postponed indefinitely. While a decision must always be made, a particular program may be blocked indefinitely.

Many solutions have been proposed to this problem [ 5 , 6 , 7 , , 8 , 18 , 19 ]. Most of these solutions depend on the existence of special instructions which are executed whenever a process wants to enter its critical section. Examples of these instructions are the Test-and-Set instruction which- is a machine instruction for the IBM 360 series computers [ 14 ], the LOCK and UNLOCK statements for high level languages like FORTRAN and ALGOL discussed by Dennis and Van Horn [ 5 ], and the P and V operations proposed by Dijkstra [ 7 , 8 ]. Two programs using Dijkstra's P and V operations to achieve exclusive access to their critical sections are shown in Table 1. The programs are specified in a version of the ALGOL programming

Table 1. Dijkstra's P, V Solution to the Mutual Exclusion Problem

```

BEGIN INTEGER S;           S := 1;

PARBEGIN

PROCESS 1: BEGIN

L1:    P(S) ;

CRITICAL SECTION 1;

V(S);

REMAINDER OF PROCESS 1;

GO TO L1;

END;

PROCESS 2: BEGIN

L2:    P(S) ;

CRITICAL SECTION 2;

V(S) ;

REMAINDER OF PROCESS 2;

GO TO L2;

END

PAREN

-END.

```

language. The integer variable  $S$  is called a semaphore. We will describe the solution for two processes although it can be generalized to handle an arbitrary number of processes. For two programs, the semaphore variable takes on only two values, 1 and 0. When  $S=1$ , neither process is in its critical section and when  $S=0$ , one of the processes is in its critical section. The identifiers PARBEGIN and PAREND were introduced by Dijkstra to denote that every statement appearing between these two identifiers can be executed concurrently. This is Dijkstra's version of the FORK and JOIN statements proposed by Conway [ 4 ] and others. The P operation or statement is performed on a semaphore variable and has the following effect. If the value of  $S$  is 1,  $S$  is set to 0 and the next statement is executed. If  $S$  is 0, the process must "wait" until  $S$  becomes 1 before it may proceed. The V operation is also performed on a semaphore variable and increases the value of the variable by 1. For two processes,  $V(S)$  is equivalent to setting the value of  $S$  to 1. There are two **possible** forms of activity while a process waits for a semaphore to become 1. The process may go into a tight loop repeatedly executing the  $P(S)$  operation until  $S$  becomes 1. This form of waiting is called "busy waiting" since a processor must be assigned to the process continuously. In the other form of waiting, the process is added to a queue associated with the semaphore where it resides until the semaphore becomes 1. In this case, when a  $V$  operation is performed, the queue for the appropriate semaphore variable must be examined and any process which is eligible to proceed restarted. This form

of waiting allows the processor associated with the idle process to be freed to execute other processes.

Dijkstra makes the following two assumptions about the P and V operations.

1. The P and V operations are indivisible. That is, it is impossible for one P or V operation to be initiated and then for another P or V operation to be initiated before the first is complete.

2. P and V operations may not be executed simultaneously.

Given these two assumptions, Dijkstra proceeds to analyze the behavior of the system containing the two processes and concludes that the mutual exclusion problem has been correctly solved although he does not claim that the analysis presented is formal.

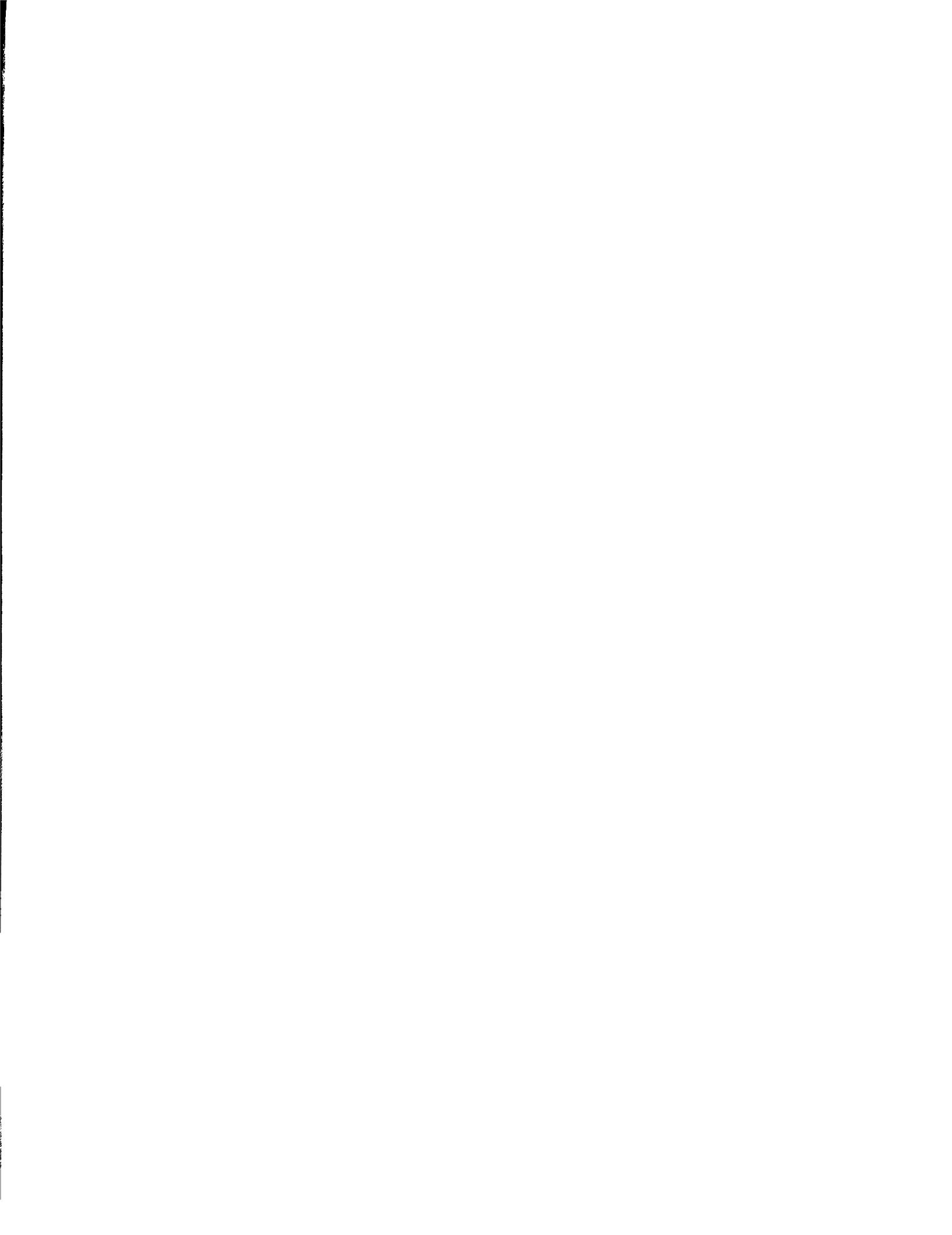

**Dijkstra's** conclusions are hard to accept for several reasons. First, he has not said enough about the system environment to determine if the P and V operations will work. The situation is **described** in Fig. 1. Each process is able to read and change the value of the semaphore S. Dijkstra does not say whether he intends the system to operate in a synchronous manner under the control of a master clock or whether the components in some way operate **independently**. It is important to account for delays which may be present in the environment. These delays may be in the lines over which processes access the semaphore variables and also in the processes themselves. It is possible in a physical system for operations to occur simultaneously and this possibility should not be dismissed

Figure'1. System configuration for **Dijkstra's** mutual exclusion problem solution.

by simply assuming simultaneous interactions do not occur. Any analysis procedure or model should consider all possible variations in timing of system operations. Another objection is that Dijkstra has solved the mutual exclusion problem for programs by presenting another mutual exclusion problem which must be solved in the logic circuits of the system. In order to guarantee that the assumptions about the indivisibility of the operations and the absence of simultaneous P and V executions hold, another mutual exclusion problem, nearly identical to the one presented earlier mutual exclusion must be solved. In fact, the statement of the problem given will suffice if we replace the words "critical section" by "P or V operation".

We do not intend to be overly critical of Dijkstra's work. Other published solutions to the mutual exclusion problem depend on the exclusive execution of some primitive operation. A possible exception is the work of Clark [ 3 ]; however, we are not aware of the details of their implementation. We feel that there remain unanswered questions and a need for more work in this area. In this and subsequent papers, we discuss a new approach to the study of parallel systems. Methods based on the use of flow tables are presented which allow circuits and programs to be described in a common framework. These methods permit the formal analysis of the operation of systems of the type we have just described and make it possible to consider the effects of delays. They are applicable in the synthesis of solutions to problems such as the mutual exclusion problem. A

mode of operation is described for parallel systems which does not depend on synchronous operation or the exclusive execution of any primitive operations.

## PARALLEL SYSTEMS

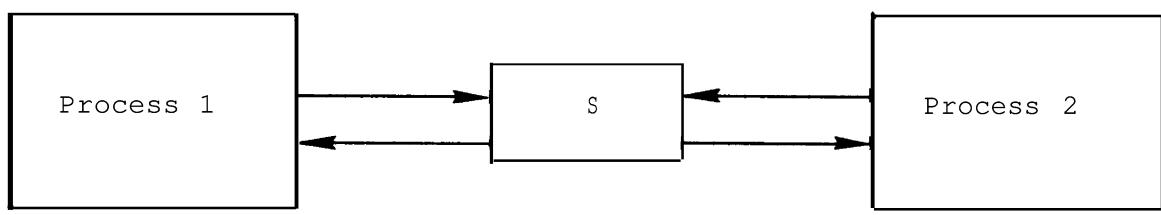

A diagram of a portion of a possible system configuration is shown in Fig. 2. The square boxes represent system components. These components may be programs or circuits. The operation of a circuit or the execution of a program is referred to as a process in the sense used in the introduction.. Some of the components may act as control mechanisms which enable and disable other components. Each interconnecting line represents a physical wire which carries a binary level signal. Each line has associated with it a direction of propagation for transmission of signal value changes from the output of one component to the input of another. The direction of propagation is indicated by arrowheads in the system diagram.

The operation of the system can be described in a general way as follows. Whenever a process wants to perform an operation that could affect other processes, the process requests permission to perform the operation from a control mechanism. The permission has the form of an enabling signal sent from the control mechanism to the process. It is the responsibility of the control mechanism to ensure that no situation arises that violates restrictions placed on system operation. One control mechanism can seek authorization

Figure 2. Typical parallel system configuration.

for an action from another control mechanism and there need be no central control mechanism responsible for the operation of the entire system.

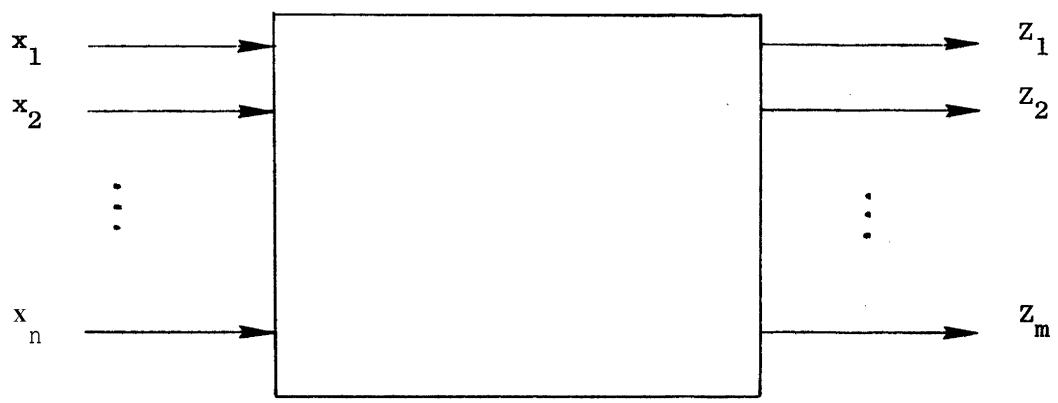

The general form of a system component is shown in Fig. 3. The component has  $n$  input lines and  $m$  output lines. Each input line has an associated input variable  $x_i$ ,  $i = 1, \dots, n$ . The values of the input variables define the input state of the component.

, Each input variable has two possible values, 0 and 1. Each component produces outputs which are also binary signals. Each output line has an associated output variable or excitation variable  $z_i$ ,  $i = 1, \dots, m$ . The values of the output variables define the output state of the component. Each input and output line is connected to exactly one other component.

#### FLOW TABLES

In any model of computer systems, it is necessary to be able to describe precisely the operation of each system component. Many models of parallel computations and parallel computer systems have been proposed in which functions are used to describe component behavior [ 1 , 2 , 15 , 16 , 17 , 20 , 21 , 22 , 24 , 25 , 27 ]. These functions define mappings of component input states into output states. This approach has the advantage of complete generality in the types of component behavior that can be described. Any operation that can be described by a mathematical function can be represented.

Figure 3. General form of a component.

There are several disadvantages associated with this approach **however**.

First, most of the interesting properties of the system, such as whether or not the system ever halts or whether one system is equivalent to another, are undecidable. That is, there do not exist algorithms which determine for any arbitrary system if the system ever halts or for two arbitrary systems, if they do the same thing. A second disadvantage is that the function does not necessarily describe the program or circuit that implements the function.

The model we propose uses flow tables rather than functions to describe component operation. Flow tables were first introduced by **Huffman** [ 13 ] and are normally used in the design of sequential switching circuits [ 23 ]. There is a direct correspondence between a sequential circuit and a flow table. In another paper, we show that flow tables can be used to describe computer programs and give procedures for constructing the program that corresponds to a given flow table and the flow table that corresponds to a given program. Thus there is a direct correspondence between a program or circuit implementation and flow table used to describe the implementation. This correspondence is two-way. A program or circuit can be analyzed to determine what it does and a flow table solution to a problem can be synthesized or designed and then a program or circuit implementation produced.

A possible disadvantage of using flow tables is that only mathematical functions which require finite internal storage can be described. For example, given a component with two inputs  $x_1$  and  $x_2$  it

is impossible to use a flow table to determine if an arbitrary number of 1-0-1 transitions on the  $x_1$  input is always followed by exactly the same number of 1-0-1 input transitions on the  $x_2$  input. We are interested in the study of interactions among components rather than the types of problems that can be solved using these systems. We feel these interactions are best studied in a model which requires finite storage and will show that problems which arise in **interconnecting** components can be solved using finite techniques. We view a system as a finite collection of components which have a finite number of interconnections and therefore mathematical properties such as termination and equivalence are decidable.

Associated with each component, as shown in Fig. 3, is a flow table of the form shown in Table 2. This table has  $2^n$  columns, one column for each possible input state and  $r$  rows where each row represents an internal state of the component. Each internal state is designated by a unique integer number  $(1, 2, \dots, r)$ . The table entry designated by an internal-state input-state pair specifies the next internal state of the component. If the next-state entry is the same as the present internal state, the entry is called a stable entry and the component (flow table) is said to be in a stable state or stable. If the next-state entry is not the same as the present internal state, the entry is called an unstable entry and the component (flow table) is said to be in an unstable state or unstable. An output state is associated with each internal state. While it is possible for the output state to depend on the

Table 2. General Form of a Flow Table

|                |  | Input State         |  |     |        |  |     |                     |              |            |

|----------------|--|---------------------|--|-----|--------|--|-----|---------------------|--------------|------------|

|                |  | $x_1 x_2 \dots x_n$ |  |     |        |  |     |                     | Output State |            |

|                |  | 00...1              |  |     | 11...1 |  |     | $z_1 z_2 \dots z_m$ |              |            |

| Internal State |  |                     |  |     |        |  |     |                     |              |            |

| i              |  |                     |  | (i) |        |  | j   |                     |              | 10 . . . 0 |

| j              |  |                     |  |     |        |  | (j) |                     |              | 11 . . . 0 |

| r              |  |                     |  |     |        |  |     |                     |              |            |

| S (next state) |  |                     |  |     |        |  |     |                     |              |            |

input state as well as the internal state [ 23 ], this will not be done in this paper. A flow table must satisfy the following restriction. Every unstable entry must specify a next internal state entry which is stable. Thus the table in Table 3a is a flow table but the table of Table 3b is not. To be precise, the following definition of a flow table is given.

-Definition 1:

A flow table is a table with  $2^n$  columns, one for each input state, and  $r$  rows, one for each internal state. Associated with each row is an output state. Each unstable entry must specify a next internal state which is stable.

As a consequence of the fact that the output state is associated with an internal state and since each unstable entry leads directly to a stable entry, it follows that each output variable may change value at most once during any internal state transition.

In order to describe situations such as in Table 3b, we define a state table.

Definition 2:

A state table is a table which is identical to a flow table except that it is not required that every unstable entry specify a next internal state that is stable.

Table 3. a) Flow Table Example    b) Table Which is Not a Flow Table

|   |     | x |   |   |

|---|-----|---|---|---|

|   |     | 0 | 1 | z |

|   |     | 1 | 2 | 0 |

| 1 | (1) |   |   |   |

| 2 | 3   | 0 |   | 1 |

| 3 | 0   | 4 |   | 1 |

| 4 | 1   | 0 |   | 0 |

a)

|   |     | x   |   |   |

|---|-----|-----|---|---|

|   |     | 0   | 1 | z |

|   |     | 1   | 2 | 0 |

| 1 | 0   | 1   | 2 | 0 |

| 2 | 3   | 3   | 3 | 1 |

| 3 | 4   | 0   | 3 | 1 |

| 4 | (4) | (4) | 4 | 0 |

b)

Of course every flow table is also a state table. The distinction between flow tables and state tables has been made previously [ 23 ]. Others do not make this distinction; state tables are not introduced and the term normal flow table is used to describe the case where every transition leads directly to a stable state and each output variable changes at most once during each internal state transition [ 10 , 11 , 28 ].

#### DELAY ASSUMPTIONS

The following assumptions are made about physical delays present in a parallel system.

Assumption 1:

The time for a value change to propagate from a component output to a component input (the line delay) is finite and unbounded.

Assumption 2:

Within a component, the delays are finite and bounded.

The intent of Assumption 1 is that line delays cannot be controlled. If a "pulse" or short 1 value is produced at a component output, it is not assumed that this value necessarily must propagate to a component input. The consequences of these assumptions are explored in this and subsequent papers. It should be noted that if all delays are assumed to be bounded, a "synchronous" solution to the mutual exclusion problem can be obtained in which the maximum delay time is used to determine the basic cycle time for the system. Our line delay **assump-**

is different from that made in other models where line delays are either assumed to be bounded or zero [ 1, 15, 16, 17, 20, 21, 22, 24, 25, 27 ].

#### A FLOW TABLE SOLUTION FOR THE TWO-PROCESS MUTUAL EXCLUSION PROBLEM

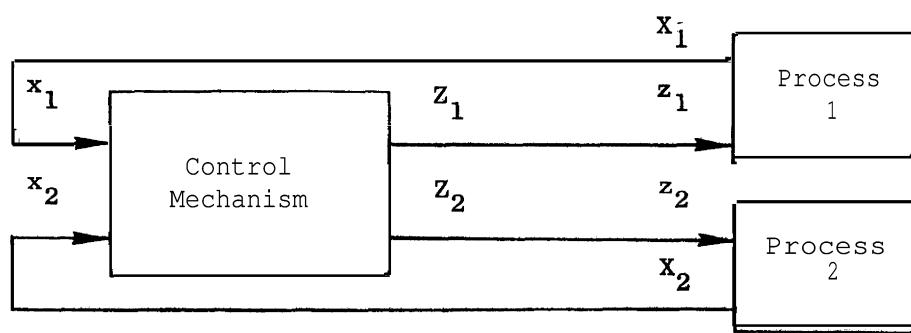

We now return to the two-process mutual exclusion problem discussed in the introduction and use flow table methods to design a solution or control algorithm for this problem. The system configuration is shown in Fig. 4. The variables shown are the input variables for each component. The interpretation of the variable values is given in Table 4. Suppose  $x_1$  and  $z_1$  both have the value 0. When process 1 wants to enter its critical section (CS1), it sets the value of its output variable  $X_1$  to 1. The 1 value eventually reaches the control mechanism input. The control mechanism sets the value of  $z_1$  to 1. This value propagates to the input of process 1, enabling the process to enter its critical section. The sequence of actions on the part of process 1, just described in words, can be described by a flow table. Such a flow table is shown in Table 5a. The process is initially in internal state 1 with input state  $z_1=0$ . Internal state input-state combination will be denoted by a pair of states separated by a dash (-), in this case, 1-0. The 1-0 entry in Table 5a is 2 indicating that eventually this process enters internal state 2. The output state for internal state 2 is  $x_1=1$ . The 2-0 entry is (2), a stable entry. The process remains in this stable state until the input transition  $z_1: 0 \rightarrow 1$  occurs. We assume that a process does

Figure 4. System configuration for the two-process mutual exclusion problem.

Table 4. Interpretation of Variable Values for Fig. 4 (i=1,2)

$x_i = 1$  : process i wants to enter critical section i (**CSi**) or process i is in **CSi**

$x_i = 0$  : process i does not want to enter **CSi** and process i is not in **CSi**

$z_i = 1$  : process i may enter **CSi**

$z_i = 0$  : process i may not enter **CSi**

Table 5. Design of a Flow Table for Process 1.

|   |  | $z_1$    | $x_1$ |   |     |

|---|--|----------|-------|---|-----|

|   |  | 0        | 1     | 0 | 1   |

|   |  | 1        | 2     | 1 | 2   |

| 1 |  | 2        |       | 1 | 2   |

| 2 |  | (2)      |       | 2 | (2) |

|   |  |          |       |   |     |

|   |  | <b>S</b> |       |   |     |

|   |  | (a)      |       |   |     |

|   |  | $z_1$    | $x_1$ |   |     |

|---|--|----------|-------|---|-----|

|   |  | 0        | 1     | 0 | 1   |

|   |  | 1        | 2     | 1 | 2   |

| 1 |  | 2        |       | 1 | 2   |

| 2 |  | (2)      |       | 2 | (2) |

|   |  |          |       |   |     |

|   |  | <b>S</b> |       |   |     |

|   |  | (b)      |       |   |     |

Table 6. Flow Table for Process 2

|   |  | $z_2$    | $x_2$ |   |     |

|---|--|----------|-------|---|-----|

|   |  | 0        | 1     | 0 | 1   |

|   |  | 1        | 2     | 1 | 2   |

| 1 |  | 2        |       | 1 | 2   |

| 2 |  | (2)      | 1     | 2 | (2) |

|   |  |          |       |   |     |

|   |  | <b>S</b> |       |   |     |

not remain in its critical section indefinitely. Therefore the 2-1 entry must be unstable and should be 1 indicating that the process eventually return to internal state 1 where  $x_1$  is set to 0. The unstable transition does not necessarily occur in a short time and, in general, a substantial portion of the operating time of a component may be spent in unstable transitions. The 1-1 entry in the flow table must be 1. This is necessary to ensure that the control mechanism recognizes that process 1 has left its critical section. The control does this by setting  $z_1$  to 0 which eventually enables process 1 to start its cycle again. The complete flow table for process 1 is given in Table 5b. The corresponding flow table for process 2 is given in Table 6.

If the 1-1 entry in Table 5b were 2, the table of Table 7 would be obtained. This table is a state table and not a flow table since the 2-1 entry does not specify a stable state. If this table described the behavior of process 1, it would be possible for both restrictions on the mutual exclusion problem to be violated. First, the  $x_1: 1 \rightarrow 0 \rightarrow 1$  transition could be so short that the 0 value never is recognized by the control. Thus, if process 2 desires to enter its critical section, the control would never realize that process 1 was finished and process 2 would never be enabled violating Restriction 2. On the other hand, if process 2 desires to enter its critical section but is not enabled ( $x_2 = 1$  and  $z_2 = 0$ ) and the 0 value for  $x_1$  appears momentarily and is recognized by the control, the control may disable process 1 ( $z_1 \rightarrow 0$ ) and enable process 2 ( $z_2 \rightarrow 1$ ).

Table 7. An Improper State Table

|   |   | $z_1$ |   |

|---|---|-------|---|

|   |   | 0     | 1 |

|   |   | $x_1$ |   |

| 1 | 0 | 2     | 2 |

|   | 1 | 3     | 1 |

$s$

But process 1 can re-enter its critical section before  $z_1$  becomes 0.

In this case, both processes would be in their critical sections simultaneously violating Restriction 1. This informal analysis is not intended to replace more formal analysis procedures to be presented in a later paper. However, it does point out the advantages of the flow table in making the designer consider all possible state transitions, allowing him to detect and eliminate many potential errors during the synthesis procedure.

Tables 5b and 6 describe the behavior of the two components of the system which contain critical sections. We are now ready to design the control mechanism. The control mechanism has two input variables  $x_1$  and  $x_2$  and four possible input states; therefore, there are four columns in the associated flow table. We require that if neither process is enabled to enter its critical section and if process requests arrive at the control simultaneously, access is given to the process that was not enabled last. Because of this requirement, the control mechanism must "remember" which process was enabled last. Two internal states are required for this purpose. Two more internal states are required, one to produce the enabling signal for process 1 and the other to produce the signal for process 2. Thus a minimum of four internal states are required for the control mechanism.

The usual techniques of flow table synthesis produce first a primitive flow table which has one stable entry in each row. Simplification procedures are then used to eliminate unnecessary internal

states [ 23 ]. To simplify this discussion a flow table with four internal states will be obtained directly. To see how the design proceeds, suppose that neither process is requesting access to its critical section,  $x_1 x_2 = 00$ , and process 2 was in its critical section last. Let the corresponding table entry 1-00 be as shown in Table 8a. The output state is  $Z_1 Z_2 = 00$ , and the control is stable waiting for an input transition. If the transition  $x_1 x_2: 00 \rightarrow 01$  occurs, the control must enter a new internal state where process 2 is enabled, as shown in Table 8b. From 1-00, the transition  $x_1 x_2: 00 \rightarrow 10$  may also occur and process 1 must be enabled, say by internal state 3. If the  $x_1 x_2: 00 \rightarrow 11$  transition occurs while in 1-00, that is, simultaneous requests, state 3 is entered and process 1 is enabled since process 2 was enabled last. Internal state 4 is used to remember that process 1 was enabled last. From 4-00, transitions analogous to those from 1-00 can occur'. The table as specified thus far is shown in Table 8c. Consider the 2-01 entry. In this state, process 2 is requesting access to its critical section and is enabled,  $x_2 = 1$  and  $Z_2 = 1$ . There are three possible input transitions,  $x_1 x_2: 01 \rightarrow 11$  or  $01 \rightarrow 00$  or  $01 \rightarrow 10$ . The first indicates that process 1 also desires to enter its critical section and the 2-11 entry is 2 indicating that the control must wait until process 2 leaves its critical section before enabling process 1. Notice that, as defined by the flow table in Table 5b, once  $x_1$  becomes 1, it does not change to 0 until after  $Z_1$ , is set to 1. The  $x_1 x_2: 01 \rightarrow 00$  transition indicates that process 2 has left its critical section.

Table 8. Design of the Control Flow Table' for the Two-Process Mutual Exclusion Problem

|          |  | $x_1 x_2$ |                                                                                   | $z_1 z_2$ |    | $x_1 x_2$ |                                                                                     | $z_1 z_2$ |    |

|----------|--|-----------|-----------------------------------------------------------------------------------|-----------|----|-----------|-------------------------------------------------------------------------------------|-----------|----|

|          |  | 00        | 01                                                                                | 11        | 10 | 00        | 01                                                                                  | 11        | 10 |

|          |  | 00        | 01                                                                                | 11        | 10 | 00        | 01                                                                                  | 11        | 10 |

| (2 last) |  | 1         |  |           |    | 00        |   | 2         |    |

| 1        |  |           |                                                                                   |           |    | 00        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |  |           |    |

| 2        |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    | 01        |                                                                                     |           |    |

|          |  |           |                                                                                   |           |    |           |                                                                                     |           |    |

|          |  | $x_1 x_2$  |           |          |          |           |    | $x_1 x_2$  |           |          |          |           |          |    |  |

|----------|--|------------|-----------|----------|----------|-----------|----|------------|-----------|----------|----------|-----------|----------|----|--|

|          |  | 00         | 01        | 11       | 10       | $z_1 z_2$ |    | 00         | 01        | 11       | 10       | $z_1 z_2$ |          |    |  |

| (2 last) |  | 1          | <b>12</b> | 3        | 3        | 00        |    | 1          | <b>12</b> | 3        | 3        | 00        |          |    |  |

| (2 gets) |  | 2          |           | <b>2</b> | <b>2</b> | 01        |    | 2          | 1         | <b>2</b> | <b>2</b> | <b>3</b>  | 01       |    |  |

| (1 gets) |  | 3          |           |          | <b>3</b> | <b>3</b>  | 10 |            | 3         |          | <b>3</b> | <b>3</b>  | <b>3</b> | 10 |  |

| (1 last) |  | 4          | <b>4</b>  | 2        | 2        | 3         | 00 |            | 4         | <b>4</b> | 2        | 2         | 3        | 00 |  |

|          |  | $S$        |           |          |          |           |    | $S$        |           |          |          |           |          |    |  |

|          |  | <b>(c)</b> |           |          |          |           |    | <b>(d)</b> |           |          |          |           |          |    |  |

In this case, the control return to internal state 1, remembering that process 2 was in its critical section last. The final possibility,  $x_1 x_2: 01 \rightarrow 10$  accounts for the simultaneous occurrence of both of the first two transitions. In this case, the control enters internal state 3 and enables process 1. These transitions are included in Table 8d. From the 2-11 entry, the only possible transition is  $x_1 x_2: 11 \rightarrow 10$ , which takes the control to internal state 3. The transitions from the 3-10 and 3-11 entries are analogous to those from 2-01 and 2-11. The complete control flow table and process flow tables are shown in Table 9. These flow tables describe all possible interactions of the components in this system. The next step in the design process is to produce the actual programs and circuits that implement this system. Before this can be done, it is necessary to discuss in more detail the mode of operation used for system components.

#### BASIC COMFONENT STRUCTURE

We assume that there is no bound on the time for value changes to propagate in lines (Assumption 1); therefore, no global timing constraints can be made on a system and master clocks, which are commonly used to synchronize the operation of digital systems, cannot be relied upon. One approach to the elimination of master clocks utilizes propagation-limited logic [ 12 ]. Extra connections are provided between components. Each component has special inputs which

Table 9. Flow Tables for the Two-Process Mutual Exclusion Problem

| $z_1$ | $x_1$ |

|-------|-------|

| 0     | 2     |

| 1     | (1)   |

(a) Process 1

| $z_2$ | $x_2$ |

|-------|-------|

| 0     | 2     |

| 1     | (1)   |

(b) Process 2

| $x_1 x_2$  | 00  | 01  | 11  | 10  | $z_1 z_2$ |

|------------|-----|-----|-----|-----|-----------|

| (2 last) 1 | (1) | 2   | 3   | 3   | 00        |

| (2 gets) 2 | 1   | (2) | (2) | 3   | 01        |

| (1 gets) 3 | 4   | 2   | (3) | (3) | 10        |

| (1 last) 4 | (4) | 2   | 2   | 3   | 00        |

(c) Control

determine when the component output values may be changed. Special component outputs are also provided so that a component can notify other components when it is ready to accept new input information.

We propose a structure for components which does not require extra connections such as are used in propagation-limited logic. Extra control connections complicate formal analysis of a system and in the case of the mutual exclusion problem are unnecessary. However, extra circuitry is required to isolate a component from input changes which may occur while the component is responding to an earlier input change. Consider the operation of a fundamental-mode sequential circuit in an environment where line delays are unbounded. Fundamental-mode operation is defined as follows [ 23 ]:

Definition 3:

A sequential circuit is said to be operating in fundamental-mode if and only if all input changes occur when the circuit is stable.

A general form for a sequential circuit with level inputs and level outputs for fundamental-mode operation-is shown in Fig. 5. Set-Reset flip-flops\* are used to store the internal state of the circuit and the output values depend only on the internal state. The internal

---

\* A Set-Reset (S-R) flip-flop has two inputs, S and R, and two outputs, y and y'. When **S=0** and **R=1**, **y=0** and **y'=1**. When **S=1** and **R=0**, **y=1** and **y'=0**. When **S=0** and **R=0**, the output of the flip-flop is determined by the most recent 1 value for S or R. If S and R have 1 values simultaneously, the values of y and y' are arbitrary.

Figure 5. A general form for a sequential circuit using Set-Reset flip-flops.

logic and output logic boxes contain combinational circuits, circuits with no loops in the direction of signal propagation.

Fundamental-mode operation is usually attained by requiring that there be an interval between input value transitions of sufficient duration to allow the circuit to become stable. In our model, if a circuit or component has more than one input, it is possible for the circuitry to be responding to a change on one input line when a change on another input line occurs. Thus, it is not reasonable to assume fundamental-mode operation. To illustrate the difficulties if a circuit in the form of Fig. 5 is not operated in fundamental mode, consider the flow table shown in Table 10. Suppose the present table entry is 1-00 and the input value sequence  $x_1 x_2$ :  $00 \rightarrow 01 \rightarrow 11$  occurs.

One possible internal transition sequence is shown in Fig. 6a and another in Fig. 6b. In the first case, the duration of the 01 input state is sufficient to cause the 2-01 table entry to be entered.

This is not the case in Fig. 6b. As a result, seemingly identical input sequences can produce different internal state transitions and as a **consequence** different output states. Such behavior is not **desirable**. Discussions of these difficulties are concerned with hazards in flow tables and circuits which undergo multiple-input transitions and are beyond the scope of this paper [ 9 , 10 ]. Instead, we define a mode of operation which guarantees that every input transition results in a unique internal-state transition and a unique output-state transition. Before presenting our mode of **operation**, another mode of operation commonly used with sequential circuits

Table 10. Flow Table Example

|   |  | $x_1 x_2$ |     |     |     |           |  |

|---|--|-----------|-----|-----|-----|-----------|--|

|   |  | 00        | 01  | 11  | 10  | $z_1 z_2$ |  |

| 1 |  | (1)       | 2   | 3   | 3   | 00        |  |

| 2 |  | 1         | (2) | (2) | 3   | 01        |  |