Customer Engineering

Manual of Instruction

# 700

Series Data Processing Systems Component Circuits

Book A. General Theory

Book B. 701-704-709 Components

Book C. 702-705 Components

Book D. Auxiliary Equipment

Book E. Appendix

| Department or Branch Office | Mand, CE     | Telepho<br>Number | ne M:90571 |

|-----------------------------|--------------|-------------------|------------|

| Address 210-21              | Z E. mai 89. | _City Su          | State VA   |

| Home Address                |              | City              | State      |

© 1955, 1956, 1957 by

International Business Machines Corporation

590 Madison Avenue, New York 22, N.Y.

Printed in U. S. A.

Form 22-6746-0

#### **FOREWORD**

This manual is written at a level that assumes the reader has a background of basic electronics. The text material is not written from a standpoint of design but rather from a standpoint of the circuit understanding that is necessary for servicing. Where design information is deemed necessary, it is included. For those who feel a need for review, the Appendix (Book E) contains formulas and procedures necessary for simple computations of voltage levels and currents flowing in the circuits. Book E also contains some design procedures for those who want more material on this subject.

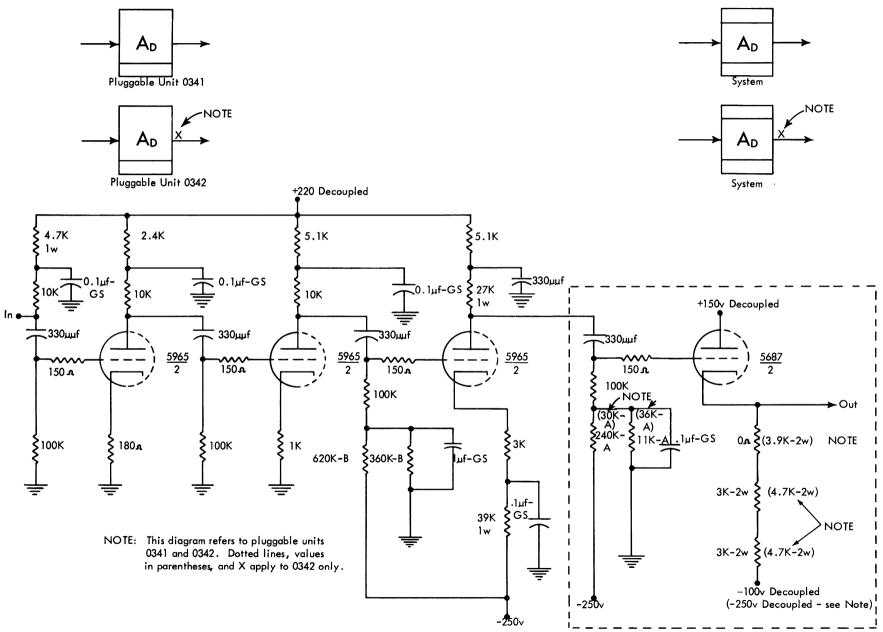

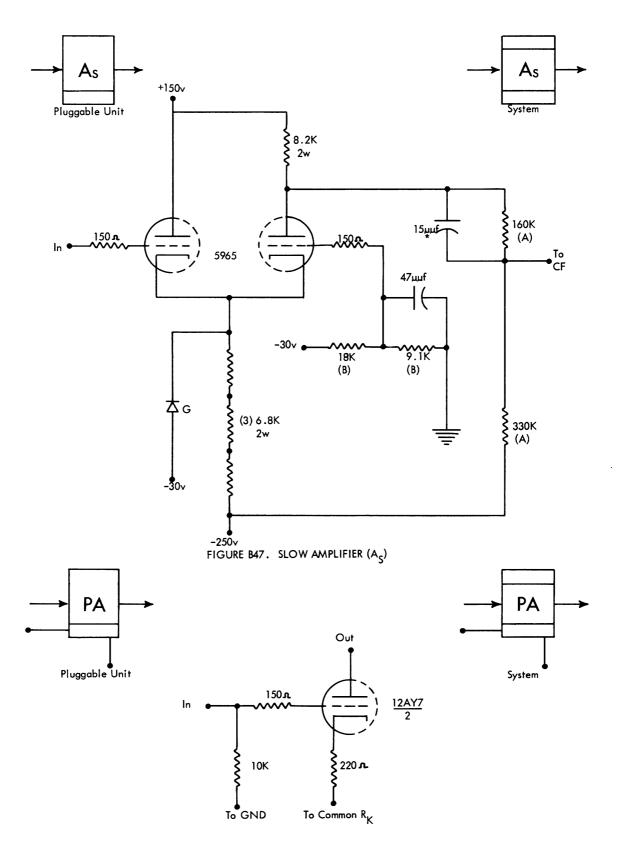

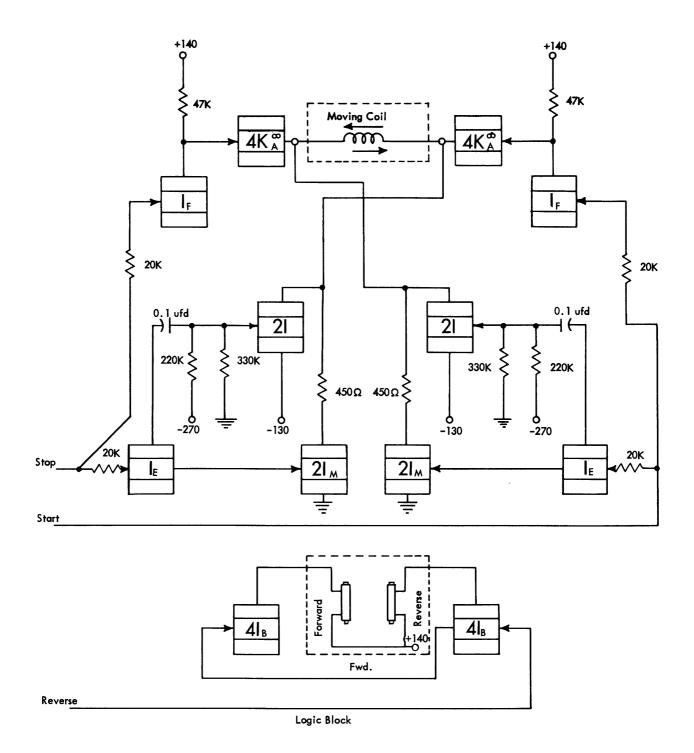

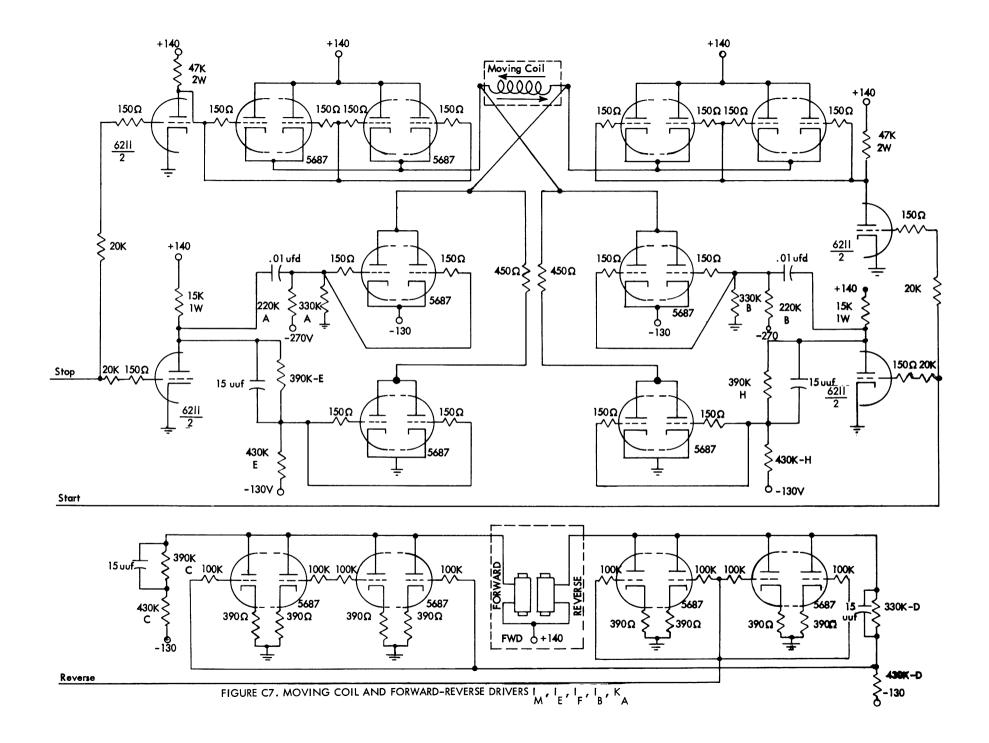

Data-processing machines, such as the 700 series machines, contain many thousands of individual electronic components (resistors, capacitors, inductors, electron tubes, crystal diodes, and so on). Together, they form the "nerve system" of the calculator. Because of the complexity of showing the miles of circuits that make up these machines, the logic block method of circuit layout is used. Logic blocks simplify circuit tracing and trouble shooting. Each logic block represents an individual circuit. Each circuit has a specific function in the area where it is used. With the logic block method, circuits are easily identified and the location of each component is easily found. The following pages contain the logic blocks of component circuits, the circuit schematics, their purpose, how the circuits function, the inputs, and the resultant nominal outputs of these circuits. Given voltage levels and wave forms are suggested values only, as loading conditions affect individual circuits in the machine.

This manual is divided into five main books.

<u>Book A</u> contains information that is pertinent to all component circuits and should be studied before investigating any individual circuit. The location procedure is described early in the manual so that it may be reviewed with each circuit until it is fully understood.

Book A also describes circuits that are popularly called basic or standard circuits. Because these circuits are most commonly used, a thorough study of them helps the customer engineer in understanding the remaining circuits. For this reason, they are explained in greater detail than circuits that are merely modifications of the standard circuits.

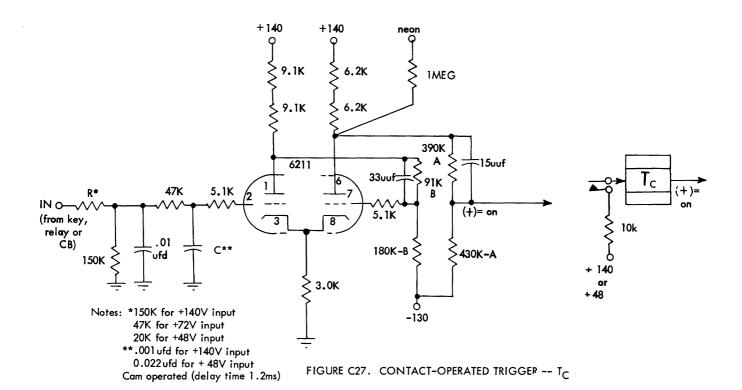

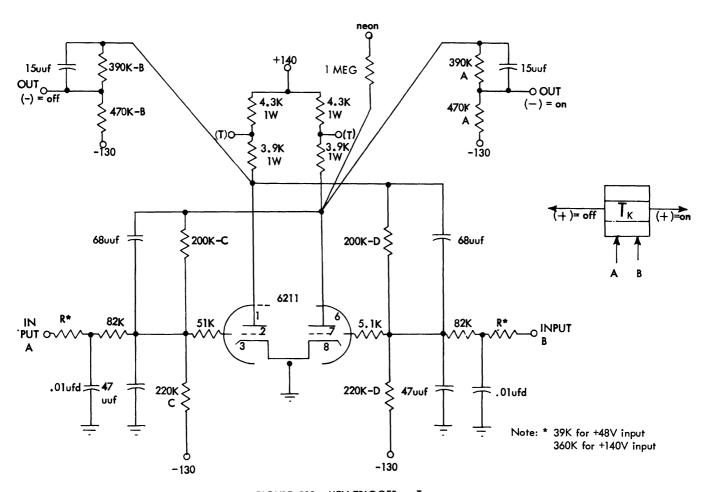

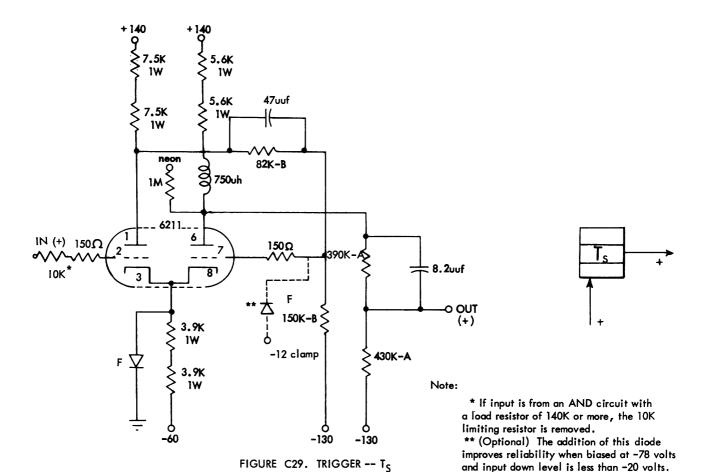

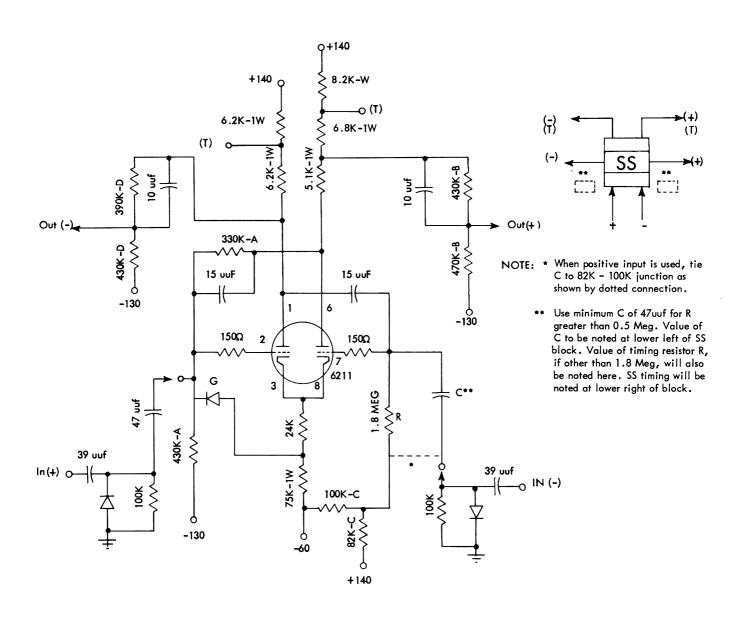

Book B contains information about the pluggable unit panels, the systems block diagrams and the MF neon locations peculiar to the 701, 704, and 709 machines. It also has a complete listing of component circuits assigned to the 701, 704, and 709 systems except power supply and transistor components. Every circuit listed in this book is cross-referred to the "4" pages of machine systems, e.g., inverter I (section 2.01.01, Book B) is the same as 4.01.01 and key trigger  $T_K$  (section 2.02.05, Book B) is the same as 4.02.05. Wherever advisable, the reader is referred to Book A for a more detailed description of the circuit.

<u>Book C</u> contains information about the 702 and 705 systems' pluggable unit panels, edge connectors, circuit locations and panel designations.

Also, this book contains a complete listing of component circuits except power supply components. The basic circuits are duplicated here, with the reader referred to Book A for a complete description. This duplication is made so that circuits listed in this section can have cross reference to the "C" pages of machine systems. ("C" pages contain circuit schematic and standard pluggable unit wiring procedure.) An example is the inverter I (section 2.01.01, Book C) which is the same as C.01.01 and key trigger  $T_K$  (section 2.02.04, Book C) which is the same as C.02.04. Circuits that appear in isolated areas such as memory or drum alone are briefly discussed here but full discussion of their usage is found in the respective machine manuals.

<u>Book D</u> contains information and the component circuits for the 700 series auxiliary equipment. The machines described in this book are the 720 Printer, the 760 Control and Record Storage Unit, the 774 Tape Data Selector, and the 777 Tape Record Coordinator

The Appendix,  $\underline{Book\ E}$ , contains detailed component specifications, basic electrical formulas, samples of logic block layouts, and a sample of design procedure.

## NOTICE

The text and illustrations included in the following pages have been prepared for teaching purposes and as an aid for learning the component circuits of the 700 series machines. All material was prepared from information relative to production at a given level. Engineering changes may alter exact timings, logic blocks or component values; therefore, the customer engineer is advised not to use this information alone as a reference manual or servicing aid.

#### **ABBREVIATIONS**

The following abbreviations are used throughout this manual. Component circuits block designations (such as I for inverter) are not included in this list.

| A            | all (cycles)            | inst              | instruction                                      |

|--------------|-------------------------|-------------------|--------------------------------------------------|

| a            | ampere                  | I/O               | input/output                                     |

| AC           | alternating current     | K                 | kilo (10 <sup>3</sup> ) (usually refers to ohms) |

| adr          | address                 | Kc                | kilocycles                                       |

| amp          | amplifier               | L                 | inductor                                         |

| bksp         | backspace               | lt                | left                                             |

| C            | capacitor               | meg               | megohms (10 <sup>6</sup> )                       |

| C            | cycle                   | m                 | milli (10 <sup>-3</sup> )                        |

| CB           | circuit breaker         | MF                | main frame                                       |

| CF           | core frame              | MQ                | multiplier quotient                              |

| CP           | card punch              | $\mathbf{\Omega}$ | ohm                                              |

| CPU          | central processing unit | op                | operation                                        |

| CT           | cycle time              | $\mathbf{Pr}$     | printer                                          |

| CS           | core storage            | Q                 | quotient                                         |

| ctr          | counter                 | R                 | resistance                                       |

| DC           | direct current          | rewd              | rewind                                           |

| DF           | drum frame              | RI                | read-in                                          |

| е            | voltage                 | rt                | right                                            |

| $\mathbf{E}$ | execute (time)          | Rd                | read                                             |

| EC           | edge connector          | S (sec)           | seconds                                          |

| EOF          | end of file             | sw                | switch                                           |

| EOR          | end of record           | stg               | storage                                          |

| f            | farad                   | tgr               | trigger                                          |

| h            | henry                   | u                 | micro $(10^{-6})$                                |

| I            | current                 | uu                | micro-micro $(10^{-12})$                         |

| I            | instruction             | v, V              | volt                                             |

| intlk        | interlock               | $\mathbf{Wr}$     | write                                            |

|              |                         |                   |                                                  |

Component Circuits

Book A. General Theory

# CONTENTS

| Section | Title                               | Symbol    | Page |

|---------|-------------------------------------|-----------|------|

| 1.00.00 | GENERAL INFORMATION                 |           | A 5  |

| 1.01.00 | Definition of Terms                 |           | A 5  |

| 1.02.00 | Pluggable Unit                      |           | A 5  |

| 1.03.00 | Pluggable Unit Location             |           | A 7  |

| 1.04.00 | Pulse Sketches and Wave Forms       |           | A 7  |

| 1.05.00 | Input/Output Levels                 |           | A 9  |

| 1.06.00 | Crystal Diodes                      |           | A 9  |

| 1.07.00 | Electron Tubes                      |           | A10  |

| 1.08.00 | Circuit Delays                      | • • • • • | A11  |

| 2.00.00 | STANDARD CIRCUITS                   |           | A13  |

| 2.01.00 | +AND (-OR) Circuit                  | . A       | A13  |

| 2.01.01 | Circuit Description                 |           | A13  |

| 2.01.02 | Rise/Fall Time                      |           | A15  |

| 2.02.00 | +OR (-AND) Circuit                  | . 0       | A15  |

| 2.02.01 | Circuit Description                 |           | A15  |

| 2.02.02 | Rise/Fall Time                      |           | A17  |

| 2.03.00 | +AND Driving +OR Circuit            |           | A17  |

| 2.03.01 | Circuit Description                 |           | A17  |

| 2.03.02 | Rise/Fall Time                      |           |      |

| 2.04.00 | Diode Cascading                     |           | A19  |

| 2.05.00 | Inverter                            | . I. I    | A23  |

| 2.05.01 | Circuit Description                 | -K        | A23  |

| 2.05.02 | Compensated Output                  |           |      |

| 2.06.00 | Trigger                             | . т       | A27  |

| 2.06.01 | On and Off Convention for Trigger . |           | A27  |

| 2.06.02 | General Trigger Circuit Operation . |           |      |

| 2.06.03 | Specific Components in a Trigger .  |           |      |

| 2.06.04 | Electronic Reset                    |           |      |

| 2.06.05 | Manual Reset                        |           |      |

| 2.06.06 | Inputs to a Trigger                 |           |      |

| 2.06.07 | Input Requirements for the Trigger. |           |      |

| 2.06.08 | Outputs from the Trigger            |           |      |

| 2.06.09 | Voltage Levels in the Trigger       |           |      |

| 2.06.10 | Block Representation of the High-   |           |      |

| 2.00.10 |                                     |           | A34  |

| 2.06.11 | Speed Trigger                       |           |      |

| 2.06.11 | Application of Triggers             |           |      |

| 2.07.00 |                                     |           | 1.00 |

| 2.07.00 | Diode Gate                          |           | A39  |

| 2.07.02 | <del>_</del>                        |           |      |

| 2.01.02 | Variations                          |           |      |

|         | Diode Gate                          |           |      |

| 2.08.01 | Circuit Description                 |           | A41  |

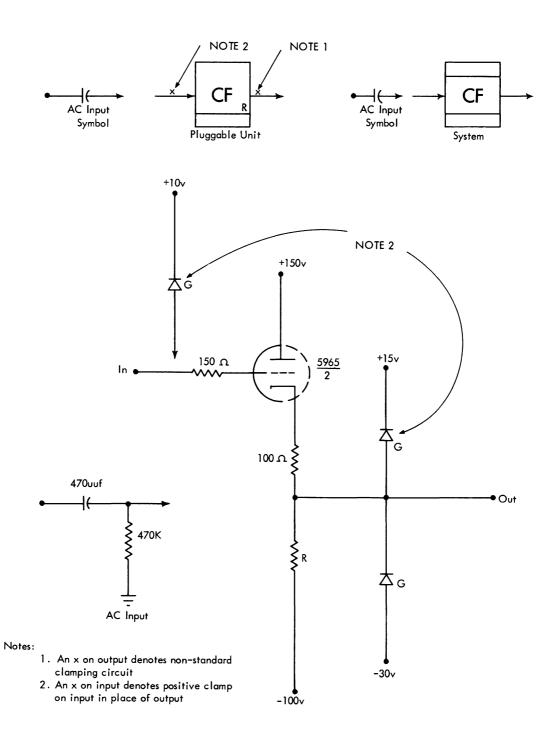

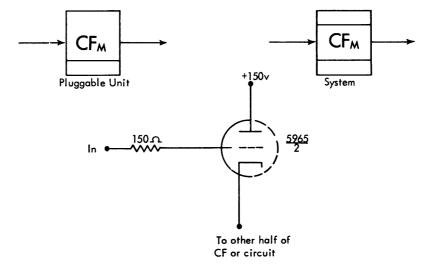

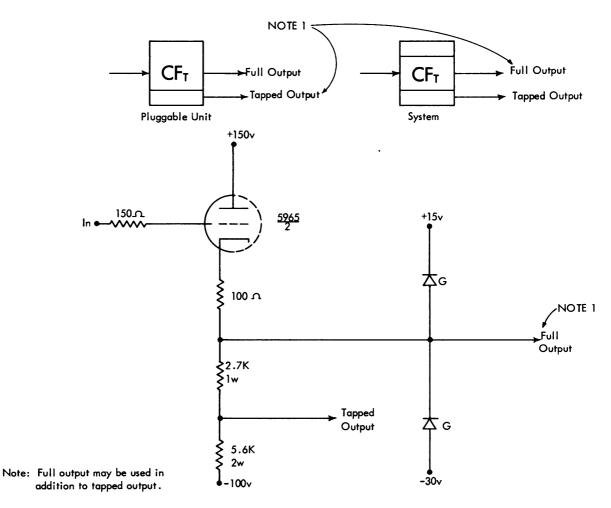

| 2.09.00 | Cathode Follower                    |           |      |

| 2.09.01 | Circuit Description                 |           |      |

| 2.09.02 | Positively Returned Resistive Load. |           |      |

| 2.09.03 | Negatively Returned Resistive Load  |           |      |

| 2.09.04 | Capacitive Load                     |           | A45  |

# CONTENTS (continued)

| Section | Title                                  | Symbol                                  | Page |

|---------|----------------------------------------|-----------------------------------------|------|

| 2.09.05 | Parallel Cathode Follower              |                                         | A45  |

| 2.09.06 | Cathode Follower OR Circuit            |                                         | A46  |

| 2.09.07 | Cathode Follower Inputs                |                                         | A46  |

| 2.09.08 | Summary                                |                                         | A46  |

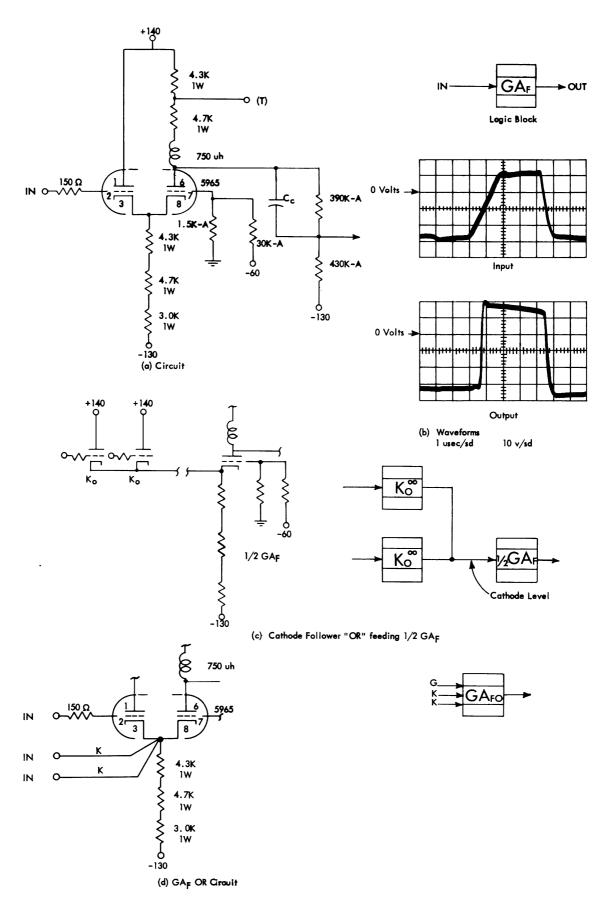

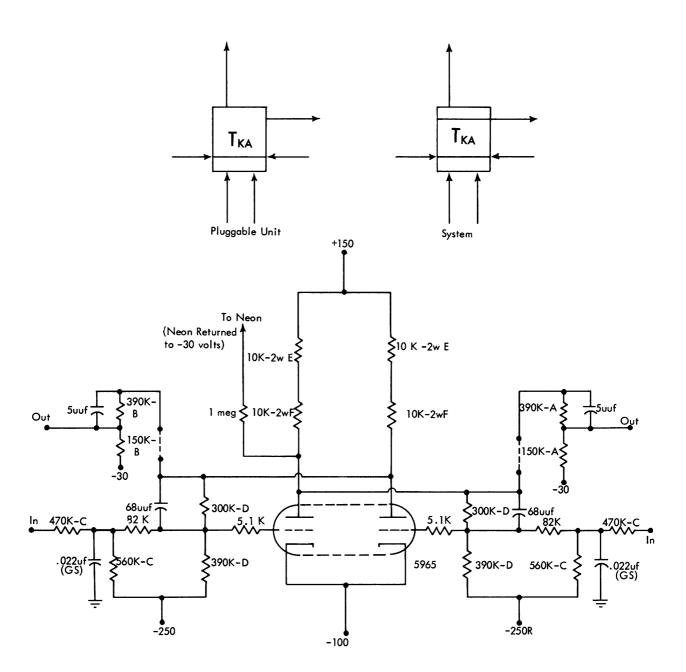

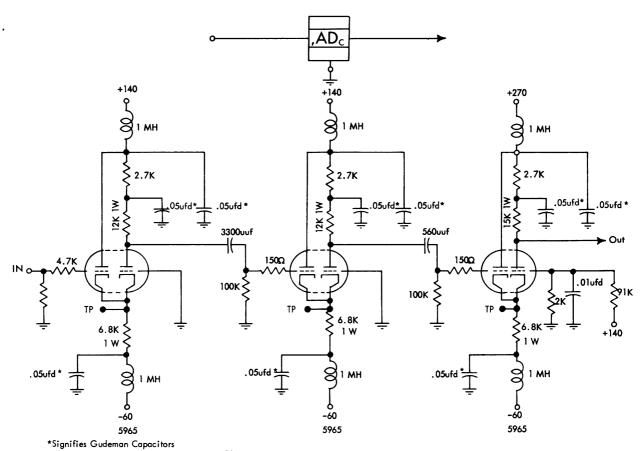

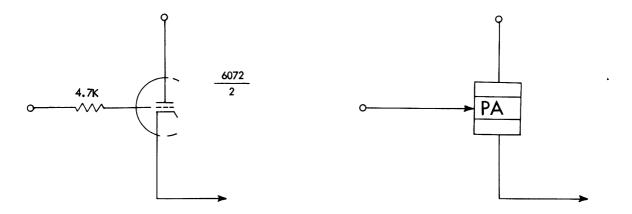

| 2.10.00 | Grounded-Grid Amplifier                | $GA_{r}$                                | A49  |

| 2.10.01 | Circuit Description                    |                                         | A49  |

| 2.10.02 | Variation                              | $1/2 \text{ GA}_{\text{F}}$             | A49  |

| 2.10.03 | Variation                              | GA <sub>FO</sub>                        | A50  |

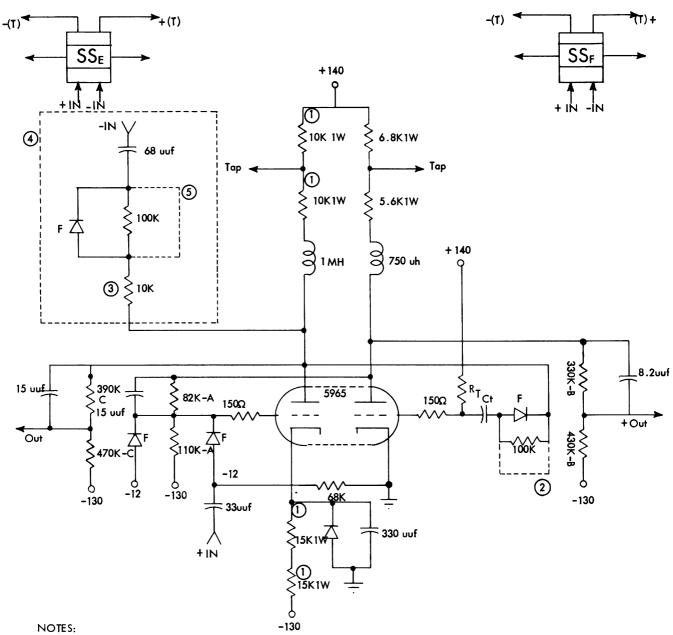

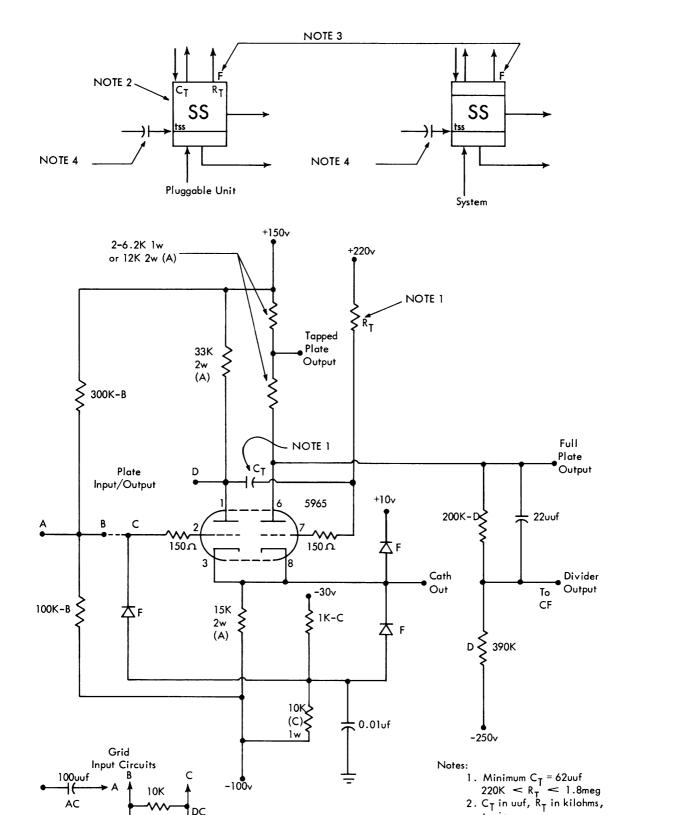

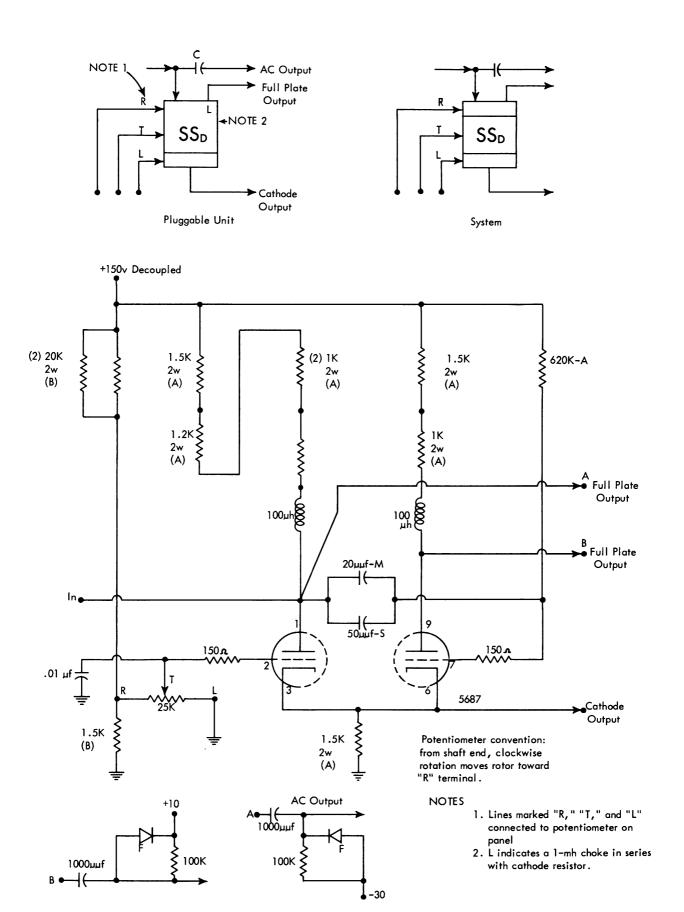

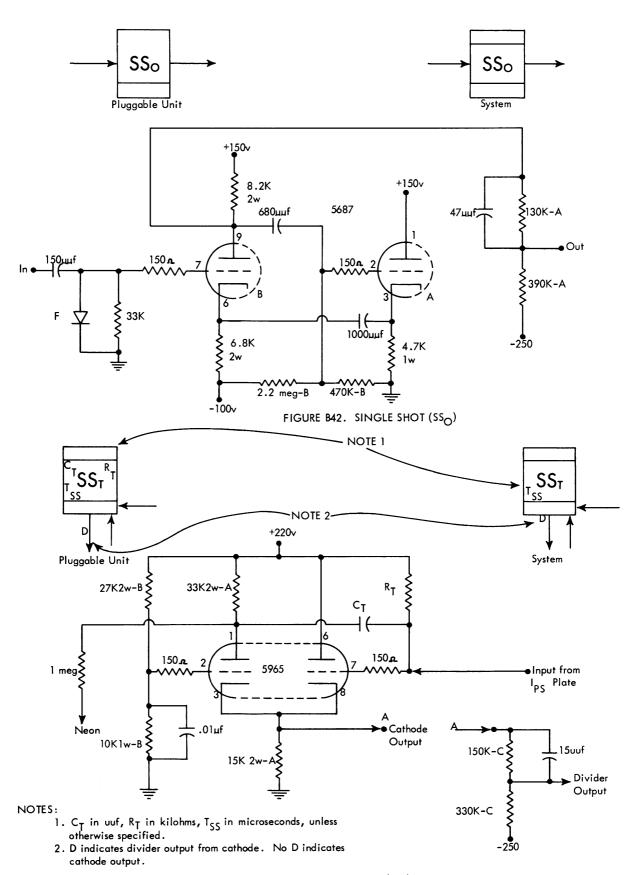

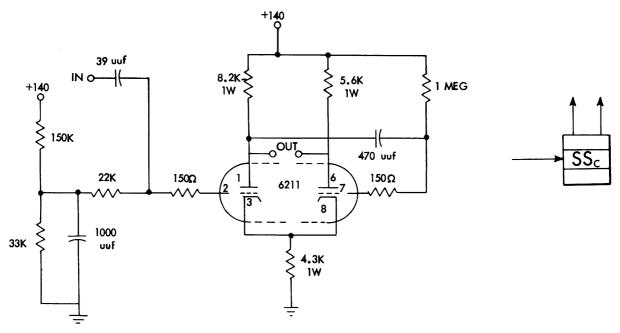

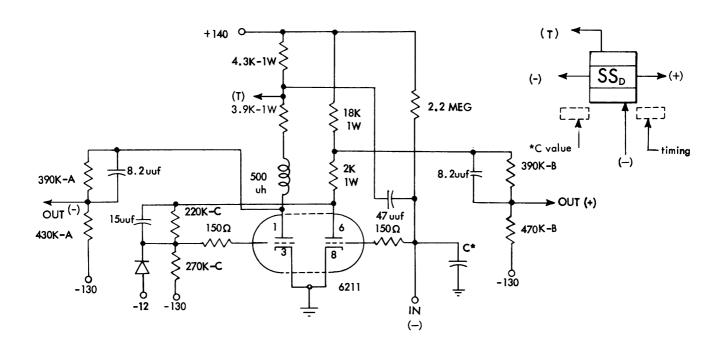

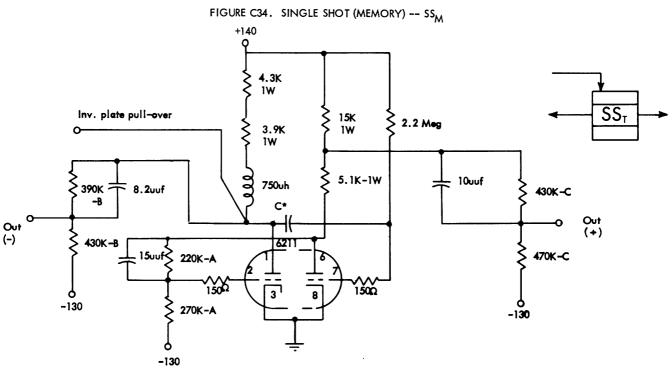

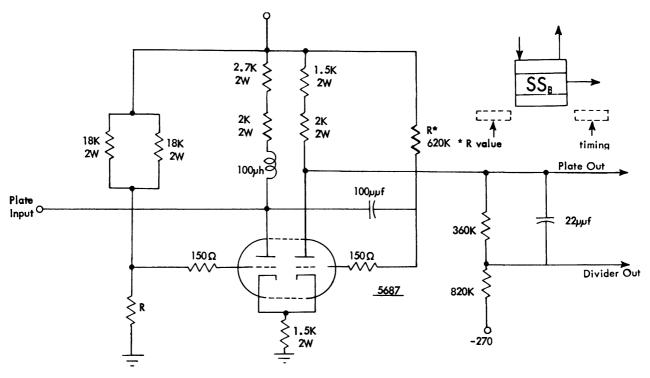

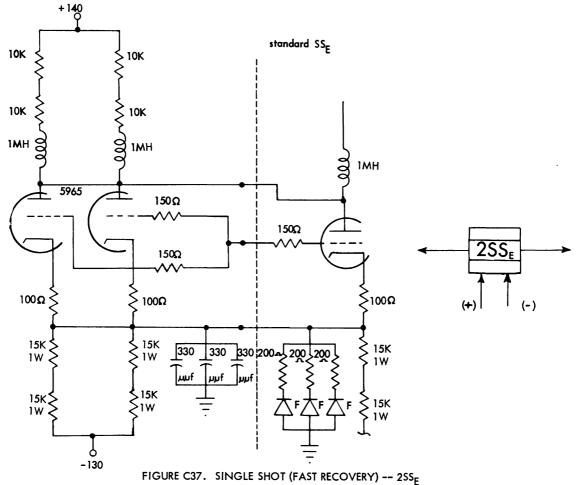

| 2.11.00 | Single Shot                            | $SS_{E}^{1}$                            | A53  |

| 2.11.01 | Circuit Description                    |                                         | A53  |

| 2.11.02 | Recovery Time                          |                                         | A55  |

| 2.11.03 | Timing Accuracy                        |                                         | A55  |

| 2.11.04 | Inputs                                 |                                         | A55  |

| 2.11.05 | Outputs                                |                                         | A55  |

| 2.11.06 | Miscellaneous                          |                                         | A56  |

| 2.11.07 | Variation                              | SS <sub>T</sub>                         | A56  |

| 2.11.08 | Outputs                                | $\mathrm{ss}_{\mathbf{F}}^{\mathbf{r}}$ | A56  |

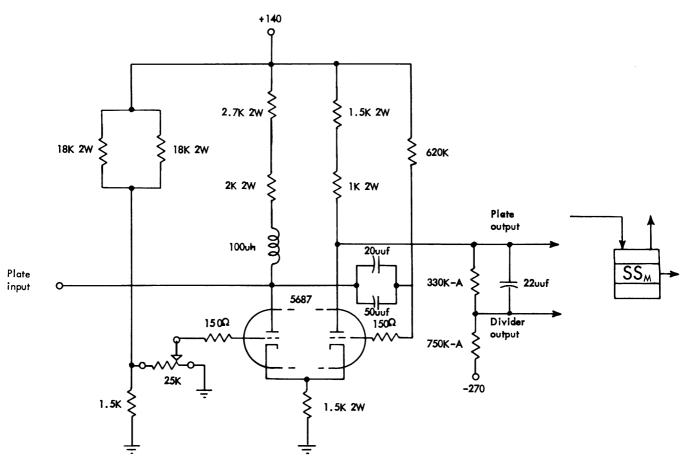

| 2.12.00 | Pulse Forming Inverter                 | Ing                                     | A59  |

| 2.12.01 | Circuit Description                    |                                         | A59  |

| 2.12.02 | Ipr Timing                             |                                         | A59  |

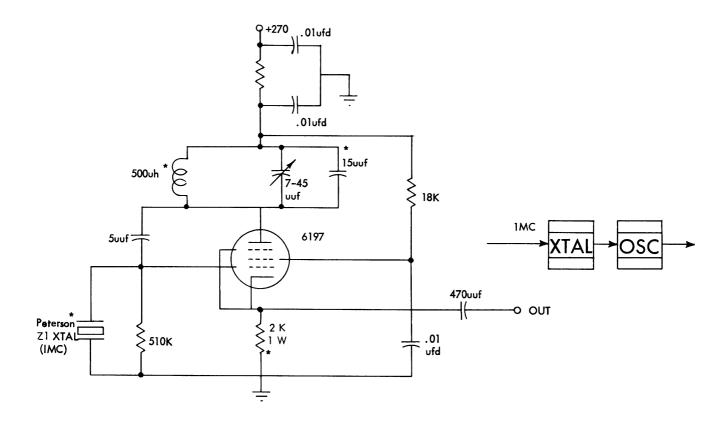

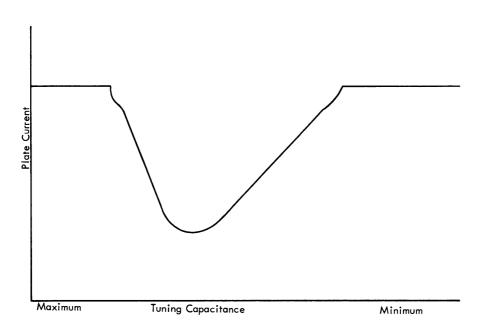

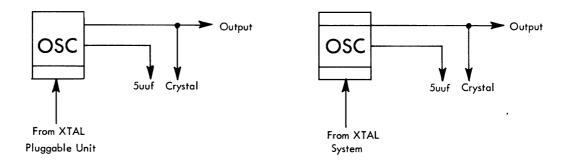

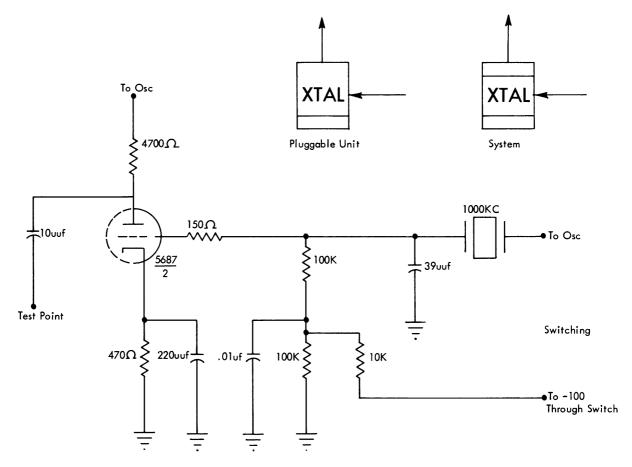

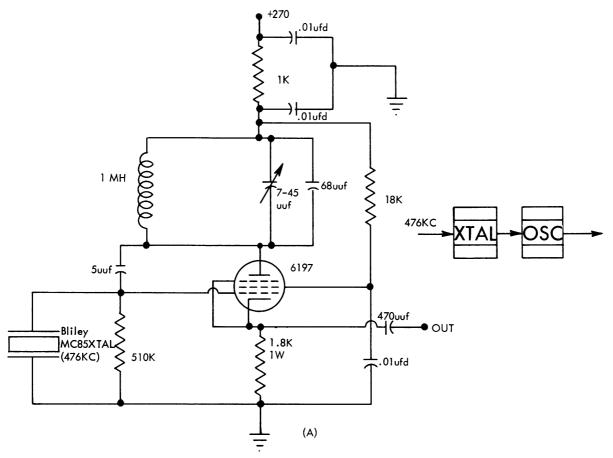

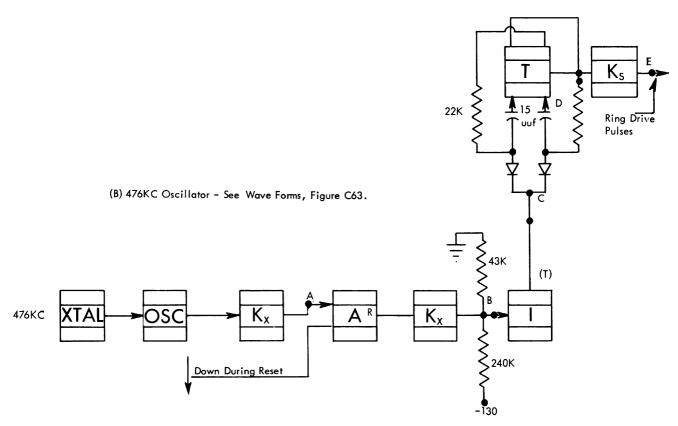

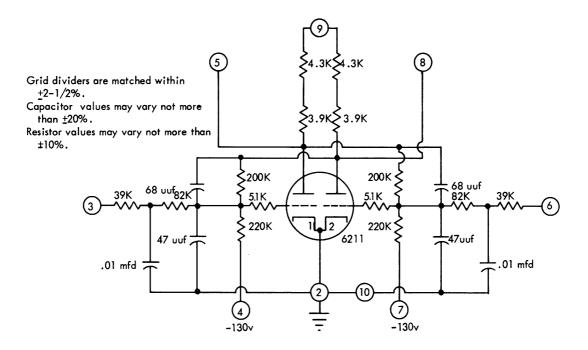

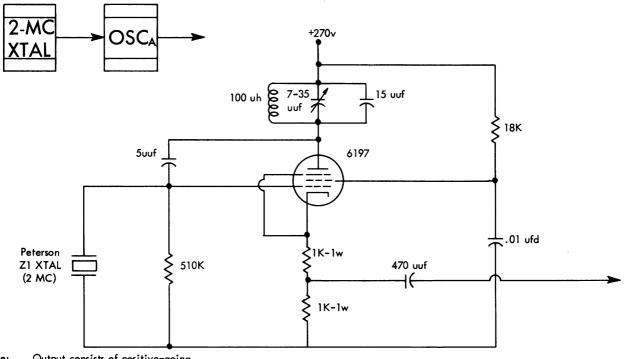

| 2.13.00 | Oscillator (Clock)                     |                                         | A61  |

| 2.13.01 | Circuit Description                    |                                         | A61  |

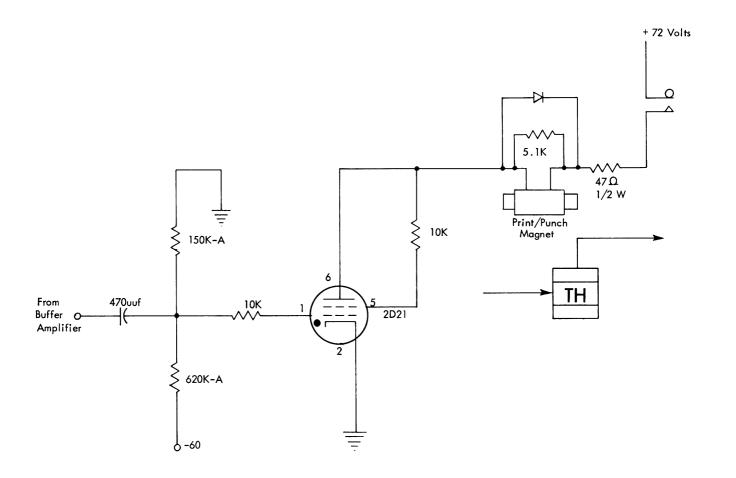

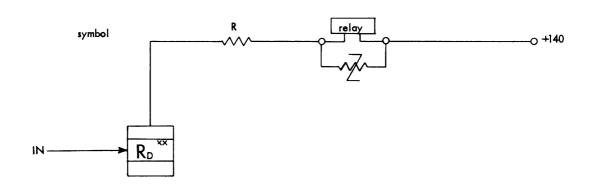

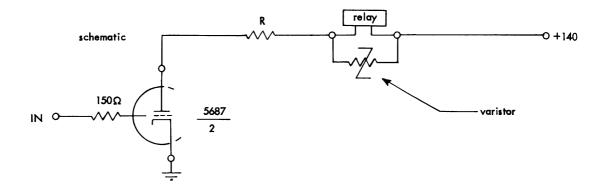

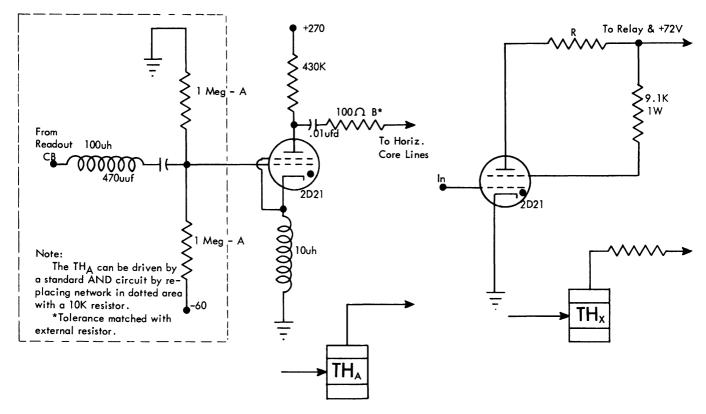

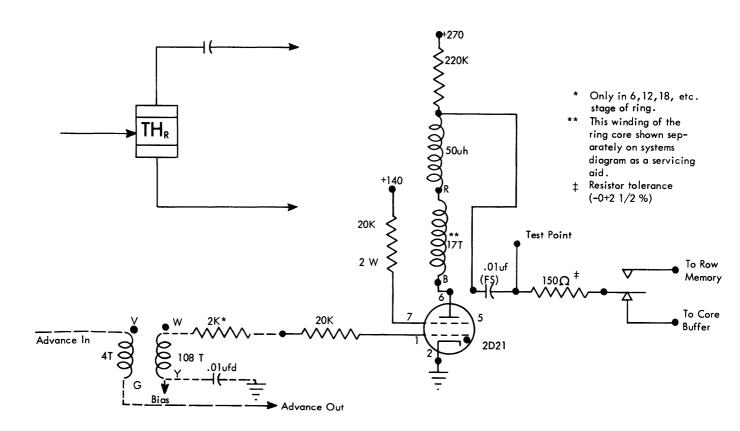

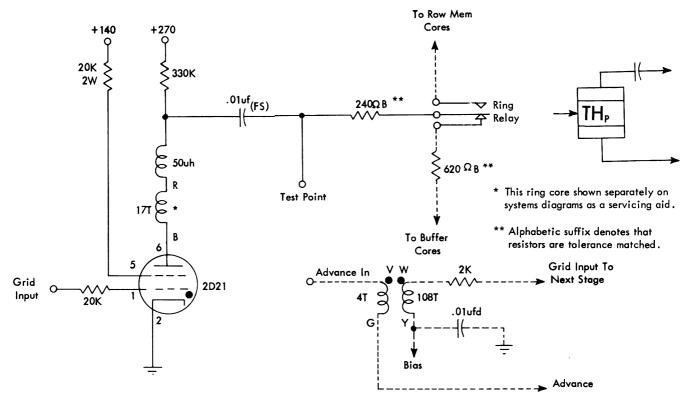

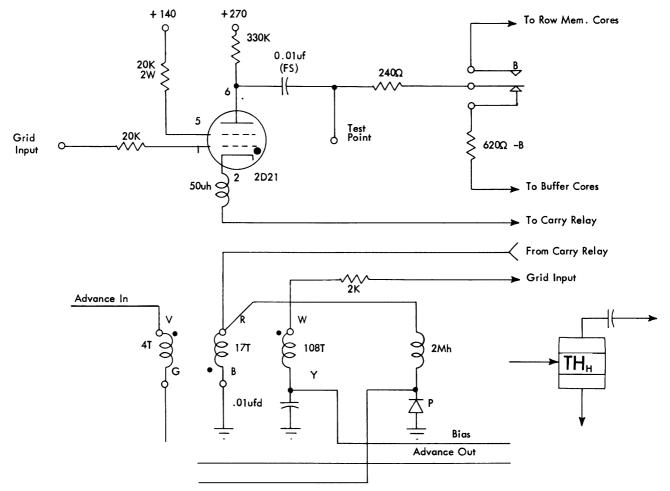

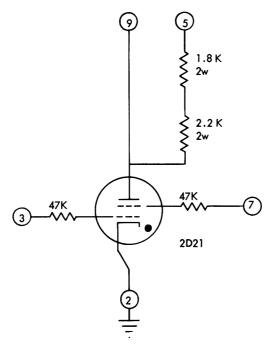

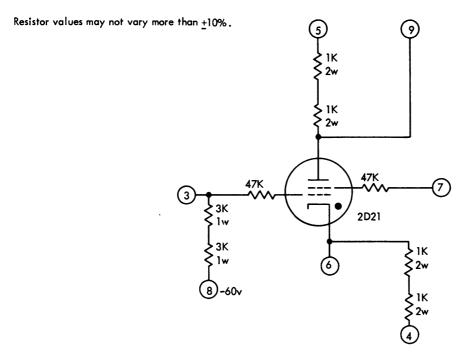

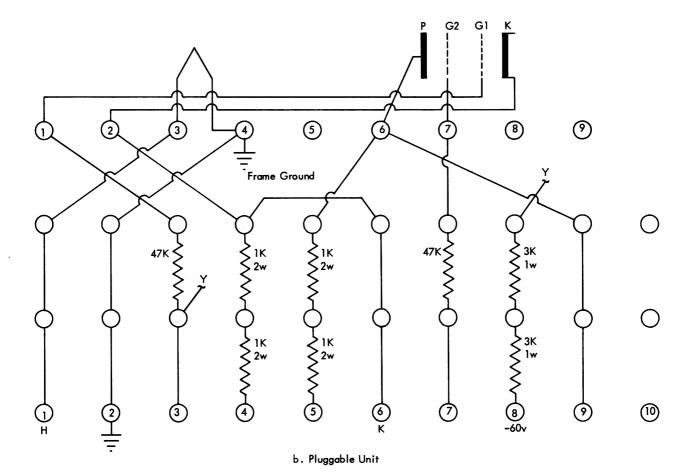

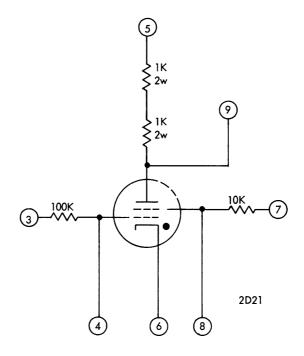

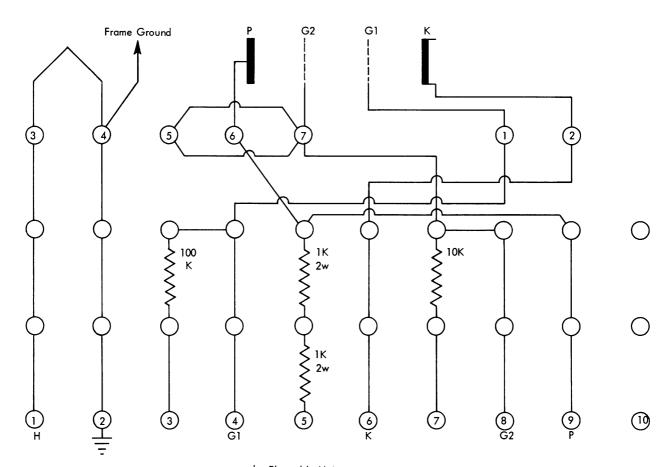

| 2.14.00 | Thyratron Circuits                     |                                         | A62  |

| 2.14.01 | Printer/Punch Magnet Thyratron         |                                         | A63  |

| 2.15.00 | Peaker                                 |                                         | A65  |

| 2.15.01 | Principles of Peaker Circuit Operation |                                         |      |

| 2.15.02 | Wave-Form Generator Peaker             | PKR <sub>7</sub>                        | A66  |

# ILLUSTRATIONS

| Figure     | Title Symbol F                                    | age |

|------------|---------------------------------------------------|-----|

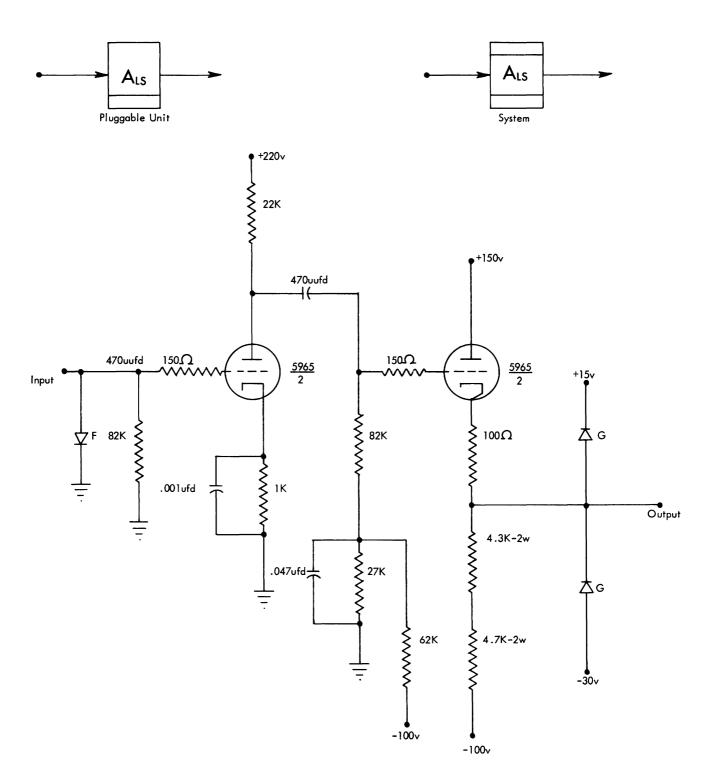

| A1         | Pluggable Unit                                    | 6   |

| A2         | Panels A-D                                        | 8   |

| A3         | Panel A (Wiring Side)                             | 8   |

| A4         | Panel Wiring                                      | 8   |

| <b>A</b> 5 | +AND (-OR) Circuit                                | 12  |

| A6         | +OR (-AND) Circuit                                | 14  |

| A7         | +AND Driving +OR                                  | 116 |

| <b>A</b> 8 | Cascaded +AND Circuit A <sub>C</sub> A            | 18  |

| A9         | Standard Inverter                                 | 122 |

| A10        | High Speed Trigger                                | 26  |

| A11        | Trigger Inputs                                    | 128 |

| A12        | Trigger Inputs                                    | 130 |

| A13        | Self-Gated Binary Input                           | 132 |

| A14        | Trigger Outputs                                   | 32  |

| A15        | Trigger Register                                  | 136 |

| A16        | Leslie Ring                                       | 136 |

| A17        | Trigger Counters                                  | 136 |

| A18        | Diode Gate $D_G$ A                                | 864 |

| A19        |                                                   | 440 |

| A20        | Standard Cathode Follower                         | 42  |

| A21        | Contact Integrating and Differentiating Inputs to |     |

|            | Cathode Followers                                 | 44  |

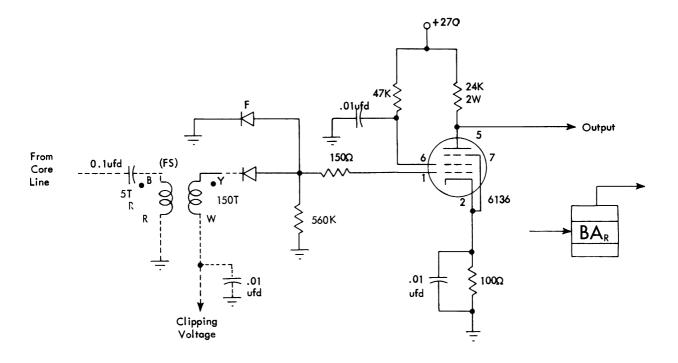

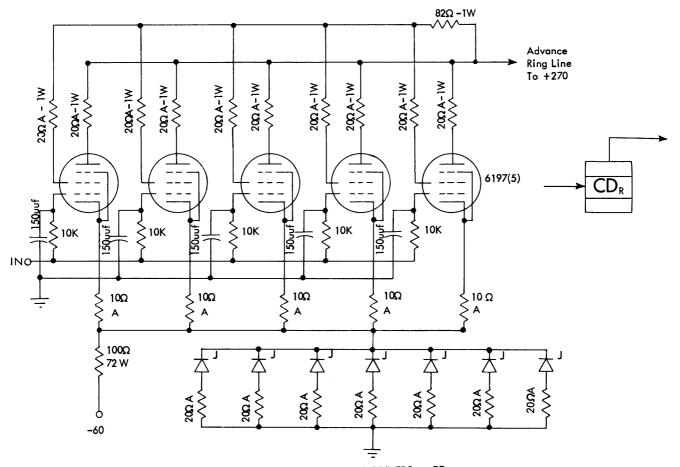

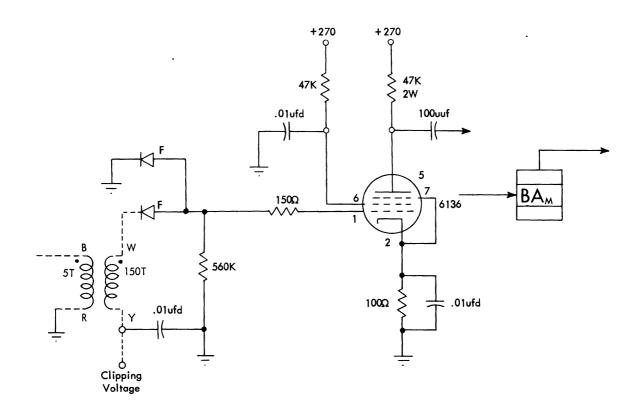

| A22        | Grounded Grid Amplifier (Full Plate) GAF A        | 48  |

| A23        | Single Shots $\cdot$                              | 152 |

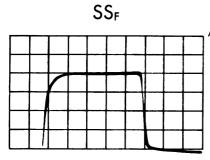

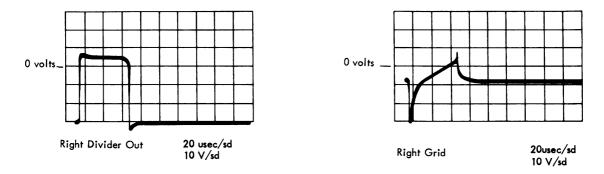

| A24        | Output Wave Forms $SS_F$ and $SS_E$ . A           | 154 |

| A25        |                                                   | 158 |

| A26        |                                                   | 460 |

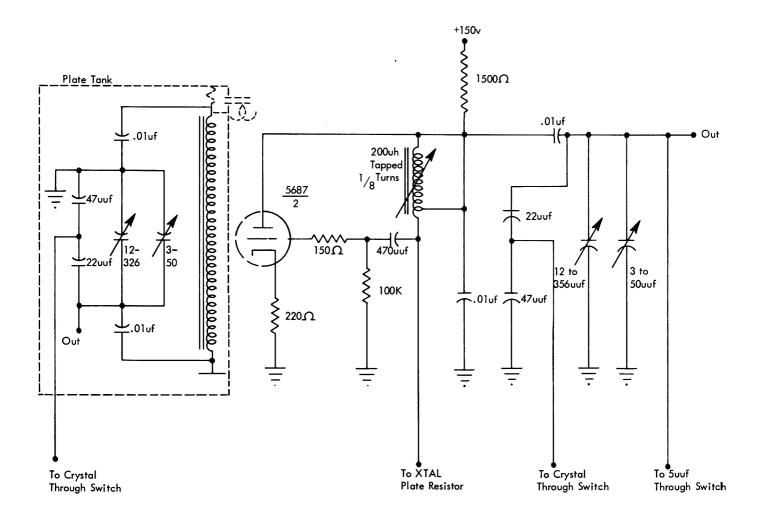

| A27        | General Oscillator Tuning Characteristic Curve    | 460 |

| A28        | Print/Punch Magnet Thyratron TH A                 | 64  |

| A29        | Wave-Form Generator Peaker PKR <sub>Z</sub> A     | 64  |

|            | $oldsymbol{L}$                                    |     |

#### 1.00.00 GENERAL INFORMATION

#### 1.01.00 DEFINITION OF TERMS

Certain terms in the circuit descriptions must be clarified or defined, e.g., "standard cathode follower" or "standard inverter." All circuits are standard but the basic ones (such as AND, OR, I, K, T, and SS) are the most commonly used. Others may be merely modifications of these basic circuits or entirely different circuits; they are popularly called "special circuits," used in a very few applications.

The term "tube" may refer to one or both sections of a dual tube, but the term is not used unless the reference is clear in the text. The terms "left tube" and "right tube" refer to the placement of the components on the schematic. They are not to be confused with the terms "front" and "back" that are used to denote the physical placement of the tube socket on the pluggable unit.

The voltage levels of the pulses and input/output lines fall into two general classifications: signal level and plate level (section 1.05.00). The terms "rise" and "fall" refer to the transition of a pulse. Rise or fall time is usually the time required for a pulse transition to reach 80 percent of its final value (from ten percent to 90 percent). Rise and fall time of a pulse is expressed in volts per microsecond (millionth of a second). Pulse width is measured at a point halfway between voltage levels.

Electron flow (-to+) is assumed in all circuit descriptions. Increasing the absolute potential gradient across a capacitor is called charging the capacitor. When this gradient decreases, the capacitor is discharging. During some types of transitions, the polarity of the voltage across the capacitor reverses; therefore, the terms "charge" and "discharge" as defined above may be confusing. In these cases assume that one terminal of the capacitor is connected to a steady voltage which is always more negative than the opposite terminal. If this assumption is made, the above definitions of charge and discharge still apply. For example, if the voltage at one terminal of a capacitor changes from -30 volts to +10 volts and the opposite terminal is grounded, assume then that the capacitor has been charged. It discharges when the voltage returns to -30 volts.

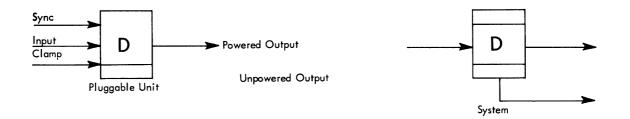

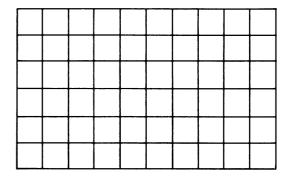

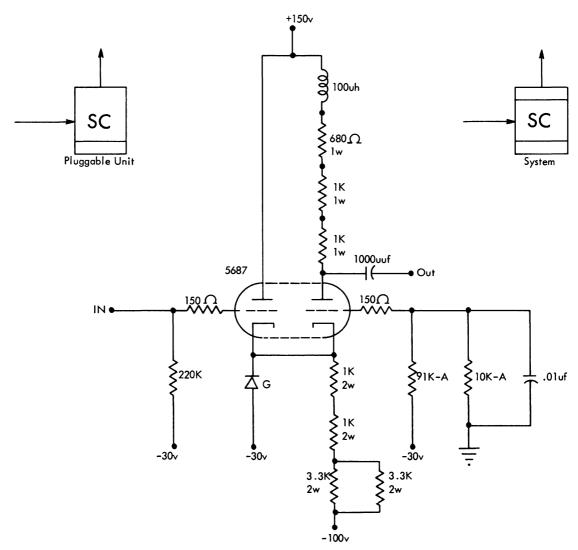

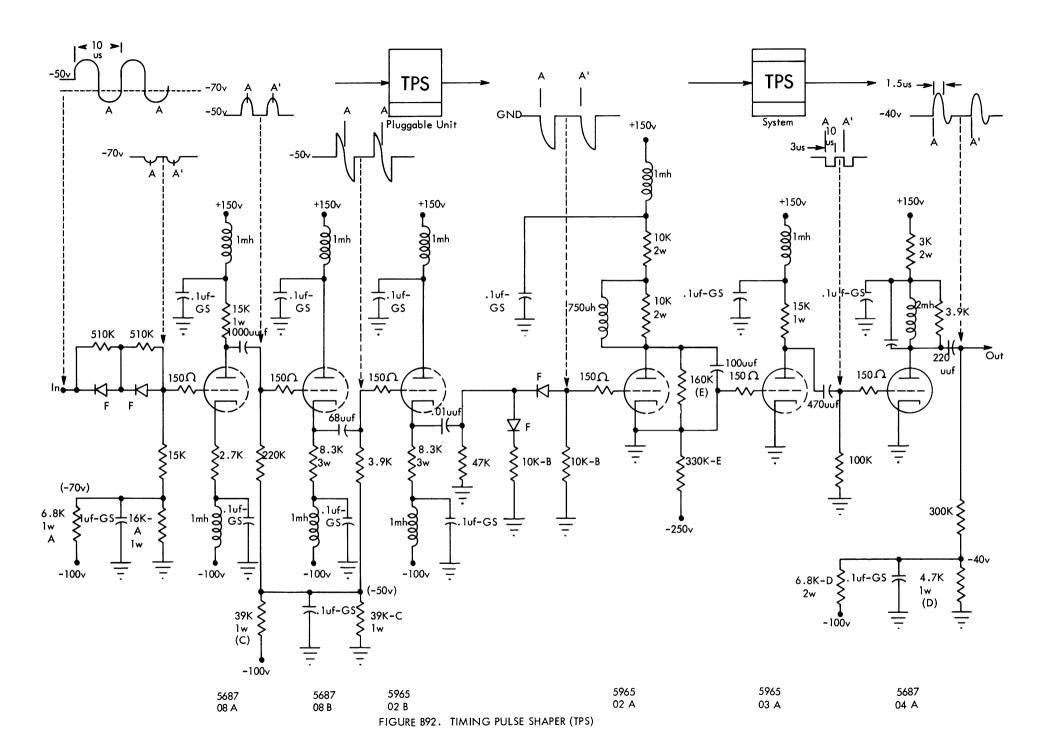

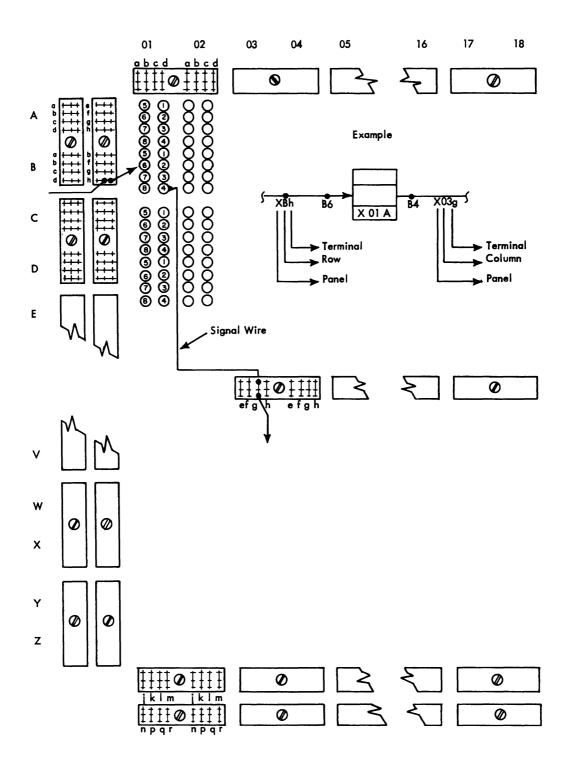

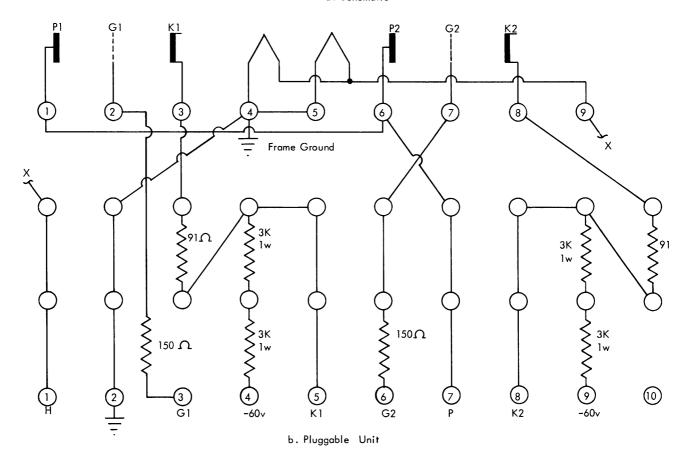

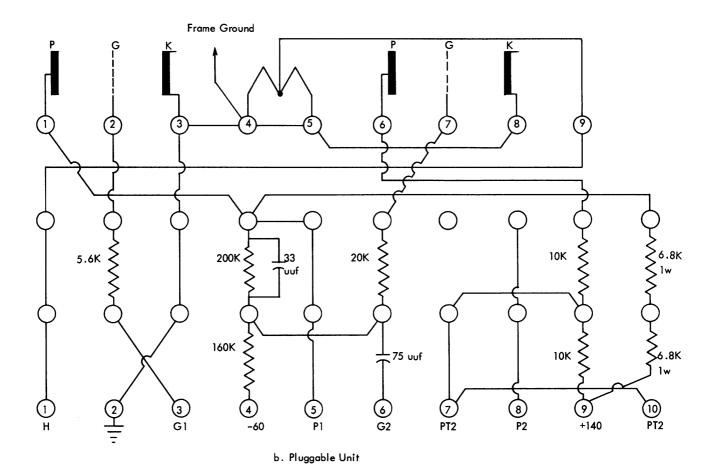

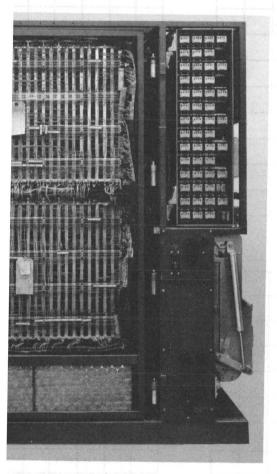

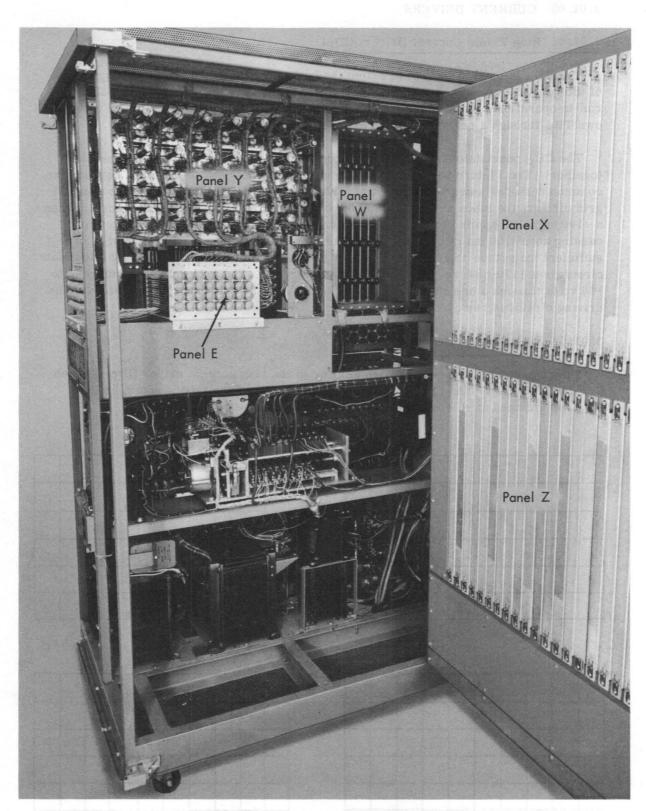

#### 1.02.00 PLUGGABLE UNIT

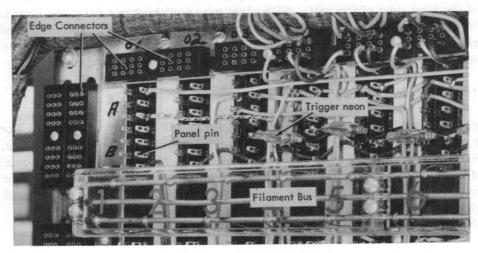

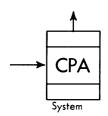

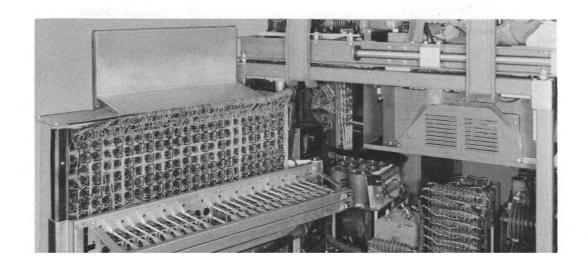

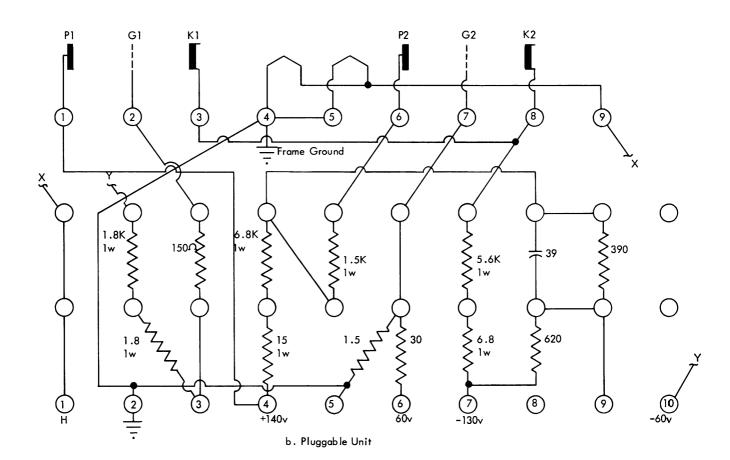

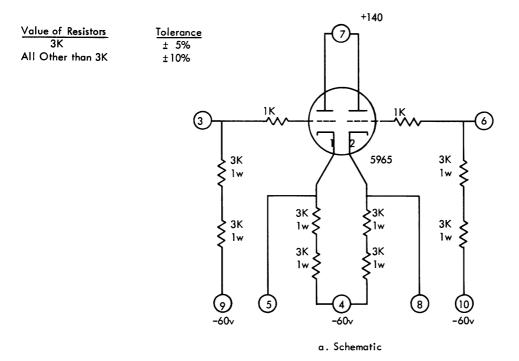

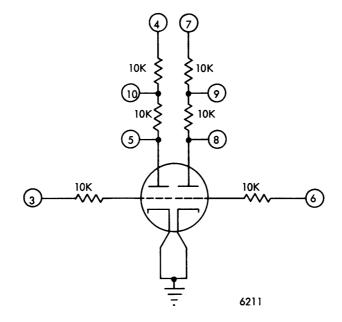

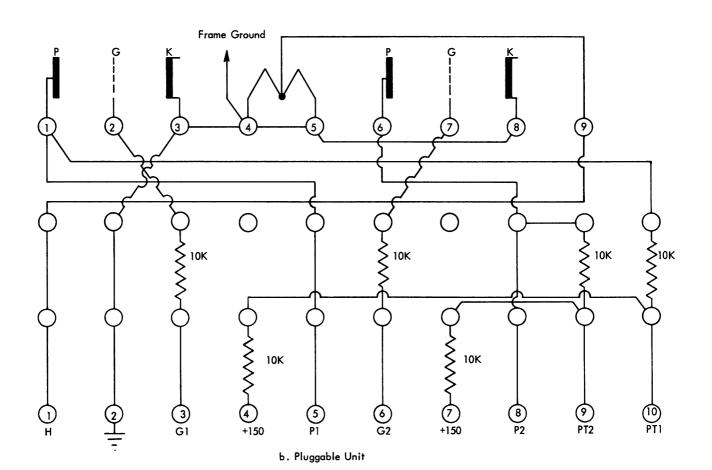

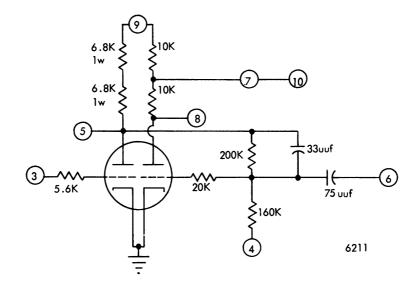

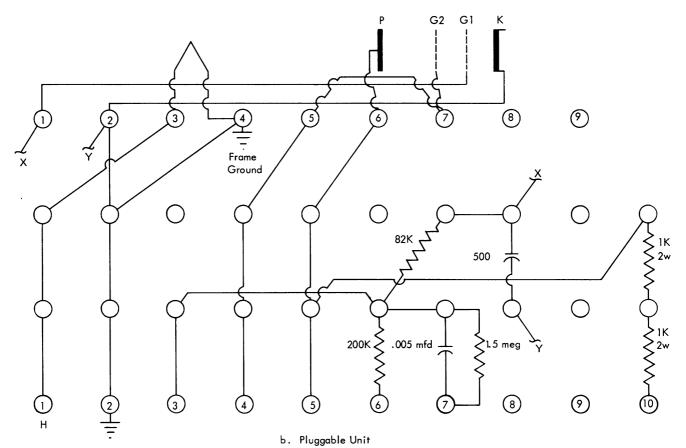

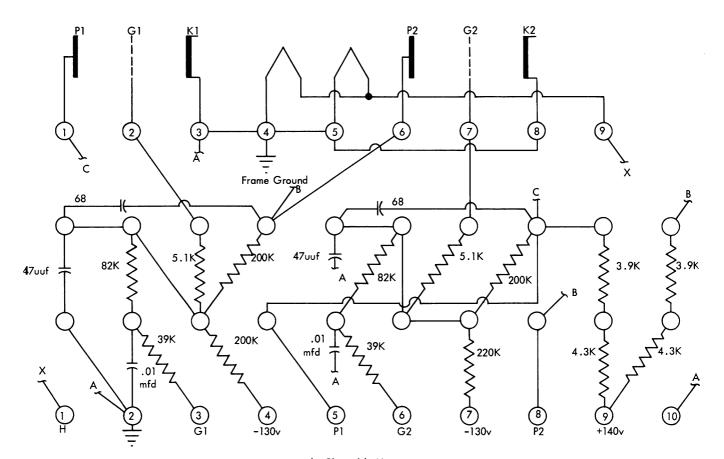

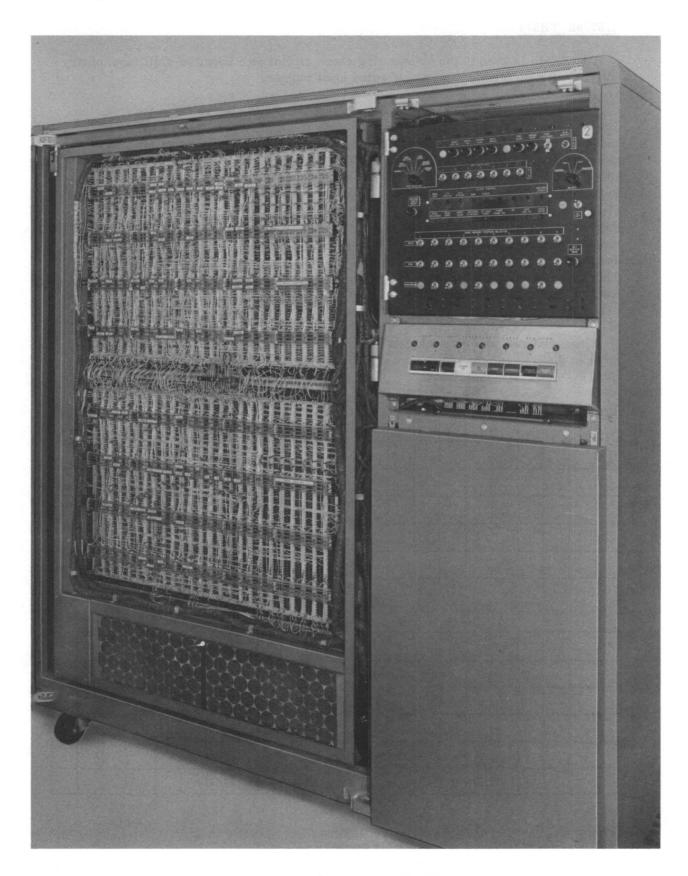

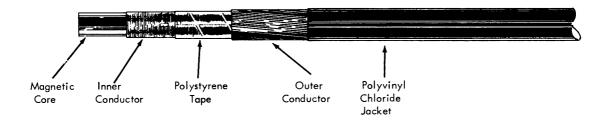

The pluggable unit acts as the carrier for most of the component circuitry (tubes, resistors, capacitors, and so on) in the 700 series systems (Figures A1a and A1b). The unit has eight tube sockets, although it need not have the full complement of eight tubes. Filament terminals of all tube sockets are wired.

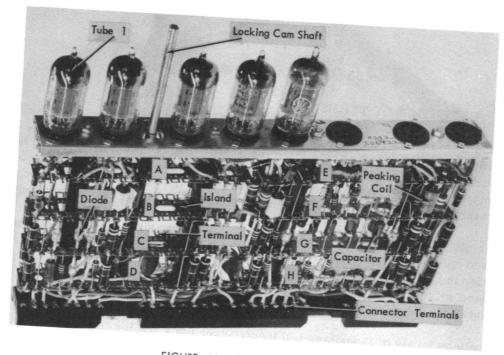

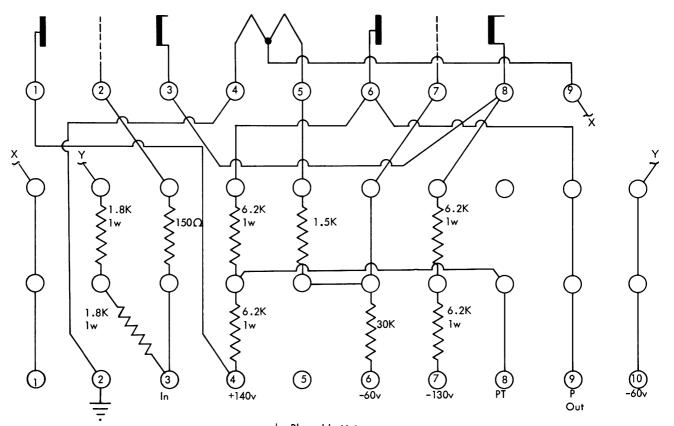

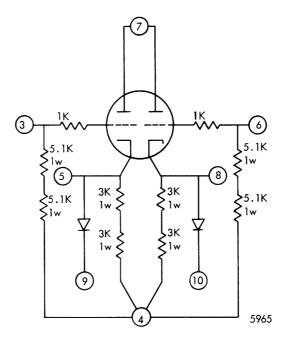

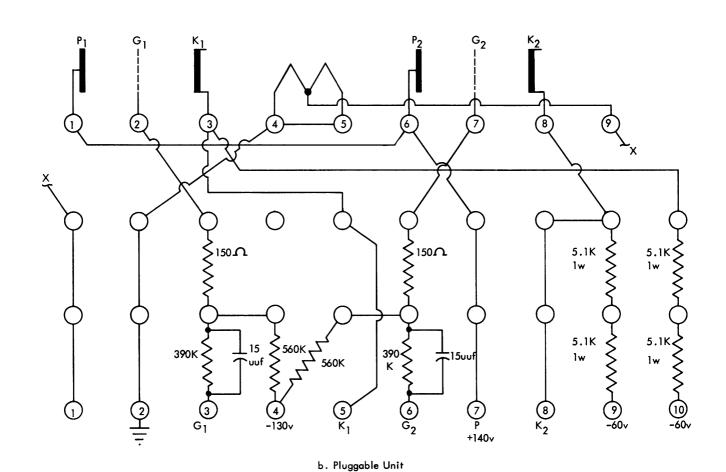

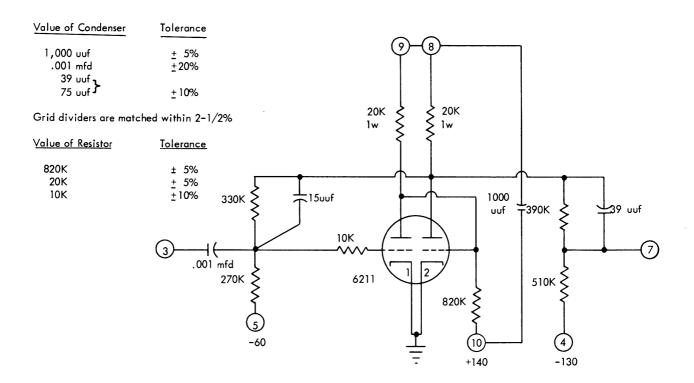

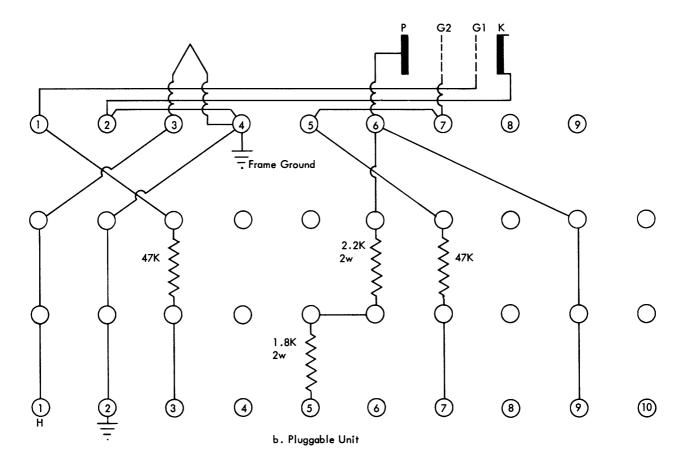

FIGURE Ala. PLUGGABLE UNIT

FIGURE A16. PLUGGABLE UNIT

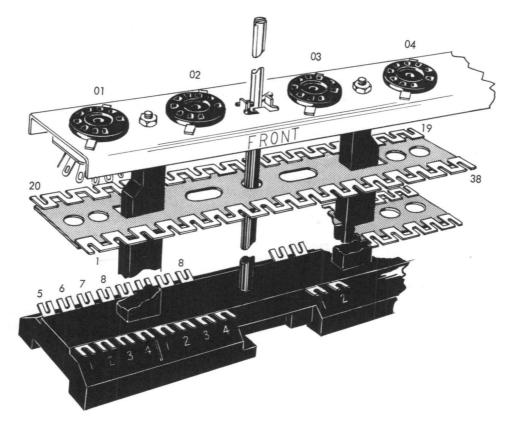

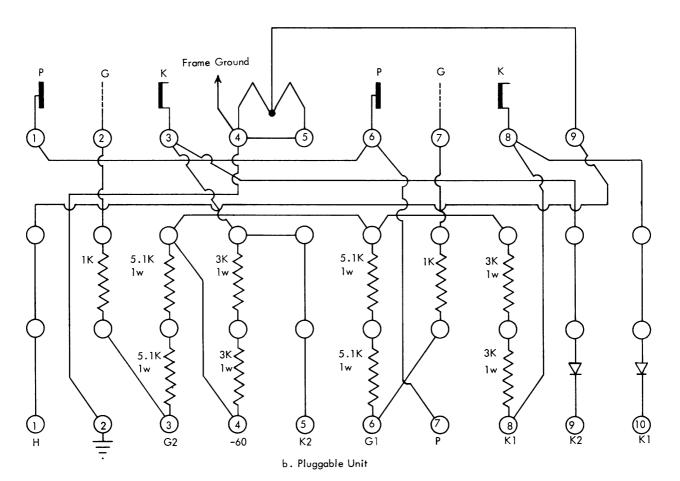

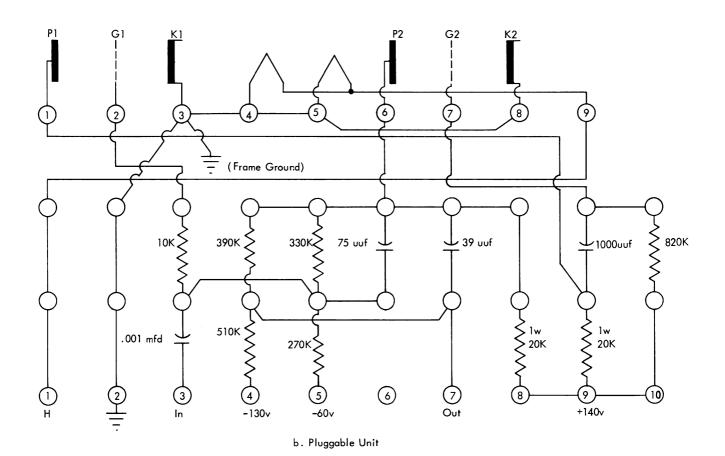

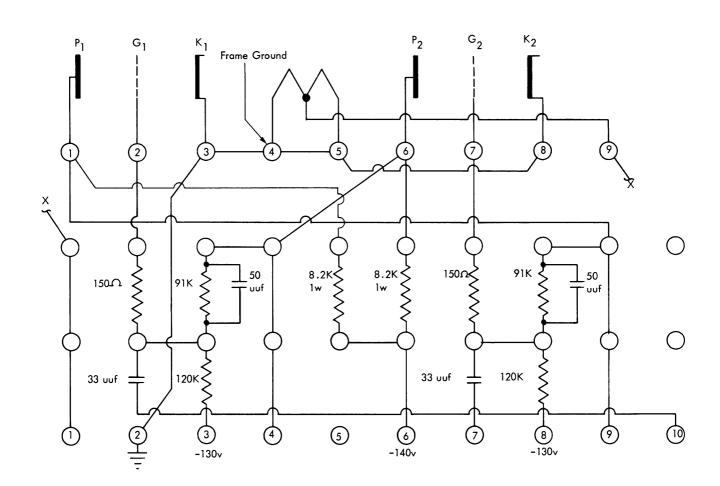

Mounted within the pluggable unit are eight terminal strips each consisting of 38 solder terminals or lugs. The terminals are numbered 1-19 on the front of the unit and 20-38 on the back. The terminals are initially shorted together and cut open to make the terminals individual. This procedure eliminates the need for jumpers. The terminal strips are called islands and are located by their corresponding positions in the unit (A through H). The circuit components are mounted between these islands.

Directly beneath each tube position, at the base of the unit, is a group of connector terminals labeled 1 through 8. These terminals are internally connected to the male knife connectors beneath the base. The unit connects to a female receptacle that has solder lugs extending out on the wiring side of the panel (panel pins). There are eight panel pins for each tube position. The panel pins are used for the entry of service wiring (voltage supplies) and signal wiring to the unit.

The locking-cam shaft extends through the unit and is used to seat the unit into its female connector. The unit is aligned to the connector; rotating the shaft with a pluggable unit wrench cams the unit downward to lock it in place. The contacts on the female connector are aligned vertically in such a way that the negative voltages are applied before the positive voltages when the unit is installed. The reverse is true when the unit is removed. However, it is wise to drop DC voltages before removing or installing pluggable units.

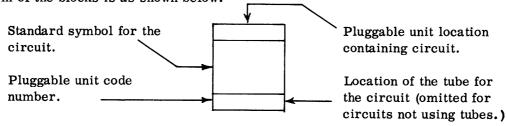

Each machine systems index section has a pluggable unit location chart for each panel on the machine. This chart includes unit part numbers. Standardization of units is retained wherever possible. Thus, the same units may have components used on one machine and unused on another.

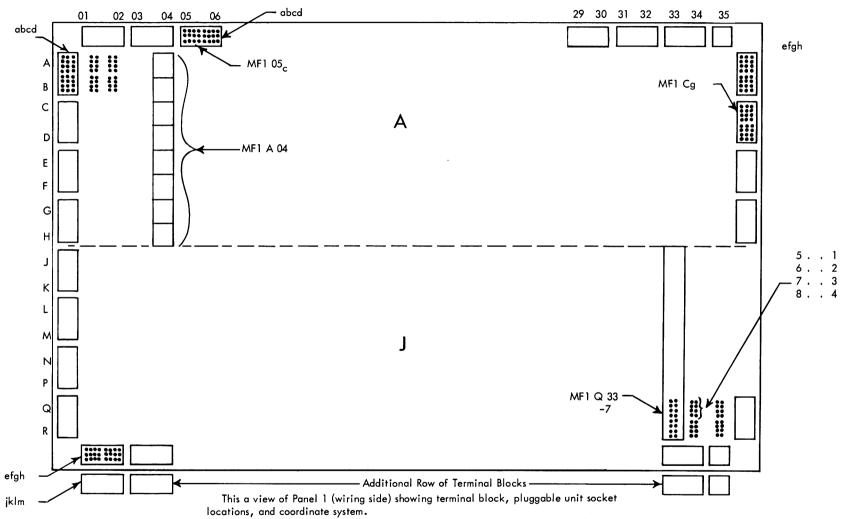

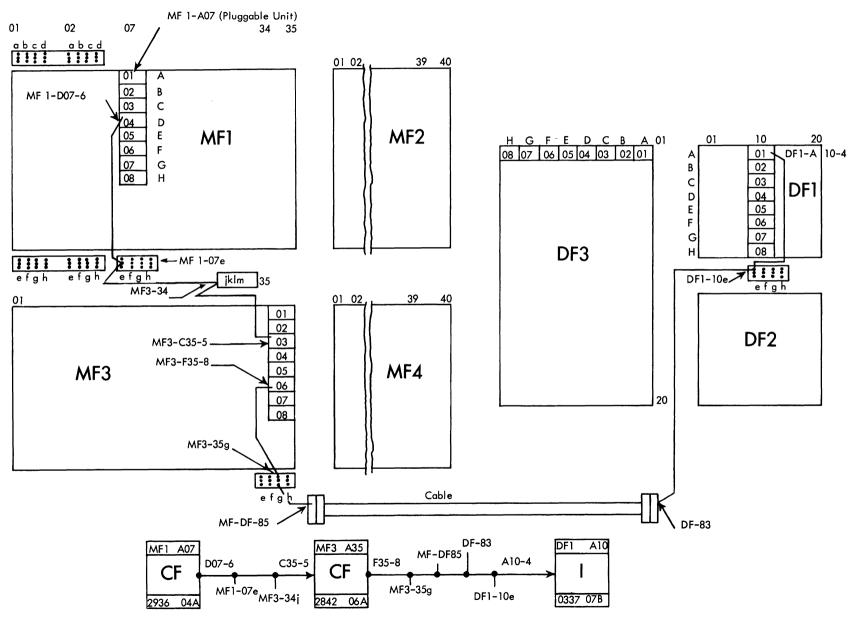

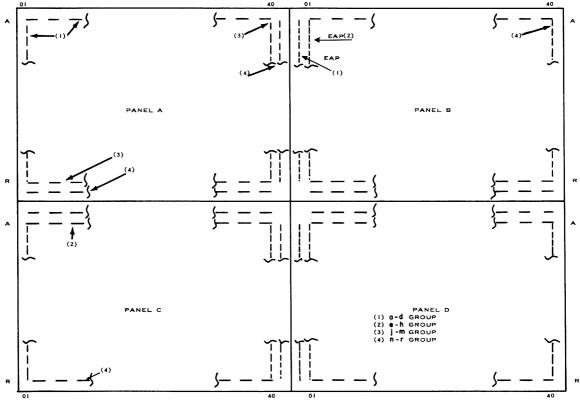

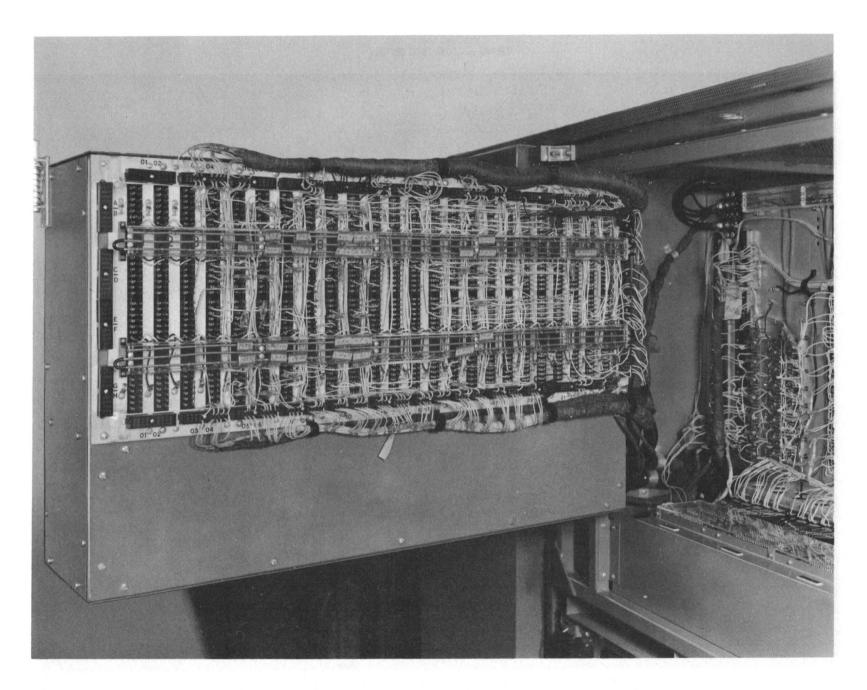

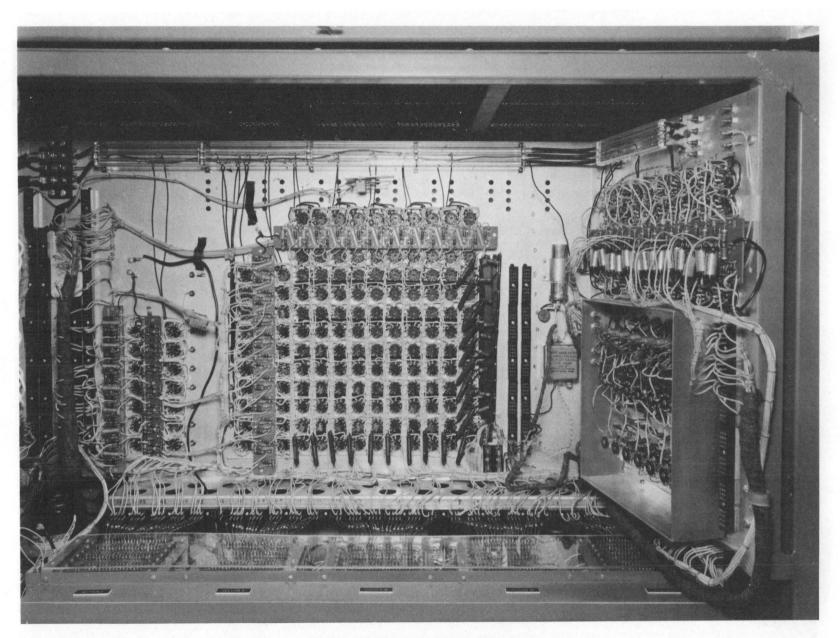

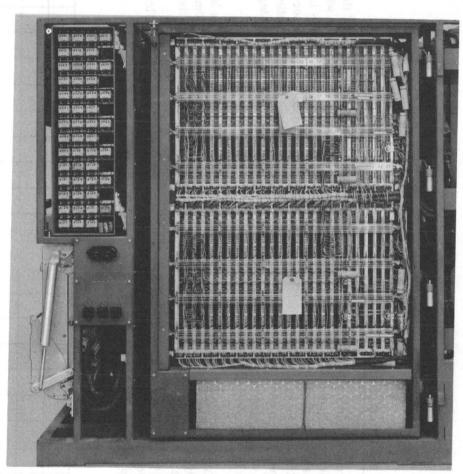

#### 1.03.00 PLUGGABLE UNIT LOCATION

All panels that contain pluggable units use the coordinate reference system for locating specific points on the panel. The vertical axis is labeled with upper case letters A-Z, omitting I and O. The horizontal axis is labeled with numbers 01-40, the number of columns depending upon the specific unit. Thus, the intersection of a horizontal and a vertical notation locates a specific section of the panel. Location is given to any pluggable unit in the panel by giving the column and alphabetic location of the first tube of the unit. With eight tube positions per unit, the first tube locations can be only A, J, or S. Because the islands are lettered and the island terminals are numbered, any component on a unit can be located. Panel pins receive their location from the tube socket that is in line with the pin group.

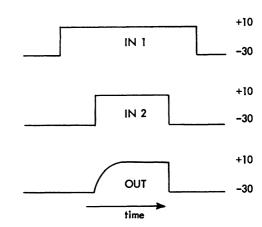

#### 1.04.00 PULSE SKETCHES AND WAVE FORMS

Sketches and wave form drawings are included to aid circuit explanation. For drawing convenience, pulse sketches are shown in many cases as a square wave, although the perfect square wave (zero rise and fall time) does not exist. Actual rise and fall time is usually several tenths of a microsecond. Distortion effects of a circuit on an incoming pulse are occasionally overemphasized to show graphically what is causing the distortion. Also, poor input pulses are used to show pulse-shaping and level-setting characteristics of a circuit.

The same circuit can operate differently throughout the machine because of variables such as stray capacitance, output loading, and variations in component tolerances.

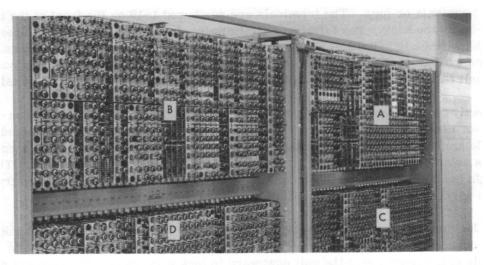

FIGURE A2. PANELS A-D

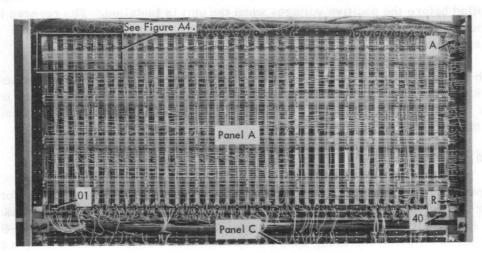

FIGURE A3. PANEL A (WIRING SIDE)

FIGURE A4. PANEL WIRING

#### 1.05.00 INPUT/OUTPUT LEVELS

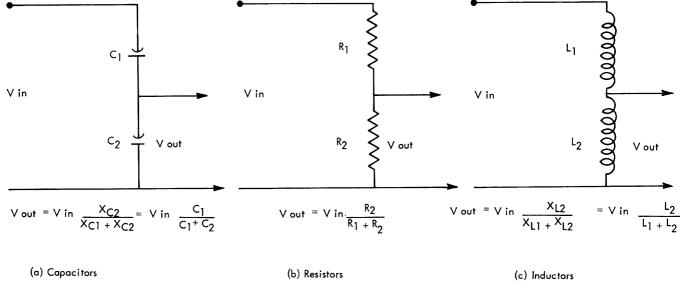

The voltage levels of pulses and information lines fall into two classifications: signal level and plate level. Signal levels are developed at divider outputs while plate levels are developed at full plate, tapped plate, or tapped divider outputs.

Signal level limits are usually +10 to -30 volts, with certain circuits requiring variations. In high-speed computer circuits, the effect of line capacitance to ground is detrimental. Therefore, the voltage swing above and below ground was chosen as a minimum satisfactory level. Circuits are controlled by the input rise from -30 to +10 volts, the fall from +10 to -30 volts (± shift inputs), or the steady up or down level. The rate of change from one voltage level to another must usually be fast (60 volts/microsecond). Some circuits have adverse effects on the voltage shift; they damp or cut down the amplitude, slow the shift time, or cause general distortion. Other circuits overcome these faults with their pulse-shaping and level-setting characteristics.

Because plate levels are about 100 volts, they are noted as plate levels in the system pages. This notation is an aid to proper sensitivity settings on the oscilloscope or voltmeter. Plate level outputs are used for economical component usage. They perform the same duty as signal levels.

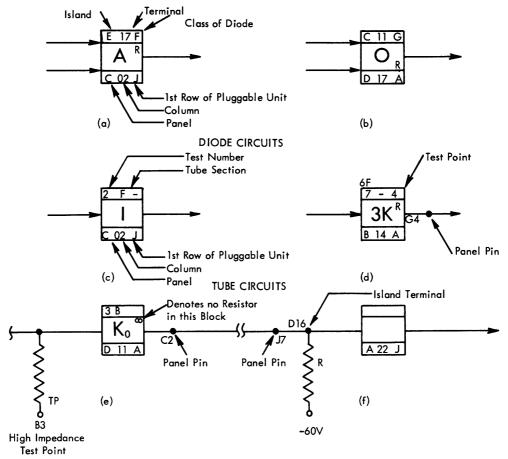

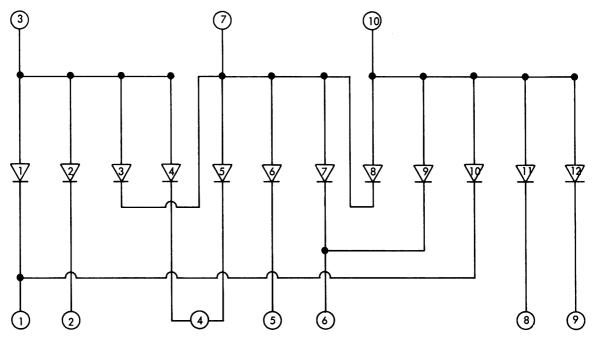

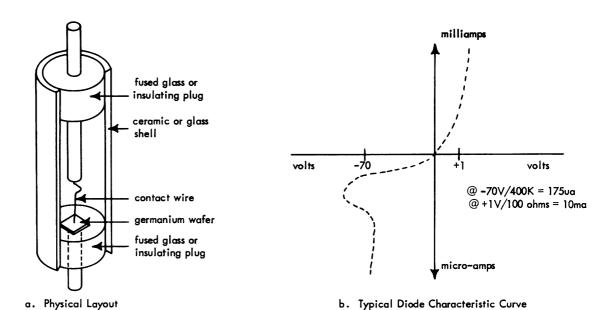

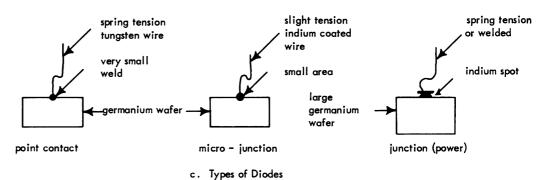

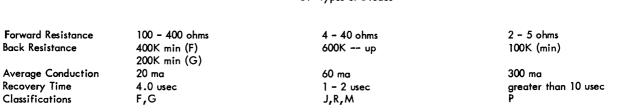

## 1.06.00 CRYSTAL DIODES

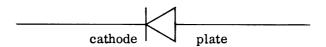

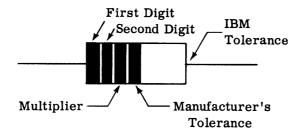

Crystal diodes rather than vacuum tube diodes are used in the machine wherever possible. The small crystal diodes have an obvious advantage in size over their counterpart in vacuum tubes; they have the added advantage of not needing a filament or heater, thus reducing power requirements and wattage loss in heat. Because the number of diodes employed is large, these are distinct advantages. Many watts are saved by their use and thousands of unwanted BTU's of heat are avoided. The symbol used for the crystal diode is shown below with plate and cathode labeled.

Crystal diodes are divided into various classes depending on their back and forward resistance and upon their ability to pass current. Back resistance is the DC resistance exhibited by a diode when the cathode is more positive than the plate. With the cathode more positive than the plate, the diode is theoretically cut off. Forward resistance is the opposite of this, or the resistance exhibited by a diode when the plate is more positive than the cathode. Diode specifications and identification markings, as well as theory and construction, are listed in the Appendix (sections 1.01.05 and 1.02.04, Book E).

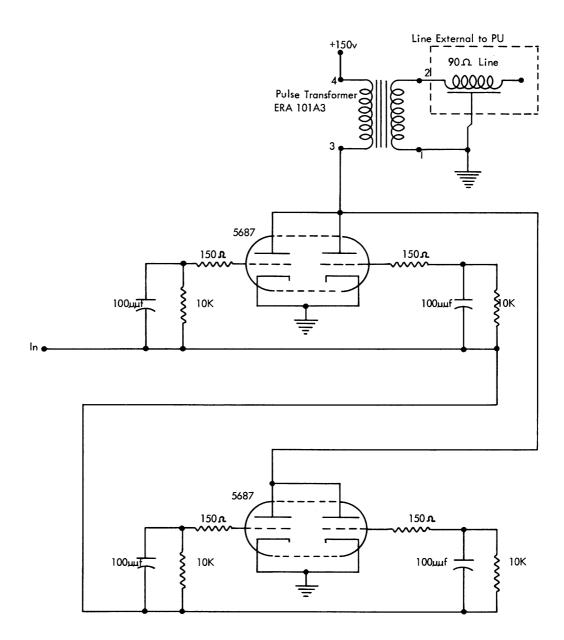

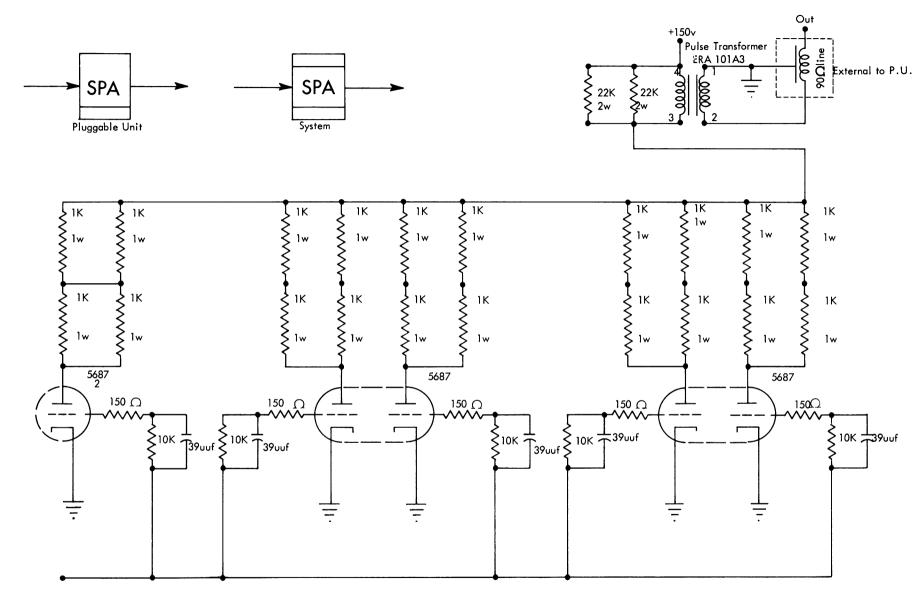

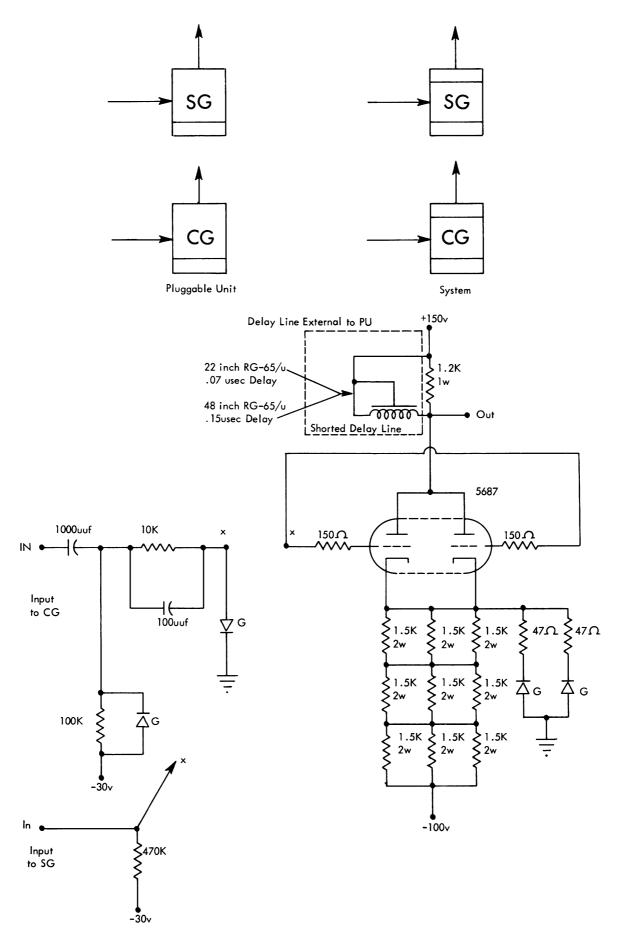

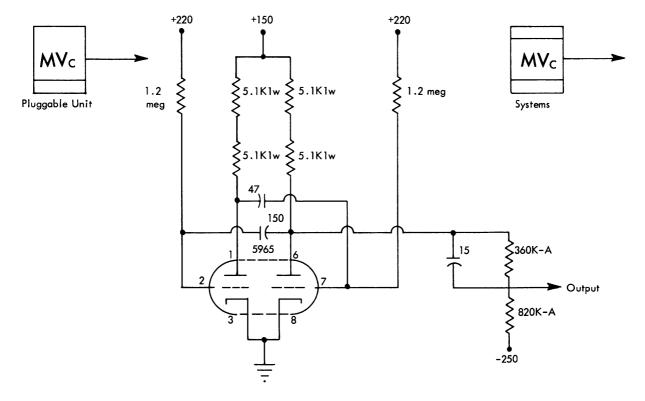

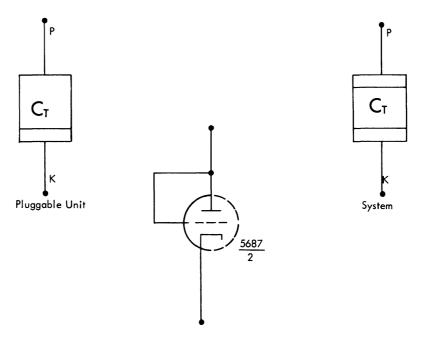

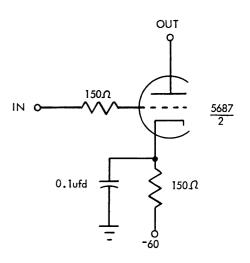

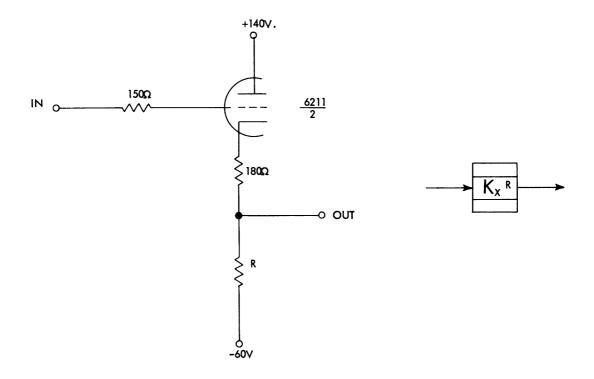

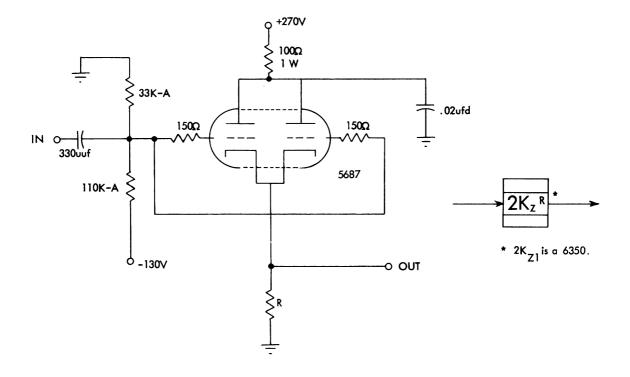

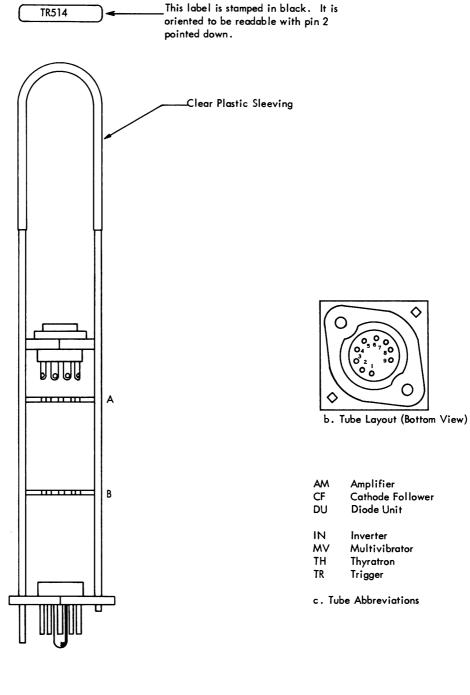

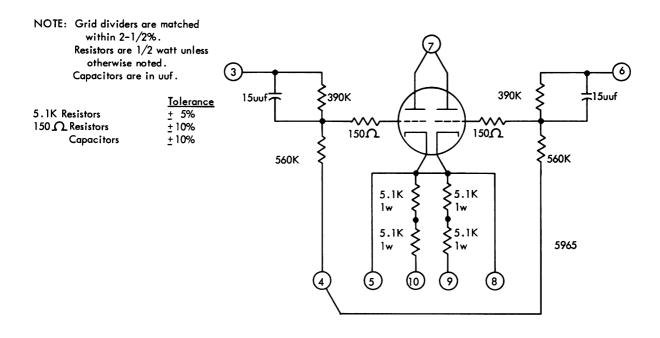

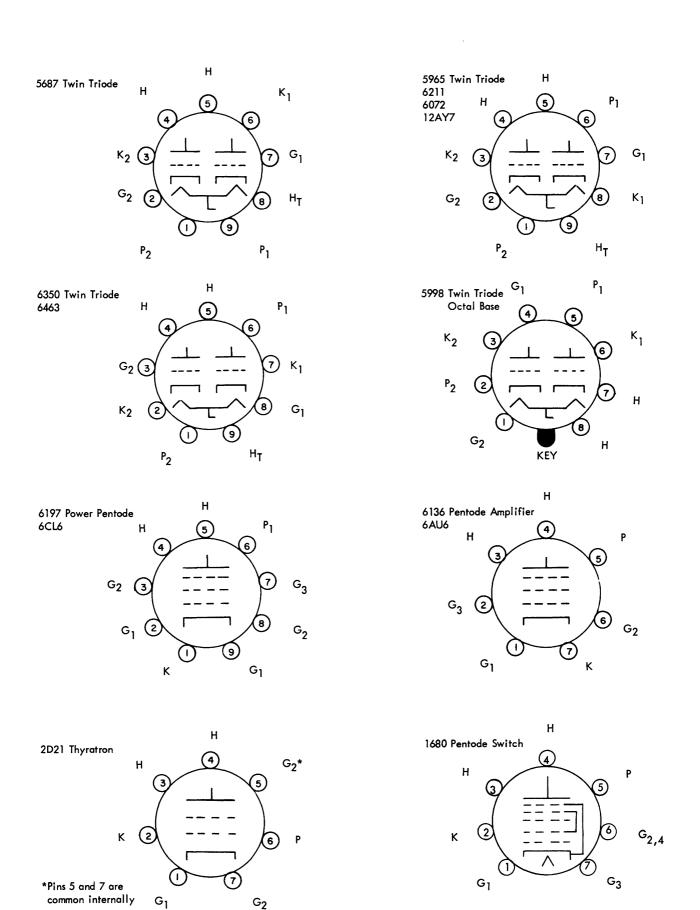

#### 1.07.00 ELECTRON TUBES

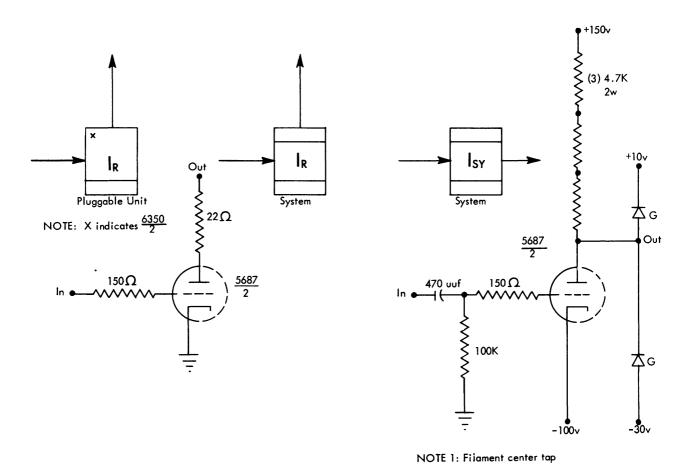

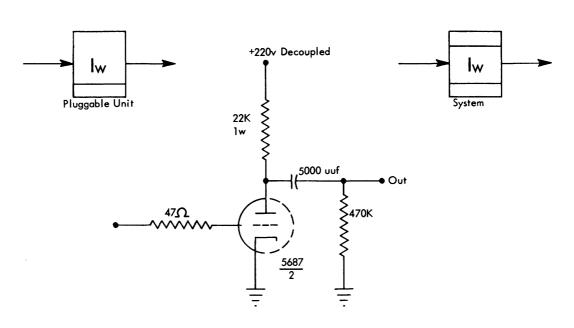

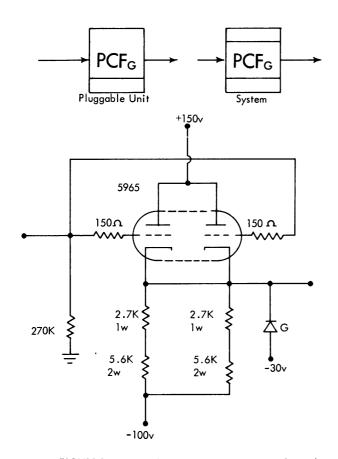

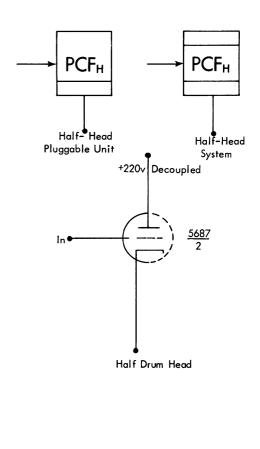

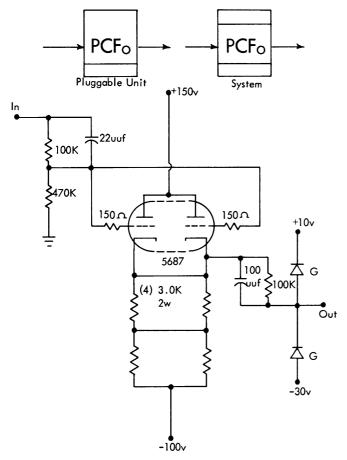

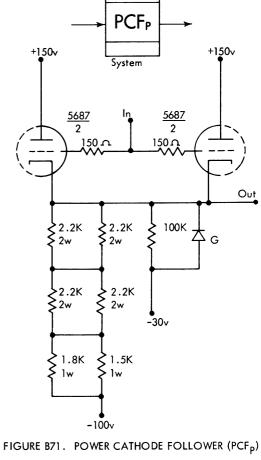

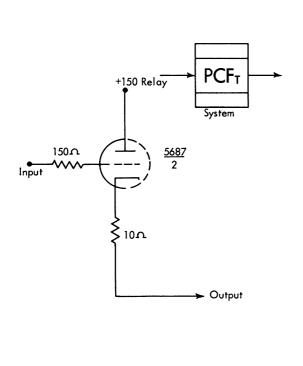

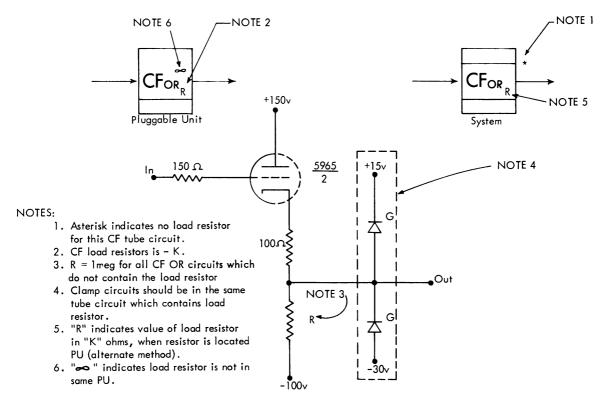

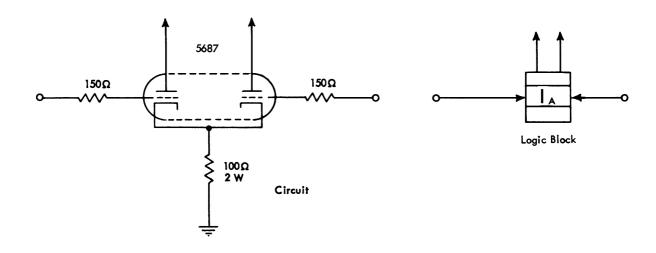

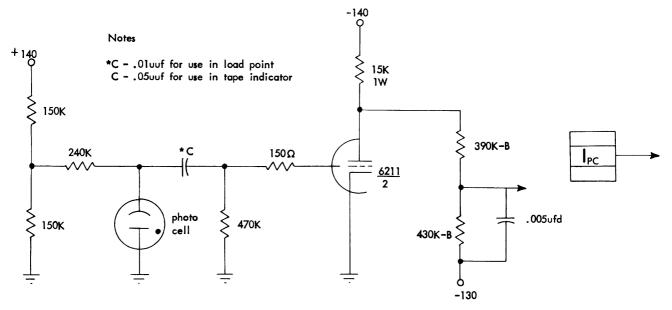

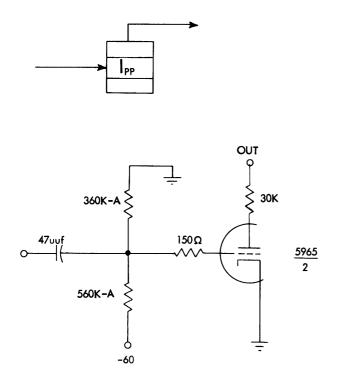

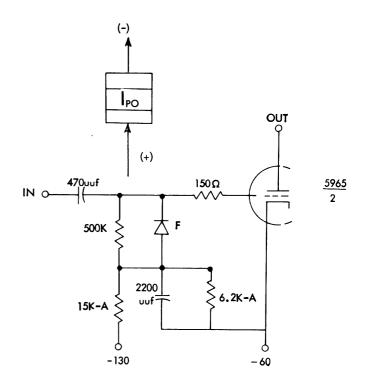

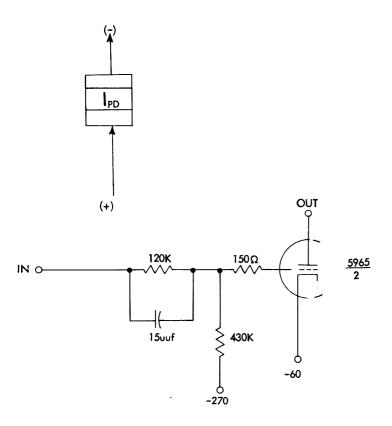

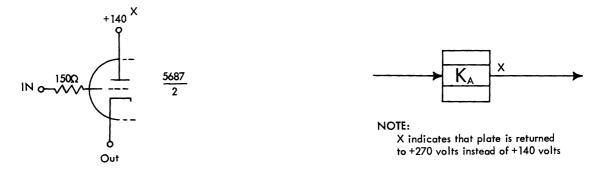

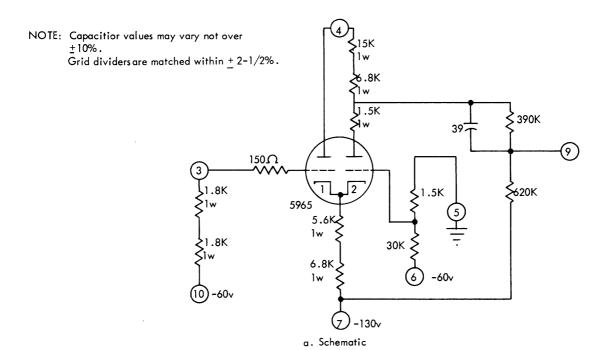

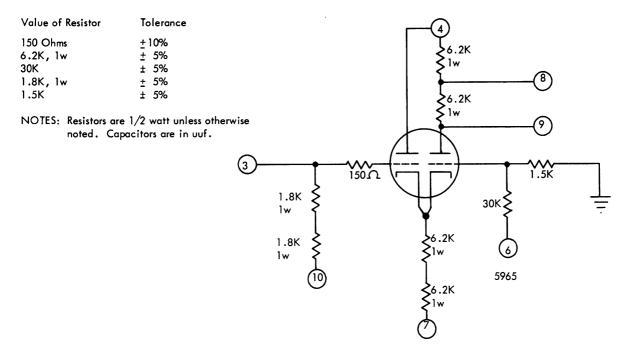

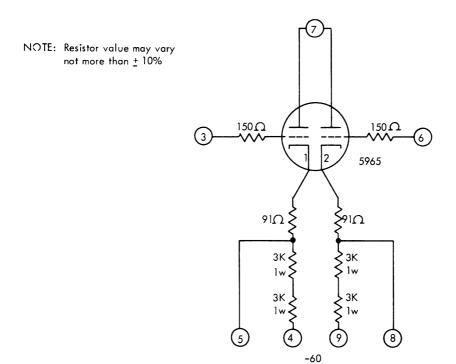

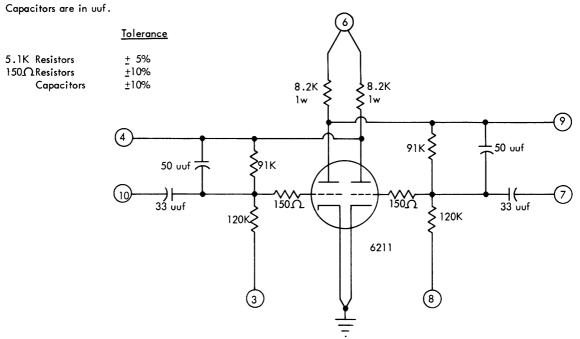

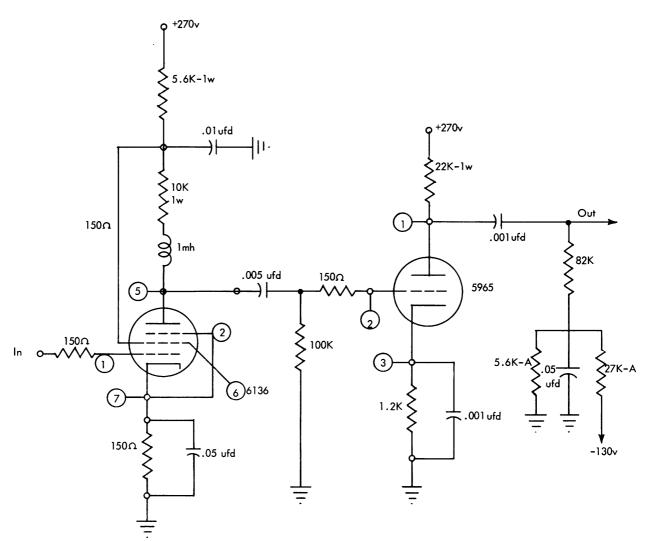

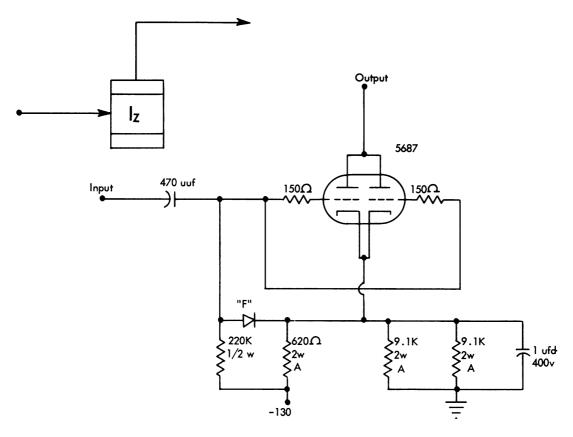

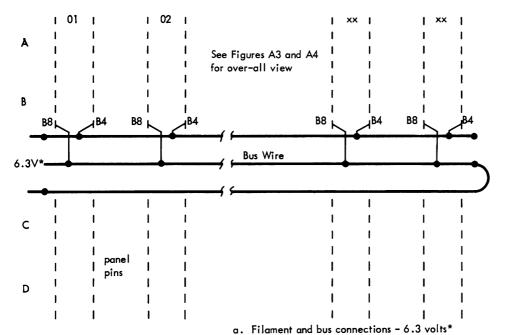

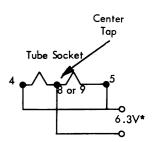

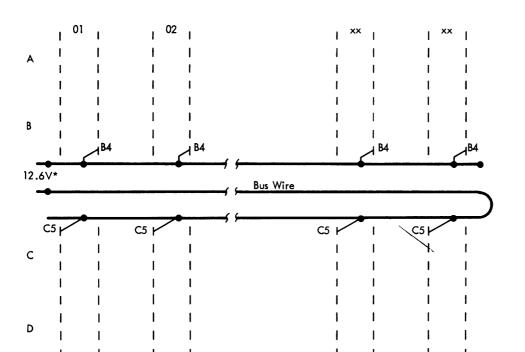

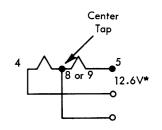

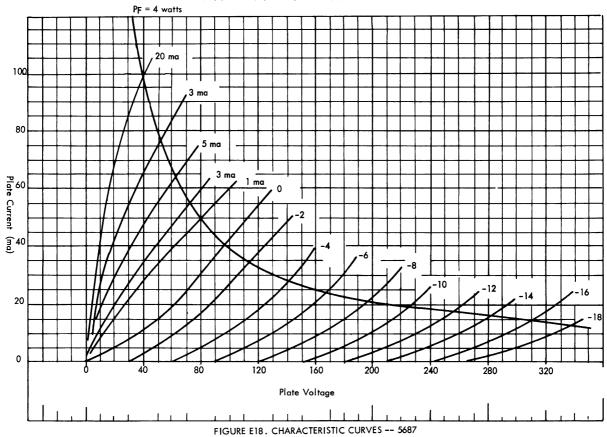

The three most commonly used tubes in the 700 series are the 6211, 5965 and 5687. The tubes are listed in the order of their usage in the system. The 6211 is most used because it has the lowest filament current requirements and the 5687 is used only where maximum power is needed. The three tubes are 12.6v dual triodes with center tapped filaments so that either a 6.3 v or 12.6v filament supply can be used.

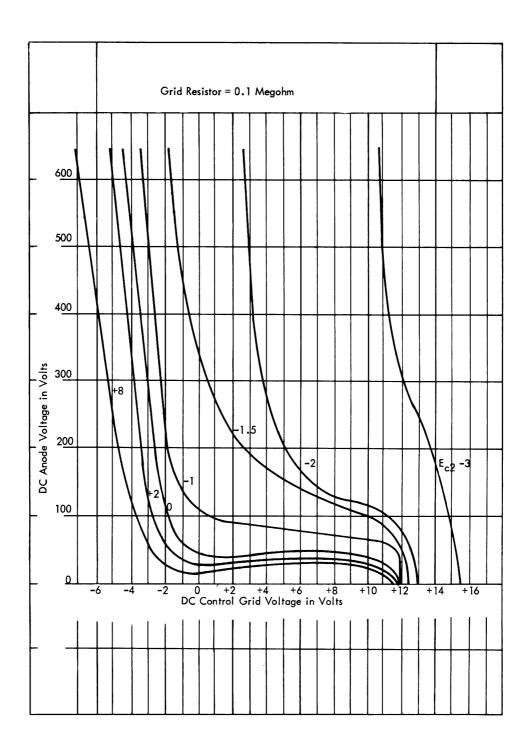

The filament transformers are center tapped to either ground or a minus voltage. The AC value is thereby superimposed on different DC levels. Keeping the filament supply at a certain DC level minimizes the potential difference between cathode and heater (a manufacturer's tube specification). In sensitive amplifier circuits, this procedure also is used to prevent the cathode from being positive with respect to the filament and causing current flow from filament to cathode. Detrimental noise would be introduced into the amplifier circuit. See Figure E10 for the filament wiring layout. Note that the panel pins are different for each voltage level; thus, a 6v pluggable unit is inoperative in a 12v pluggable unit socket, preventing damage to the filaments. The four tube groups are fed by the filament bus in such a manner as to have the filament current travel the same bus bar distance regardless of the tap-off position. Therefore, the filament supply voltage is uniform along the complete length of the bus bar.

In most tube circuits, the status of the tube is either cut off or in full conduction, and full conduction is usually only two-thirds of recommended maximum current. In other circuits, where maximum current is exceeded, the duty cycle is very short. The duty cycle is based on a time of 30 seconds. Thus, a ten percent duty cycle indicates that the tube is operating or conducting about three seconds out of every 30 seconds. The individual durations of conduction are usually in the order of fractional parts of a microsecond and the average of these durations meets the above specifications. Because of the two basic conditions (conducting or cut-off), the cut-off bias is frequently used in circuit description.

These voltages are:

| 6211 | -8.5 volts |

|------|------------|

| 5965 | -6.5 volts |

| 5687 | -13 volts  |

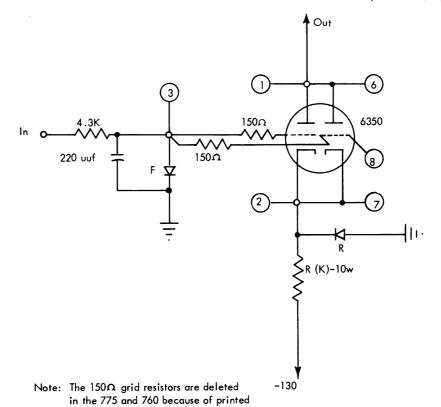

Most tubes contain a 150-ohm parasitic suppression resistor in the grid circuit. Omission on the circuit schematic does not imply that this resistor is missing. In circuit design, modifications are made to insure proper operation with tubes falling in the classification 25 percent weak to 20 percent hot. Other tube specifications are listed in the Appendix.

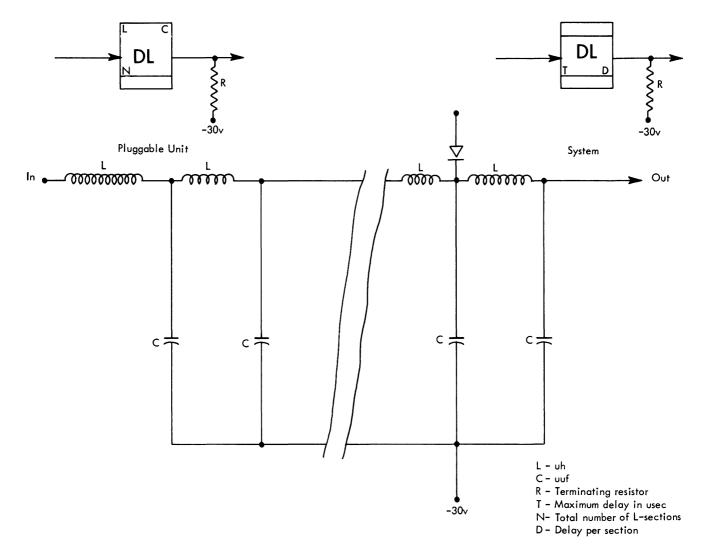

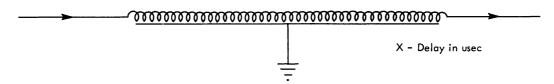

#### 1.08.00 CIRCUIT DELAYS

A characteristic of many tube circuits is the delays that are produced. Delay is defined as the time elapsing between the beginning of a voltage shift at a grid and the beginning of a resultant shift at the plate. Because a positive input pulse starts from a level of about -15 to -30 volts and must rise to the cut-off point for the tube before any conduction occurs, the time required to rise to this point appears as delay in the output. Conversely, any time required for an input pulse to fall from the nominal +10v level (where grid current flows) to ground (where grid current ceases) also appears as a delay in the output. Therefore, the slower the voltage transition at the grid, the more delay produced at the plate. This delay can be approximated as roughly one half of the rise or fall time of the input pulse. Delay of a circuit should not be confused with rise and fall time characteristics.

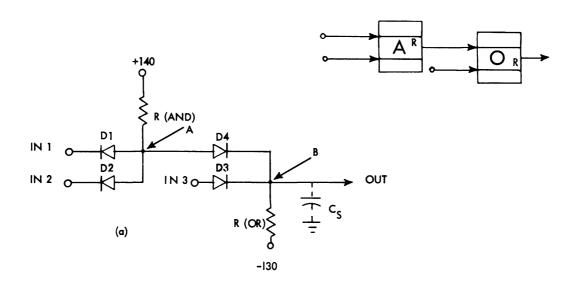

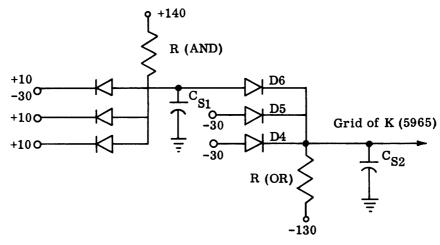

(+AND) (-OR) (-OR) (-OR)

\* Point B is terminal 14 on island C.

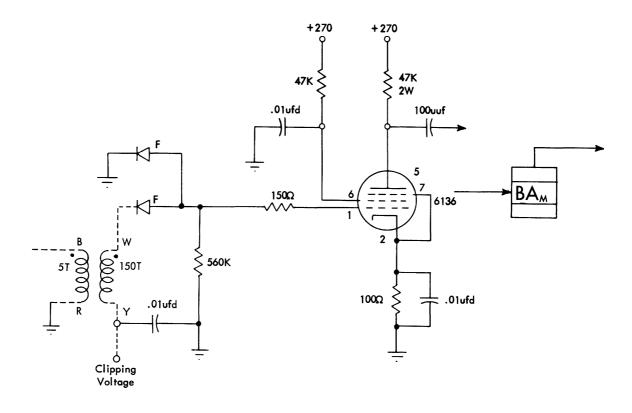

FIGURE A5. + AND (-OR) CIRCUIT

#### 2.00.00 STANDARD CIRCUITS

The circuits in this section are popularly called standard or basic circuits because of their frequent usage in the system. The circuits are kept in one section as an aid to a thorough understanding of their operation and early application to machine logic.

## 2.01.00 + AND (-OR) CIRCUIT

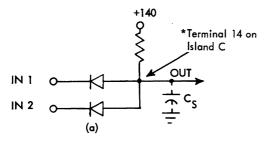

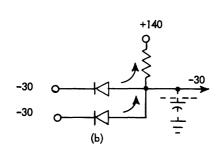

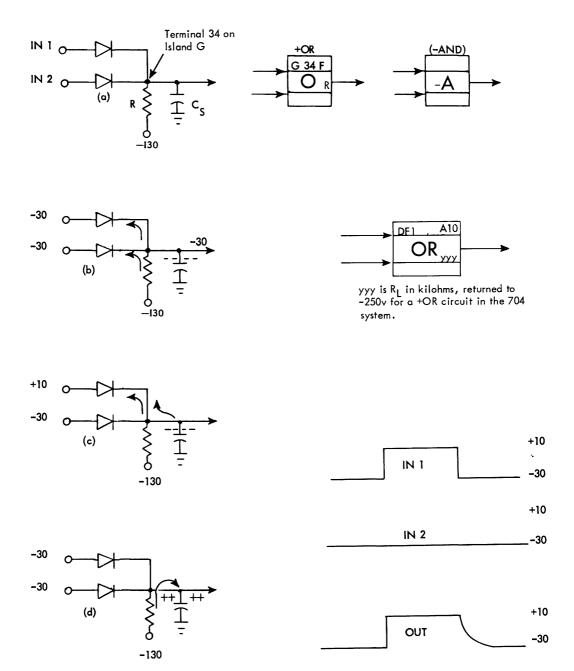

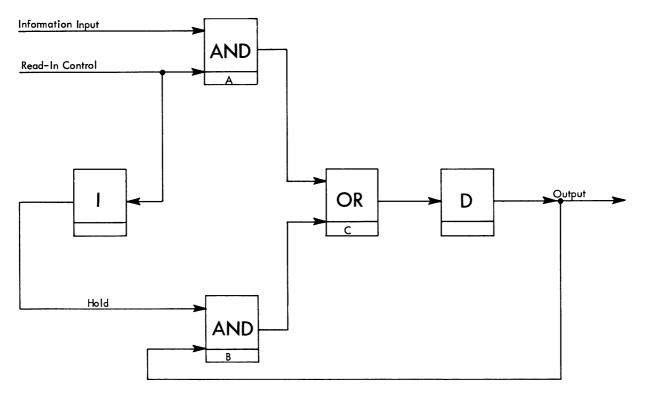

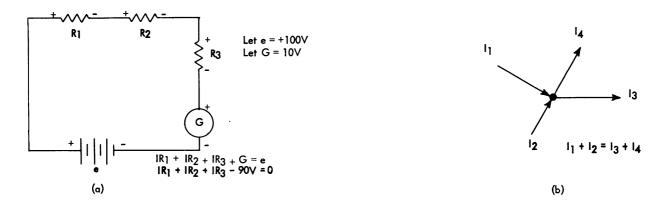

The +AND circuit in Figure A5 is the first of four basic diode circuits used. Diode circuits form the basis for switching, decoding, adder, sampling and control circuits. They are economical because they use few components and require no vacuum tubes.

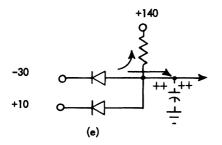

The circuit configuration for the +AND and the -OR are identical. The polarity designations are adopted in order to work with negative logic, that is, the recognition of the absence as well as presence of information. Logical operation of these two circuits is as follows:

+AND circuit requires all inputs to be plus for a plus output.

-OR circuit gives a minus output if any input is minus.

Each description holds true for either circuit because the circuits are identical. However, the logical usage is different. The +AND insures that both inputs are up before the output comes up, while the -OR gives a minus output as long as any input is down.

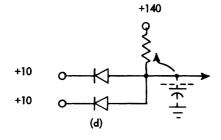

Figure A5f is the logic block and circuit configuration for the tapped-output AND circuit  $A_B$ . Thus, an output higher than +10 volts is obtainable. The information in the upper portion of the logic block locates the junction point of the two resistors. This point is the tap. It represents the output of the  $A_B$ .

## 2.01.01 Circuit Description

Figure A5a shows the junction point of the diodes and the resistor (R). This point is always used to locate diode circuits within pluggable units. Resistor (R) limits current and controls the rise time of the output. C<sub>S</sub> represents input capacity of the circuit being driven and stray wiring capacity.

If both inputs are at -30 volts, the polarity is correct for both diodes to conduct (Figure A5b). The resultant current flow through R causes a voltage drop across it to maintain a level of about -30 volts. Because of the diode's forward resistance of 100 ohms, the voltage at the junction will be -29.04 volts. For practical purposes, the output is -30 volts and  $C_{\rm S}$  is discharged.

If input 1 changes instantaneously to +10 volts, diode 1 is cut off because the cathode is more positive than the plate (Figure A5c). Diode 2, with -30 volts on its cathode, maintains conduction and the output remains unchanged. There is a small amount of current flowing through diode 2 to the +10v source, but its effect is negligible.

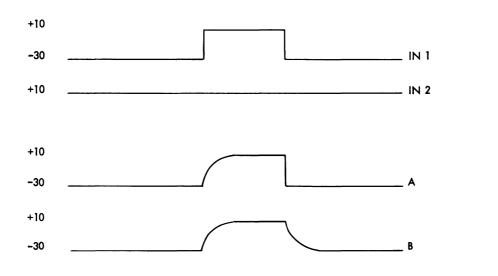

FIGURE A6. +OR (-AND) CIRCUIT

When input 2 changes to +10 volts, diode 2 is cut off because  $C_S$  momentarily is holding the output at -30 volts (Figure A5d).  $C_S$  has to charge through R to +140 volts and this delays the rise of the output level. The voltage level at the junction starts heading for +140 volts but, as soon as +10 volts is reached, the diodes go back into conduction. The output is now +10 volts and  $C_S$  is charged to +10 volts.

When input 1 falls to -30 volts, diode 1 conducts harder, discharges  $C_S$ , and diode 2 is cut off (Figure A5e). The output follows the input down to -30 volts and  $C_S$  is discharged. When input 2 falls to -30 volts, diode 2 goes back into conduction to help maintain the -30 volts output.

The action of an AND circuit may be summarized as follows: The output voltage of an AND circuit approximately equals the most negative input voltage. This statement is true regardless of the number of inputs.

# 2.01.02 Rise/Fall Time

The fall time of an AND circuit usually follows the input. However, the rise time depends upon the time constant of an RC circuit and is delayed. In circuit design where the value of  $C_S$  and the desired rise time is known, this formula determines the value of the limiting resistor. By transient analysis the formula for calculating rise time is:

Rise Time

-30 volts to +10 volts

$t = {0.17RC (701-704) \atop 0.27RC (702-705)}$

R in megohms

C in uuf (CS)

t in usec

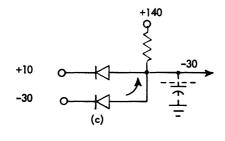

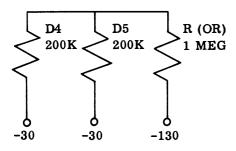

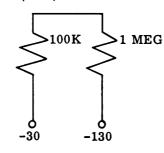

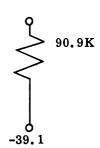

# 2.02.00 +OR (-AND) CIRCUIT

The circuit configurations for +OR and the -AND circuits are identical. Logical operation of these two circuits is:

+OR circuit gives a plus output, if an input is plus.

-AND circuit requires that all inputs be minus for a minus output.

Therefore, the +OR circuit differs from the +AND circuit in that it needs only one input up to bring the output up.

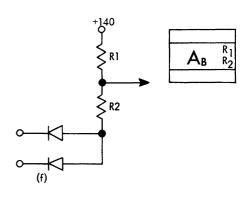

# 2.02.01 Circuit Description

If both inputs are at -30 volts, the polarity is correct for both diodes to conduct (Figure A6b). The voltage drop across the limiting resistor sets the output level at about -30 volts and  $C_{\rm S}$  is discharged.

If either input rises to +10 volts, that leg conducts harder and provides a charge path for C<sub>S</sub> (Figure A6c). The other diode cuts off and the output follows the input

FIGURE A7. + AND DRIVING + OR

in rising to +10 volts. It is normal for only one input to an OR circuit to come up at a time.

When the input that was up at +10 volts drops to -30 volts,  $C_S$  momentarily is still charged to +10 volts, and the input diode is cut off (Figure A6d). This means that the fall time of the output is delayed because  $C_S$  maintains a plus voltage until it is discharged through R. The RCs time constant controls the fall time of the OR output. The input diodes again conduct when the level at the junction reaches a point slightly more plus than -30 volts.

The action of an OR circuit is summarized as follows: The output voltage of an OR circuit approximately equals the most positive input voltage.

# 2.02.02 Rise/Fall Time

The rise time of an OR circuit usually follows the input. However, the fall time is now the affected part of the output and depends upon an RC delay. Fall time of an OR circuit is computed by the following formula:

Fall Time  $t = {0.17RC (701-704) \atop 0.34RC (702-705)}$

+10 volts to -30 volts R in megohms

C in uuf t in usec

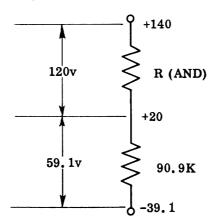

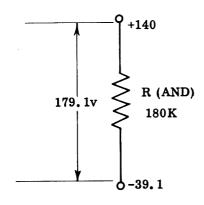

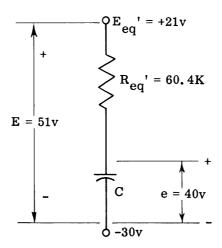

## 2.03.00 +AND CIRCUIT DRIVING +OR CIRCUIT

Throughout the system, AND/OR circuits are tied together to form a network that decodes, adds or multiplies. A common situation is: AND circuits drive OR circuits. The circuit configuration is shown in Figure A7a.

## 2.03.01 Circuit Description

Assume the following initial status:

Inputs 1 and 3 at -30 volts

Input 2 at +10 volts

The voltage at point A is about -30 volts because D1 conducts through R (AND). Parallel current also flows up through R (OR), through D4, and through R (AND). The parallel current does not affect the voltage level at point A because D1 controls the level. Point A, being at -30 volts, sets the output level at -30 volts; CS is discharged.

Input 1 is changed to +10 volts, D1 and D2 are momentarily cut off because  $C_S$  holds the output at -30 volts. D4 conducts; as point B starts to rise, D3 is cut off. Neglecting the effect of diode back resistances, the output rises exponentially from -30 volts toward a voltage determined by the DC voltage division between R (AND) and R (OR). This is the DC voltage that would be present at the output if diodes D1, D2, and D3 were disconnected from the circuit. (Design practice sets this level at about +20 volts).  $C_S$  charges toward this voltage and is clamped at +10 volts by the input. Note that if R (AND) was too large, the diodes would remain cut off and the output would never reach +10 volts.

FIGURE A8. CASCADED +AND CIRCUIT

When either input 1 or 2 falls to -30 volts, the respective diode conducting causes point A to fall immediately to -30 volts. D4 is cut off because point B cannot change until  $C_S$  discharges. Normal OR circuit fall-time delay takes place and the output falls exponentially to -30 volts.

## 2.03.02 Rise/Fall Time

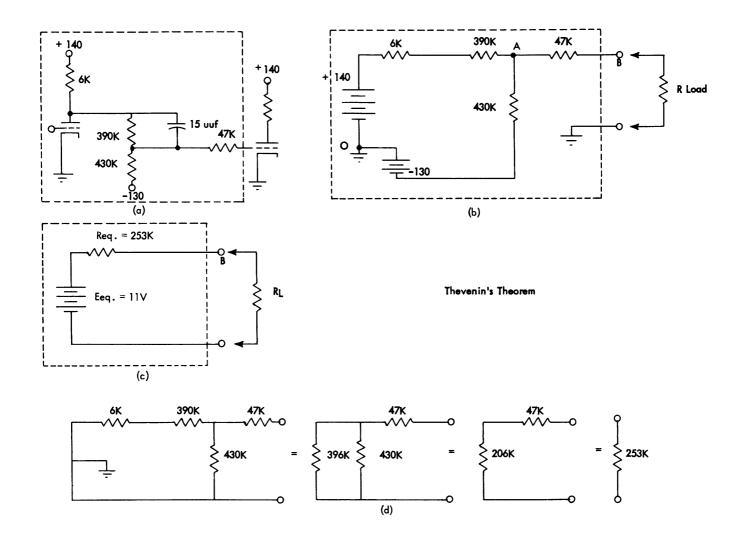

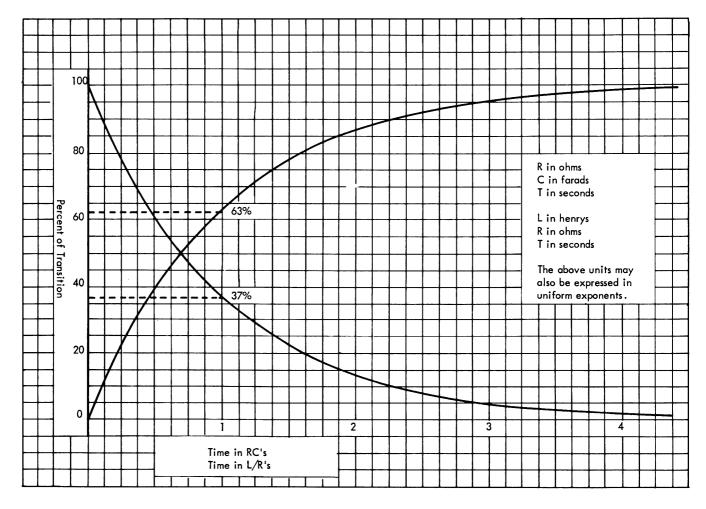

It has been shown that the output of a +AND driving a +OR combines the rise/fall time delays of both circuits. However, the rise time formula listed in section 2.01.00 does not apply here. The formula is based on the percentage of the total circuit voltage the output has to swing. For example, the rise time for a +AND circuit is given as t=0.27RC. The 0.27RC comes from universal time constant curve (Figure 89). The voltage limits in the +AND are +140 volts and -30 volts for a total of 170 volts. The output swing is 40 volts. Thus the percent of output switch is 40/170 or 23.5 percent. This percent of transition intersects the curve at 0.27RC (time constant) and hence, the rise time formula. In the case of the AND/OR, the total equivalent voltage that the output sees has to be computed by Thevenin's Theorem (section 1.01.01, Book E). By computing the fraction  $40/E_{\rm eq} + 30$  volts) and by using the curve in Figure E2, the number of time constants (t/T) corresponding to this fraction can be found. With this value use the following formula to compute the rise time of the AND/OR combination:

Rise Time  $t=R_{\mbox{eq}}$  C t/T -30 volts to +10 volts R in megohms C in uuf T in usec

The fall time of a +OR circuit driving a +AND circuit can be computed in a similar manner.

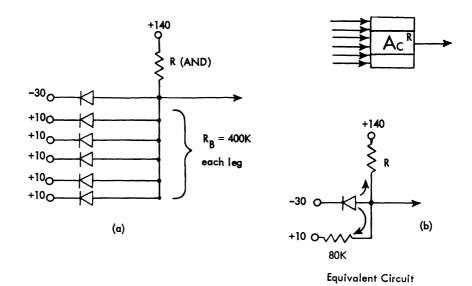

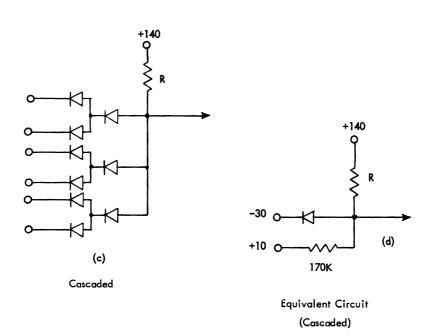

## 2.04.00 DIODE CASCADING

The back resistances of the diodes in AND/OR circuits act as a load on the driving circuits. When this effective back resistance is too low, the driving source (another diode circuit or cathode follower) cannot supply enough current to maintain proper down levels or maintain required rise/fall times. Diode AND/OR circuits with 5,6, and 7 inputs are used and these circuits present the problem of lowered effective back resistance.

A six input AND circuit is shown in Figure A8 before and after cascading. Back resistance of an AND circuit is especially important when only one input is at -30 volts and is maintaining the output down level. This condition is shown in Figure A8a. Assume that each diode has a back resistance value of 400K. Each input that is at +10 volts can be represented as a resistor of 400K because each of these diodes is cut off. Five resistors of 400K in parallel give an equivalent resistance value of 80K as shown in Figure A8b. Therefore, the 80K acts as additional load to the -30v driving source.

When a diode is placed in series with each pair of input diodes (A8c), effective back resistance is increased to 170K (A8d). The driving source now sees almost twice as much resistance offered by the inputs. Cascading cuts down the current requirements for this circuit. If the -30v input is a high impedance source (such

as an OR circuit), excess current drawn by cut-off diodes can raise the down level. Low impedance sources are also limited as to the amount of current that can be supplied to a positively returned load.

Multiple input OR circuits present the same problem when all inputs are down at -30 volts except one. The one leg rising to +10 volts must handle the charging current from  $C_S$  and the cut-off diodes. The lowered back resistance of the cut-off diodes affects rise time and cascading increases the needed back resistance.

The original design of AND/OR circuit networks determines whether cascading saves tubes or simply represents a waste of diodes.

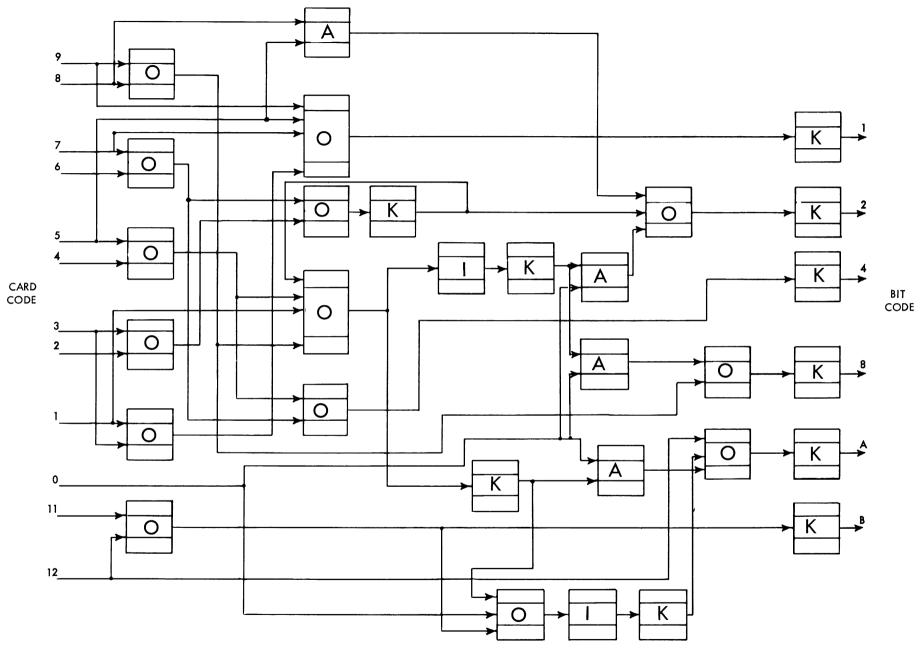

Cascaded AND/OR circuits are designated  $A_{C}$  and  $O_{C}$ , respectively, in logic blocks. An example of AND/OR usage is shown in the Appendix and in the illustration "12 to 6 Translator."

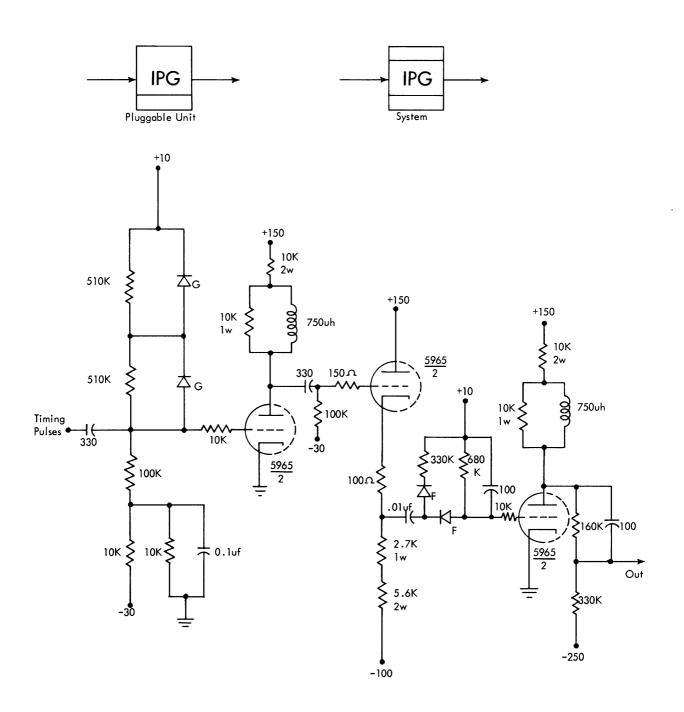

# NOTES

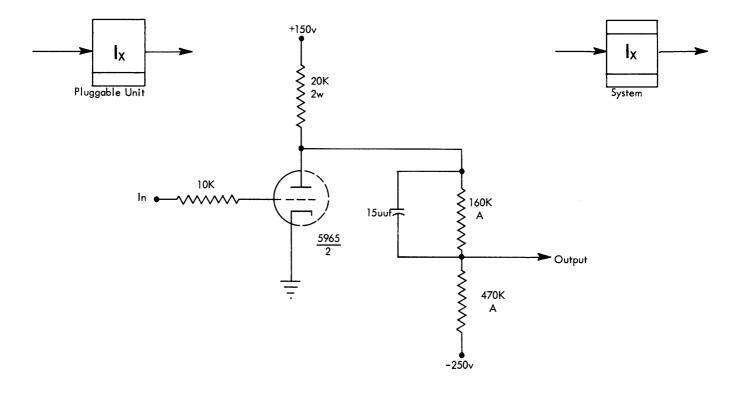

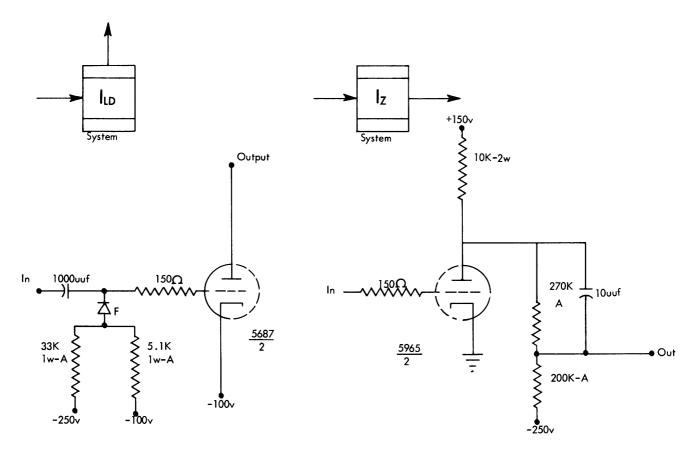

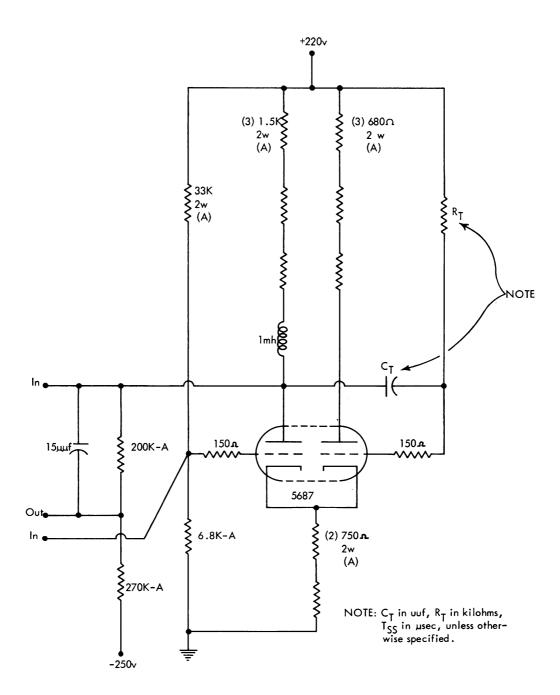

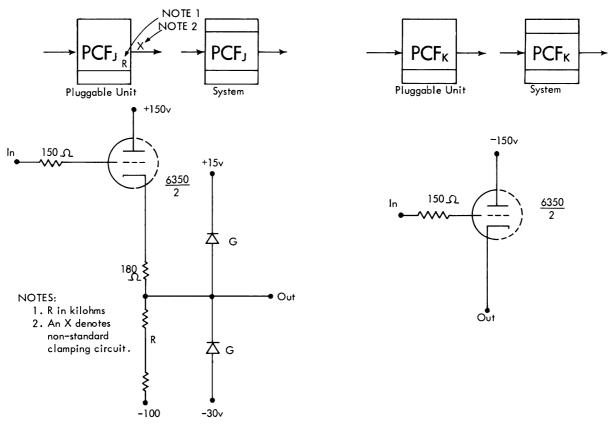

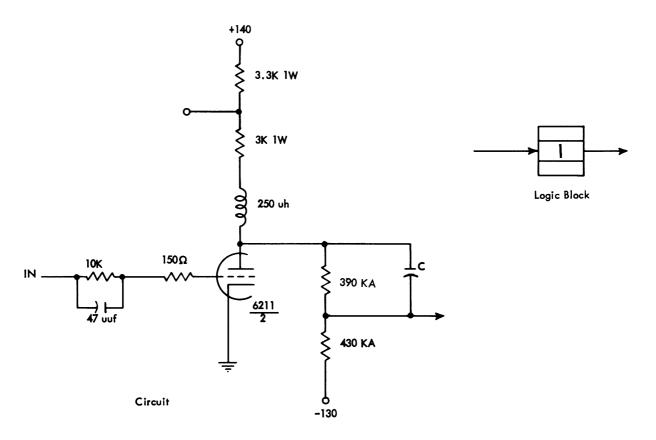

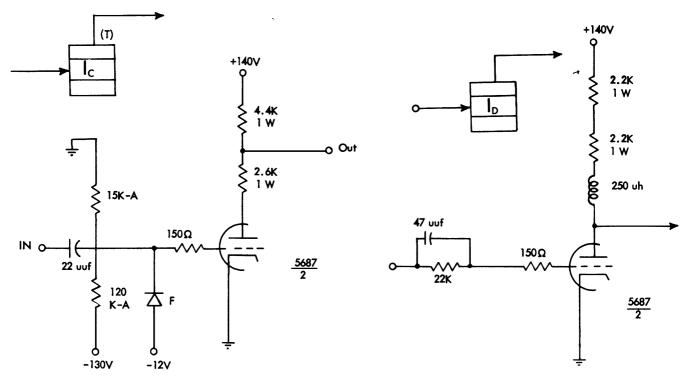

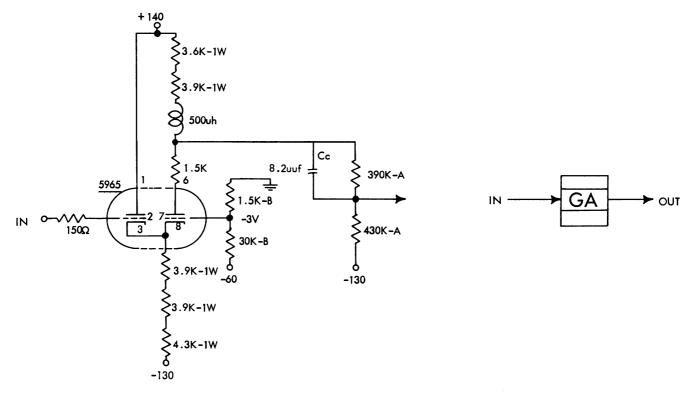

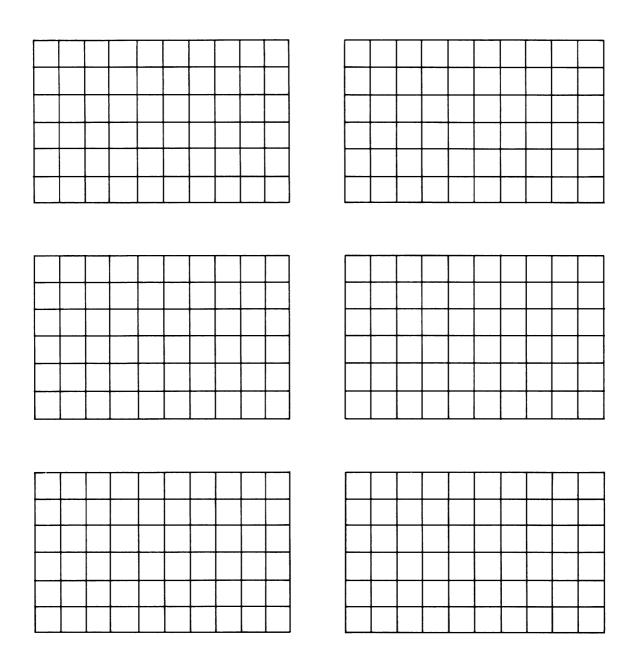

FIGURE A9. STANDARD INVERTER

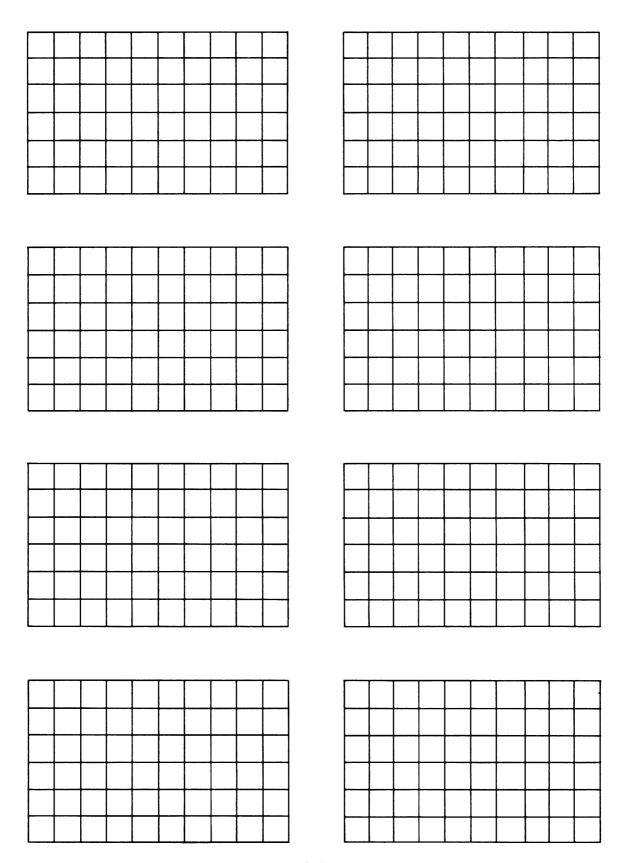

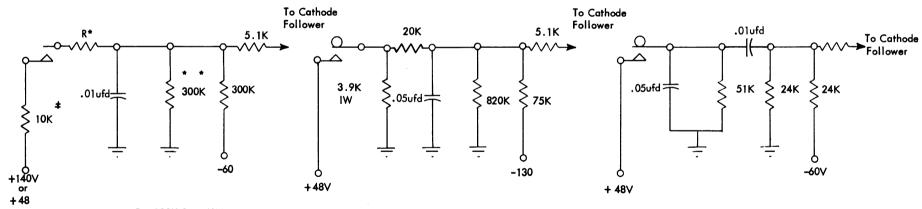

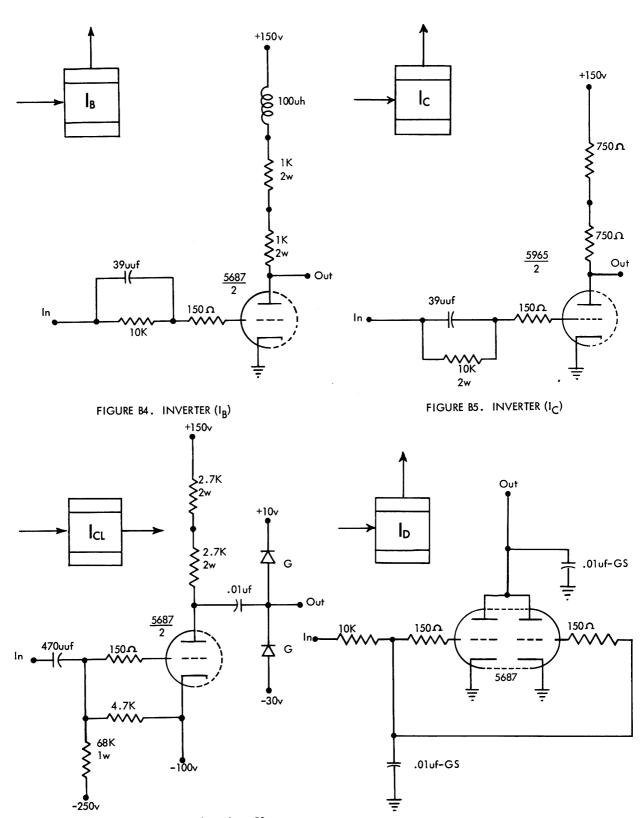

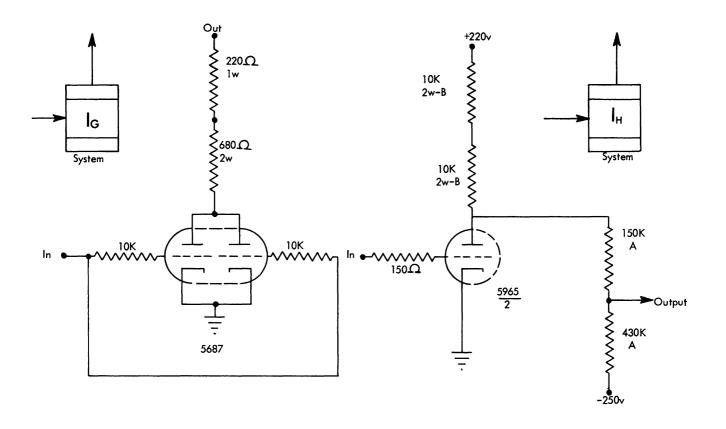

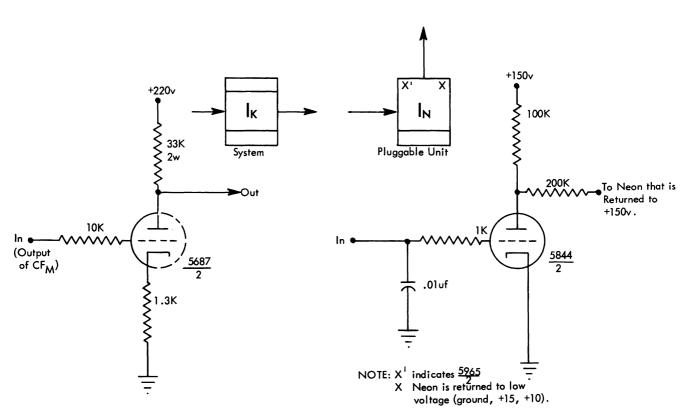

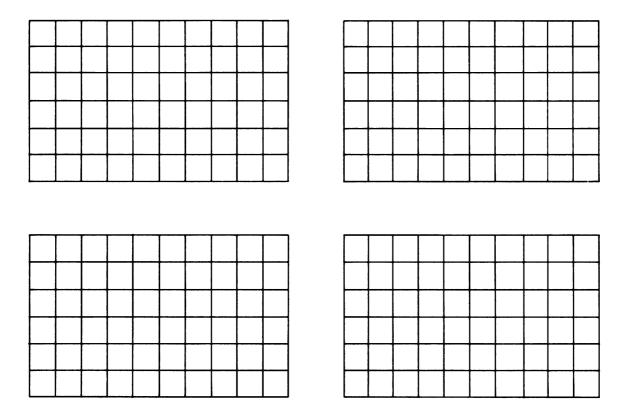

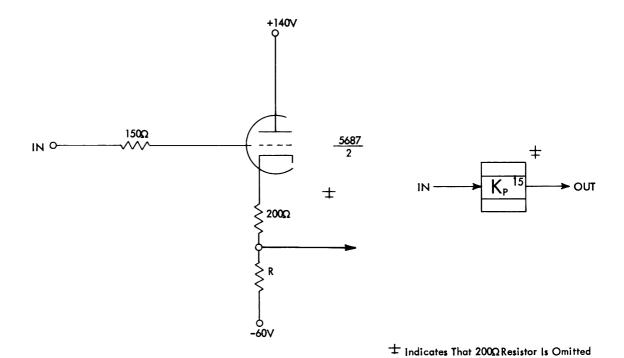

# 2.05.00 INVERTER (I) $(I_K)$

The standard inverter in the 700 series is the high-speed inverter (Figure A9). The inverter circuit produces a negative shift at its plate when a positive shift is applied to the grid, and a positive shift at its plate when a negative shift is applied to the grid. This property makes it useful in inverting logical conditions, such as changing binary zeros to binary ones. The inverter is also a level setter and pulse shaper because of its amplification properties.

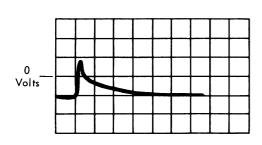

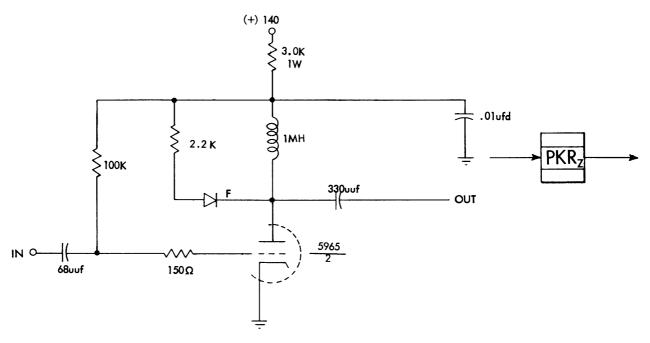

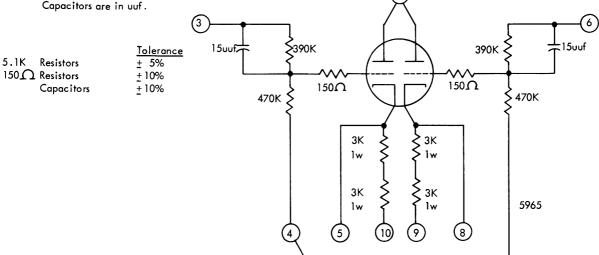

The large resistance in the plate circuit gives a large voltage swing, but does not slow down the signal transition appreciably. The coil in the plate circuit speeds the rise of the plate voltage. When the tube is cut off, the coil produces a voltage which for a short time makes the plate more positive than it would be without the coil. The coil causes a slight overshoot in this rise of the plate voltage but has practically no effect upon the fall time of the circuit. The effect of this coil on the voltage at the plate is shown in Figure A9f. The lower dotted line represents the voltage without the coil; the upper overshoot represents the voltage produced by the coil. The resultant shape of the voltage shows the tendency to square the rise; this results in a fast-rising voltage at the plate. The 10K resistor and its by-pass capacitor are used for grid current limiting when a low impedance driving circuit is used. The inverter has a nominal rise time of 0.2 usec (microsecond) and a fall time of 0.25 usec. An I<sub>K</sub> is the same circuit but uses one half of a 5965 tube.

# 2.05.01 Circuit Description

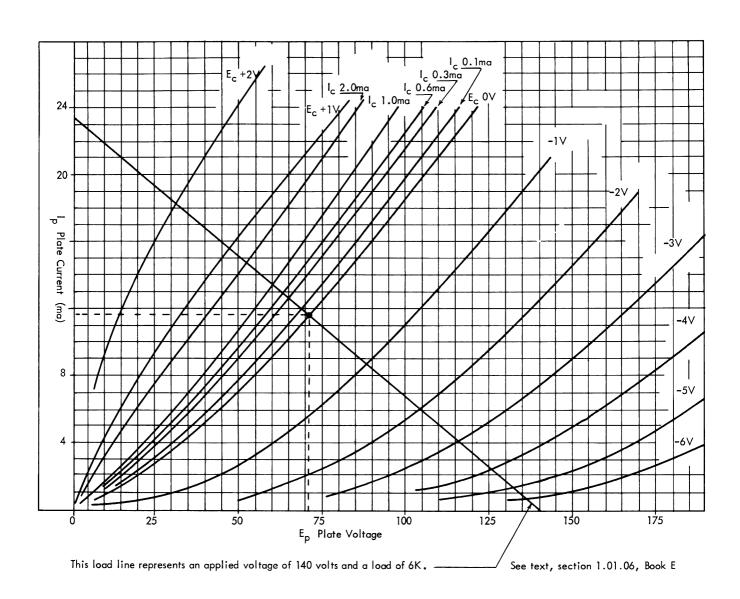

The minimum input requirements are +5 volts and -13 volts. Assume that the input voltage is -20 volts. The tube is well beyond cut-off because cut-off bias is -8.5 volts for a 6211. The divider output is at +10 volts because 0.33 ma are flowing through the divider circuit (Figure A9b). The DC resistance of the coil (25 ohms) is disregarded.

When the input rises to +5 volts or higher, the tube is in full conduction (Figure A9c). With a load of 6.3K, tube current is found to be about 12.3 ma. Grid current keeps the grid slightly above ground. The current flowing through the plate load causes the voltage at the plate to drop to +62 volts. However, the divider circuit is tied to the plate and the +62v level. Divider current drops to 0.23 ma and this current adds to the tube current through the plate load. The voltage at the plate is lowered to +62 volts and the divider output is -30 volts. Although this method of calculating plate current is an approximation, its simplicity overrules the small error involved.

The level-setting characteristic of the inverter circuit is shown in Figure A9d. Because the circuit is fully operated by only a portion of the input pulse, the amplification of the tube resets the levels of the pulse. Pulse shaping is aided by both the amplification and the action of the peaking coil.

## 2.05.02 Compensated Output

The circuit produces a fast rise and fall at the plate. This voltage shift must be fed to the next circuit where stray capacitance acts upon the shift. Figure A9e shows that if  $C_S$  is charged through  $R_1$ , the output wave form is distorted. However, by adding a compensating capacitor C, the wave form produced by CR2 adds to the

output. Thus  $C_S$  has a fast charge path and the output more nearly represents the voltage shift at the plate. The compensating capacitor is 8.2 uuf or 15 uuf depending on the input capacity of the next circuit.

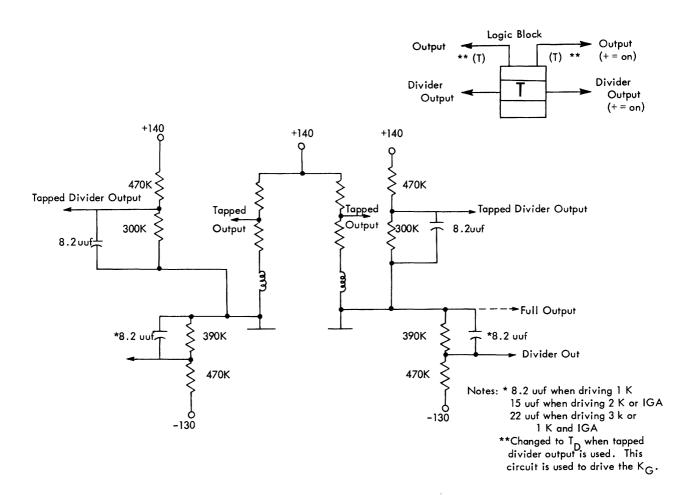

The divider output is high impedance and must feed a cathode follower directly (high impedance input). The voltage for a tapped plate swings from +139 volts to +99 volts, and at the divider output from +10 volts to -30 volts.

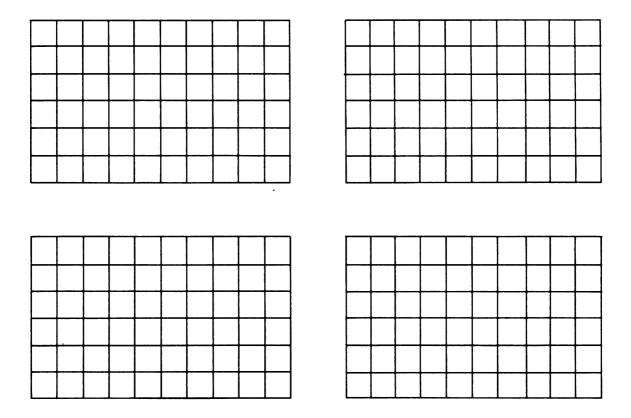

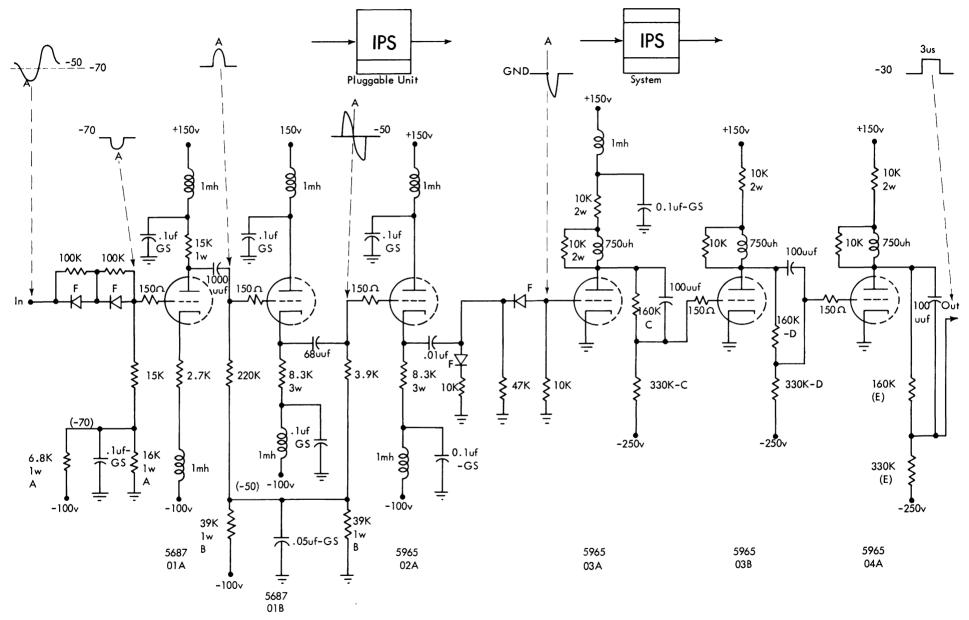

# NOTES

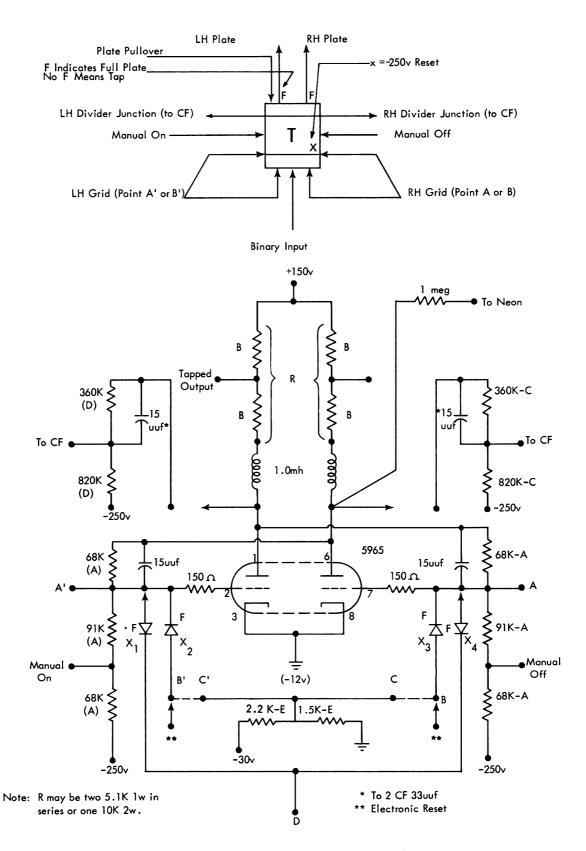

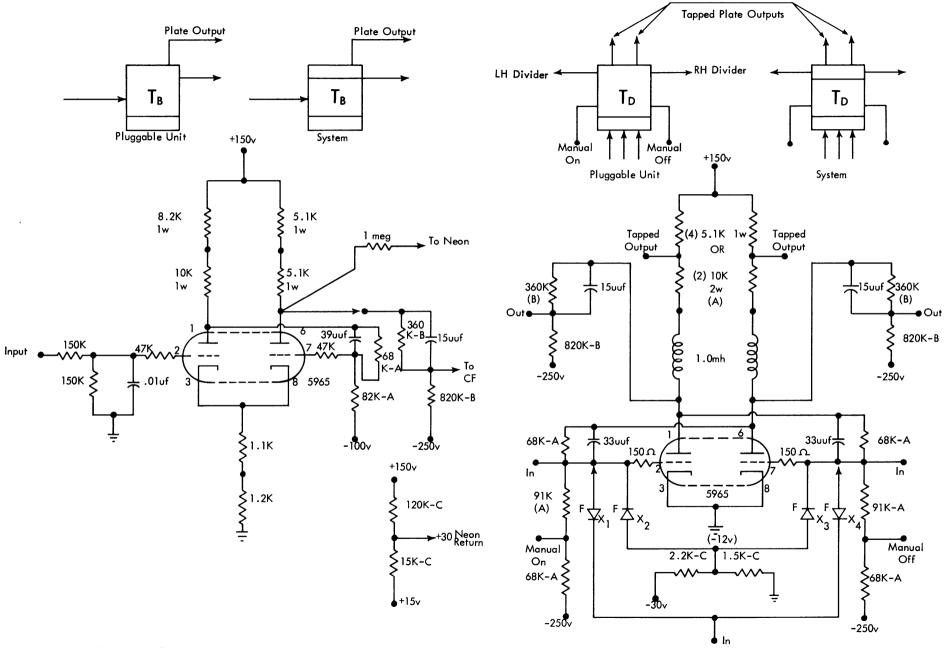

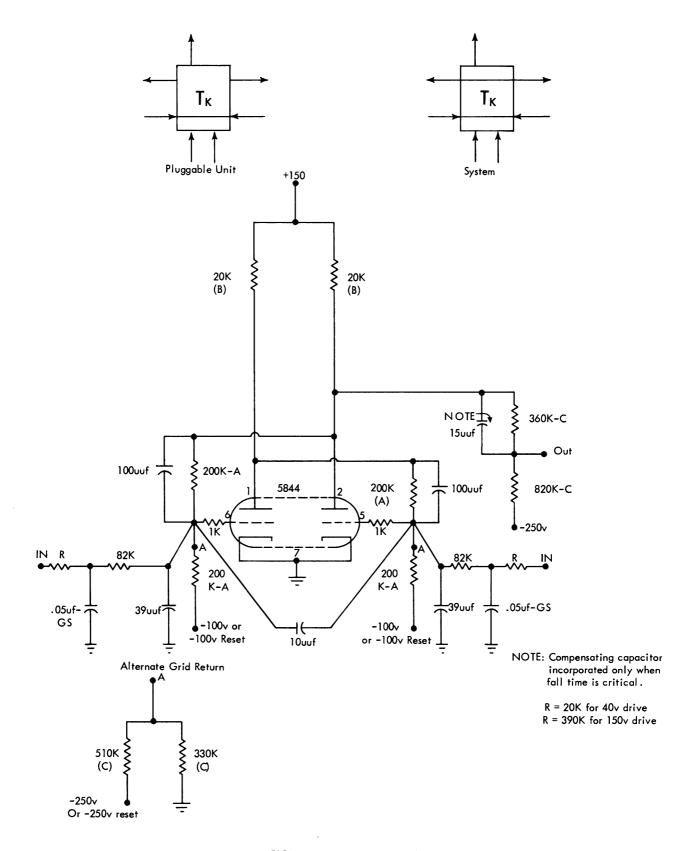

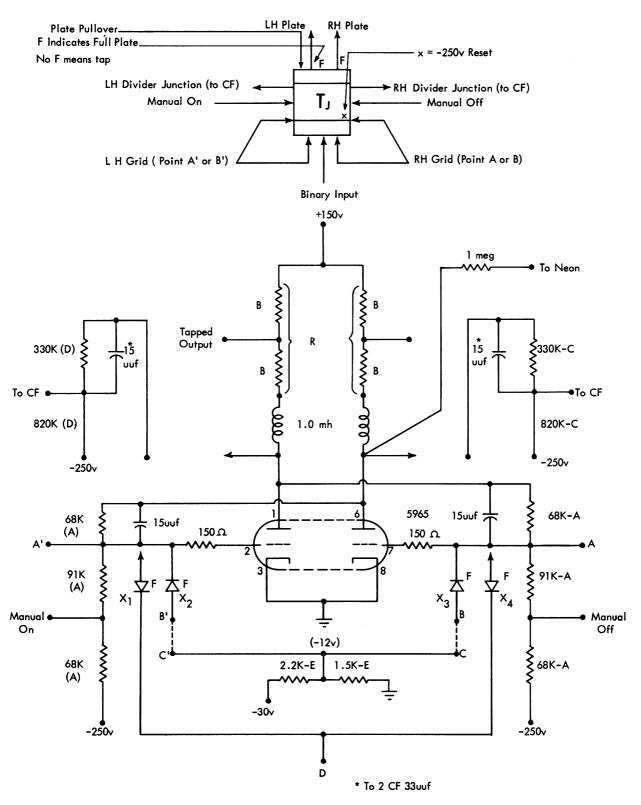

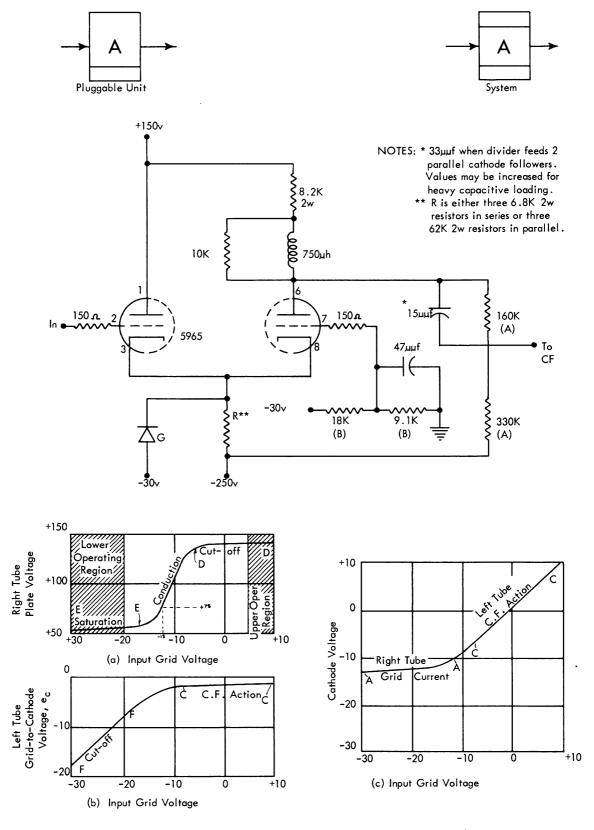

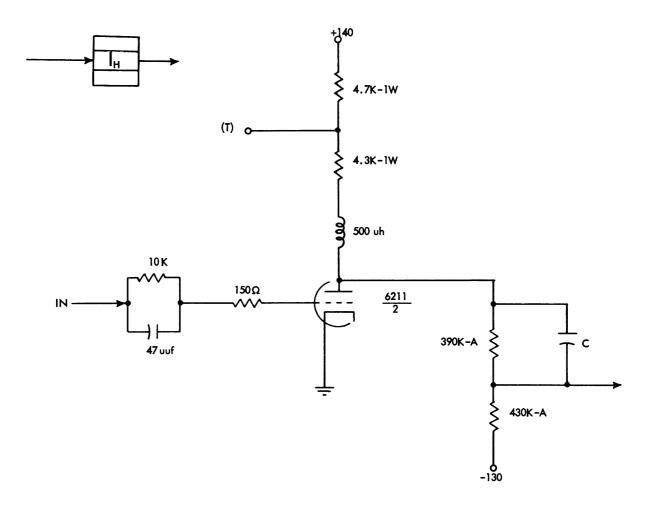

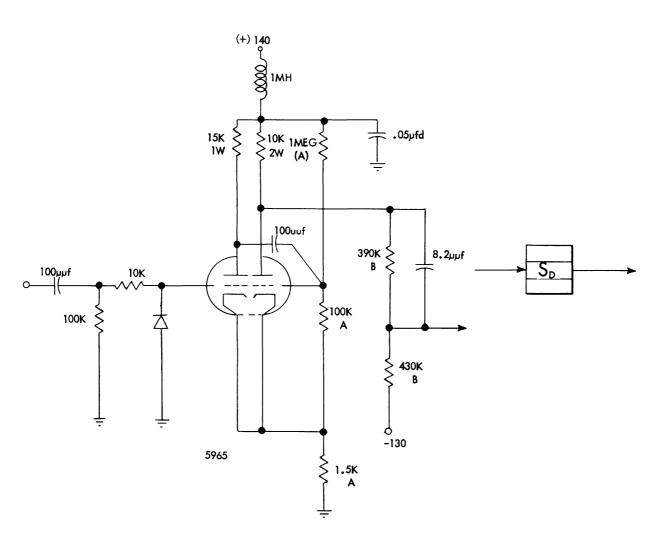

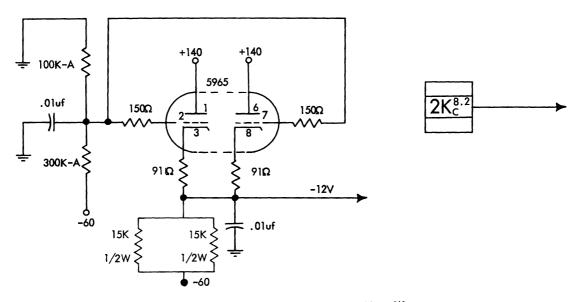

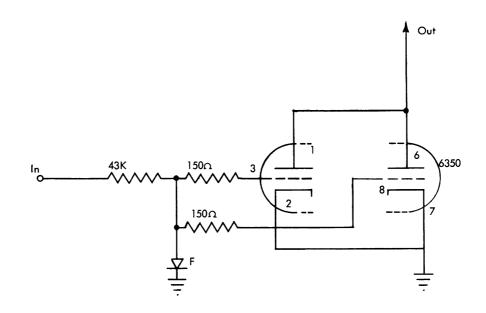

FIGURE A10. HIGH SPEED TRIGGER (T)

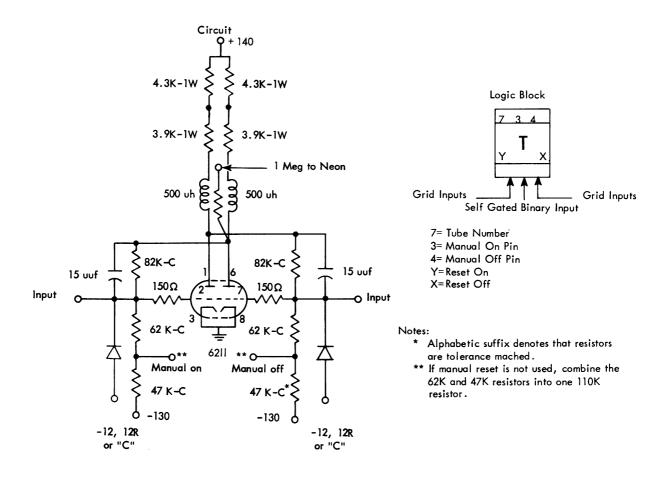

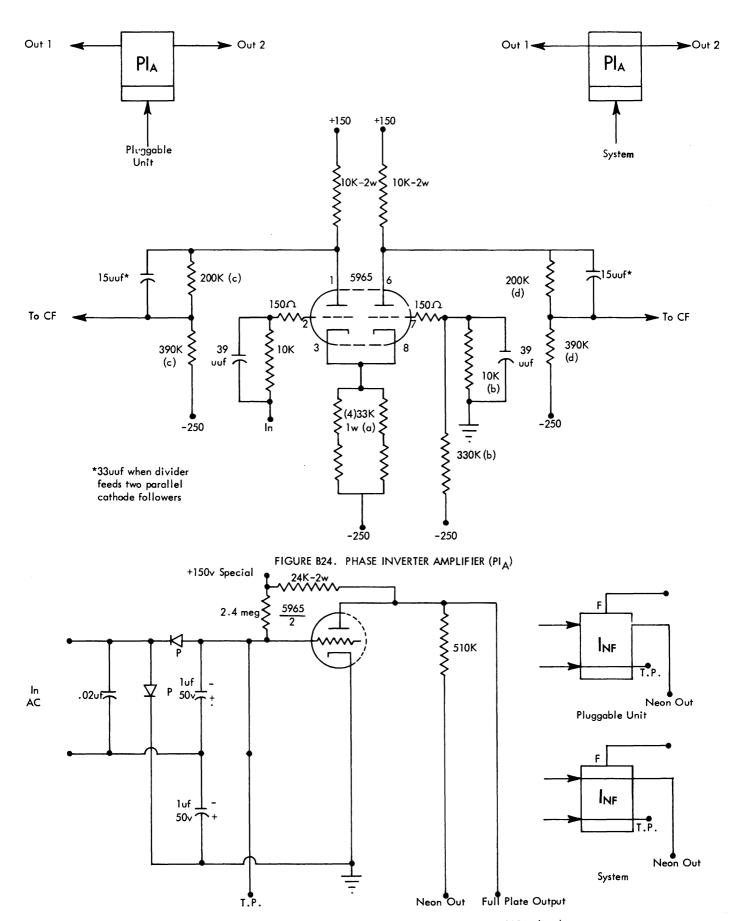

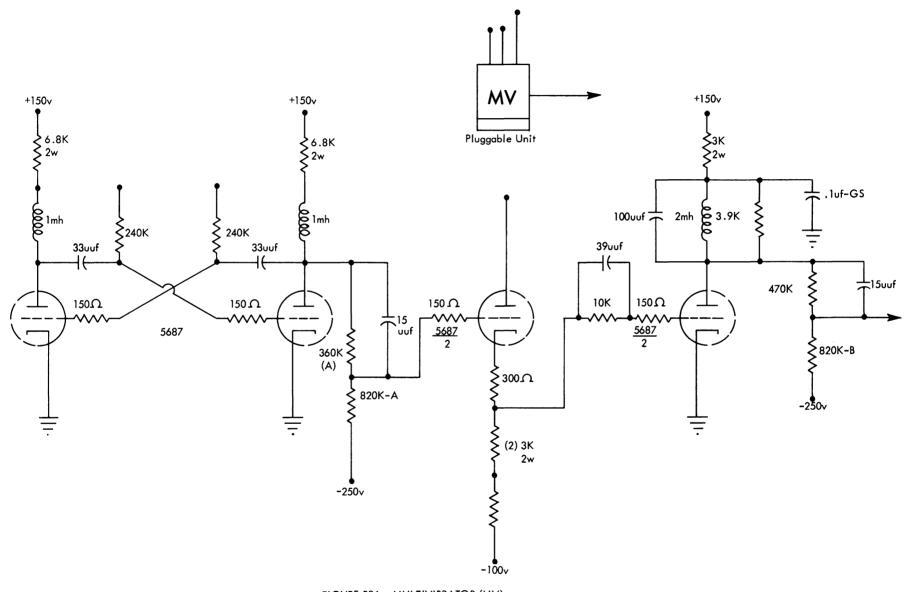

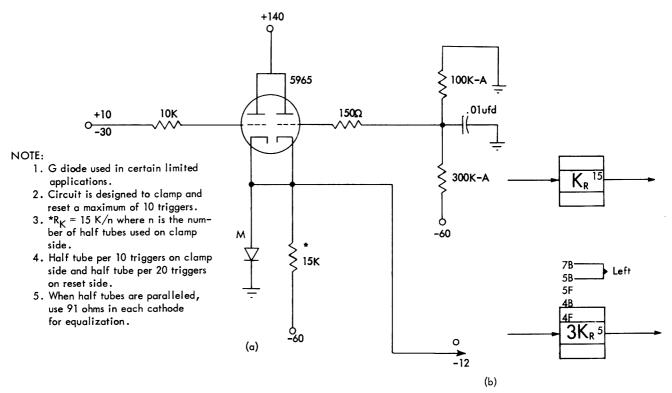

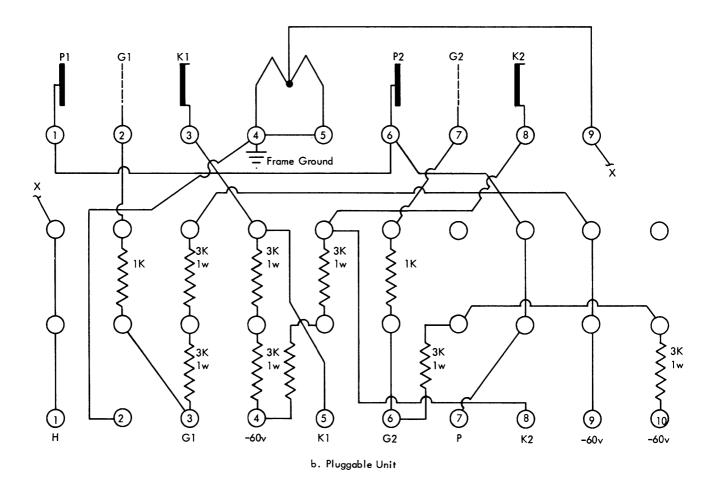

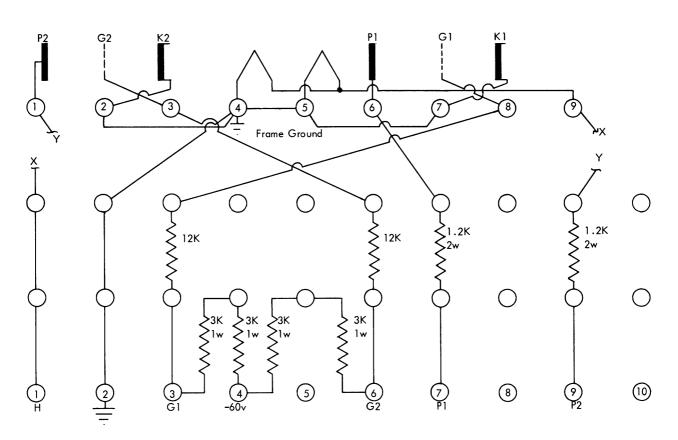

#### 2.06.00 TRIGGER (T)

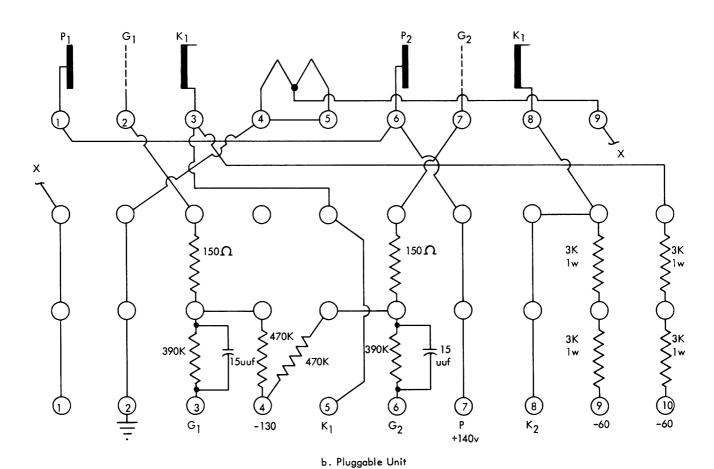

A trigger is a bistable multivibrator; that is, it remains in either one of two stable states until an external signal forces it to assume the other state. This forcing action is called triggering or flipping; another name for the trigger circuit is "flip-flop." The bistable property of a trigger makes it useful as a storage device. It is used in registers, counters, and gate-forming circuits.

# 2.06.01 On and Off Convention for Triggers

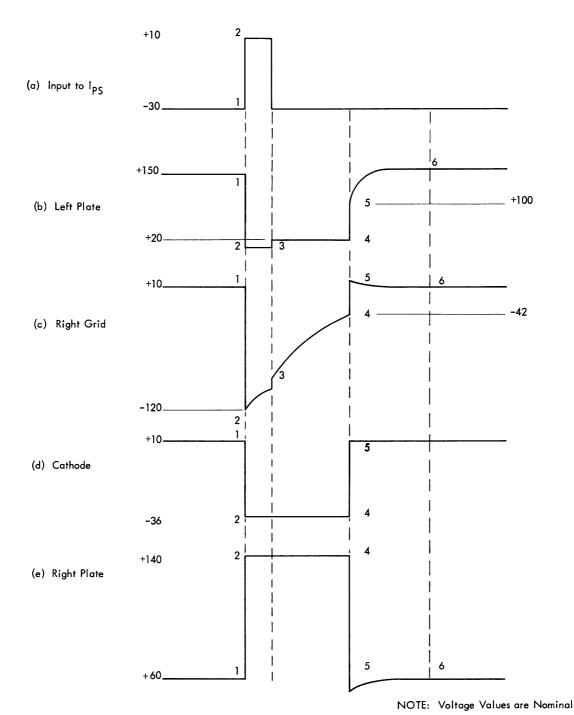

A trigger is said to be on when its left tube is conducting. Therefore, the left side is called the "on-side," and the right side is the "off-side." In the "on" state, the left grid is up, the right plate is up, the right grid is down, and the left plate is down (Figure A10). If a trigger is used for storing binary information, it is storing a one when on and a zero when off.

# 2.06.02 General Trigger Circuit Operation

Basically, a trigger circuit resembles two inverter circuits in that each plate output is coupled to the opposite grid. In one stable state, the left tube is in full conduction (about 9.5 ma) while the right tube is cut off. In the other state, the right tube is in full conduction while the left tube is cut off. To change from one state to another, an external signal must be applied to a sensitive point in the trigger circuit.

For example, assume that the right tube is conducting (trigger off). The right plate is down; that is, its voltage is considerably less than +140 volts, while the left plate is up (near +140 volts). One method of flipping this circuit is to apply a negative pulse to the right grid. Because the right tube is conducting, grid current keeps the grid at about zero volts. The negative input pulse causes the right tube to cut off; consequently, the right plate voltage rises. This rise is then coupled through the plate-to-grid voltage divider (cross coupling circuit) to the left grid, pulling this grid voltage up toward ground. The left tube then begins to conduct, pulling its plate voltage down. This shift at the plate of the left tube is coupled back to the right grid and reinforces the initial action. The cross coupling circuits speed the regenerative action and the circuit stabilizes with the right side cut off and the left side in full conduction. The input pulse can now be removed without reflipping the trigger, because conduction on the left side holds the right side cut off.

The trigger can also be flipped by applying a positive pulse to a non-conducting grid or by lowering the plate voltage of a cut-off side through an external circuit. In any case, an input pulse must initiate a regenerative action to cut off the conducting tube and bring the non-conducting tube into full conduction.

# 2.06.03 Specific Components in a Trigger

Each plate is coupled to the opposite circuit through a compensated voltage divider. High-speed operation is obtained with the aid of the peaking coils in each plate circuit. The plate circuit may contain one resistor or two from which a reduced plate voltage swing may be taken as an output.

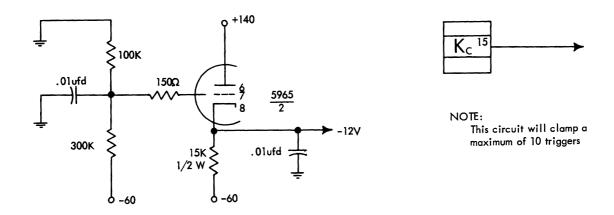

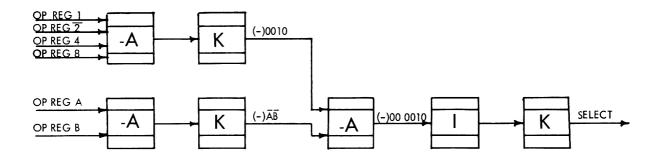

e. +OR Fed by Single Input and a +AND

To prevent delay in the flipping of a trigger caused if the down grid voltage is far below cut-off, the grids are clamped by diodes. The plate of the diode is a -12v power supply. Any attempt to lower the grid voltage below -12 volts causes the clamp diode to conduct harder. With this procedure, the grids need to rise only a few volts to start conduction.

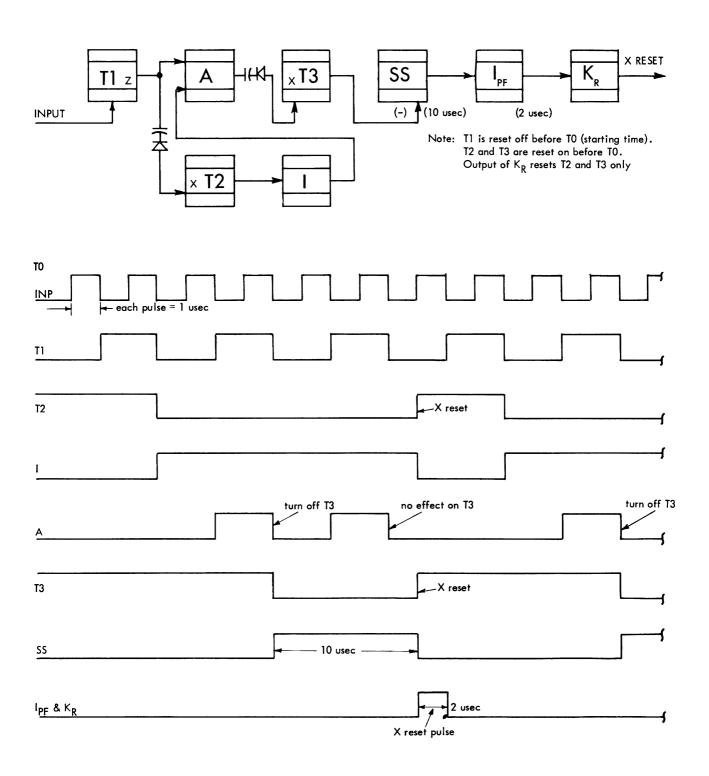

#### 2.06.04 Electronic Reset

Because either side of a trigger can go into conduction when power is first applied, a provision must be made to establish a specific status. The trigger may be reset with the output of the reset cathode follower ( $K_R$ ) applied at the desired reset point. The reset cathode follower is usually preceded by either the pulse forming inverter ( $I_{PF}$ ) or a single shot (SS). The reset point is the plate of the -12v clamp diode. The reset cathode follower provides -12v as a clamp voltage and changes to zero volts for reset. Bringing the plate of the clamp diode to ground forces a non-conducting grid up; that side of the trigger goes into conduction. The reset pulse lasts long enough to insure that the regenerative action is complete. The notation of reset is placed in the title section of the logic block (Figure A10). The notation on the left indicates "reset on." and on the right indicates "reset off." A trigger may have several resets, but only one takes place at a time. The origin of the reset is marked on the Systems page.

Triggers may also be reset by the output of other triggers but in this case, they are pulled over (Book A, section 2.06.06) in the usual manner rather than by applying the pulse to the reset point. All triggers with the letter X in either the right or left-hand corner (depending on whether the trigger is to be reset off or on) are reset by "power on reset" through a reset cathode follower.

#### 2.06.05 Manual Reset

A manual method of flipping helps to test the trigger circuit. The points in Figure A10 marked "manual on" or "manual off" are wired to pins on the panel. If a trigger is on and the manual-off pin on the panel is touched by a tweaking probe, the trigger is flipped off. The tweaking probe is merely a line connected through a by-passed, high-impedance resistor to ground. The ground connection pulls the tweak points (manual points) up toward ground, thus providing a positive shift at the grid to flip the trigger. Tweaking the manual-on point turns the trigger on if it was initially off.

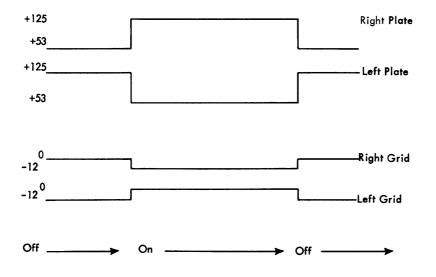

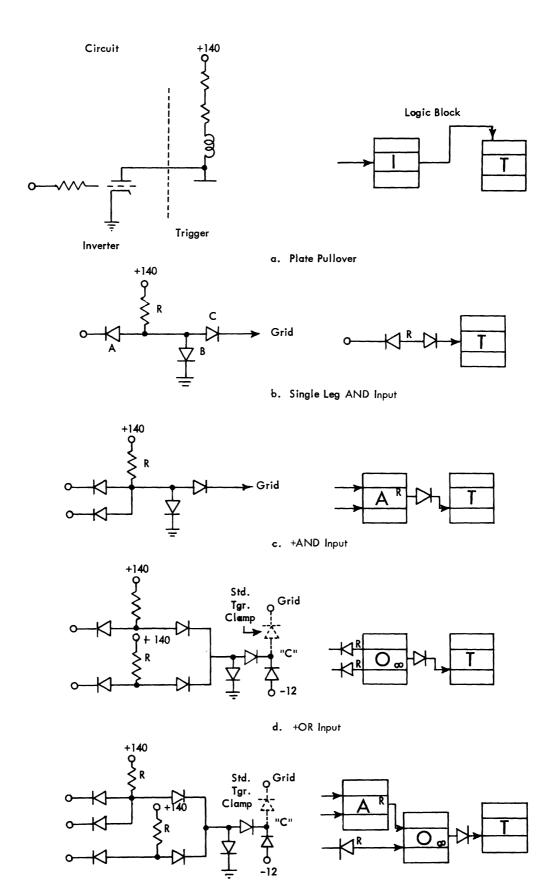

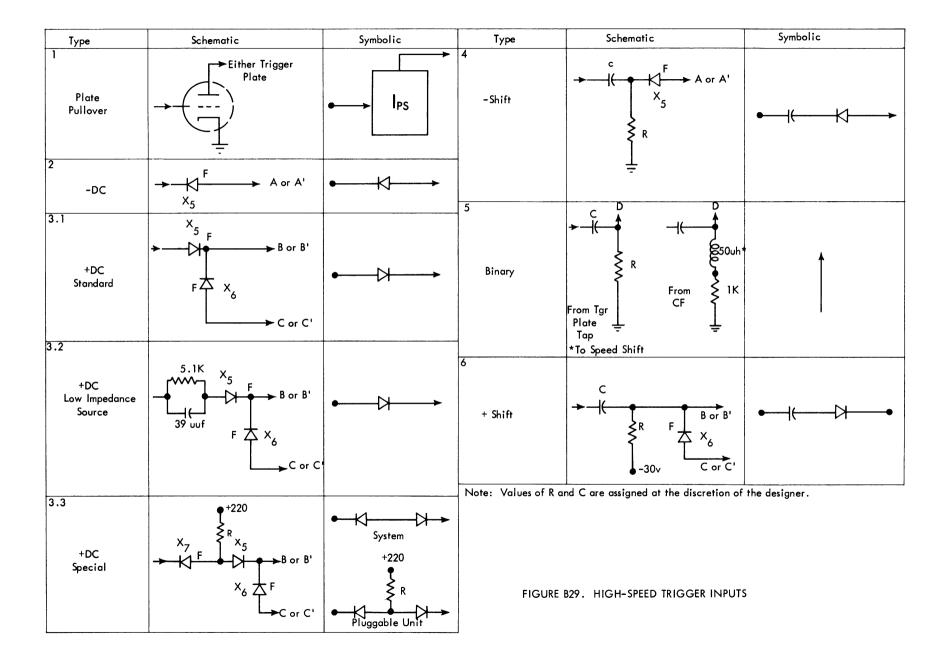

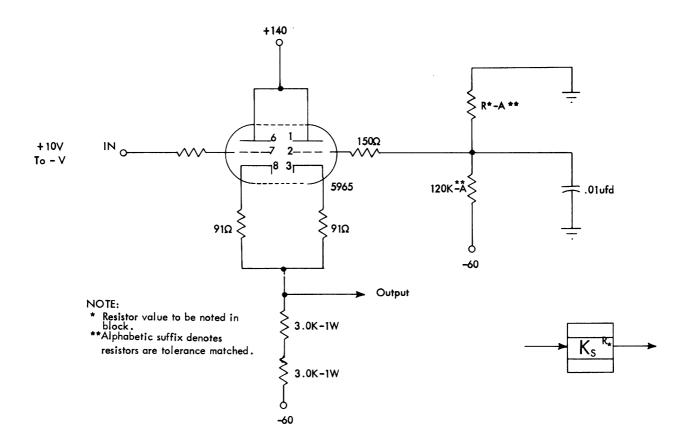

# 2.06.06 Inputs to a Trigger

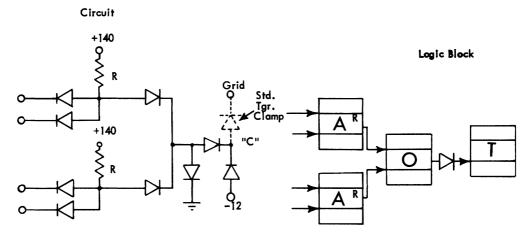

Figures A11-A14 show several inputs to a trigger circuit. These are explained as follows:

#### Plate Pullover Input

The simplest input is the plate pullover type (Figure A11a). The plate pullover input is merely an inverter whose plate is connected to a plate of the trigger circuit. The plate load of the inverter is the plate resistor of the trigger. When a positive pulse is applied to the grid of a pullover inverter tube connected to an up plate of a trigger, the negative shift at the plate caused by conduction through the plate resistor of the trigger causes the trigger to flip. As long as the input to the pullover inverter

a. +OR Circuit Fed By 2 +AND Circuits

FIGURE A12. TRIGGER INPUTS (cont'd)

remains positive, no external signal on any other input to the trigger can flip it. That is, the plate pullover method exhibits holding action. If the inverter were connected to a down plate of a trigger, then the application of a positive gate to the pullover inverter grid would not affect the trigger in any manner other than producing a holding action.

#### DC Inputs

Several AND/OR circuit configurations are used as DC trigger inputs. All are grid inputs and they exert holding action on the trigger when the DC input is up. Each circuit contains a clamp diode to prevent driving the grid above ground. Although normal AND/OR circuit outputs swing between +10 volts and -30 volts, the ground clamp and the -12v grid clamp keeps the swing between 0 volts and -12 volts.

A typical application is the one-legged AND circuit feeding the trigger (Figure A11b). Assume that the input is -30 volts and the grid is non-conducting (-12 volts). The base of the limiting resistor is -30 volts and diode C is cut off. As the input rises to +10 volts, the base of the resistor rises to zero and is held at that point by the ground clamp, diode B. Diode C starts to conduct at -12 volts and continues to conduct, forcing the grid up. The tube conducts; the trigger flips and is held in this status by the holding action of the input circuit. When the input drops to -30 volts, the voltage at the base of the resistor falls to -30 volts also. Because the trigger grid stays at zero volts (conducting), diode C cuts off as soon as the input passes zero volts on the fall. Only the holding action has been removed and the trigger does not flip back until impulsed by a different input.

The same operation takes place when the OR circuit block feeds the trigger (Figure A11d). The infinity sign in the block means that the return resistor for the OR circuit is in the grid circuit of the trigger. In all cases, the diode closest to the trigger block indicates the polarity of the pulse operating the trigger.

Figure A11d shows the normal clamp diode used as an input. An additional diode is added for clamp and reset purposes. Usually the clamp diode is used as an input when several input circuits are tied to the same grid. This procedure increases the impedance of the grid circuit in the same manner as cascading in AND/OR circuits. This increased impedance is necessary to prevent unbalancing the grid circuits and producing unstable triggering.

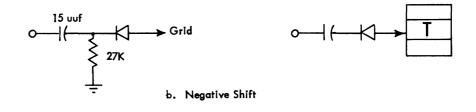

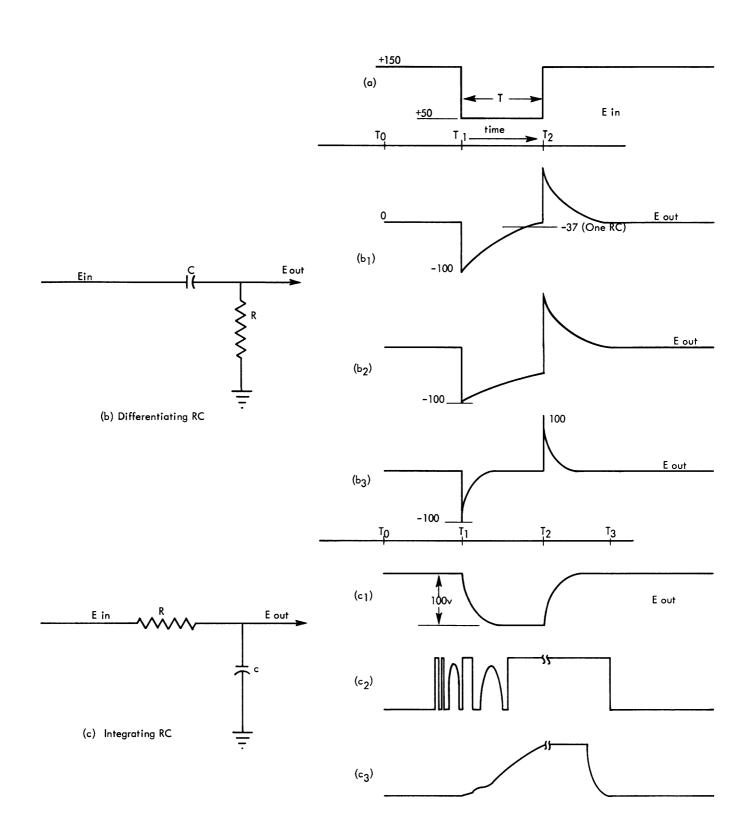

#### Negative Shift Input

The negative shift input (Figure A12b) is an AC input and does not exhibit holding action. The negative facing diode blocks a positive shift and allows a negative shift to cut off the tube. Because of the RC circuit involved, recovery time of the input circuit is a necessary consideration. A notation, such as 0.2 usec, may be placed near a shift input to denote the recovery time. The notation 0.2 usec means that the input must be positive for 0.2 usec before a negative transition begins. The RC circuit must recover (time out) to transmit the full shift to the grid.

FIGURE A13. SELF GATED BINARY INPUT

FIGURE A 14. TRIGGER OUTPUTS

#### Binary Input

The binary input is a negative shift input to a trigger and allows it to be flipped regardless of its previous state (unless it is being held by another circuit). A binary input is indicated when the same signal is applied to both the left and right grid (Figure A12c). For example, if the trigger is off and it is fed a pulse through a binary input, the trigger is flipped on. If another pulse is then applied to the binary input, the trigger is flipped off.

One grid is initially at ground, and the other is about -12 volts. The negative shift begins at ground and pulls the conducting grid negative. The first twelve volts of the negative shift cannot affect the cut-off grid because the binary input diode connected to that grid is cut off. By the time this diode is ready to conduct, the regenerative action initiated by the negative shift on the opposite grid produces a positive shift at the formerly cut-off grid.

If the differentiated spike is narrow enough and not excessively large in amplitude, it does not interfere with the positive shift at the formerly cut-off grid. However, if it is too wide or too large in amplitude, it may interfere with the positive shift, causing the trigger to flip back to its initial state. For this reason, the binary input should not be fed a pulse of very great amplitude.

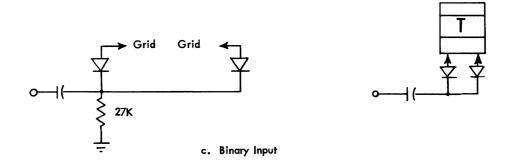

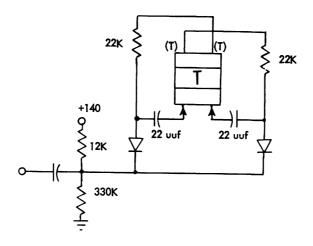

# Self-Gated Binary Input

The most widely used binary input to a trigger is the self-gated binary. It is used when pulse amplitude and width would affect a normal binary input. The circuit is shown in modified block form in Figure A13. When the ordinary binary input exhibits self-gating action for the first 12 volts of the negative input shift, the self-gated input exhibits this property for the full pulse amplitude because of the different voltage levels maintained at the input diodes.

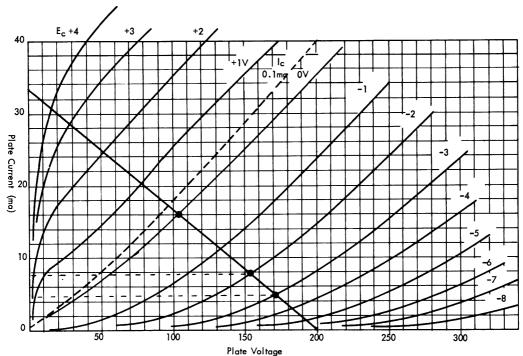

The voltage at the junction of the 12K and the 330K resistors is about +135 volts. When the input is a -30v shift, the voltage at the diode junction is then +105 volts. Now the potential at the junction of the diode, the 22K resistor and the 22-uuf capacitor of the conducting side of the trigger, is about +132 volts. The potential at this same point on the cut-off side is about +94v. Thus, the diode on the cut-off side cannot conduct while the one on the conducting side conducts. The conducting grid is brought down; this side ceases to conduct while the cut off grid is brought up to ground and starts to conduct.

The driving circuit may be either a standard cathode follower with the minimum load or a standard 6211 inverter tap or trigger tap. The inputs are 25v to 35v negative shifts. The input fall time must be less than 0.25 microsecond for a 25v input and less than 0.4 microsecond for a 35v input. Recovery of the input network limits the frequency of operation to 150KC maximum (with minimum input signal). The trigger output rise time is 0.35 microsecond; the fall time, including delay, is 0.2 microsecond.

### 2.06.07 Input Requirements for the Trigger

The following are minimum requirements for flipping a trigger with various inputs:

Plate Pullover: standard inverter input.

DC: lower level -20 volts to -30 volts; upper level +5 volts to +15 volts.

Minus Shift: 25v minus shift; 60 volts/usec minimum slope. Binary input: 25v minus shift; 60 volts/usec minimum slope.

# 2.06.08 Outputs from the Trigger

There are four types of outputs from a trigger (Figure A14). The full plate swing of either plate may be used, or the plate resistor may be tapped when a smaller swing is needed. Generally, this tapped output is used for feeding binary inputs of other triggers. A standard signal level may be obtained from a voltage divider connected to either plate. If the divider is not used, it is not wired into the circuit. When driving a plate-level cathode-follower  $K_G$  (702-705 components only), a special divider from the trigger plate to +140 volts is used. The output of this tapped divider (TD) is about the same as the tapped plate.

### 2.06.09 Voltage Levels in the Trigger

The following are nominal voltage levels in a high-speed trigger:

Full plate: +53 volts and +125 volts (divider connected).

Tapped plate: +94 volts to +132 volts (divider connected).

Divider output: -30 volts to +10 volts.

Grid: Tends to go down to -25 volts but is clamped by diode at -12 volts.

Tends to go up to +17 volts but is grid-clamped at about ground.

Manual reset points: -74 volts to -79 volts.

When the voltage divider is not connected to the plate output, the upper plate level is +125 volts, and the lower level is only a few volts higher than the +53 volts. A trigger may produce some delay and gives a nominal rise time of 0.35 usec and fall time of 0.3 usec.

#### 2.06.10 Block Representation of the High-Speed Trigger

A single trigger may have many outputs; it may have different inputs to the same grid or the same type of inputs to opposite grids. A grid input may be shown in either lower corner. A self-gated binary input is indicated merely by a straight line drawn into the middle of the bottom of the block. Diodes closest to the trigger block indicate the polarity of the voltage affecting the trigger.

A tapped output is represented by a line coming out of the top of the block near one side and with a T placed next to the line. Full plate outputs are represented similarly with no T. The divider output is drawn from the side of the block. When the divider is changed to drive a plate level cathode follower, a TD is placed next to the line at the top of the block.

### 2.06.11 Special Features

To indicate the state of a trigger, a neon is usually connected through a one-megohm resistor to the right plate. The neon is mounted on the panel and is returned to ground. It is lit when the trigger is on. A trigger circuit always uses the half tubes in the same envelope. If a manual reset is not used, the 62K and 47K resistors are combined into one 110K resistor (grid return). Values of compensating capacitors are changed in the same manner as in the inverter.

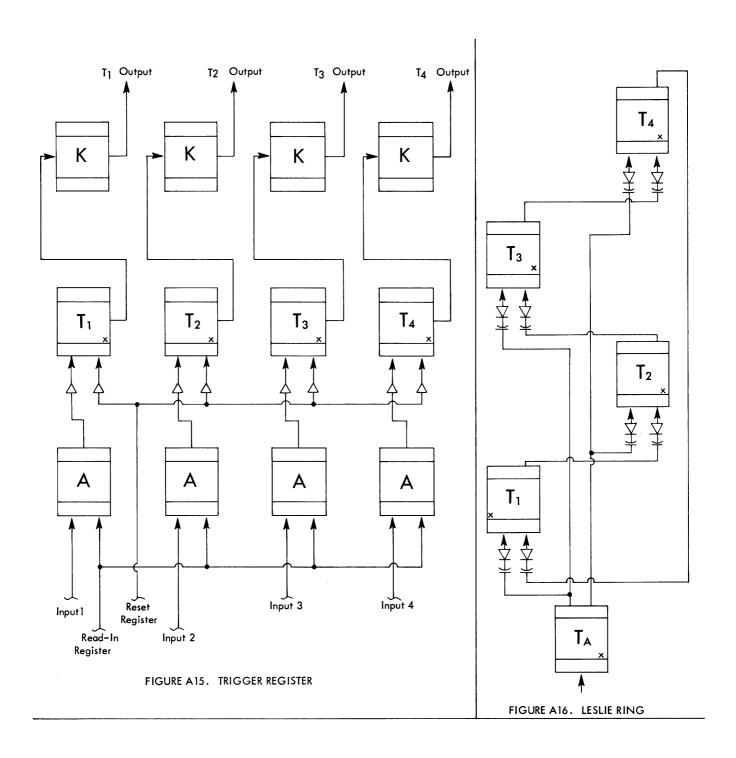

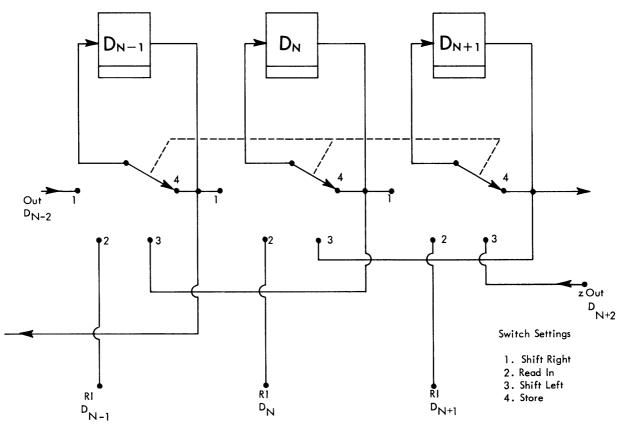

# 2.06.12 Application of Triggers

### Trigger Registers

Trigger registers are frequently used as temporary storage throughout the 700 series. An example of a four-position register is shown in Figure A15. The register is reset by opening the -250v bias at the off-side. It may also be reset by "reset register." When this line goes positive, it resets the triggers off through the +DC inputs to the off-side of each trigger. The triggers store the information fed to the inputs. At read-in-register time, the input lines are sampled at the AND circuits across the bottom of Figure A15. If any of the AND outputs goes positive, the trigger tied to it through a +DC input is turned on. This information is stored here until the next reset time. The output of the register is available from cathode followers tied to the off-side plates of the triggers.

### Leslie Ring

As shown in Figure A16, the on-side grids of alternate triggers are connected together and each set is connected to opposite sides of binary connected trigger  $(T_A)$ . The input to the ring is fed to the binary trigger, the negative shift at the on-side plate is fed to  $T_1$ , turning  $T_1$  off. Note that at  $T_2$ , there is now a negative pulse turning the trigger on while a positive shift to the on-side grid is not seen by the trigger, since the negative-shift input is being used. With the next negative shift to the binary trigger, the trigger goes off, sending a negative shift to  $T_2$  and  $T_4$ . This negative shift turns  $T_2$  off. The fact that  $T_2$  is going off gives a negative shift to  $T_3$ , turning it on. Again, note that  $T_3$  is being hit only at the off-side grid. The ring steps around in like manner until the last trigger goes off. If the output of the last stage is not fed back to close the loop, the ring stops when the last trigger goes off.

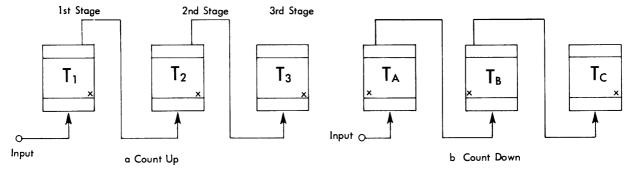

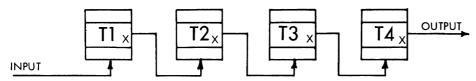

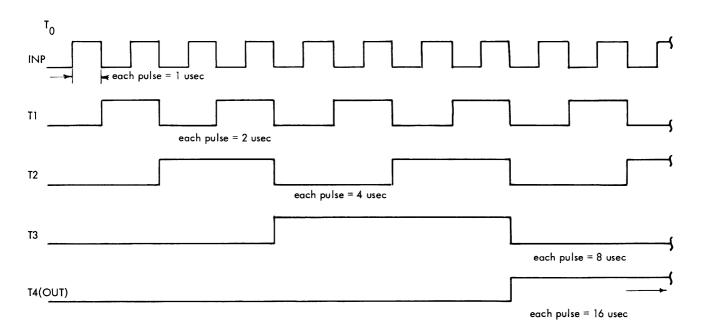

### **Trigger Counters**

Pulses can be accumulated in binary triggers in the form of trigger counters. As shown in Figure A17a, the counter is reset with all the triggers off. The input is fed to the first stage only. As the first negative shift is fed to the input, the first stage goes on, making its off-side plate go plus. This pulse shift is fed to the second stage with no effect. As the second negative shift at the input turns the second stage on. Note at this time that only when a trigger goes off does it affect the following stage. With a third impulse, the first stage is turned on, leaving the first and second stages on and the third stage off. With the fourth negative shift at the input, the first trigger goes off, feeding a negative shift to the second stage, and turning it off. As the second stage goes off, the negative shift from its off-side

FIGURE A17. TRIGGER COUNTERS

plate turns the third stage on. By correlating the triggers that are on with the number of pulses fed to the system, the first stage may be said to represent one, while the second stage represents two, and the third stage represents four. At this time, we have fed four pulses to the counter and have turned on the third stage indicating the sum of the input pulses. With the fifth pulse, the first stage again goes on, leaving the third stage on and indicating the accumulation of four and one.

As the counter accumulates, it may be shown that the sixth pulse would turn on the second stage. Likewise the seventh pulse turns the first stage on, leaving the equivalent of four, two, and one in the counter. With the eighth pulse, all positions are turned off, restoring out counter to its original condition. This counter is said to be an octonary counter. Similarly, counters with various radices (base numbers) may be constructed. To achieve this, various forms of blocking and feed-back circuits are used when the radix of the counter is not an integral power of two. The illustration discussed above is sometimes called a "count-up" counter. There is application in the 704 for "count-down" counters. Such a configuration is shown in Figure A17b. In this application the counter is usually set up to some predetermined value, and pulses are subtracted from this value. Let us say that by some means the counter is reset, as indicated by the X's in Figure A17b. This would put a 3 in the counter. To subtract 1 for each input pulse, the counter goes to zero with three pulses. The first pulse to the counter turns the first stage off. Using the output from the on-side, note that there is no further action in the counter since a positive shift from the on-side of the first stage has no effect on the binary input of the second stage. As the next pulse comes in, the first stage is turned on. This gives a negative shift to the second stage, turning the second stage off. The third pulse turns the first stage off leaving the counter with all zeros. The output of the triggers is tested to determine when the counter goes to zero, thereby indicating when a predetermined number of pulses has been sensed.

Note that the count-up and count-down counters are basically alike, but the carry from stage to stage is taken from opposite plates. A reason for using the count-down counter is that the counter does not have its "ripple-down" just before it registers zero. The term "ripple-down" pertains to the action of a count-up counter when all the triggers of the counter are on and the next pulse must turn each of the triggers off in succession. Ripple-down also describes the action in a count-down counter when all the triggers are off and the next pulse turns each stage on. Since it takes a definite time to flip a trigger, the time is accumulative in ripple-down and a considerable delay is introduced in the system.

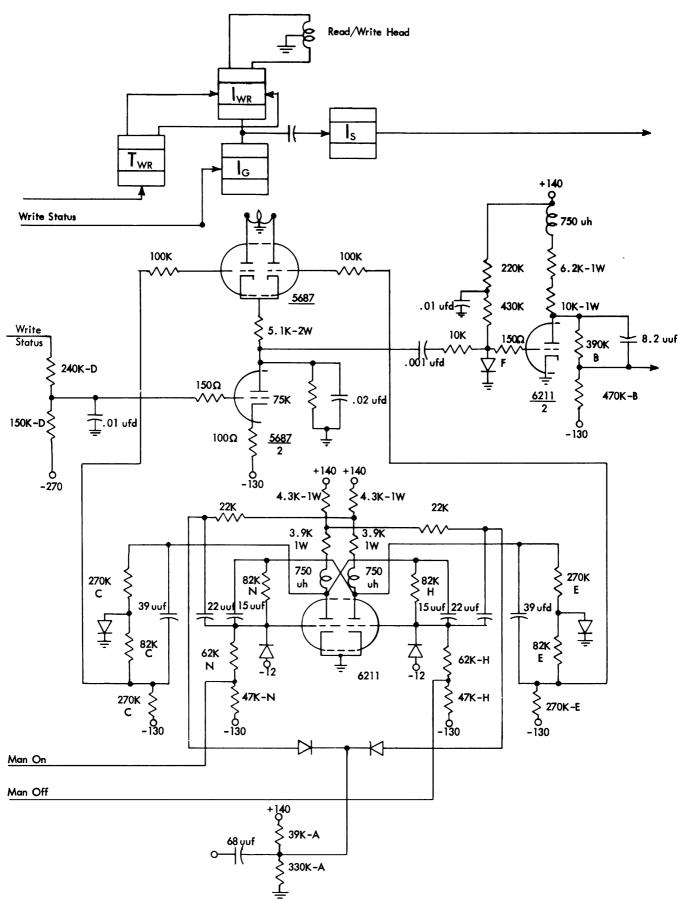

FIGURE A18. DIODE GATE - DG

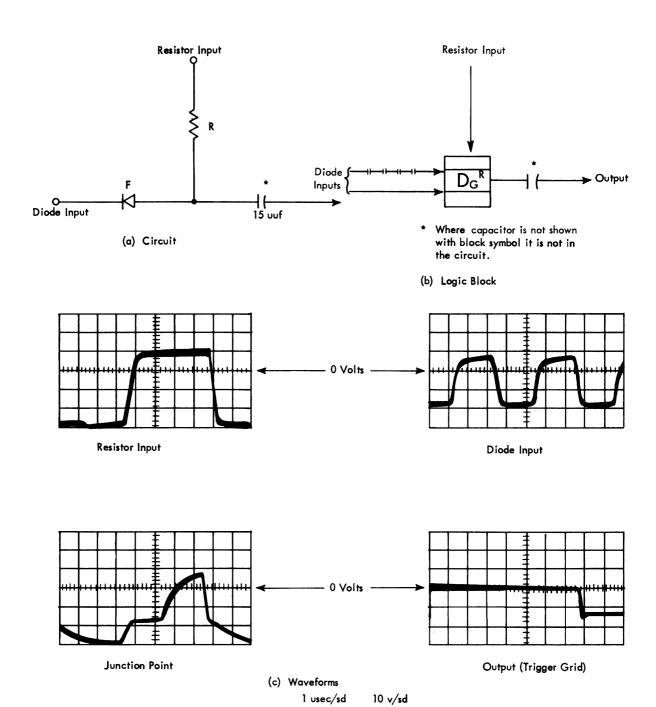

# 2.07.00 DIODE GATE (D<sub>G</sub>)

The diode gate acts somewhat in the same manner as an AND circuit and is used to flip a trigger. It is used where speed of operation is not essential.

### 2.07.01 Circuit Description

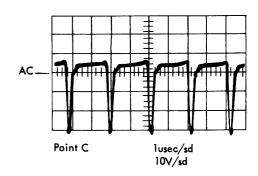

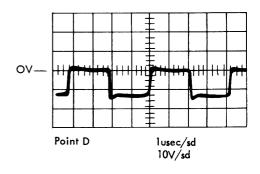

The upper end of the 39K resistor is connected to a circuit (such as a divider output of a trigger) that will supply a nominal +10v to -30v gate pulse. The diode input is the output of a special cathode follower that gives a +10v to -14v pulse. The prerequisite for proper operation is that the gate input overlap the diode input.

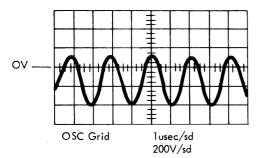

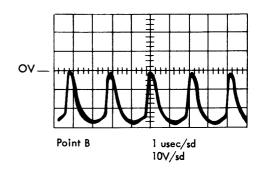

A typical operation is shown in Figure A18. All the pictures have the same time relationship. The diode input shows two +8v to -18v pulses (an example of normal circuit variations, hence the usage of "nominal"). The gate of +9 volts to -30 volts is going to select or "gate" one of the pulses at the diode input. The junction point is initially at about -30 volts and the diode is cut off. As the gate rises to +9 volts, the junction point rises exponentially to -18 volts and is held at that point by the diode's going into conduction. As the diode input rises to +8 volts, the diode again is cut off and the junction point rises exponentially toward +9 volts. The capacitor is now charged. When the diode input falls to -18 volts, the diode's conducting provides a discharge path for the capacitor and the junction point falls sharply to the diode input level of -18 volts. The diode maintains this voltage level until the gate falls. When the gate falls, the diode cuts off and the junction point falls exponentially to -30 volts. The sharp fall from +9 volts to -18 volts is coupled through the capacitor to the trigger grid. The negative shift forces the grid from 0 volts to -12 volts (held by -12v grid clamp) and causes the trigger to flip off. The trigger was turned on by a different circuit.

The above description has shown that coincidence of the gate and diode input is necessary for the diode gate to flip the trigger. The exponential rise and fall at the junction point do not affect the trigger.

#### 2.07.02 Variations

A second diode input may be added (broken line, Figure A18b) to the circuit. The  $\mathbf{D}_{\mathbf{G}}$  must then have coincidence of all inputs to operate; a negative shift into either diode input causes a negative shift output.

The resistor input can be fed from a trigger tap at plate level. The diode input must be fed from a special plate level cathode follower to give the same voltage relationship as previously described.

The capacitor is shown outside the diode gate block. When it is not shown outside the block, it is not in the circuit. There are special cases in the drum where the output of a diode gate is fed directly to the grid of a cathode follower. In this case, the circuit acts as an AND circuit. However, the capacitor can be placed in the output of the cathode follower for AC coupling purposes. In all diode gate blocks, the upper section contains the location of the junction point.

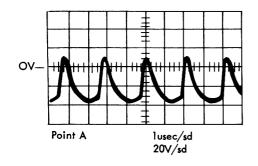

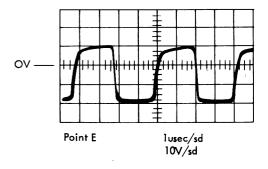

b. Capacitor Input 20V/sd 1 usec/sd

c. Point B 10V/sd 1 usec/sd

Center line = 0 volts

d. Point A 10V/sd 1 usec/sd

FIGURE A19. DIODE GATE - GJ

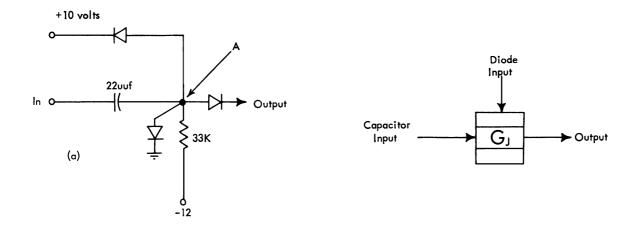

# 2.08.00 DIODE GATE (G<sub>J</sub>)

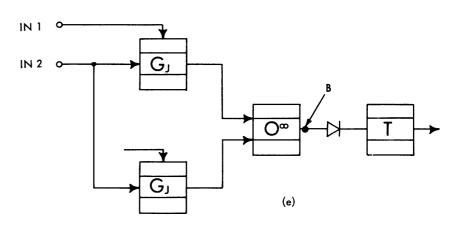

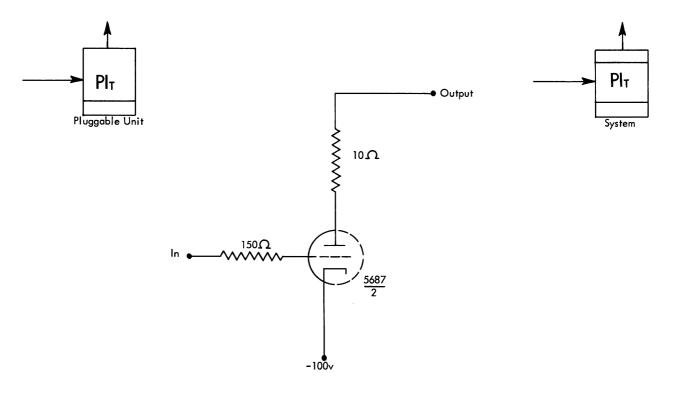

The diode gate  $G_J$  serves a purpose similar to that of the diode gate  $D_G$ . It is a gated input circuit and flips a trigger with a positive shift. The circuit appears in certain registers in CPU. The  $G_J$  operates faster than the  $D_G$ .

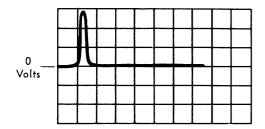

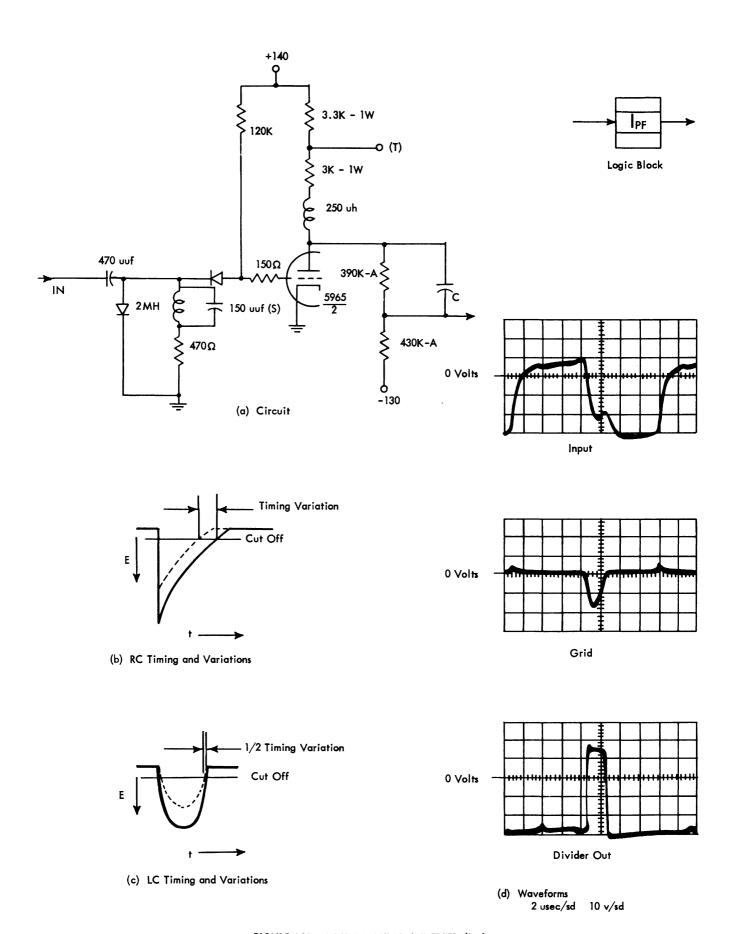

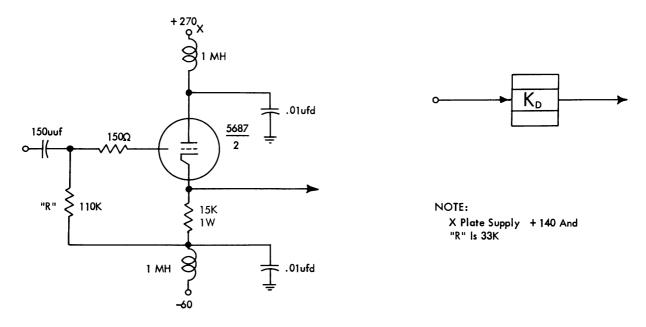

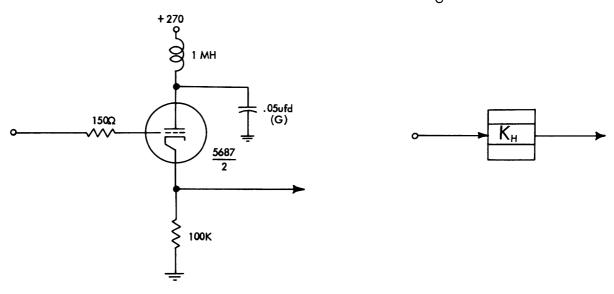

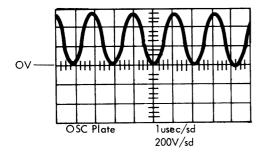

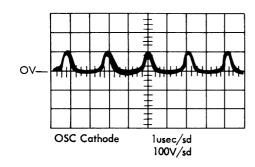

# 2.08.01 Circuit Description (Figure A19)

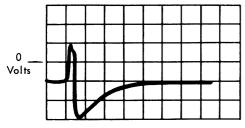

The diode input is a +10v to -30v gate from a cathode follower, while the input to the 22-uuf capacitor is a sharp 55v + pulse, originating in the wave-form generator peaker (PKR<sub>Z</sub>). This pulse is applied to a cathode follower that drives the capacitor input. When the input to the diode is -30 volts the output is approximately -30 volts, and the +55v pulse at the capacitor input is swamped out by the heavily conducting input diode. However, when the input to the diode is +10 volts, the diode is cut off because the plate is at about -12 volts. The 55v pulse now causes the output to swing from -12 volts up to ground.

Figures A19b, A19c and A19d show typical wave forms. A steady +10 volts is at the diode input. Figure A19e shows the points where the wave forms are located. Point A is the junction point of the diode gate (A19a).

The ground clamp tends to prevent overdriving the trigger grid positive. The input diode to the trigger block isolates the negative shift of the input pulse. The value of the return resistor is 33K and is not shown in the logic block. As in other diode circuits, the upper section of the block contains the location of the junction point.

FIGURE A20. STANDARD CATHODE FOLLOWER

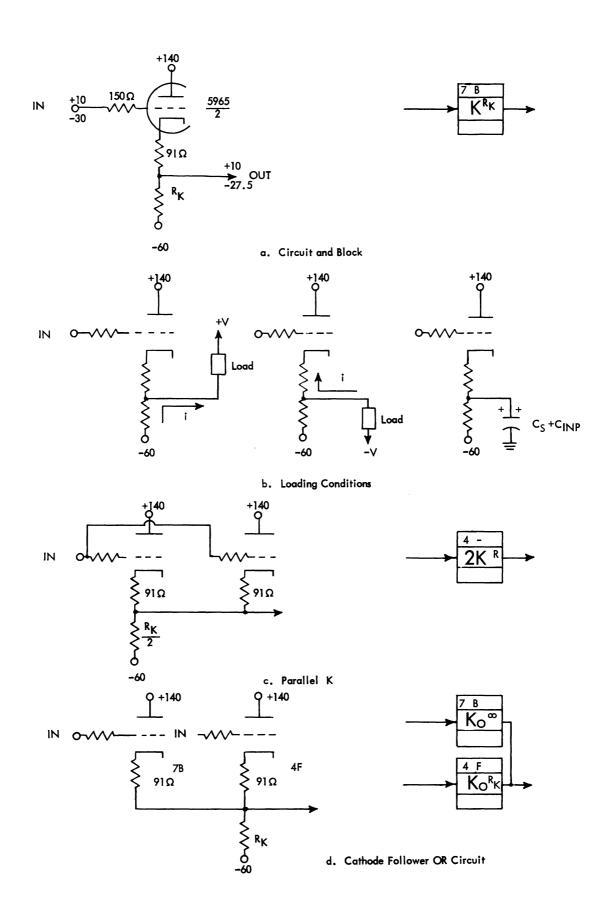

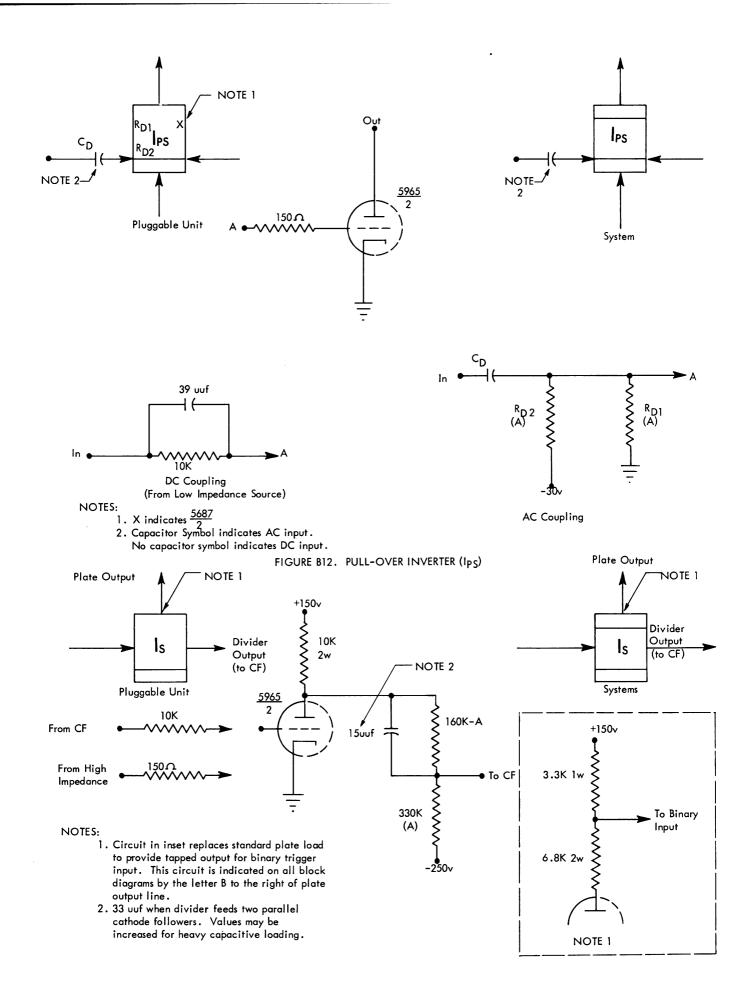

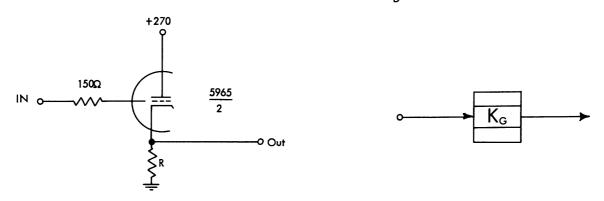

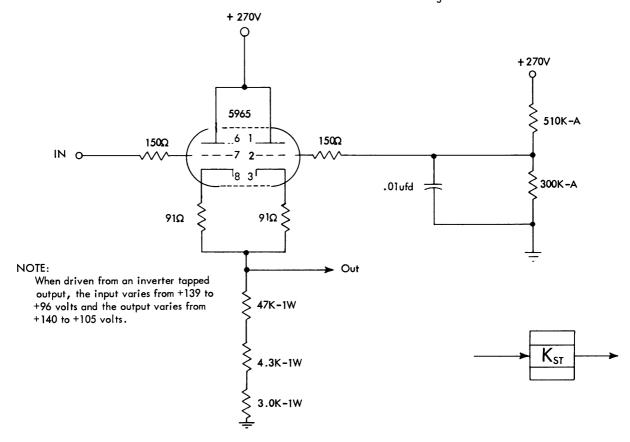

### 2.09.00 CATHODE FOLLOWER (K)

The basic powering circuit in the 700 series is the cathode follower K (Figure A20). Cathode followers have many characteristics that promote their wide use in calculators. They are primarily power amplifiers and, therefore, are used for supplying a stable voltage level for driving resistive loads such as diode AND-OR circuits or capacitive loads such as wiring capacitance. Their high input impedance and low output impedance make them useful for impedance matching and isolation. They do not invert a signal, but they do attenuate a signal.

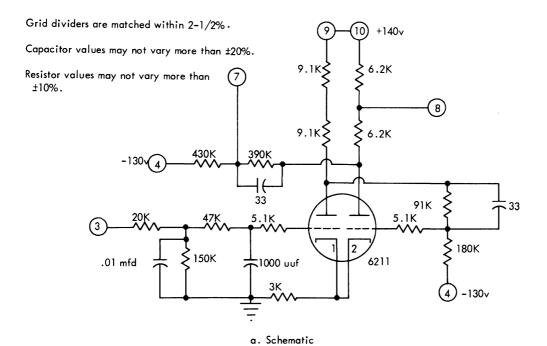

### 2.09.01 Circuit Description

To understand thoroughly the natural actions of a cathode follower, the self-biasing characteristics of the circuit should be understood. The plate, with +140 volts, is always calling for more current. The controlling grid is calling for more current as long as the effective bias is positive, is neutral when the bias is zero, and completely resists the plate command when the effective bias reaches -3 volts (-30 volts on the grid). The grid takes control at -1v bias, when the input is +10 volts. The reason for the different stable points of bias voltage at the two different input levels is readily understood by noting the effective plate voltage in both cases. Because the effective plate voltage is only 129 volts with +10 volts on the grid, only one volt bias is needed. With an effective plate voltage of 167 volts (-30 volts on the grid), more bias (-3 volts) is needed to overcome the effect of the plate.

The tube conducts in such a manner as to tend to regulate itself, that is, not to allow an appreciable voltage change from grid to cathode. If the tube current increases, the tube tends to cut itself off as the cathode tends to rise. This cut-off action tends to decrease the current. If, on the other hand, the current tends to decrease, the cathode potential tends to fall, thus increasing the current flow. This type of self-regulation is called inverse voltage feed-back.

Current through the tube causes a voltage drop across the 91-ohm dropping resistor. With the input at +10 volts, this drop should about equal the grid-to-cathode rise, so that the output voltage is also +10 volts. If the input signal should drop to -30 volts, then the output voltage would also drop. Note from the tube characteristics that a change in current through the tube, which accompanies the change in voltage across the load, increases the negative grid bias to about three volts. With this bias and this current, the drop across the 91-ohm bias resistor changes from the one volt to about one-half volt. This means that the drop across the dropping resistor can no longer compensate for the grid-to-cathode rise, and the output will now be more positive than the input. The voltage rise in a cathode follower is about one tenth of a volt per volt change in signal level with the minimum cathode load in the circuit. As the cathode resistor is increased, the value of the lower level can be expected to increase also (about one volt per 3K increase in cathode resistor). The gain of a cathode follower operating class A is about 0.9.

- \* R = 130K for +48V input R = 430K for +140V input

- \*\* 390K to give a -34V down level

‡ The 10K resistor may be removed when it is desired to pass more than 0.26ma through the contacts

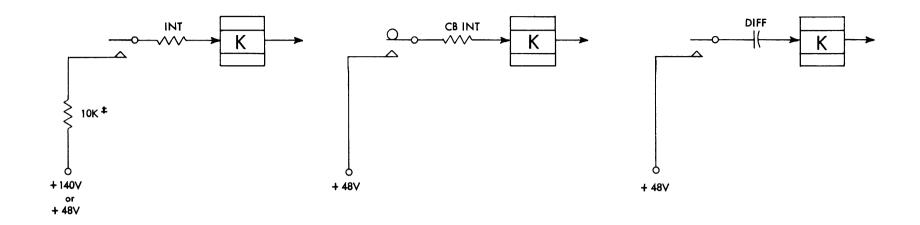

INT, C.B. INT, or DIFF. may be used with K,  $K_X$  or  $K_P$

#### 2.09.02 Positively Returned Resistive Load

If the cathode follower load is resistive and is returned to a positive voltage, the current for the load must be supplied from the -60v supply through the cathode resistor (Figure A20b). Because the tube regulates itself, this load current is taken away from the tube. As load current increases, tube current decreases. Design limits the minimum current through the tube to 1.5 ma. Therefore, a single cathode follower (5965 tube) can supply 10.5 ma without materially affecting voltage level (low impedance output).

### 2.09.03 Negatively Returned Resistive Load

A load that is returned to a minus supply voltage is effectively paralleled with  $R_K$  (Figure A20b). Therefore, any current demands of the load must be met by the tube. A value of  $R_K$  is chosen so that, in parallel with the load, the total impedance is such that both currents together will not exceed 12 ma.

### 2.09.04 Capacitive Load

Let the loading become capacitive and the situation changes somewhat (Figure A20b). Assume that a capacitance is connected from the output to ground. If the grid now shifts from +10 volts to -30 volts, what are the conditions? Because the voltage across the capacitance cannot change suddenly, the cathode is held at +10 volts while the grid shifts to -30 volts. The tube is cut off for a time. The output voltage drops at a rate determined by the RC path of the capacitance and the load resistor. After the voltage has dropped far enough, the tube starts to conduct again. When the input again shifts to +10 volts the capacitance is charged by the current through the tube. Usually the input capacitance from succeeding stages is such that the RC time constants encountered are comparable to rise and fall time of the input. Therefore, the extremes of cut-off and very heavy conduction to charge the capacitance are not encountered, and the output follows the input. If the RC time constant is such as to cause the above mentioned extremes, the output does not follow the input but depends on the RC time constant. This condition appears as output distortion.

### 2.09.05 Parallel Cathode Follower

The use of more than one cathode follower in parallel helps to minimize the voltage rise of the down level through the circuit with a given load. Paralleling the cathode followers also provides more current for the line charging purposes to speed output voltage shifts. In addition, the paralleling lowers the effective cathode resistance, allowing faster discharging of line capacitance. Each tube can use one  $\mathbf{R}_K$  or the value of  $\mathbf{R}_K$  can be divided by the number of tubes paralleled. When cathode followers are paralleled, the connections are made at the grid parasitics and the output (Figure A20c). The number of half tubes in parallel precedes the symbol K in the block diagram, thus a whole tube cathode follower is symbolized by 2K. Parallel cathode followers are more susceptible to parasitic oscillation than are most of the other circuits or unparalleled cathode followers.

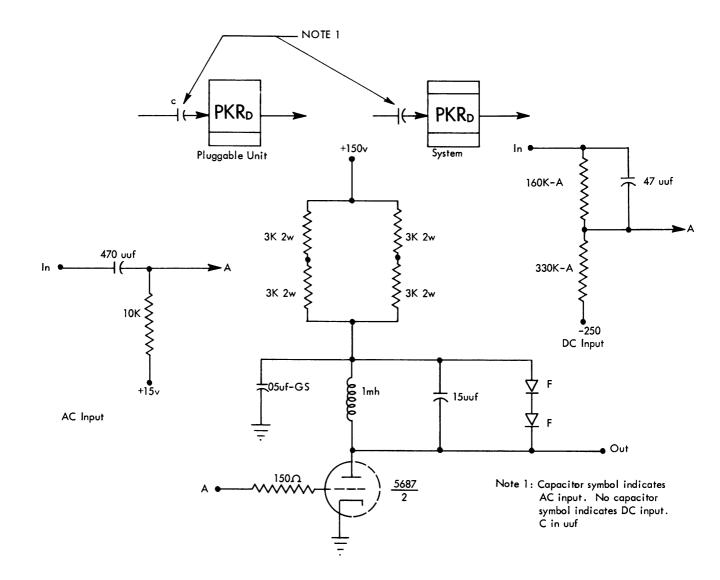

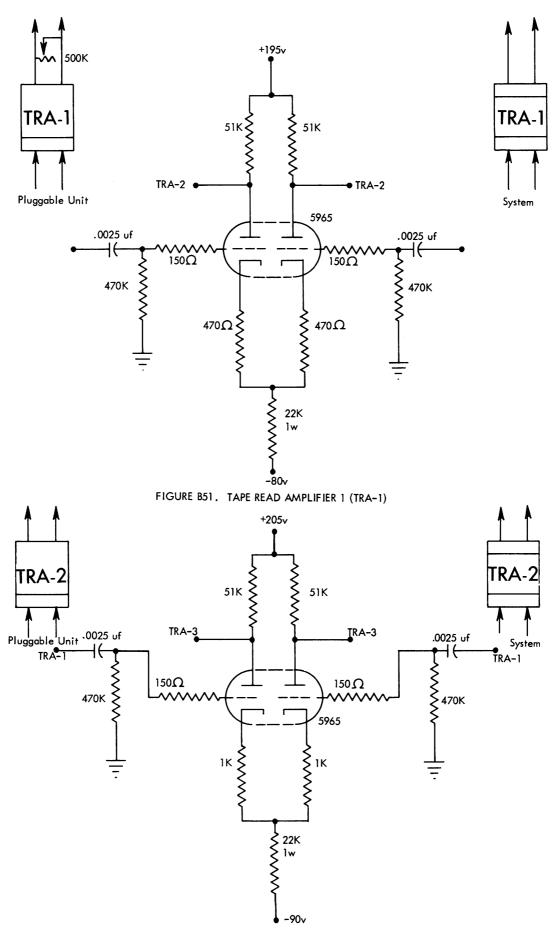

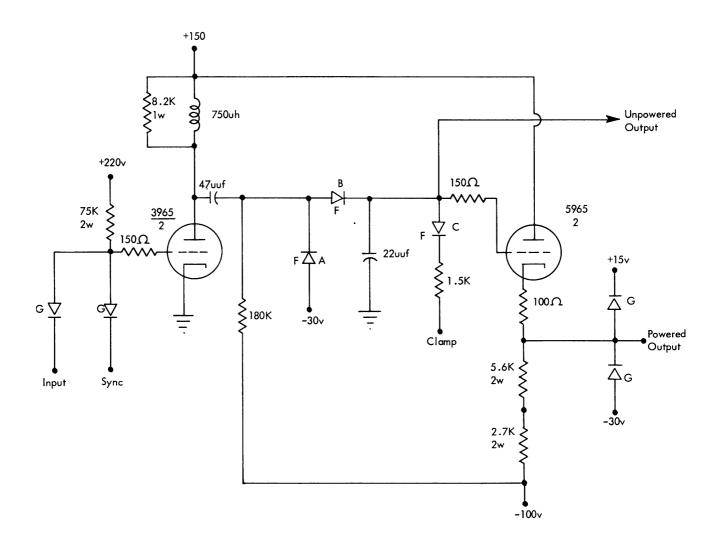

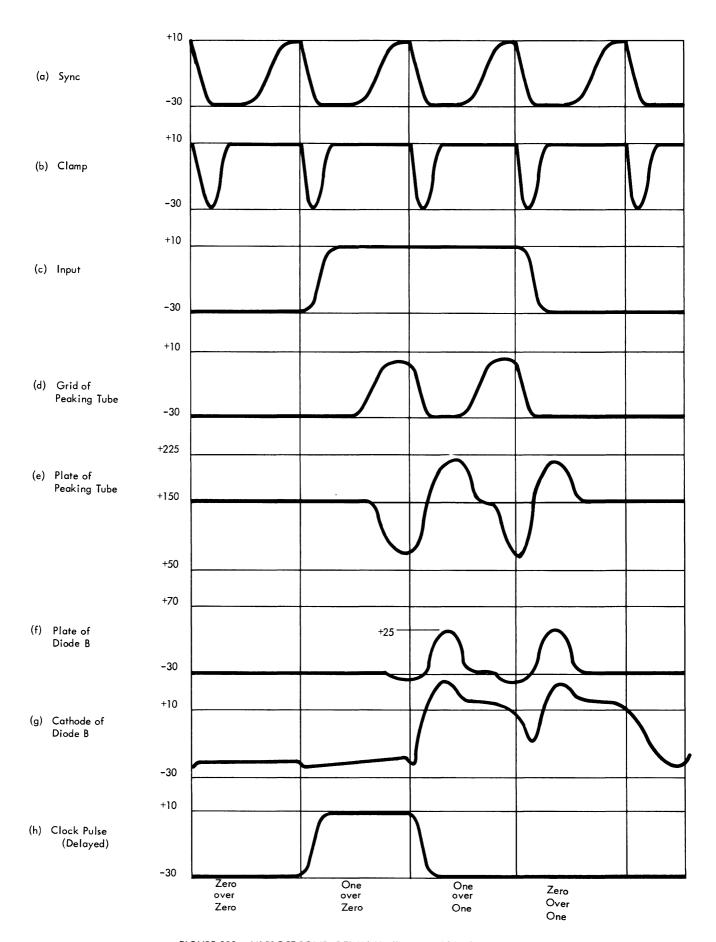

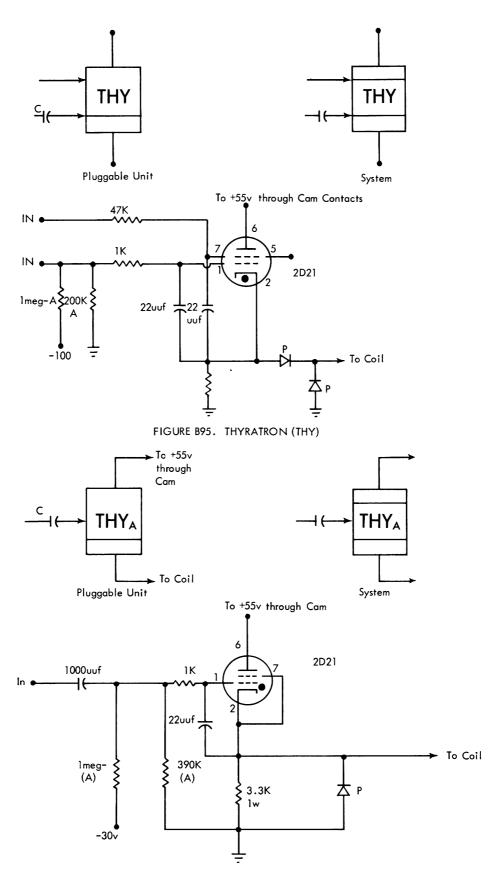

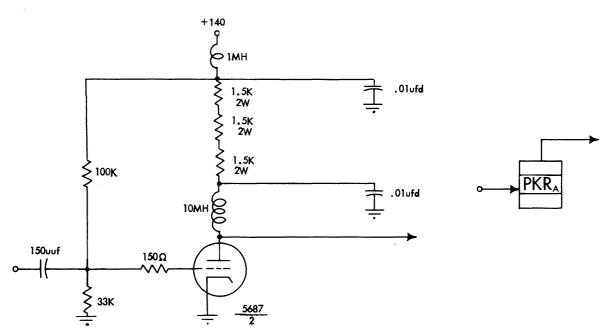

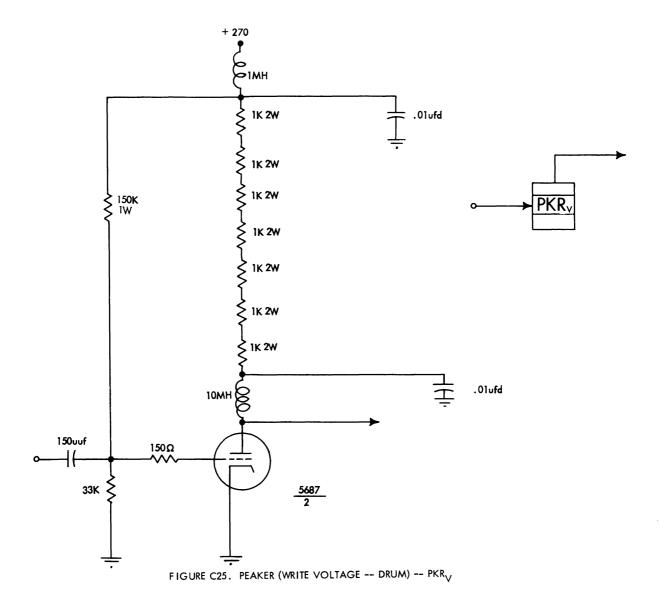

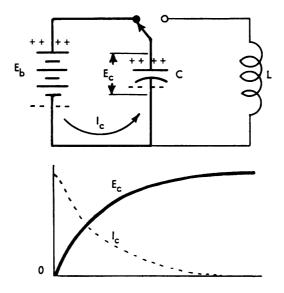

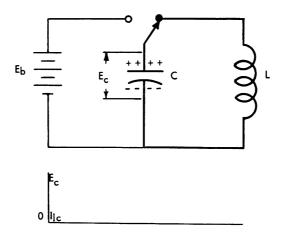

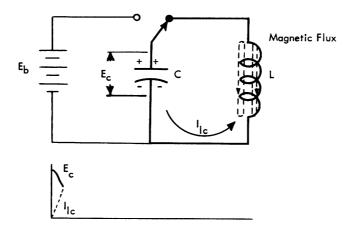

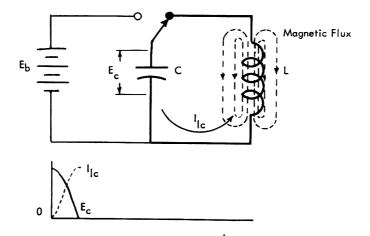

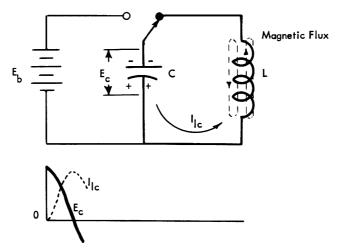

### 2.09.06 Cathode Follower OR Circuit