## **Errata**

In the paper "Silicon CMOS Devices Beyond Scaling" by W. Haensch et al. in the *IBM Journal of Research and Development*, Volume 50, No. 4/5, July/September 2006, the exponent 2 was omitted from the expression  $fCV^2$  in the body and caption of Figure 1. The corrected figure follows.

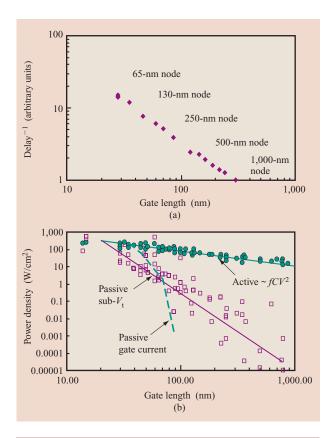

## Figure 1

(a) MOSFET performance vs. gate length; normalized MOSFET intrinsic device delay  $(CV/I_{\rm eff})$  vs. gate length. (b) Power density vs. gate length; data collected from literature for active power density and passive power density. Lines are intended to show trend.  $(fCV^2 = \text{frequency} \times \text{capacitance} \times \text{voltage}^2.)$

In the paper "Continuous MOSFET Performance Increase with Device Scaling: The Role of Strain and Channel Material Innovations" by D. A. Antoniadis et al. in the *IBM Journal of Research and Development*, Volume 50, No. 4/5, July/September 2006, the last term of Equation (5) should be multiplied by v. The corrected equation follows.

$$\begin{split} I_{\mathrm{eff}} &= [I_{\mathrm{D}}(V_{\mathrm{G}} = V_{\mathrm{dd}}/2, V_{\mathrm{D}} = V_{\mathrm{dd}}) \\ &+ I_{\mathrm{D}}(V_{\mathrm{G}} = V_{\mathrm{dd}}, V_{\mathrm{D}} = V_{\mathrm{dd}}/2)]/2 \\ &= [Q_{\mathrm{s}}'(V_{\mathrm{G}} = V_{\mathrm{dd}}/2, V_{\mathrm{D}} = V_{\mathrm{dd}}) \\ &+ Q_{\mathrm{s}}(V_{\mathrm{G}} = V_{\mathrm{dd}}, V_{\mathrm{D}} = V_{\mathrm{dd}}/2)]v/2 \\ &= C_{\mathrm{exiny}}'W[(3 - \delta)V_{\mathrm{dd}}/4 - V_{\mathrm{t}}]v. \end{split} \tag{5}$$