# Continuous MOSFET performance increase with device scaling: The role of strain and channel material innovations

D. A. Antoniadis I. Aberg C. Ní Chléirigh O. M. Nayfeh A. Khakifirooz J. L. Hoyt

A simple model that links MOSFET performance, in the form of intrinsic switch delay, to effective carrier velocity in the channel is developed and fitted to historical data. It is shown that nearly continuous carrier velocity increase, most recently via the introduction of process-induced strain, has been responsible for the device performance increase commensurately with dimensional scaling. The paper further examines channel material innovations that will be required in order to maintain continued commensurate scaling beyond what can be achieved with process-induced strain, and discusses some of the technological tradeoffs that will have to be faced for their introduction.

#### 1. Introduction

Conventional MOSFETs have proven to be remarkably scalable to gate lengths of about 60 nm, which are compatible with the 130-nm high-performance CMOS technology node. Intrinsic device performance up to this node has increased by about 17% per year, following an inverse gate-length  $(1/L_g)$  dependence commensurate with channel length decrease. This performance increase has relied in part on the steady increase of channel carrier velocity due to gate-length scaling combined with innovations, such as super-steep retrograde channel doping, and highly doped halos around very highly doped source and drain junctions. However, the intrinsic carrier transport properties in the channel material have remained constant, i.e. those of the relaxed silicon lattice; from the 90-nm node onward, additional innovations have been introduced to increase channel carrier mobilities, and hence allow continuation of velocity increase, by the imposition of process-induced strain in the silicon channel of otherwise conventional MOSFETs. The introduction of strain into the Si channel at the 90-nm node (see for example [1]) has been critical to increasing carrier mobility and velocity in the channel and maintaining historical CMOS performance trends. In Section 2 of this paper, a model is developed that quantitatively illustrates the relationship among carrier velocity, MOSFET drain current, and switching time.

Carrier velocity is extracted from published data, and its historical progression is plotted as a function of gate length. From the analysis, it is clear that additional improvements in channel velocity and therefore in mobility will be required in order for commensurate scaling (delay inversely proportional to gate length) to continue. Section 3 reviews the status of research efforts to improve electron and hole mobility using heterostructures of strained Si and strained SiGe, on both bulk and on-insulator substrates. Section 4 contains a discussion of some remaining challenges associated with these heterostructure MOSFETs, and the paper concludes in Section 5.

## 2. Impact of velocity on MOSFET switching time

The drain saturation current in a MOSFET normalized to the channel width,  $I_D/W$ , can be approximated as follows:

$$(I_{\rm D}/W) = Q'_{\rm s} v = C'_{\rm oxinv} (V_{\rm G} - V_{\rm t}) v,$$

(1)

where  $Q_s'$  is the channel charge areal density at the virtual source,  $C_{\text{oxinv}}'$  is the gate-to-channel capacitance per unit area at inversion, and v is the effective carrier velocity at the virtual source, which is thus defined as the point in the channel at which the charge density is given by  $C_{\text{oxinv}}'(V_G - V_1)$ .  $V_G$  is the applied gate-source

©Copyright 2006 by International Business Machines Corporation. Copying in printed form for private use is permitted without payment of royalty provided that (1) each reproduction is done without alteration and (2) the Journal reference and IBM copyright notice are included on the first page. The title and abstract, but no other portions, of this paper may be copied or distributed royalty free without further permission by computer-based and other information-service systems. Permission to republish any other portion of this paper must be obtained from the Editor.

0018-8646/06/\$5.00 © 2006 IBM

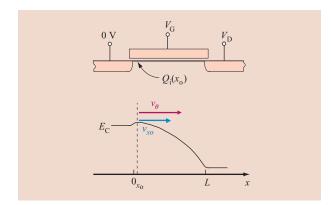

Illustration of the virtual source position  $x_0$  in the channel.

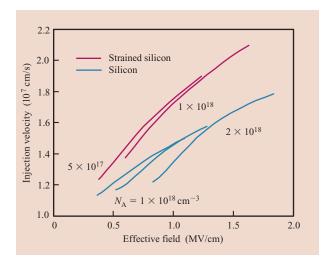

# Figure 2

Calculated injection velocity  $\nu_{\theta}$  vs. channel effective field for relaxed and ~1% biaxially strained bulk MOSFETs with different channel dopings. It was assumed that only the  $\Delta_2$  valleys are populated in simulating strained devices. The velocity would be even higher with uniaxial strain along the <110> direction because of the decrease in effective mass.

voltage, and  $V_{\rm t}$  is the effective threshold voltage in saturation, i.e., obtained from linear extrapolation of the  $I_{\rm D}$ - $V_{\rm G}$  curve to  $I_{\rm D}$  = 0;  $V_{\rm t}$  is given by

$$V_{\rm t} = V_{\rm t0} - \delta V_{\rm D}, \tag{2}$$

where  $V_{t0}$  is the effective threshold voltage at drain-to-source voltage  $V_{\rm D}$ , equal to zero, and  $\delta$  is the drain-induced barrier-lowering (DIBL) coefficient. On the other hand, the intrinsic MOSFET switching delay,  $\tau$ , is given by

$$\tau = \frac{\Delta Q_{\rm G}}{I_{\rm eff}} \,, \tag{3}$$

where  $\Delta Q_{\rm G}$  is the charge difference at the gate electrode between the two logic states, including both channel charge and intrinsic gate electrode fringing capacitance charge, and is given by

$$\Delta Q_{\rm G} = C'_{\rm oxinv} W(V_{\rm dd} - V_{\rm f}) + C_{\rm f}^* V_{\rm dd} \,, \tag{4}$$

and  $I_{\text{eff}}$  is the effective MOSFET switching current [2] given by

$$\begin{split} I_{\text{eff}} &= [I_{\text{D}}(V_{\text{G}} = V_{\text{dd}}/2, V_{\text{D}} = V_{\text{dd}}) \\ &+ I_{\text{D}}(V_{\text{G}} = V_{\text{dd}}, V_{\text{D}} = V_{\text{dd}}/2)]/2 \\ &= [Q_{\text{s}}'(V_{\text{G}} = V_{\text{dd}}/2, V_{\text{D}} = V_{\text{dd}}) \\ &+ Q_{\text{s}}(V_{\text{G}} = V_{\text{dd}}, V_{\text{D}} = V_{\text{dd}}/2)]v/2 \\ &= C_{\text{oxinv}}'W[(3 - \delta) V_{\text{dd}}/4 - V_{\text{I}}]. \end{split} \tag{5}$$

Using Equations (4) and (5) in (3) results in

$$\tau = \frac{V_{\rm dd} - V_{\rm t} + (C_{\rm f}^* V_{\rm dd} / C_{\rm oxinv}' L_{\rm g}) L_{\rm g}}{[(3 - \delta)/4] V_{\rm dd} - V_{\rm t}} L_{\rm g}},$$

(6)

where  $V_{\rm dd}$  is the supply voltage and  $C_{\rm f}^*$  is the total effective gate fringing capacitance, including all internal and external fringing capacitances, with the Miller effect on the drain side taken into account. It is interesting to note that  $C_{\rm f}^*$  is nearly independent of technology generation for properly scaled devices [3], with a value of about 0.5 fF/ $\mu$ m.

Because of the existence of finite resistance between the source contact (and the drain contact) and the channel,  $R_s$ , the actual carrier velocity at the virtual source,  $v_{xo}$ , can be approximated by

$$v_{\rm xo} = \frac{v}{[1 - C_{\rm oxinv}' R_{\rm s} W (1 + 2\delta) v]} \ . \tag{7}$$

The virtual source point is located near the top of the potential barrier between source and channel, and  $v_{xo}$  is related to the so-called source injection velocity,  $v_{\theta}$ , or ballistic-limit velocity, as discussed by Lundstrom [4]. Figure 1 illustrates these concepts. Exact evaluation of  $v_{xo}$  has been described in [5]. The ballistic velocity  $v_{\theta}$  for electrons vs. effective electric field in the channel is plotted in Figure 2, for both relaxed and strained Si using a self-consistent Schroedinger–Poisson solver, SCHRED [6]. For the strained Si it was assumed that only the  $\Delta_2$  valleys are populated, with no other changes relative to relaxed Si. The assumption that all electrons occupy the  $\Delta_2$  valleys corresponds roughly to an energy splitting between the  $\Delta_2$  and  $\Delta_4$  valleys greater than 140 meV, or a biaxial tensile strain level higher than approximately 1%.

While Equation (1) has been used primarily to model transistors in the ballistic limit, it actually fits state-of-the-

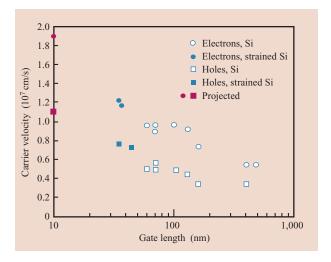

art transistor data over the period of the last two decades. Indeed, close examination of selected (bulk-Si) publications [7–15] allows  $v_{xo}$  for both electrons and holes to be tracked over the same period of time, for gate length  $L_{\alpha}$  ranging from 480 nm to 35 nm. In those selected publications,  $C_{\text{oxinv}}$  is given or can be estimated accurately,  $\delta$  can be extracted from the data, and  $R_s$  (or at least its upper bound) can be reasonably estimated from the output I-V characteristics near  $V_D = 0$ . In the data analyzed, values of the denominator in Equation (7) were typically higher than 0.80, indicating no more than  $\sim 20\%$ correction to the raw extracted velocity, v. The values of  $v_{xo}$  extracted from the literature data are shown in Figure 3, as well as the required electron and hole velocities at  $L_g = 10$  nm in order to continue the historical reduction of delay in direct proportion to  $L_{\rm g}$ , as discussed below. As can be seen for both electrons and holes, the carrier velocity  $v_{xo}$  has been steadily increasing with decreasing  $L_g$ . For all gate lengths down to 60 nm, the channel is unstrained (100) silicon, and therefore the carrier mobility vs. effective field relationship has been essentially unchanged. The main reason for the general trend of velocity increase with scaling can be understood from the scattering theory [4] as being due to reduction of the characteristic length of the potential barrier near the source, as  $L_g$  is scaled, and therefore reduction of backscattering. This reduction in the characteristic length of backscattering has been the result of proper scaling of the electrostatic design of MOSFETs, and has been achieved via innovations in source/drain and channel doping engineering. The key point here is that  $v_{xo}$  should increase (provided  $v_{xo}$  is smaller than  $v_{\theta}$ ) when there is a reduction in backscattering, either by reduction of the length over which backscattering can occur, which is the case here, or by reduction of the scattering rate. However, closer examination of the data shows that from  $L_{\rm g} \sim 130$  nm to 60 nm there has actually been a saturation of velocity increase that is most likely due to the increase of coulombic scattering near the source associated with increase in doping that counterbalances the decrease in the backscattering effective length.

Below 60 nm, the increase in velocity observed in Figure 3 is due to the introduction of well-known strain-induced mobility increases in the channel via innovative process steps [14, 15], which has brought about a decrease in the backscattering rate. With channel carrier mobility being a proxy for the inverse of the backscattering rate, it has been found experimentally via the application of strain that in short-channel devices there exists a  $\sim$ 0.5 ratio of proportionality between channel electron or hole velocity and mobility [1, 16]. An additional effect contributing to this proportionality ratio may also be the fact that the ballistic injection velocity increases because of the reduction in the carrier effective mass by applying

#### Figure 3

Calculated historical virtual source velocity  $v_{xo}$  of electrons and holes vs. gate length. Also shown are velocities at  $L_{\rm g}=10$  nm that are required to continue the historical relation of intrinsic FET switching delay time to gate length. See text discussion and Figure 4.

strain. At first sight, it would appear that both n- and p-MOSFETs are approaching the ballistic limit after these innovations, but as Figure 2 shows (for electrons), this is not necessarily the case, because the injection velocity is also increasing. The electron injection velocity would be even higher with uniaxial strain along the <110> channel direction as a result of decreased effective mass [17].

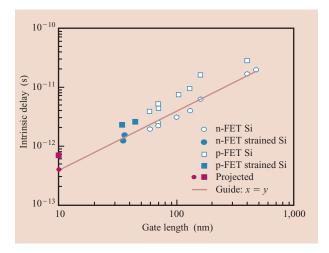

MOSFET intrinsic delay calculated from extracted historical device data and Equation (5) is shown in **Figure 4** for n- and p-MOSFETs. Also shown are the projected intrinsic delays at  $L_{\rm g}=10$  nm, using the corresponding extrapolated velocities of Figure 3 and making some more or less optimistically reasonable assumptions about device electrostatics (i.e.,  $\delta=0.1$  V/V, subthreshold swing about 90 mV/decade resulting in  $I_{\rm off}\sim300$  nA, at  $V_{\rm dd}=0.8$  V. The last two values are from the 2004 International Technology Roadmap for Semiconductors (ITRS '04) [18] for  $L_{\rm g}=10$ -nm devices (22-nm high-performance node).

It is notable that historically the increase in velocity and therefore the steeper-than- $L_{\rm g}$  decrease of the  $L_{\rm g}/v$  term has counterbalanced a parallel increase in the prefactor to that term in Equation (6), resulting in nearperfect proportionality between  $\tau$  and  $L_{\rm g}$ . Continuous improvement in intrinsic delay with scaling will require increasingly higher velocities, and at least for electrons in silicon, even with uniaxial strain, the velocity would have to approach the theoretical ballistic velocity as we approach 10-nm gate lengths. This would suggest that, at

Calculated historical intrinsic FET switching delay time and gate length.

# Figure 5

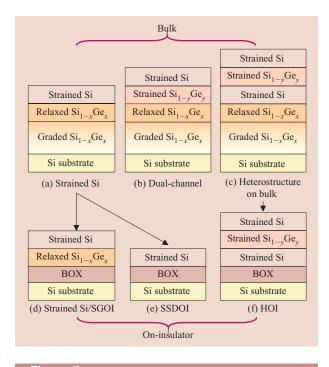

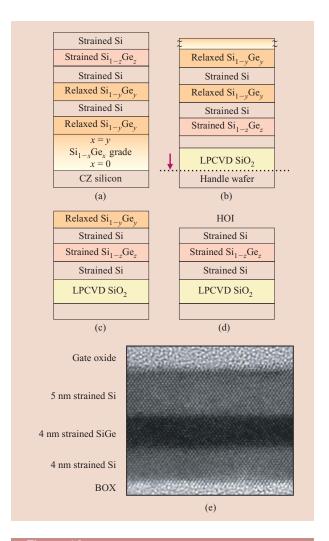

Schematic illustration of various heterostructure substrates used to investigate enhanced mobility, including bulk epitaxial technologies such as (a) biaxial strained Si on relaxed SiGe, (b) dual-channel structure (y > x), and (c) heterostructure on bulk; and on-insulator implementations on buried oxide (BOX) layers such as (d) strained Si/relaxed Si<sub>1-x</sub>Ge<sub>x</sub> on insulator (SGOI), (e) strained Si directly on insulator (SSDOI), and (f) heterostructure on insulator (HOI). Arrows indicate the relationship between on-insulator substrates and their bulk counterparts.

least for n-FETs, this is not likely to happen in silicon channels.

It is clear from this discussion that the increase in channel carrier velocity results from backscattering reduction, and while some of it may result from further scaling of the characteristic length for backscattering, the channel mobility increase is, from this point in time onward, the main lever for continuing the historical decrease of transistor delay  $\tau$  in proportion to  $L_{\rm g}$ . Prospects for continued channel mobility increase are discussed in the following sections.

#### 3. Strain and new channel materials

Although process-induced stress has been used to achieve significant mobility enhancements in short-channel devices (e.g., ~2x for holes in 65-nm technology [15]), the Si/SiGe materials system has the potential to achieve very large improvements in mobility (e.g., ~10x hole-mobility enhancements for strained Ge channels), as discussed below. The following two sections review the status of research on Si/SiGe heterostructure MOSFETs in bulk and on-insulator technologies.

#### Si/SiGe heterostructures on bulk

Figure 5 schematically illustrates various heterostructure substrates that have been used to investigate biaxial strain and high-mobility channel materials, including epitaxial structures on bulk substrates and on-insulator implementations. The on-insulator ("OI") substrates are generally derived from bulk structures by a combination of epitaxial growth, wafer bonding, and delamination or etch-back methods, which preserve the strain state of the layers. For example, strained silicon directly on insulator (SSDOI), illustrated in Figure 5(e), is derived from biaxial strained Si/relaxed  $Si_{1-x}Ge_x$  by transfer of the epitaxial layers and removal of the relaxed Si<sub>1-x</sub>Ge<sub>x</sub> virtual substrate, leaving a strained Si layer directly in contact with silicon dioxide [19–21]. The on-insulator technologies provide a pathway to implementing mobility enhancement in partially or fully depleted devices, in ultrathin-body MOSFETs, or nonplanar (e.g., doublegate) MOSFETs, and are discussed in the next subsection. This section focuses on the investigation of mobility in bulk MOSFETs.

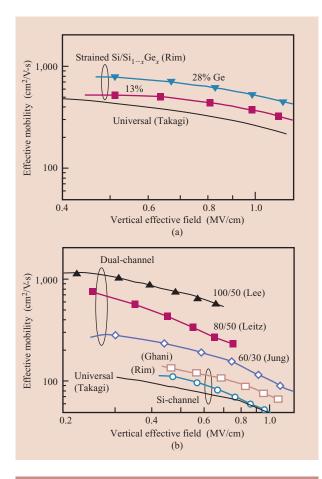

**Figure 6** compares effective mobility in bulk MOSFETs for (a) electrons in strained Si/relaxed SiGe and (b) holes in Si-channel and strained Si/Si<sub>1-y</sub>Ge<sub>y</sub> dual-channel heterostructures. Dual-channel heterostructures [Figure 5(b)] use a combination of strained Si and strained Si<sub>1-y</sub>Ge<sub>y</sub> to enable simultaneously high electron and hole mobilities [23–25]. In addition, because of the high Ge content and compressive strain, these structures offer significantly higher hole mobility than either biaxial-tensile strained Si [Figure 6(b),  $\circ$ ] or process-induced

strained Si [Figure 6(b),  $\Box$ ]. As illustrated in Figure 6(b), the hole mobility increases with increasing Ge fraction in the strained Si<sub>1-y</sub>Ge<sub>y</sub> channel. A hole-mobility enhancement factor of approximately 10x, relative to unstrained Si, is obtained for a p-MOSFET with a thin strained Si layer ( $\sim$ 5 nm) on top of a strained Ge channel ( $\sim$ 12 nm) on a relaxed Si<sub>0.5</sub>Ge<sub>0.5</sub> virtual substrate [25]. The electron mobility in the strained Si channel is

# Figure 6

Comparison of MOSFET effective mobility in bulk technologies for (a) electrons in strained Si/relaxed  $Si_{1-x}Ge_x$ , and (b) holes in various Si-channel and strained Si/strained SiGe dual-channel implementations. For the strained Si channel p-MOSFETs, the data from Rim et al. is for biaxial strained Si/relaxed  $Si_{1-x}Ge_x$  (28%) [22], and the data from Ghani et al. is for process-induced compressively strained Si implemented by the growth of SiGe in the source/drain regions [1]. For dual-channel structures, the notation y/x represents the Ge percentage in the strained  $Si_{1-y}Ge_y$  layer and in the relaxed  $Si_{1-x}Ge_x$  substrate, respectively. The highest hole mobility is obtained for a pure Ge channel strained in biaxial compression to a relaxed  $Si_{0.5}Ge_{0.5}$  substrate [25]. Other dual-channel data is from Leitz et al. [23] and Jung et al. [24]. The curves marked "Universal" are for unstrained Si, from Takagi et al. [26].

## Figure 7

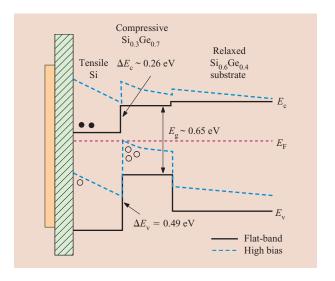

Energy band lineup for bulk p-MOSFETs fabricated in 70/40 dual-channel heterostructures, for bias conditions near flat-band (solid lines) and at high gate bias (dashed lines). Due to the band lineup, an electron inversion layer forms in the strained Si layer in the n-MOSFET, while hole inversion occurs first in the highmobility strained SiGe layer, and at higher gate bias in the strained Si cap layer. Band offset values derived from Ni Chleirigh et al. [31].

enhanced by approximately a factor of 2 for the same structure. The high hole mobility results from a combination of the small Ge in-plane hole effective mass, the biaxial-compression-induced strain splitting of the valence bands, and the use of a thin Si cap layer, which enables a low interface state density to be obtained at the semiconductor/insulator interface. In Ge surface-channel MOSFETs, where the gate dielectric is formed directly on Ge without an intermediate Si layer, reported hole-mobility enhancements are in the range of 1.4 to 2x [27–29], and n-MOSFET performance is disappointing [30]. The use of Si-compatible gate insulator technology makes the strained Si/strained Ge dual-channel heterostructure very attractive.

Detailed understanding of dual-channel MOSFET operation requires information on the energy bands for the heterostructure. The energy band lineup for bulk 70/40 dual-channel p-MOSFETs is illustrated schematically in **Figure 7** (the notation y/x represents the Ge percentages in the strained  $Si_{1-y}Ge_y$  layer and in the relaxed  $Si_{1-x}Ge_x$  substrate, respectively). The large valence band offset ( $\sim$ 0.5 eV) confines holes to the highmobility strained  $Si_{1-y}Ge_y$  channel. Due to the band lineup, an electron inversion layer forms in the strained Si layer in the n-MOSFET, while in the p-MOSFET, hole inversion occurs first in the high-mobility strained SiGe

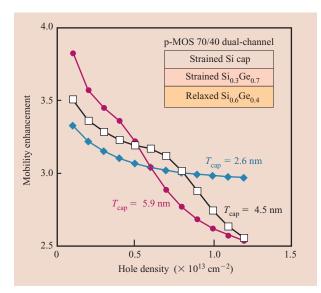

Measured effective hole-mobility enhancement factor relative to Si control devices for 70/40 dual-channel heterostructure p-MOSFETs with  $\mathrm{Si}_{0.3}\mathrm{Ge}_{0.7}$  layer thickness ~ 10 nm. The mobility enhancement at high inversion charge densities is largest for thin strained Si cap layer thicknesses,  $T_{\mathrm{cap}}$ , where the holes primarily populate the high-mobility strained  $\mathrm{Si}_{0.3}\mathrm{Ge}_{0.7}$  layer. The Si cap thickness was extracted on each device by fitting measured C-V characteristics, as discussed in the text. The 3-nm-thick gate oxide was grown at 600°C, and the source/drain anneal was 800°C for 10 s. The data is for ring-structure MOSFETs with  $W=1,000~\mu\mathrm{m}$  and  $L=50~\mu\mathrm{m}$ .

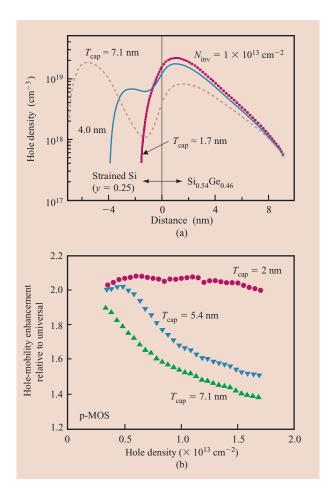

layer, and, at higher gate overdrive, in the strained Si cap layer, assuming a sufficiently thick Si cap layer. If the Si cap is thin ( $\sim$ 2 nm), holes can be forced into the Si<sub>1-y</sub>Ge<sub>y</sub>, resulting in high mobility even at high inversion charge densities. The impact of the Si cap thickness on mobility is illustrated in **Figure 8**, which shows the measured hole-mobility enhancement factor, relative to Si control devices, for 70/40 dual-channel p-MOSFETs [32]. For the thinnest Si cap, mobility enhancements of 3x are obtained at all inversion charge densities measured (up to  $1.3 \times 10^{13}$  cm<sup>-2</sup>). The Si cap thickness was extracted on each device by fitting simulations to measured capacitance voltage (C-V) characteristics, as discussed in the next subsection.

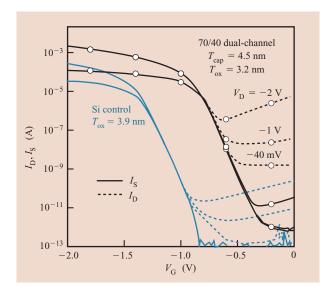

A challenge for these structures is illustrated in **Figure 9**. Measured off-state drain current is higher for dual-channel p-MOSFETs than for similarly processed Si control devices. The leakage occurs in the drain/gate overlap region, and the temperature dependence suggests a combination of band-to-band and trap-assisted tunneling [32]. The leakage increases with increasing Ge fraction, x in the substrate and y, in the  $Si_{1-y}Ge_y$  channel,

## Figure 9

Comparison of measured subthreshold characteristics for 70/40 dual-channel and Si control p-MOSFETs ( $W=1,000~\mu\mathrm{m}$ ,  $L=50~\mu\mathrm{m}$ , n<sup>+</sup> polysilicon gate). Subthreshold swing is 72 mV/decade for both devices. The threshold voltage is smaller for the dual-channel devices because of the narrower bandgap of the heterostructure. Off-state leakage is higher in dual-channel MOSFETs compared with control devices. From [32], reproduced with permission; ©2005 IEEE.

consistent with a reduction in the bandgaps of the strained Si and SiGe channel layers [32]. Drain leakage has also been observed in narrow-bandgap pseudomorphic Si/Ge/Si p-MOSFETs grown on unstrained Si [33]. These authors report reduced leakage for ultrathin Ge channels (~3 nm), though this also reduces the mobility enhancement. Detailed understanding requires further investigation, especially of the material quality in the ion-implanted gate/drain overlap region, which is subject to damage-enhanced interdiffusion of the Si and SiGe [34]. Optimization of the process should reduce trap densities in this region and the off-state leakage. Although the narrow bandgap of high-Ge-content SiGe may be associated with increased leakage, the reduction in the "effective bandgap" of the heterostructure (the energy difference between  $E_c$  in strained Si and  $E_v$  in strained SiGe, illustrated in Figure 7), relative to unstrained Si, has a positive implication: A single metal gate material, with a workfunction near the "mid-gap" of the heterostructure, may be utilized for both n- and p-MOSFETs, yielding appropriate threshold voltages [35, 36].

A remaining challenge of these structures is the fact that the p-MOSFET, even with a 1-nm-thick Si cap layer, is not strictly a surface-channel device, and thus the electrostatics are somewhat compromised. For heavily doped substrates and thin gate oxides, this results in a larger subthreshold swing than observed for Si control devices [37]. The ideal subthreshold swing is recovered when the heterostructures are fabricated into fully depleted on-insulator MOSFETs, as discussed below. Simulations of the scalability of these structures are discussed in the following subsection.

#### Strained heterostructures on insulator

Strained Si/strained SiGe heterostructure on insulator (HOI) combines the transport benefits of the dualchannel structure with the electrostatics of fully depleted SOI (FD-SOI), and the potential to scale the body thickness into the ultrathin regime. To fabricate HOI, strained Si/strained SiGe/strained Si is grown on relaxed  $Si_{1-x}Ge_x$ , and the top three layers are transferred to the insulator, with the original strain state preserved in the transfer process, as illustrated in Figure 10 [38]. A similar process may be used to fabricate strained Si directly on the insulator, with "x% SSDOI" referring to the Ge fraction of the relaxed  $Si_{1-x}Ge_x$  in the donor substrate. In HOI, the strained Si on either side of the SiGe layer reduces the interface state density at the semiconductor/ dielectric interface, compared with devices in which the SiGe is in direct contact with the oxide (see for example [39] for a discussion of SiGe/oxide interface quality). In HOI, the lower strained Si layer also has the potential to serve as a second (bottom) channel for electrons, in double-gate structures. The top strained Si layer serves as the electron channel in the n-MOSFET, and it can be selectively thinned to a thickness of 1 to 2 nm on the p-MOSFET to enable near-surface-channel operation with Si-compatible gate dielectric technology.

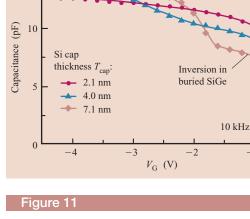

HOI has been fabricated with up to 55% Ge in the Si<sub>1-v</sub>Ge<sub>v</sub> channel, and donor-wafer relaxed SiGe layers with Ge content of 25% ("55/25 HOI") [40]. A reduced thermal budget process is used for both substrate fabrication (maximum bond anneal 600°C, 2.5 hr) and MOSFET processing (600°C, 5-hr gate oxidation, and 800°C 10-s source/drain activation) [40]. As in dualchannel MOSFETs, control of the strained Si cap thickness is critical to the operation of HOI MOSFETs. The Si cap thickness on the p-MOSFET can be extracted from a combination of C-V measurements and simulations, as illustrated in Figure 11. Calculations using the Dessis simulator [42] are employed, and quantum effects are taken into account using the density gradient correction model, with density of state values modified for strained Si and models verified on bulk dual-channel devices [31]. Figure 12(a) shows simulated hole-density distributions as a function of distance from the strained Si/SiGe interface, in 46/25 HOI. As illustrated in the figure, thin Si cap layers (~2 nm) result in a hole

# Figure 10

Fabrication process for HOI, illustrating the layer structure (a) as grown; (b) after deposition of low-temperature oxide, planarization, bonding, grind-back and TMAH etch (the arrow marks the location of the bond interface); (c) after selective etch, stopping on the Si layer, and removal of the Si etch stop; (d) after SC-1 removal of the Si $_{1-y}$ Ge $_y$  etch-stop layer, resulting in the HOI structure (from [38], reproduced with permission; ©2004 IEEE); SSDOI is fabricated by a similar process, without growth of the strained Si $_{1-z}$ Ge $_z$ layer. (e) Cross-section transmission electron micrograph (XTEM) of a 55/25 HOI structure after MOSFET fabrication.

distribution that is primarily in the high-mobility, compressively strained SiGe, even at high inversion charge densities of 10<sup>13</sup> cm<sup>-2</sup>. Such thin-cap HOI devices enable constant hole-mobility enhancement as a function of inversion charge density, illustrated in **Figure 12(b)**.

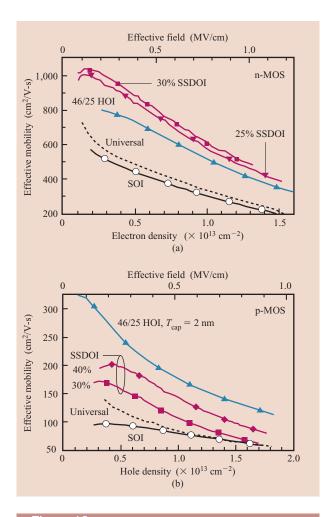

**Figure 13** compares electron and hole mobilities in SSDOI and HOI [40]. Mobility in co-fabricated SOI control devices is close to the published universal mobility curves (dashed lines) [26]. For electrons [Figure 13(a)],

Inversion in Si cap

15

Measured (symbols) and simulated (curves) gate-to-channel inversion capacitance for 46/25 HOI p-MOSFETs ( $T_{\rm ox}=3.5$  nm, n<sup>+</sup> polysilicon gates). Simulations are from [42] using the density gradient quantum correction model with default parameters. As is consistent with the band lineups illustrated in Figure 7, for the thicker-cap devices, the inversion layer forms in the buried SiGe at low gate overdrives and in the strained Si cap layer at higher overdrives. For the 2.1-nm-thick cap device, the Si cap is too thin to accommodate the holes, and inversion occurs primarily in the SiGe layer, resulting in a slight decrease in the maximum capacitance or an increase in the effective insulator thickness. From [41], reproduced with permission; ©2004 IEEE.

mobilities in HOI and in corresponding SSDOI are similar, though slightly degraded in HOI, perhaps associated with the finite Si cap thickness (5 nm) and the impact of Ge from the underlying SiGe layer, which is absent in SSDOI. For holes [Figure 13(b)], very high strain levels (e.g., 40% SSDOI) are required to achieve hole-mobility enhancement in tensile-strained Si at high inversion charge densities,  $N_{\rm inv}$ . This can be explained by quantization effects that reduce the strain-induced splitting of the valence bands in strong inversion, for the case of biaxial tensile strain in Si [44, 45]. In compressively strained Si (biaxial or uniaxial), quantization effects are not expected to counteract the strain-induced valence band splitting; thus, hole-mobility enhancement should be relatively constant with increasing inversion charge density (as observed in p-MOSFETs with Si channels under compressive stress [46]). When compressive stress is applied to SiGe, constant hole-mobility enhancement may also be expected with inversion charge density, because of the similarity of the Si and SiGe valence band structure. Indeed, as illustrated in Figure 13(b), the hole-mobility enhancement in compressively strained 46/25 HOI is

maintained at large inversion charge density, and is significantly larger than that observed in 40% SSDOI.

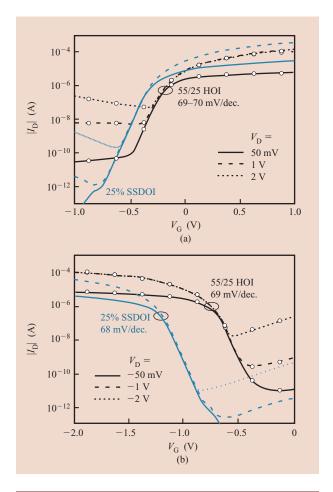

Figure 14 compares long-channel subthreshold characteristics for 25% SSDOI and 55/25 HOI n- and p-MOSFETs. Low subthreshold swing is achieved in fully depleted HOI MOSFETs in spite of the buried SiGe channel, an advantage compared with bulk dual-channel heterostructure devices [37]. The issue of elevated off-state leakage relative to SSDOI or SOI control devices, discussed above for bulk heterostructures, remains in

Figure 12

In 46/25 HOI, (a) simulated hole density as a function of distance from the strained Si/SiGe interface, for three Si cap-layer thicknesses; (b) measured hole-mobility enhancement factors. In (a) the total integrated inversion charge density,  $N_{\rm inv}$ , is fixed at  $10^{13}$  cm $^{-2}$ . The thicker cap devices show separate inversion-layer formation in the SiGe and Si layers. For the 1.7-nm-thick cap device, hole inversion occurs primarily in the SiGe even at high inversion charge density. This is evident in the higher mobility at high inversion charge densities for the devices with thin strained Si caps shown in (b), where enhancement factors are taken relative to the universal curve derived from Takagi [26]. From [41], reproduced with permission; ©2004 IEEE.

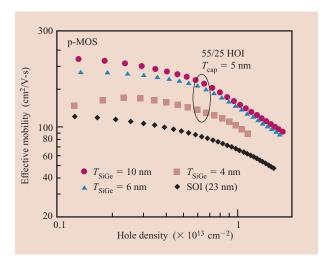

HOI. Thinning the SiGe layer from 10 nm to 4 nm reduces the off-state leakage by roughly a factor of 3, but the mobility is also reduced, as illustrated in **Figure 15** [40]. Further study of the leakage mechanisms is required in order to understand the tradeoffs between enhanced mobility and drain leakage.

The behavior of these new heterostructure materials in short-channel devices requires investigation. The electrostatics for the p-MOSFET have been simulated to evaluate the impact of the heterostructure on scalability.

# Figure 13

Comparison of measured effective mobility in SSDOI (10- to 20-nm body thickness), SOI, and HOI for (a) electrons, (b) holes. Mobility in lightly doped SOI control devices is close to the published universal mobility from [26]. Due to the simplicity of the contact and source/drain processes, a Kelvin mobility-extraction MOSFET [43] with  $L=100~\mu\mathrm{m}$  was used to enable accurate mobility extraction even with the high parasitic resistance of thin-body devices. From [40], reproduced with permission; ©2006 IEEE.

# Figure 14

Measured subthreshold characteristics for (a) n-MOSFETs and (b) p-MOSFETs ( $W=50~\mu\mathrm{m}, L=50~\mu\mathrm{m}, T_\mathrm{ox}=4~\mathrm{nm}, \mathrm{n^+}$  polysilicon gates) fabricated in SSDOI and 55/25 HOI. The body thickness for both the SSDOI and HOI MOSFETs is ~20 nm. For HOI, the body thickness includes the 10-nm-thick SiGe layer and the surrounding strained Si layers. The strained Si cap thickness (3–5 nm) and band structure differences between strained Si and SiGe result in threshold voltage shifts between the SSDOI and HOI MOSFETs. Differences in parasitic resistance make direct comparison of the on-state currents difficult. As for bulk heterostructures, off-state leakage is higher in HOI than in SSDOI or SOI control devices (not shown). From [40], reproduced with permission; ©2006 IEEE.

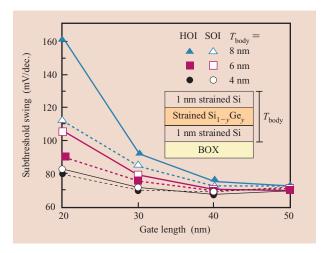

**Figure 16** compares simulated subthreshold swing (SS) for 46/25 HOI and SOI p-MOSFETs of equal body thickness, assuming 1-nm-thick Si cladding layers on either side of the SiGe layer (i.e.,  $T_{\rm body} = 1$  nm Si +  $T_{\rm SiGe}$  + 1 nm Si). The physical device parameters were taken from the International Roadmap for Semiconductors (ITRS) [18], assuming a fixed equivalent oxide thickness of 1 nm. For gate lengths down to 20 nm, subthreshold swing in

Measured hole mobility in 55/25 HOI with ultrathin strained SiGe channels, compared with SOI control devices. In the HOI, the top and bottom strained Si layers are 4 to 5 nm thick, as illustrated by the XTEM in Figure 10. When the thickness of the buried SiGe layer is reduced, the hole mobility decreases, particularly for the devices with a 4-nm-thick SiGe layer. From [40], reproduced with permission; ©2006 IEEE.

# Figure 16

Simulated subthreshold swing (SS) for 46/25 HOI and SOI p-MOSFETs for body thicknesses  $T_{\rm body}$  of 8, 6, and 4 nm, assuming 1-nm-thick Si cladding layers on either side of the SiGe layer (i.e.,  $T_{\rm body}=1~{\rm nm~Si}+T_{\rm SiGe}+1~{\rm nm~Si}$ ). The doping in the semiconductor was fixed at  $10^{17}~{\rm cm^{-3}}$  and the device physical parameters were taken from the ITRS [18], assuming an equivalent oxide thickness of 1 nm. The source/drain doping profile gradient was taken to be 2 nm/dec., and the gate length  $L_{\rm eff}$  is defined by the points where the source/drain doping reaches  $2\times10^{19}~{\rm cm^{-3}}$ . The density gradient model was used in [42], with parameters calibrated from Schrödinger solutions.

HOI is only slightly increased ( $\sim$ 15%), compared with that for SOI, for total film thicknesses  $T_{\rm body}$  less than or equal to 6 nm. This SS increase originates from the decreased semiconductor capacitance associated with the displacement of the hole charge centroid from the oxide/semiconductor interface. When the body thickness is comparable to the inversion layer thickness (e.g., 4 nm), the subthreshold swing of the HOI device approaches that of the SOI device. At this thickness, however, the hole-mobility enhancement is expected to decrease as the SiGe channel layer is thinned. Investigation of transport in short-channel devices incorporating these new materials is a topic for future research.

# 4. Discussion and future opportunities

Although the mobilities achieved in long-channel strained Si/strained SiGe heterostructures on bulk and insulator are promising, there are significant practical challenges associated with implementing these materials in a manufacturable CMOS technology, including material quality of the as-grown epitaxial layers, process integration issues such as interdiffusion between thin Si and SiGe layers, and the potential for formation of defects in strained layers during processing. Progress in these challenging areas has been achieved. Significant improvements have been demonstrated in reducing the defect densities in relaxed SiGe layers on Si substrates [47]. Interdiffusion at Si/SiGe interfaces is being studied and limits the thermal budget as the Ge content is increased because of the strong dependence of the interdiffusivity on Ge fraction and strain [48]. Laser annealing may be a solution to this issue. Enhanced diffusion of dopants along misfit dislocations at the strained Si/SiGe interface has been associated with increased off-state leakage in short-channel MOSFETs, and the strained Si thickness and Ge fraction in the SiGe layer must be limited, for a given thermal budget, to prevent this phenomenon [49, 50]. It should be noted that many of these challenges are associated with the presence of SiGe during CMOS processing, and that SSDOI thus has the potential for simpler process integration than HOI structures (but with less mobility leverage for p-MOSFETs).

Additional research on gate dielectric materials to be used with these structures is required. High-*k* dielectrics have been employed on strained Si surface-channel n-MOSFETs, and can be used to recover the mobility loss associated with high-*k* insulators such as HfO<sub>2</sub> on Si [22, 51]. A potential benefit of devices incorporating strained Si on SiGe is the possibility of reduced gate leakage currents, associated with the increased barrier height at the semiconductor/gate dielectric interface due to the strain-induced lowering of the conduction-band

energy [52]. An additional challenge for Ge-containing devices is the need for a high-quality high-k gate dielectric that can be formed directly on SiGe or Ge. High-k gate dielectrics (e.g., TiN gate electrode with HfO<sub>2</sub> dielectric) have been demonstrated directly on Si<sub>0.7</sub>Ge<sub>0.3</sub>, with 1.5x hole-mobility enhancement, but gate leakage currents were larger than for Si control devices [53]. Until a highquality gate insulator for SiGe or Ge is developed, a thin (~1-nm) Si cap layer, which enables the use of Sicompatible gate technology, is a reasonable compromise for the p-MOSFET. High-k gate stacks with metal gate electrodes (TiN/HFO<sub>2</sub>) have been demonstrated on strained SiGe channels, with thin sacrificial Si layers  $(\sim 1 \text{ nm})$  used to improve the interface quality [36], and on MOSFETs incorporating strained Si (2.5 nm thick)/strained Ge (7 nm thick) on relaxed SiGe (50% Ge) with 9x hole-mobility improvement over Si control devices [54]. Thus, the use of high-k gate stacks with strained Si/strained Ge is expected to enjoy the same large mobility enhancements demonstrated in earlier work using SiO<sub>2</sub> gate dielectrics [25].

An area of interest for future work is the combined use of global and local stress techniques, for example by the application of process-induced stress (Si<sub>3</sub>N<sub>4</sub> etch-stop liners over the gate) to devices containing initially biaxially strained Si or Ge channels. Such methods may offer larger enhancements than can be obtained from either process-induced or global stress techniques alone. This concept is illustrated in [55], where the impact of mechanical stress on SOI and SSDOI devices is studied. In that work, biaxial tensile strain in the Si is used to split the conduction-band degeneracy and repopulate all electrons into the  $\Delta_2$  conduction band. Superimposed on this stress is a uniaxial component along the [110] direction, induced by mechanical bending, which deforms the  $\Delta_2$  band, i.e., induces a change in the effective mass. Such effective mass changes are important in shortchannel devices because of the impact of effective mass on the Coulomb-scattering-limited channel mobility.

The application of these enhanced-mobility materials to nonplanar devices, such as FinFETs or tri-gate structures, requires investigation. Patterning-induced changes in strain and mobility also require study. Patterning of initially biaxially strained SiGe films on insulator has been used to produce uniaxially strained SiGe p-MOSFETs with improved short-channel mobilities [56]. The passivation of SiGe heterostructures will remain an issue, since nonplanar devices inherently have a large surface-to-volume ratio. Finally, since InGaAs and related compounds have very high electron mobilities (of the order of 10,000 cm²/V-s), these materials are attractive for investigation as high-performance n-FETs on Si substrates. When coupled with the high hole mobility in strained Ge, a III–V/Ge channel

pair may be of interest for future n- and p-FET logic devices.

### 5. Summary and conclusions

A simple model that links MOSFET performance to effective carrier velocity in the channel has been developed and used to extract electron and hole velocities in Si MOSFETs from published electrical data. The impact of improved mobility associated with processinduced strain is evident from the extracted carrier velocities. From the analysis of carrier velocity and its effect on intrinsic device switching delay, it is clear that additional improvements in velocity (and hence channel mobility) beyond those that have been achieved with process-induced stress will be required in order for commensurate scaling (delay inversely proportional to channel length) to continue. Research on long-channel MOSFETs has demonstrated that significant mobility enhancements (e.g., 2x for electrons and 10x for holes) relative to Si MOSFETs can be achieved in the strained Si/strained SiGe materials system. On-insulator analogs of these bulk heterostructure devices (e.g., SSDOI and HOI) have been demonstrated, with encouraging mobility and subthreshold characteristics. Associated with these heterostructures are several fundamental tradeoffs, such as the mobility enhancement and the leakage current, both of which increase with Ge content. The heterostructure must be optimized with such tradeoffs in mind. There are also enormous practical challenges in implementing these heterostructures in a manufacturing technology. The higher mobility offered by SiGe, Ge, and III–V semiconductors on silicon, and the improvements in lattice-mismatched epitaxial growth, continue to make these heterostructures a promising and active area of device research.

#### **Acknowledgments**

This work was supported by research contracts from the Microelectronics Advanced Research Corporation (MARCO) and the Semiconductor Research Corporation (SRC).

# References

- T. Ghani, M. Armstrong, C. Auth, M. Bost, P. Charvat, G. Glass, T. Hoffmann, K. Johnson, C. Kenyon, J. Klaus, B. McIntyre, K. Mistry, A. Murthy, J. Sandford, M. Silberstein, S. Sivakumar, P. Smith, K. Zawadzki, S. Thompson, and M. Bohr, "A 90 nm High Volume Manufacturing Logic Technology Featuring Novel 45 nm Gate Length Strained Silicon CMOS Transistors," *IEDM Tech. Digest*, pp. 978–980 (2003).

- M. H. Na, E. J. Nowak, W. Haensch, and J. Cai, "The Effective Drive Current in CMOS Inverters," *IEDM Tech. Digest*, pp. 121–124 (2002).

- Y. Taur and T. H. Ning, Fundamentals of Modern VLSI Devices, Cambridge University Press, 1998, pp. 246–247.

- M. Lundstrom, "Elementary Scattering Theory of the Si MOSFET," IEEE Electron Device Lett. 18, 361–363 (1997).

- A. Lochtefeld and D. A. Antoniadis, "On Experimental Determination of Carrier Velocity in Deeply Scaled NMOS: How Close to the Thermal Limit?", *IEEE Electron Device* Lett. 22, 95–97 (2001).

- SCHRED 2.0 User's Manual (online); see http:// www.nanohub.org/.

- R. A. Chapman, C. C. Wei, D. A. Bell, S. Aur, G. A. Brown, and R. A. Haken, "0.5 Micron CMOS for High Performance at 3.3 V," *IEDM Tech. Digest*, pp. 52–55 (1988).

- 8. R. A. Chapman, J. W. Kuehne, P. S.-H. Ying, W. F. Richardson, A. R. Paterson, A. P. Lane, I.-C. Chen, L. Velo, C. H. Blanton, M. M. Mosiehl, and J. L. Paterson, "High Performance Sub-Half Micron CMOS Using Rapid Thermal Processing," *IEDM Tech. Digest*, pp. 101–104 (1991).

- M. Rodder, S. Aur, and I.-C. Chen, "A Scaled 1.8 V, 0.18 μm Gate Length CMOS Technology: Device Design and Reliability Considerations," *IEDM Tech. Digest*, pp. 415–418 (1995).

- S. Yang, S. Ahmed, B. Arcot, R. Arghavani, P. Bai,

S. Chambers, P. Charvat, R. Cotner, R. Gasser, T. Ghani,

M. Hussein, C. Jan, C. Kardas, J. Maiz, and P. McGregor, "A

High Performance 180 nm Generation Logic Technology,"

IEDM Tech. Digest, pp. 197–200 (1998).

- T. Ghani, S. Ahmed, P. Aminzadeh, J. Bielefeld, P. Charvat, C. Chu, M. Harper, P. Jacob, C. Jan, J. Kavalieros, C. Kenyon, R. Nagisetty, P. Packan, J. Sebastian, M. Taylor, J. Tsai, S. Tyagi, S. Yang, and M. Bohr, "100 nm Gate Length High Performance/Low Power CMOS Transistor Structure," *IEDM Tech. Digest*, pp. 415–418 (1999).

- S. Tyagi, M. Alavi, R. Bigwood, T. Bramblett,

J. Brandenburg, W. Chen, B. Crew, M. Hussein, P. Jacob,

C. Kenyon, C. Lo, B. Mcintyre, Z. Ma, P. Moon, P. Nguyen,

L. Rumaner, R. Schweinfurth, S. Sivakumar, M. Stettler,

S. Thompson, B. Tufts, J. Xu, S. Yang, and M. Bohr, "A

130 nm Generation Logic Technology Featuring 70 nm

Transistors, Dual Vt Transistors and 6 Layers of Cu

Interconnects," IEDM Tech. Digest, pp. 567–570 (2000).

- S. Thompson, M. Alavi, R. Arghavani, A. Brand, R. Bigwood, J. Brandenburg, B. Crew, V. Dubin, M. Hussein, P. Jacob, C. Kenyon, E. Lee, B. Mcintyre, Z. Ma, P. Moon, P. Nguyen, M. Prince, R. Schweinfurth, S. Sivakumar, P. Smith, M. Stettler, S. Tyagi, M. Wei, J. Xu, and S. Yang, and M. Bohr, "An Enhanced 130 nm Generation Logic Technology Featuring 60 nm Transistors Optimized for High Performance and Low Power at 0.7–1.4 V," *IEDM Tech. Digest*, pp. 257–260 (2001).

- 14. K. Goto, S. Satoh, H. Ohta, S. Fukuta, T. Yamamoto, T. Mori, Y. Tagawa, T. Sakuma, T. Saiki, Y. Shimamune, A. Katakami, A. Hatada, H. Morioka, Y. Hayami, S. Inagaki, K. Kawamura, Y. Kim, H. Kokura, N. Tamura, N. Horiguchi, M. Kojima, T. Sugii, and K. Hashimoto, "Technology Booster Using Strain-Enhancing Laminated SiN (SELS) for 65 nm Node HP MPUs," *IEDM Tech. Digest*, pp. 209–212 (2004).

- P. Bai, C. Auth, S. Balakrishnan, M. Bost, R. Brain, V. Chikarmane, R. Heussner, M. Hussein, J. Hwang, D. Ingerly, R. James, J. Jeong, C. Kenyon, E. Lee, S.-H. Lee, N. Lindert, M. Liu, Z. Ma, T. Marieb, A. Murthy, R. Nagisetty, S. Natarajan, J. Neirynck, A. Ott, C. Parker, J. Sebastian, R. Shaheed, S. Sivakumar, J. Steigerwald, S. Tyagi, C. Weber, B. Woolery, A. Yeoh, K. Zhang, and M. Bohr, "A 65 nm Technology Featuring 35 nm Gate Lengths, Enhanced Channel Strain, 8 Cu Interconnect Layers, Low-k ILD and 0.54 μm² SRAM Cell," *IEDM Tech. Digest*, pp. 657–660 (2004).

- A. Lochtefeld and D. A. Antoniadis, "Investigating the Relationship Between Electron Mobility and Velocity in Deeply Scaled NMOS via Mechanical Stress," *IEEE Electron Device Lett.* 22, 591–593 (2001).

- K. Uchida, T. Krishnamohan, K. C. Saraswat, and Y. Nishi, "Physical Mechanisms of Electron Mobility Enhancement in Uniaxial Stressed MOSFETs and Impact of Uniaxial Stress Engineering in Ballistic Regime," *IEDM Tech. Digest*, pp. 135–138 (2005).

- 18. International Technology Roadmap for Semiconductors, 2004 Update (online); see <a href="http://www.itrs.net/Common/2004Update/2004Update.htm">http://www.itrs.net/Common/2004Update/2004Update.htm</a>.

- K. Rim, K. Chan, L. Shi, D. Boyd, J. Ott, N. Klymko,

F. Cardone, L. Tai, S. Koester, M. Cobb, D. Canaperi, B. To,

E. Duch, I. Babich, R. Carruthers, P. Saunders, G. Walker,

Y. Zhang, M. Steen, and M. Ieong, "Fabrication and Mobility Characteristics of Ultra-Thin Strained Si Directly on Insulator (SSDOI) MOSFETs," *IEDM Tech. Digest*, pp. 47–52 (2003).

- T. A. Langdo, A. Lochtefeld, M. T. Currie, R. Hammond, V. K. Yang, J. A. Carlin, C. J. Vineis, G. Braithwaite, H. Badawi, M. T. Bulsara, and E. A. Fitzgerald, "Preparation of Novel SiGe-Free Strained Si on Insulator Substrates," Proceedings of the IEEE International SOI Conference (Cat. No. 02CH37347), 2002, pp. 211–212.

- T. S. Drake, C. Ní Chléirigh, M. L. Lee, A. J. Pitera, E. A. Fitzgerald, D. A. Antoniadis, D. H. Anjum, J. Li, R. Hull, N. Klymko, and J. L. Hoyt, "Fabrication of Ultra-Thin Strained Silicon on Insulator," *J. Electron Mater.* 32, 972–975 (2003).

- K. Rim, J. Chu, H. Chen, K. A. Jenkins, T. Kanarsky, K. Lee, A. Mocuta, H. Zhu, R. Roy, J. Newbury, J. Ott, K. Petrarca, P. Mooney, D. Lacey, S. Koester, K. Chan, D. Boyd, M. Ieong, and H.-S. Wong, "Characteristics and Device Design of Sub-100 nm Strained Si N- and PMOSFETs," Symp. VLSI Technol., pp. 98–99 (2002).

- 23. C. W. Leitz, M. T. Currie, M. L. Lee, Z.-Y. Cheng, D. A. Antoniadis, and E. A. Fitzgerald, "Hole Mobility Enhancements in Strained Si/Si<sub>1-y</sub>Ge<sub>y</sub> p-Type Metal-Oxide Semiconductor Field Effect Transistors Grown on Relaxed Si<sub>1-x</sub>Ge<sub>x</sub> (x < y) Virtual Substrates," Appl. Phys. Lett. 79, 4246–4248 (2001).

- 24. J. Jung, M. L. Lee, S. Yu, E. A. Fitzgerald, and D. A. Antoniadis, "Implementation of Both High-Hole and Electron Mobility in Strained Si/Strained Si<sub>1-y</sub>Ge<sub>y</sub> on Relaxed Si<sub>1-x</sub>Ge<sub>x</sub> (x < y) Virtual Substrate," *IEEE Electron Device Lett.* **24**, 460–462 (2003).

- M. L. Lee and E. A. Fitzgerald, "Optimized Strained Si/ Strained Ge Dual-Channel Heterostructures for High Mobility P- and N-MOSFETs," *IEDM Tech. Digest*, pp. 429–432 (2003).

- S. Takagi, A. Toriumi, M. Iwase, and H. Tango, "On the Universality of Inversion Layer Mobility in Si MOSFET's: Part I—Effects of Substrate Impurity Concentration," *IEEE Trans. Electron Devices* 41, 2357–2362 (1994).

- 27. H. Shang, H. Okorn-Schmidt, K. K. Chan, M. Copel, J. A. Ott, P. M. Kozlowski, S. E. Steen, S. A. Cordes, H.-S. P. Wong, E. C. Jones, and W. E. Haensch, "High Mobility p-Channel Germanium MOSFETs with a Thin Ge Oxynitride Gate Dielectric," *IEDM Tech. Digest*, pp. 441–444 (2002).

- A. Ritenour, S. Yu, M. L. Lee, N. Lu, W. Bai, A. Pitera, E. A. Fitzgerald, D. L. Kwong, and D. A. Antoniadis, "Epitaxial Strained Germanium p-MOSFETs with HfO<sub>2</sub> Gate Dielectric and TaN Gate Electrode," *IEDM Tech. Digest*, pp. 433–436 (2003).

- 29. C. O. Chui, H. Kim, D. Chi, B. B. Triplett, P. C. McIntyre, and K. C. Saraswat, "A Sub-400 C Germanium MOSFET Technology with High-*k* Dielectric and Metal Gate," *IEDM Tech. Digest*, pp. 437–440 (2002).

- C. O. Chui, H. Kim, P. C. McIntyre, and K. C. Saraswat, "A Germanium MOSFET Process Integrating Metal Gate and Improved Hi-k Dielectrics," *IEDM Tech. Digest*, pp. 437–440 (2003).

- 31. C. Ni Chleirigh, C. Jungemann, J. Jung, O. O. Olubuyide, and J. L. Hoyt, "Extraction of Band Offsets in Strained Si/Strained Si<sub>1-y</sub>Ge<sub>y</sub> on Relaxed Si<sub>1-x</sub>Ge<sub>x</sub> Dual Channel Enhanced

- Mobility Structures," *Proceedings of the Electrochemical Society: SiGe: Materials, Processing and Devices*, PV2004-7, 2004, pp. 99–109.

- C. Ni Chleirigh, O. O. Olubuyide, and J. L. Hoyt, "Mobility and Sub-Threshold Characteristics in High-Mobility Dual-Channel Strained Si/Strained SiGe p-MOSFETs," *IEEE DRC Tech. Digest*, pp. 203–204 (2005).

- T. Krishnamohan, Z. Krivokapic, K. Uchida, Y. Nishi, and K. C. Saraswat, "Low Defect Ultra-Thin Fully Strained-Ge MOSFET on Relaxed Si with High Mobility and Low Bandto-Band-Tunneling (BTBT)," Symp. VLSI Technol., pp. 82–83 (2005).

- 34. G. Xia, H. M. Nayfeh, M. L. Lee, E. A. Fitzgerald, D. A. Antoniadis, D. H. Anjum, J. Li, R. Hull, N. Klymko, and J. L. Hoyt, "Impact of Ion Implantation Damage and Thermal Budget on Mobility Enhancement in Strained-Si n-Channel MOSFETs," *IEEE Trans. Electron Devices* 51, 2136–2144 (2004).

- S. Yu, J. Jung, J. L. Hoyt, and D. A. Antoniadis, "Strained-Si-Strained-SiGe Dual Channel Layer Structure as CMOS Substrate for Single Workfunction Metal-Gate Technology," *IEEE Electron Device Lett.* 25, 402–404 (2004).

- 36. F. Andrieu, T. Ernst, O. Faynot, Y. Bogumilowicz, J.-M. Hartmann, J. Eymery, D. Lafond, Y.-M. Levaillant, C. Dupré, R. Powers, F. Fournel, C. Fenouillet-Beranger, A. Vandooren, B. Ghyselen, C. Mazure, N. Kernevez, G. Ghibaudo, and S. Deleonibus, "Co-Integrated Dual Strained Channels on Fully Depleted sSDOI CMOSFETs with HfO<sub>2</sub>/TiN Gate Stack Down to 15nm Gate Length," Proceedings of the IEEE International SOI Conference, 2005, pp. 223–225.

- J. Jung, C. Ni Chleirigh, S. Yu, O. O. Olubuyide, and J. Hoyt, and D. A. Antoniadis, "Tradeoff Between Mobility and Subthreshold Characteristics in Dual-Channel Heterostructure n- and p-MOSFETs," *IEEE Electron Device Lett.* 25, 562–564 (2004).

- I. Åberg, O. O. Olubuyide, J. Li, R. Hull, and J. L. Hoyt, "Fabrication of Strained Si/Strained SiGe/Strained Si Heterostructures on Insulator by a Bond and Etch-Back Technique," *Proceedings of the IEEE International SOI* Conference, 2004, pp. 35–36.

- Z. Cheng, A. J. Pitera, M. L. Lee, J. Jung, J. L. Hoyt, D. A. Antoniadis, and E. A. Fitzgerald, "Fully Depleted Strained-SOI n- and p-MOSFETs on Bonded SGOI Substrates and Study of the SiGe/BOX Interface," *IEEE Electron Device Lett.* 25, 147 (2004).

- 40. I. Aberg, C. Ni Chleirigh, and J. L. Hoyt, "Ultra-Thin Body Strained Si and SiGe Heterostructure on Insulator MOSFETs," to appear in *IEEE Trans. Electron Devices* (2006)

- 41. I. Åberg, C. Ní Chléirigh, O. O. Olubuyide, X. Duan, and J. L. Hoyt, "High Electron and Hole Mobility Enhancements in Thin-Body Strained Si/Strained SiGe/Strained Si Heterostructures on Insulator," *IEDM Tech. Digest*, pp. 173–176 (2004).

- 42. TCAD, Synopsys, Mountain View, CA; see <a href="http://www.synopsys.com/products/tcad/tcad.html">http://www.synopsys.com/products/tcad/tcad.html</a>.

- D. Esseni, M. Mastrapasqua, G. K. Celler, C. Fiegna,

L. Selmi, and E. Sangiorgi, "Low Field Electron and Hole Mobility of SOI Transistors Fabricated on Ultrathin Silicon Films for Deep Submicrometer Technology Application," *IEEE Trans. Electron Devices* 48, 2842–2850 (2001).

- M. V. Fischetti, Z. Ren, P. M. Solomon, M. Yang, and K. Rim, "Six-Band K.P Calculation of the Hole Mobility in Silicon Inversion Layers: Dependence on Surface Orientation, Strain, and Silicon Thickness," *J. Appl. Phys.* 94, 1079–1095 (2003).

- E. Wang, P. Matagne, L. Shifren, B. Obradovic, R. Kotlyar, S. Cea, J. He, Z. Ma, R. Nagisetty, S. Tyagi, M. Stettler, and M. D. Giles, "Quantum Mechanical Calculation of Hole Mobility in Silicon Inversion Layers Under Arbitrary Stress," *IEDM Tech. Digest*, pp. 147–150 (2005).

- S. E. Thompson, G. Sun, K. Wu, J. Lim, and T. Nishida, "Key Differences of Process-Induced Uniaxial vs. Substrate-Induced Biaxial Stressed Si and Ge Channel MOSFETs," *IEDM Tech. Digest*, pp. 221–224 (2004).

- 47. R. Westhoff, J. Carlin, M. Erdtmann, T. A. Langdo, C. Leitz, V. Yang, K. Petrocelli, M. T. Bulsara, E. A. Fitzgerald, and C. J. Vineis, "A Novel, High Quality SiGe Graded Buffer Growth Process Using GeCl<sub>4</sub>," *Proceedings of the Electrochemical Society: SiGe: Materials, Processing and Devices*, PV2004-7, 2004, pp. 589–599.

- 48. G. Xia, O. O. Olubuyide, J. L. Hoyt, and M. Canonico, "Strain Dependence of Si–Ge Interdiffusion in Epitaxial Si/Si<sub>1-y</sub>Ge<sub>y</sub>/Si Heterostructures on Relaxed Si<sub>1-x</sub>Ge<sub>x</sub> Substrates," *Appl. Phys. Lett.* **88**, 13507–13509 (2006).

- H. C.-H. Wang, Y.-P. Wang, S.-J. Chen, C.-H. Ge, S. M. Ting, J.-Y. Kung, R.-L. Hwang, H.-K. Chiu, L. C. Sheu, P.-Y. Tsai, L.-G. Yao, S.-C. Chen, H.-J. Tao, Y.-C. Yeo, W.-C. Lee, and C. Hu, "Substrate-Strained Silicon Technology: Process Integration," *IEDM Tech. Digest*, pp. 61–64 (2003).

- J. G. Fiorenza, G. Braithwaite, C. W. Leitz, M. T. Currie, J. Yap, F. Singaporewala, V. K. Yank, T. A. Langdo, J. Carlin, M. Somerville, A. Lochtefeld, H. Bawadi, and M. T. Bulsara, "Film Thickness Constraints for Manufacturable Strained Silicon CMOS," Semicond. Sci. Technol. 19, L4–L8 (2004).

- S. Datta, G. Dewey, M. Doczy, B. S. Doyle, B. Jin, J. Kavalieros, R. Kotlyar, M. Metz, N. Zelick, and R. Chow, "High Mobility Si/SiGe Strained Channel MOS Transistors with HfO<sub>2</sub>/TiN Gate Stack," *IEDM Tech. Digest*, pp. 653–656 (2003).

- S. Takagi, T. Mizuno, T. Tezuka, N. Sugiyama, T. Numata, K. Usuda, Y. Moriyama, S. Nakaharai, J. Koga, A. Tanabe, N. Hirashita, and T. Maeda, "Channel Structure Design, Fabrication and Carrier Transport Properties of Strained-Si/ SiGe-on-Insulator (Strained-SOI) MOSFETs," *IEDM Tech. Digest*, pp. 57–60 (2003).

- 53. B. Jin, J. Brask, S. Datta, G. Dewey, M. Doczy, B. Doyle, J. Kavalieros, M. Metz, U. Shah, N. Zelick, and R. Chau, "Mobility Enhancement in Compressively Strained SiGe Surface Channel PMOS Transistors with HFO<sub>2</sub>/TiN Gate Stack," Proceedings of the Electrochemical Society: SiGe: Materials, Processing and Devices, PV2004-7, 2004, pp. 111–121.

- 54. O. Weber, Y. Bogumilowicz, T. Ernst, J.-M. Hartmann, F. Ducroquet, F. Andrieu, C. Dupre, L. Clavelier, C. LeRoyer, N. Cherkashin, M. Hytch, D. Rouchon, H. Dansas, A.-M. Papon, V. Carron, C. Tabone, and S. Deleonibus, *IEDM Tech. Digest*, pp. 143–146 (2005).

- I. Lauer, "The Effects of Strain on Carrier Transport in Thin and Ultra-Thin SOI MOSFETs," Ph.D. Thesis, Department of Electrical Engineering and Computer Science, Massachusetts Institute of Technology, Cambridge, MA, 2005.

- T. Irisawa, T. Numata, T. Tezuka, K. Usuda, and N. Hirashita, "High Current Drive Uniaxially-Strained SGOI pMOSFETs Fabricated by Lateral Strain Relaxation Technique," *Symp. VLSI Technol.*, pp. 178–179 (2005).

Received October 20, 2005; accepted for publication February 28, 2006; Internet publication June 27, 2006

Dimitri A. Antoniadis Department of Electrical Engineering and Computer Science, Massachusetts Institute of Technology, Cambridge, Massachusetts 02139 (daa@mtl.mit.edu). Dr. Antoniadis is the Ray and Maria Stata Professor of Electrical Engineering at MIT. He is Director of the multi-university Focus Research Center for Materials Structures and Devices, an IEEE Fellow, and the recipient of several professional awards. Dr. Antoniadis is an author or coauthor of more than 200 technical papers; he currently works on extreme-submicron Si, SOI, and Si/SiGe MOSFETs.

Ingvar Aberg Department of Electrical Engineering and Computer Science, Massachusetts Institute of Technology, Cambridge, Massachusetts 02139 (iaberg@mit.edu). Mr. Aberg is a Ph.D. student in electrical engineering and computer science at MIT. He received an M.S. degree in engineering physics in 2001 from Lund University, Sweden. Mr. Aberg's research topic is transport in strained Si and strained SiGe heterostructure MOSFETs, in particular for ultrathin-body on-insulator applications.

Cáit Ní Chléirigh Department of Electrical Engineering and Computer Science, Massachusetts Institute of Technology, Cambridge, Massachusetts 02139 (cait@mit.edu). Ms. Ní Chléirigh is a Ph.D. student in electrical engineering and computer science at MIT. She received an M.Eng. degree in microelectronics in 2000 from University College, Cork, Ireland. Her research topic is strained-Si and strained-SiGe heterostructure MOSFETs.

Osama M. Nayfeh Department of Electrical Engineering and Computer Science, Massachusetts Institute of Technology, Cambridge, Massachusetts 02139 (onayfeh@mtl.mit.edu). Mr. Nayfeh is a Ph.D. student in electrical engineering and computer science at MIT, where he received an M.S. degree in electrical engineering in 2004. His current research topics include Monte Carlo simulation of submicrometer electron devices, modeling of advanced transistors with novel high-mobility channel materials, and the fabrication of silicon nanoparticle/nanowire-based electronic and opto-electronic devices.

Ali Khakifirooz Microsystems Technology Laboratories, Massachusetts Institute of Technology, Cambridge, Massachusetts 02139 (khaki@mit.edu). Mr. Khakifirooz received B.S. and M.S. degrees in electrical engineering from the University of Tehran in 1997 and 1999, respectively. He is currently a Ph.D. candidate at MIT exploring carrier transport in decananometer MOSFETs and process integration issues for germanium-channel devices. He has authored or co-authored approximately 40 peer-reviewed papers. Mr. Khakifirooz is a member of the IEEE, MRS, and AVS.

Judy L. Hoyt Department of Electrical Engineering and Computer Science, Massachusetts Institute of Technology, Cambridge, Massachusetts 02139 (jlhoyt@mtl.mit.edu). Dr. Hoyt received her Ph.D. degree from Stanford University in 1988. She is a Professor of Electrical Engineering at MIT. Among other research projects, she participates in the MIT-led MARCO Focus Research Center on Materials, Structures, and Devices. Dr. Hoyt chaired the IEEE International Electron Devices Meeting in 2001. She is an author or coauthor of more than 100 technical papers, and her current research interests include Si-based heterostructures for bulk and on-insulator MOSFETs

376

## **Errata**

In the paper "Silicon CMOS Devices Beyond Scaling" by W. Haensch et al. in the *IBM Journal of Research and Development*, Volume 50, No. 4/5, July/September 2006, the exponent 2 was omitted from the expression  $fCV^2$  in the body and caption of Figure 1. The corrected figure follows.

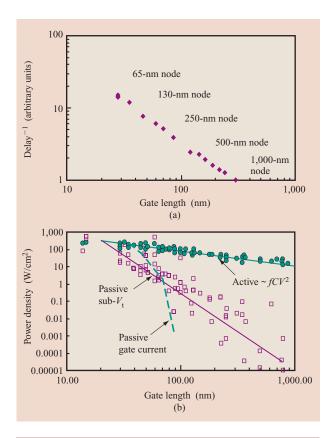

# Figure 1

(a) MOSFET performance vs. gate length; normalized MOSFET intrinsic device delay  $(CV/I_{\rm eff})$  vs. gate length. (b) Power density vs. gate length; data collected from literature for active power density and passive power density. Lines are intended to show trend.  $(fCV^2 = \text{frequency} \times \text{capacitance} \times \text{voltage}^2.)$

In the paper "Continuous MOSFET Performance Increase with Device Scaling: The Role of Strain and Channel Material Innovations" by D. A. Antoniadis et al. in the *IBM Journal of Research and Development*, Volume 50, No. 4/5, July/September 2006, the last term of Equation (5) should be multiplied by v. The corrected equation follows.

$$\begin{split} I_{\text{eff}} &= [I_{\text{D}}(V_{\text{G}} = V_{\text{dd}}/2, V_{\text{D}} = V_{\text{dd}}) \\ &+ I_{\text{D}}(V_{\text{G}} = V_{\text{dd}}, V_{\text{D}} = V_{\text{dd}}/2)]/2 \\ &= [Q_{\text{s}}'(V_{\text{G}} = V_{\text{dd}}/2, V_{\text{D}} = V_{\text{dd}}) \\ &+ Q_{\text{s}}(V_{\text{G}} = V_{\text{dd}}, V_{\text{D}} = V_{\text{dd}}/2)]v/2 \\ &= C_{\text{oxiny}}'W[(3 - \delta)V_{\text{dd}}/4 - V_{\text{t}}]v. \end{split} \tag{5}$$