# Design automation methodology and rf/analog modeling for rf CMOS and SiGe BiCMOS technologies

The rapidly expanding telecommunications market has led to a need for advanced rf integrated circuits. Complex rf- and mixed-signal system-on-chip designs require accurate prediction early in the design schedule, and time-to-market pressures dictate that design iterations be kept to a minimum. Signal integrity is seen as a key issue in typical applications, requiring very accurate interconnect transmission-line modeling and RLC extraction of parasitic effects. To enable this, IBM has in place a mature project infrastructure consisting of predictive device models, complete rf characterization, statistical and scalable compact models that are hardware-verified, and a robust design automation environment. Finally, the unit and integration testing of all of these components is performed thoroughly. This paper describes each of these aspects and provides an overview of associated development work.

D. L. Harame K. M. Newton R. Singh S. L. Sweeney S. E. Strang J. B. Johnson S. M. Parker C. E. Dickey M. Erturk G. J. Schulberg D. L. Jordan D. C. Sheridan M. P. Keene J. Boquet R. A. Groves M. Kumar D. A. Herman, Jr. B. S. Meyerson

## 1. Introduction

The rf CMOS and SiGe BiCMOS process technologies are at the leading edge of today's rapidly expanding telecommunications marketplace. Two key application areas in telecommunications are the wireless and wired areas. Examples in the wireless area include cellular telephone radios with protocols such as GSM (Global System for Mobile Communications [1]) and WCDMA (Wideband-Code Division Multiple Access [2]), location systems such as GPS (Global Positioning Satellite System), and wireless connectivity applications such as Bluetooth (2.4-GHz low power connectivity standard [3]) and 802.11x (IEEE wireless LAN standards [4]). Examples of the wired area are synchronous data transmission over optical networks using various protocols such as SONET (synchronous optical network transmission standard [5]) and SDH (synchronous digital hierarchy [6]). Both of these areas require the use of state-of-the-art rf/mixed-signal process technologies and design automation environments.

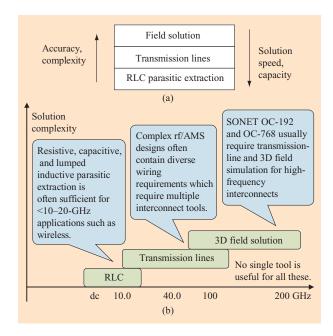

There is some differentiation between the wired and wireless requirements. The requirements for monolithic wireless chips emphasize technology with superior high-Q passives (inductors, varactors, and capacitors) in addition to the active devices, compact models with accurate noise-figure and distortion analyses, signal integrity analysis, and RLC parasitic extraction. The requirements for monolithic wired chips emphasize process technologies with very-high-speed active devices, rf/analog models of all devices—particularly FET devices, and distributed interconnect models including transmission-line models and field-solver solutions.

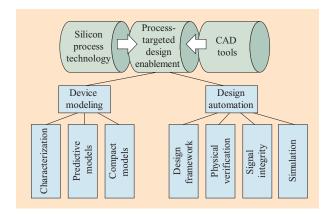

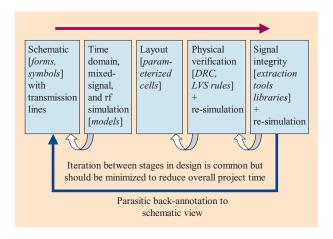

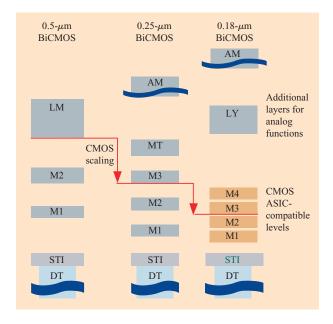

As integrated circuit (IC) design becomes more complex and application frequencies continue to rise, the different points in the supply chain must be highly integrated for final product success. The components necessary to successfully enable a silicon chip design are illustrated in **Figure 1**. There has to be a silicon technology base, a set of vendor CAD tools, and both modeling and design automation activities.

Copyright 2003 by International Business Machines Corporation. Copying in printed form for private use is permitted without payment of royalty provided that (1) each reproduction is done without alteration and (2) the *Journal* reference and IBM copyright notice are included on the first page. The title and abstract, but no other portions, of this paper may be copied or distributed royalty free without further permission by computer-based and other information-service systems. Permission to *republish* any other portion of this paper must be obtained from the Editor.

0018-8646/03/\$5.00 © 2003 IBM

Figure 1

Components required to successfully enable a silicon chip design.

The development of this rf/analog mixed-signal methodology at IBM dates back to the support for the early bipolar technology used in bipolar-based mainframes and, more recently, as an outgrowth of the analog BiCMOS processes initially developed for magnetoresistive (MR) preamplifier applications in the early 1990s. For bipolar mainframes, IBM developed internal modeling and circuit simulation tools<sup>1</sup> [7] with an efficient Monte Carlo statistical simulation package. Today, high-performance analog applications utilize the entire BiCMOS device menu and require accurate analog models for all devices. Digital models used to support the standard digital CMOS technologies do not provide sufficient accuracy in predicting the device characteristics in these regimes. In addition, analog circuit designers requested scalable bipolar junction transistor (BJT) models to remove the limitations imposed by an npn device library. These product design requirements defined the direction for the development of more advanced analog models.

In 1990, IBM began using workstation-based OEM design automation tools. In 1992, IBM released the first BiCMOS Cadence\*\*-based² design kits (starting with the design kit for CBiCMOS³), which included model libraries, symbol libraries, model/layout call-back routines, SKILL\*\* routines (SKILL is the Cadence application extension language), parameterized cells for layout, layout versus schematic checking, design-rule checking, parasitic extraction, and custom graphical user interface tools. This early kit contained all of the basic elements found in today's design kits. In 1994, work began on the

<sup>1</sup> A Statistical Analysis Program (ASTAP), an IBM internal circuit simulation tool with compiled model interface.

development of complex partial response maximum likelihood (PRML) read channel chips, which have a large digital as well as analog content. This required the development of new methodologies to handle analog mixed-signal designs. Work has continued on these tools over the past ten years, leading to a very flexible and robust design kit.

This paper describes the device-level rf/analog enablement methodology practiced at IBM. This enablement methodology is roughly divided into three major sections. The first section focuses on the co-development of the technology using a robust methodology that starts with technology concepts and evolves to early compact models (predictive modeling). Building and calibrating this methodology is a complex process, involving much greater effort than the simple use of vendor tools. The second section describes a characterization and modeling methodology that focuses on a strong rf/analog infrastructure with a statistical emphasis in order to fully simulate the product in manufacturing and predict performance yields (characterization and modeling). Finally, the third section discusses a detailed integrated design automation methodology/framework that includes physical design and verification (with inclusion of complete rf requirements), accurate signal integrity analysis, rf and mixed-signal simulation, and final test verification.

# 2. Predictive modeling

A fundamental difference between digital technology development and analog/rf technology development is the sensitivity of analog/rf circuits to many manufacturability/performance tradeoffs that must be made. Thus, while feedback between IC designers and technologists during technology definition is critical for timely product development, it is difficult to realize in practice, because to an IC designer the technology is the design kit-a complete and accurate set of compact models for both active and passive devices as well as interconnects. It is expected to reflect a stable and well-characterized process, while to the technologist the technology is a process recipe that is roughly characterized, often in flux, and, in practice, often not actually realized until the final technology qualification stage. The role of predictive modeling is to utilize detailed process and device simulation, or technology CAD (TCAD), in place of hardware to facilitate the feedback loop between circuit designer and process technologist until definitive hardware data is finally incorporated into the design kit. This feedback path provides timely notification to the technologist of potential shortcomings in the targeted technology design point, thus optimizing the use of the available experimental wafer budget. For the circuit designer, it provides more design turns with the

<sup>&</sup>lt;sup>2</sup> Cadence Design Systems, Inc., San Jose, CA.

<sup>&</sup>lt;sup>3</sup> S. Strang, IBM Microelectronics Division, Essex Junction, VT, private communication.

technology and thus a greater likelihood of meeting circuit performance targets.

# **Technology CAD**

Semiconductor TCAD originated in the early 1960s [7] with efforts to understand and optimize bipolar transistors. This effort continues today, with the increases in computing power available leveraged to understand and engineer devices with higher operating speeds and fabricated with more complex processes. The TCAD paradigm is applied to all conceivable types of active and passive devices, and intensive TCAD studies are now part of all semiconductor technology development efforts.

The TCAD paradigm can be described as follows:

Detailed process simulation creates one-, two-, or three-dimensional device representations, consisting of structural (film thicknesses and shapes) and impurity concentrations used as input for device simulation. Device simulation produces the dc and ac characteristics of interest, which are in turn used to define compact models for use in a prototype design kit for the technology. Thus, process options can receive circuit-design feedback before expending the time and budget to define these options in silicon. While TCAD is typically used to assist technology development, it is leveraged to its fullest extent when combined with compact model development to provide early technology access for circuit design.

#### **Process simulation**

Physical process simulation is the critical component in a predictive TCAD capability. Research and development of existing process simulation capabilities are due to the last decade's worth of logic CMOS scaling. Ever more sophisticated process simulation capabilities are being developed as semiconductor processing capabilities, driven by an extremely competitive microelectronics industry, continually progress. However, despite intensive efforts to bring higher-level modeling capabilities such as molecular dynamics and kinetic Monte Carlo codes into practical use, continuum codes based on silicon process physics are still the primary platform for semiconductor process simulation and are focused on here. The critical silicon process operations are impurity implantation and diffusion, oxidation, and material deposition and etching. Silicon and silicon-germanium epitaxy, an increasingly critical silicon process step, is treated via a series of material depositions and diffusions.

Despite the intensive effort to understand, characterize, and model silicon process physics driven by the CMOS logic microelectronics industry, industrial use still requires continual calibration of model parameters, and the predictive range of any process modeling capability can vary significantly between process modules. The most effective approach to TCAD calibration begins with

optimizing essential process simulation models, such as impurity diffusion coefficients, implant models, and film thicknesses, to available physical data such as that obtained from structural cross sections and secondary ion mass spectrometry (SIMS). This initial calibration provides a good starting point for multidimensional process and device simulations, the goal of which is to fit electrical data considered critical for the target use of the simulation capability. A feedback loop is then established and exercised, in which a few critical process and device model parameters are optimized to fit the target electrical data. A successful calibration effort provides a selfconsistent TCAD capability that links process levers to electrical characteristics through simulation. This has been found to be a very powerful tool to provide the ability to explore design space and optimize device performance outside the lengthy and expensive silicon fabrication process.

#### **Device simulation**

Much like process simulation, device simulation has been implemented at several levels of physical sophistication. The approach used in the pioneering continuum-based device simulation efforts [7–9] continues to be the foundation of most silicon technology CAD efforts. This is particularly true in the predictive modeling mode, which for compact model generation demands simulation of the complete device structure, including all parasitic capacitances and resistances, and often represents a considerable expanse of silicon, over a wide range of bias conditions.

Continuum-based device simulation consists of the solution of Poisson's equation along with two or more equations accounting for the transport, generation, and recombination of holes and electrons in the semiconductor. Additional equations can be added to account for carrier energy exchange with the silicon lattice, generating average carrier temperatures, and thus address nonstationary transport effects such as velocity overshoot and device lattice self-heating. A further enhancement for simulation of field-effect devices is the incorporation of some form of Schrödinger's equation to account for carrier quantization effects. An immense amount of theoretical and experimental work has been done to formulate and calibrate the many physical models required in a typical continuum device simulation, such as carrier mobility as a function of electric field, doping concentration, lattice temperature, and surface roughness, and effects of impurity concentration and species on the silicon bandgap [10].

Continuum-based device simulation is able to duplicate experimental ac measurements, such as scattering-parameter (S-parameter) extraction, by application of the ac small-signal approximation to the Poisson and transport

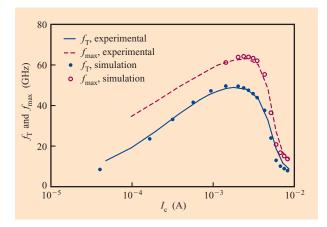

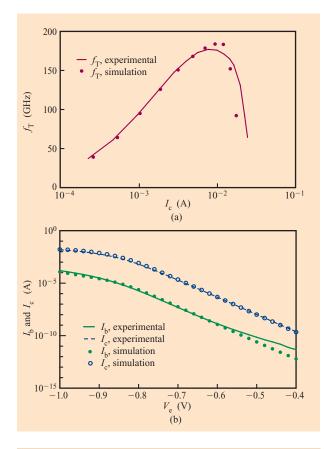

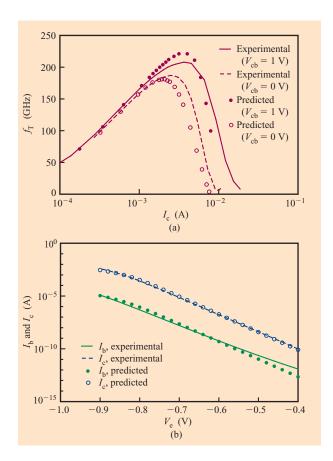

Comparison of experimental and simulated  $f_{\rm T}$  and  $f_{\rm max}$  for 50-GHz/60-GHz  $f_{\rm T}/f_{\rm max}$  SiGe HBT. The device parameters depicted here and in Figure 3, critical levers for rf performance optimization, were extracted from device-level ac measurements and small-signal ac simulations of two-dimensional device cross sections, generated by detailed process simulation and appropriately scaled in length.

equations [11]. Implementation of the small-signal approximation completes the demand on the TCAD capability of supplying all necessary electrical data for building a compact model. When device simulation is combined with process simulation and suitably calibrated, the system so formed provides the technology development effort the ability to quickly, and with a useful range of self-consistent physical accuracy, connect process levers to all critical device electrical characteristics.

Semiconductor device scaling has driven futuregeneration devices into a physical regime in which typical operation is dominated by physical transport effects that are not well addressed by enhanced continuum approaches. A greater amount of physical accuracy and detail is provided by Monte Carlo particle transport codes [12], albeit on (typically) reduced computational regions and requiring significantly longer solution times.

## **Examples**

An example of TCAD application in the technology development mode follows. A SiGe heterojunction bipolar transistor (HBT) with ac performance characterized by  $f_{\rm T}=50~{\rm GHz}$  and  $f_{\rm max}=60~{\rm GHz}$  was assumed to be the technology starting point. The objective of the analysis was to size the ac-performance consequences of simplifying the extrinsic base formation. It began by calibrating the process and device simulation to the technology. The results of the concurrent two-dimensional process and device calibration are shown in **Figure 2**. The figure

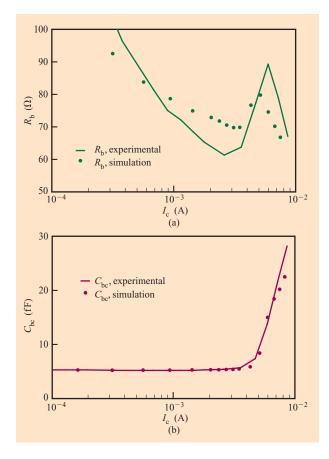

compares the experimental and simulated summary ac parametrics of cutoff frequency  $f_{\rm T}$  and maximum frequency of oscillation  $f_{\max}$ . Both parameters were well matched by their respective simulations, and they involved all aspects of the device performance—transport in both low- and high-doped and depletion regions, across signal frequencies and bias conditions—a strong indication that the ac performance of the device was captured with an adequate degree of accuracy. Figure 3(a) shows the experimental and simulated base resistance  $R_{\rm h}$  for the target device. The base resistance had a strong threedimensional component that could not be fully captured by the two-dimensional simulations; however, the simulation showed the same qualitative characteristics and was within 10 to 15% of the experimental values at the current densities at which peak ac performance  $(f_{T})$  was observed. The collector base capacitance  $C_{bc}$  [Figure 3(b)] could be modeled by the two-dimensional approach. Both simulation and experimental parameters were extracted from the low-frequency Z parameters. From this

Figure 3

Comparison of simulated and experimental  $R_{\rm b}$  (a) and  $C_{\rm bc}$  (b) for 50-GHz/60-GHz  $f_{\rm T}/f_{\rm max}$  SiGe HBT.

calibrated starting point, the consequences for the device ac performance due to a simplified, non-self-aligned (NSA) process for the extrinsic base were investigated.

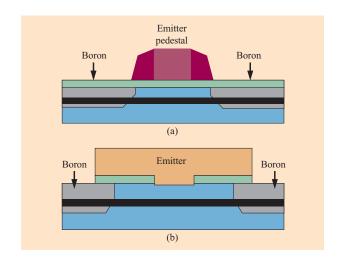

Figure 4(a) depicts the process used to form the extrinsic base in the device of Figures 2 and 3. In this selfaligned process, a pedestal structure is formed to define the future position of the emitter polysilicon, and it is surrounded by a sidewall spacer. The extrinsic base is then implanted, with the spacer controlling the separation, independently of the emitter width, between the emitter and extrinsic base. An alternative extrinsic-base formation method is shown in Figure 4(b). In this NSA method, the extrinsic base implant occurs immediately after the emitter sidewall spacer is etched. This latter process is simpler and cheaper than the self-aligned process but necessarily results in a higher base resistance, since process tolerances demand that the distance between the emitter outdiffusion and the extrinsic base implant be larger. A more subtle issue is the effect of the extrinsic-base implant on the ac performance of the device. Both experimental results and understanding of silicon process physics suggest that point defects introduced by the extrinsic base implant can induce unwanted additional diffusion in the intrinsic base, thus degrading the ac performance of the transistor [13]. It is expected that the calibrated process and device simulation capability will accurately reflect that phenomenon and provide a method to size the many tradeoffs involved in this option.

Table 1 lists comparative values of several parameters. The simulation accurately predicted the increase in base resistance and simultaneous reduction in base-collector capacitance arising from the alternate extrinsic-base process. Further, it accurately captured the improvement in cutoff frequency  $f_{\rm T}$  resulting from the extrinsic base implant of the NSA process that differed in both dose and energy, as well as being spaced farther from the emitter-base junction. Finally, these modifications in device resistance, capacitance, and cutoff frequency were accurately reflected in the predicted maximum oscillation frequency  $f_{\rm max}$ .

Another example of the TCAD predictive approach pertains to the 200-GHz SiGe HBT technology performance path [14]. On the basis of the previous-generation  $f_{\rm T}=120$ -GHz technology [15], exploration of process and device modifications was performed with TCAD to identify promising ultrahigh-performance SiGe HBT design points [16]. In particular, significant modifications to the extrinsic base process module and epitaxial-base transistor structure were suggested. Because the new process modules required significant process development effort, test structures based on a simple NSA structure were used to prototype the vertical device structure. Initial samples showed promising ac performance results for an  $f_{\rm T}=200$ -GHz SiGe HBT.

### Figure 4

(a) Formation of a self-aligned extrinsic base for a 50-GHz/60-GHz  $f_{\rm T}/f_{\rm max}$  SiGe HBT. The emitter pedestal defines where the polysilicon emitter is to be formed later in the process. The spacers on either side of the emitter pedestal provide control over the tradeoff between reduced extrinsic-base resistance and deleterious effects of the point defects introduced by the extrinsic base implant. (b) Alternate extrinsic-base formation for 50-GHz/60-GHz  $f_{\rm T}/f_{\rm max}$  SiGe HBT. In this process, the extrinsic base implant is performed after the polysilicon emitter has been deposited and etched. This is simpler and cheaper than the selfaligned process depicted in (a), but is expected to result in significant degradation of the extrinsic-base resistance. How this base-resistance degradation would interact with possible changes in device capacitances and reductions in point-defect-enhanced diffusion in the intrinsic base to modify the critical ac performance metrics of  $f_{\rm T}$  and  $f_{\rm max}$  was the question addressed by the TCAD simulations. A comparison of simulated and experimental results is shown in Table 1.

**Table 1** Comparison of TCAD evaluation of acperformance consequences of non-self-aligned extrinsic base process.

| Parameter          | Experiment    | Simulation    |

|--------------------|---------------|---------------|

| $C_{ m bc}$        | ~0            | ~0            |

| $C_{ m be}$        | ~0            | ~0            |

| $R_{\mathrm{b}}$   | $+125 \Omega$ | $+110 \Omega$ |

| $f_{\mathrm{max}}$ | -21 GHz       | -18 GHz       |

| $f_{\mathrm{T}}$   | +7 GHz        | +8 GHz        |

While process development continued apace, an early design kit based on calibrated TCAD was formulated. The process to produce this early NSA hardware was used to calibrate the process and device simulation. The complete target process was then simulated, and a scalable compact vertical bipolar inter-company (VBIC) [17] model was

Non-self-aligned TCAD calibration in preparation for TCAD definition and model extraction for  $f_{\rm T}=200\text{-GHz}$  SiGe HBT device development. Process/device simulation and measured characteristics are compared. Parts (a) and (b) pertain respectively to ac and dc characterization.

extracted from electrical simulations, following the methodology depicted in Figure 1. Basic ac and dc electrical results used in the calibration are shown in **Figure 5**. A comparison with the compact model characteristics arising from the complete process fabricated a year later is shown in **Figure 6**. Working ring-oscillator circuits, showing record silicon stage delays, were subsequently designed on the basis of the modeling [18].

#### Summary

Technology CAD is becoming an increasingly critical part of rf technology development. With careful calibration and recognition of the predictive range of the many models and assumptions that constitute the process and device simulation approaches relied upon for industrial technology development, TCAD can significantly improve the process learning and technology performance progress achieved with a given experimental budget. When

#### Figure 6

Comparison of (a) ac and (b) dc characteristics of  $f_{\rm T}=200\text{-GHz}$  SiGe HBT hardware and compact models based on TCAD simulations of target process produced nine months prior to hardware completion.

leveraged to its fullest extent, TCAD can assume an important strategic role in rf product development by providing an efficient and inexpensive link between circuit designers and technologists, resulting in a tighter coupling between the technology and its target products and increasing the likelihood of meeting time-to-market goals. By providing early design kit information prior to the appearance of experimental hardware, more design turns are available to circuit designers, further ensuring the likelihood of timely product development.

# 3. Characterization

Characterization is an important step in the development of device compact models. Compact model development and parameter extraction involve both dc and ac data; the latter is usually in the form of two-port S-parameter measurements. Test sites are designed and fabricated to provide a full complement of device test structures to

allow for on-wafer measurements in support of model development. Test structures are designed to measure specific process and model parameters over a range of biases and temperatures.

Finally, it is essential to verify model functionality and circuit simulation accuracy. For specific applications, this may include low- and high-frequency noise measurements, large-signal measurements, and two-tone intermodulation distortion measurements.

#### In-line wafer measurements

A complete set of dc measurements is taken in line during wafer fabrication, and this provides an accurate method for determining the process parameters for each individual wafer. Data is collected for each wafer run through the fabrication line that then provides a large statistical database for many process and modeling parameters. The database parameters include inputs from device attributes, measurement data, and calculation formula. Electrical parameter data analysis benefits enormously from object-oriented techniques that make it easy to create comparison charts. A detailed description of the problems associated with collecting and storing in-line data and the software programs needed to analyze the data has been presented by Freeman [19] and is not reviewed here. This data is later used in the selection of modeling wafers to be slated for characterization. Since it is essential that process variations be fully determined, wafer characterization from the in-line data is an important first step in the data-acquisition and devicecharacterization process.

# DC, C-V, and matching measurements

DC and capacitance measurements are taken on a full set of on-wafer test structures for each device type, and a statistical database is built. Numerous wafers from several lots are tested to generate a large sample size to allow for the employment of statistical modeling techniques. DC measurements are performed on devices to characterize and model device performance, whereas capacitance-voltage (C-V) measurements, in addition to allowing capacitors themselves to be characterized, are also performed to determine specific device model circuit parameters. For example, capacitance measurements on specially designed structures allow for the gate oxide and overlap capacitances to be determined and included in the circuit model for FET devices. Matching measurements are important to fully determine the variation of device parametrics between adjacent devices.

Measurements are taken on each type of device across operating conditions and at numerous bias conditions to fully represent all possible operating modes. The full set of test structures includes a complete range of device sizes. This allows geometry dependencies to be

incorporated into the models. Data is also collected at a full range of temperatures ( $-50^{\circ}$ C to  $+145^{\circ}$ C) to allow device temperature dependencies to be fully determined.

At IBM, a program has been developed in objectoriented language, referred to as the Device Measurement

And Characterization System (DMACS), which has been

described in detail elsewhere [20]. Some key attributes of

the software program are storage of large quantities of

different kinds of data; storage of automated testing

programs; the ability to drive a large variety of

instruments under program control; display of the raw

data in numerous types of plots and charts as well

as manipulation of the data with various types of

calculations; and finally, the ability to output data into a

wide variety of formats so that it may be ported to other

modeling software tools. The program in effect serves as

an engineering development tool and also as a

manufacturing characterization tool.

# AC S-parameter measurements

Small-signal equivalent-circuit models have been developed to enable devices to be represented by lumped elements rather than complicated nonlinear equations. High-frequency two-port parameters such as S-parameters are measured to enable the development of these smallsignal equivalent-circuit models and determine their associated model parameters. As with dc measurements, S-parameter measurements are taken on both active and passive devices, across a full range of both geometries and temperatures, and, for active devices, at different operating conditions and across numerous biases. For passives, S-parameters are also converted to Y-parameters (admittance parameters) and are used to determine the input and output characteristics as a function of frequency. In addition, S-parameter measurements are used to calculate two important figures of merit for transistors: the cutoff frequency of the ac-current gain,  $f_{\rm T}$ , and the cutoff frequency of the maximum power gain, also called the maximum oscillation frequency,  $f_{max}$ .

Present applications demand measurement of device ac characteristics at frequencies as high as 110 GHz. Special steps must be taken at these frequencies to ensure data integrity and quality. The reference plane must be firmly established. In addition, at these frequencies, padset parasitics become an issue. A probe-tip calibration is carried out first in order to move the measurement reference plane to the probe tips. Then a two-step dembedding procedure is used to subtract both the series and parallel parasitics of the padsets, thus obtaining the high-frequency characteristics of the device itself. This procedure is described in detail elsewhere [21]. The two-port S-parameters are measured using a vector network analyzer and ground–signal–ground (G–S–G) probes. For active devices, special care must be taken regarding the

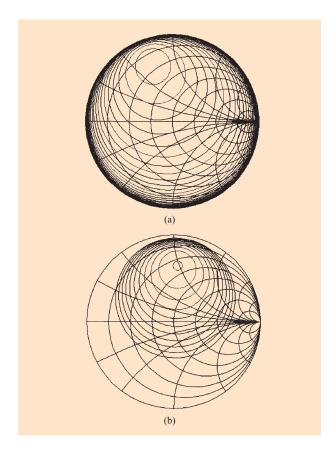

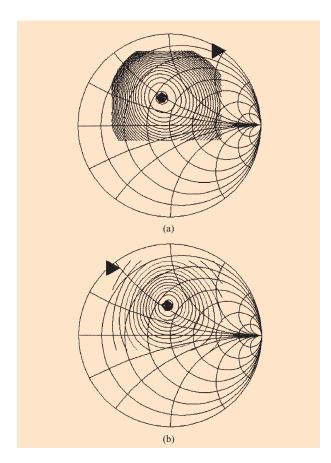

(a) Constant-gain circles vs. source impedance for an SiGe FET; contour start: 7 dB, contour step: 1 dB. (b) Constant-noise circles vs. source impedance for the same device; contour start: 5 dB, contour step: 0.5 dB. The circles illustrate the design tradeoffs that must be made between minimum noise and maximum gain.

power levels to prevent gain compression and to ensure that the device remains in the small-signal regime.

To calculate  $f_{\rm T}$ , the S-parameters are converted to H-parameters and, in graphical terms, the ac current gain,  $|H_{21}|$  (in dB), is plotted on a linear scale as a function of frequency on a log scale. The  $f_{\rm T}$  of the transistor is the point at which  $|H_{21}|$  crosses the x-axis. To facilitate the determination of  $f_{\rm T}$ , the IBM instrument control and data acquisition software (DMACS) calculates this parameter in the following manner. The  $|H_{21}|$  curve is assumed to have perfect single-pole, 20-dB/decade, roll-off characteristics. The  $f_{\rm T}$  is calculated using the base transit time  $\tau_{\rm T}$ , where

$$\tau_{\mathrm{T}} = \left| \frac{\sin \angle H_{21}}{|H_{21}|\omega} \right|. \tag{1}$$

Then  $f_{\rm T}$  is given by

$$f_{\rm T} = \frac{1}{2\pi\tau_{\rm T}}.\tag{2}$$

It can be shown from circuit theory that these equations are valid at any frequency, though care must be taken to carry out the calculation at a high enough frequency to avoid inaccuracies due to instrumentation phase limitations. The maximum oscillation frequency,  $f_{\rm max}$ , is determined as the frequency at which the maximum available power gain (MAG), also a quantity exhibiting single-pole transfer function characteristics, is unity, where

$$MAG = \left| \frac{S_{21}}{S_{12}} \right| (k - \sqrt{k^2 - 1}). \tag{3}$$

The term k is Kurokawa's stability factor and is given [22] by

$$k = \frac{1 - |S_{11}|^2 - |S_{22}|^2 + |S_{11}S_{22} - S_{12}S_{21}|^2}{2|S_{11}||S_{21}|}.$$

(4)

Using the calculation of MAG across the frequency range, DMACS then uses a linear regression routine to determine the x-intercept and thus  $f_{\rm max}$ . Again, care must be taken to ensure that an appropriate frequency range is used when performing the linear regression.

## Noise characterization

Both low-frequency flicker noise (1/f noise) and high-frequency, broadband noise parameters, including noise figure, associated gain, optimum reflection coefficient, and noise resistance, must be measured to facilitate the modeling efforts and the design of integrated telecommunication circuits in BiCMOS technologies. Flicker noise measurements are made to determine several subcircuit parameters in the modeling of the SiGe BiCMOS technologies. In addition to model verification, the broadband noise performance characterization gives the circuit designer a measure of the signal-to-noise-level degradation that will result when the device is added to the circuit, an important consideration in telecommunications systems, which typically process very low-level signals.

The associated noise figure describes the degradation of the signal-to-noise ratio between the input and output of the device. For a linear two-port device, the dependence of the noise figure on the source reflection coefficient is described by

$$F(\Gamma_{\rm s}) = F_{\rm min} + 4r_{\rm n} \frac{|\Gamma_{\rm s} - \Gamma_{\rm opt}|^2}{(1 - |\Gamma_{\rm s}|^2)|1 + \Gamma_{\rm opt}|^2},\tag{5}$$

where  $\Gamma_{\rm s}$  is the source reflection coefficient,  $F_{\rm min}$  is the minimum noise figure,  $r_{\rm n}$  is the normalized noise resistance (the sensitivity of the noise figure to changes in

the source reflection coefficient), and  $\Gamma_{ont}$  is the optimum source reflection coefficient which gives the minimum noise figure. The equation represents a parabola, indicating that a value of source impedance can be determined for which a minimum noise figure is achieved. Thus, high-frequency, broadband noise characterization, together with the gain characterization of the active device, can provide the circuit designer with the information needed to determine what kind of tradeoff must be made when impedancematching to the device for minimum noise figure vs. maximum gain. This tradeoff is illustrated in Figure 7. Figure 7(a) shows the constant-gain circles for an SiGe FET, and Figure 7(b) shows the corresponding constantnoise circles for the same device. The center of the smallest circle indicates the optimum source impedance for each parameter, and the spacing between the circles is an indication of how much the designer must give away when moving away from that optimum point.

Flicker (1/f) noise characterization is important because certain types of circuits in telecommunications systems are particularly sensitive to this low-frequency noise. Bipolar transistors and FETs exhibit very different levels of flicker noise. Therefore, it is important to characterize these devices when considering their use in circuits sensitive to such noise.

# Large-signal measurements

Determining how active devices behave at different power levels is also an important consideration when designing telecommunications systems. Many rf amplifiers are designed to operate in the weakly nonlinear region, where power-added efficiency (*PAE*) peaks. The power-added efficiency is defined as the ratio of the additional power provided by the amplifier to the dc power [23], viz.,

$$PAE = \frac{P_{\text{rf out}} - P_{\text{rf in}}}{P_{\text{dc}}}.$$

(6)

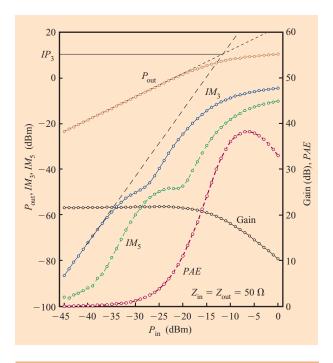

Large-signal measurements provide output power, gain, and efficiency information at a given input power level. Figure 8 shows the results of large-signal measurements made on an SiGe HBT. For these measurements, both the input and output impedance were set to 50  $\Omega$ . The figure illustrates the power levels at which the device enters compression and the power-added efficiency in that region. The 1-dB gain compression point, usually given in terms of output power, is an important quantity when considering the dynamic range of the transistor.

In addition to power level considerations, impedance matching throughout the system is an essential aspect of rf circuit design. Thus, it is also important to explore how the input and output impedance presented to each device in the system affect the performance of that device in the

# Figure 8

Measured large-signal and intermodulation distortion data for an SiGe HBT. The source and load terminations were set to 50  $\Omega$  and the determination of  $IP_3$  is illustrated.  $P_{\rm out}$  denotes the output power,  $IM_3$  denotes the third-order intermodulation product,  $IM_5$  denotes the fifth-order intermodulation product, PAE denotes the power-added efficiency, and  $P_{\rm in}$  denotes the input power.

circuit. Furthermore, a designer may want to determine the necessary impedance-matching conditions to achieve a specific desired performance from the device. Once either the desired input or output impedance is determined, contours can be generated for the other termination to illustrate tradeoffs that must be made between, for example, maximum power-added efficiency and maximum output power. Figure 9(a) shows the output power contours versus load termination for an SiGe transistor whose input impedance was conjugately matched for maximum gain. Figure 9(b) shows the power-added efficiency contours for the same device. Note that the optimum load termination for maximum output power and that for maximum power-added efficiency are near each other on the Smith chart, suggesting that a designer should be able to use this device in a circuit without a significant tradeoff between output power and poweradded efficiency.

#### **Distortion**

Many components of telecommunication systems receive numerous signals closely spaced in frequency at their inputs. The nonlinearities inherent in all active devices

(a) Output power (dBm) and (b) power-added efficiency contours vs. load termination for an SiGe transistor. Frequency = 900 MHz; source impedance set to complex conjugate match. In (a), contour start = 14.5 dBm and contour step = 0.25 dBm. In (b), contour start = 45% and contour step = 2.5%. Note that the optimum load impedance values for both are very close together, and there is a minimum tradeoff when matching for maximum output power and maximum power–efficiency.

lead to certain undesirable effects, such as intermodulation and harmonic distortion, which in turn lead to the transfer of power to other frequencies near the frequency of interest. For a device with two signals at its input, one at a frequency  $f_1$  and the other at a frequency  $f_2$ , it is traditionally the third-order (at frequencies  $2f_1$ – $f_2$  and  $2f_2$ – $f_1$ ) and fifth-order ( $3f_1$ – $2f_2$  and  $3f_2$ – $2f_1$ ) intermodulation products that are of most concern, because they are near the two frequencies of interest ( $f_1$  and  $f_2$ ) and therefore will be the most difficult to filter out of the system. Therefore, rf and telecommunications applications, such as power amplifiers, require devices that exhibit highly linear operating characteristics. Two-tone measurements must be performed on the device offerings in the SiGe BiCMOS and rf CMOS technologies to fully

analyze the linearity of the devices offered. Use is made of an ATN LP2 load-pull system to make these measurements. The third-order and fifth-order intermodulation products are commonly measured, and the third-order intercept point ( $IP_3$ ), an important figure of merit for describing linearity, is obtained. The intermodulation products are shown in Figure 8 for an SiGe HBT, and the extrapolation to  $IP_3$  is illustrated.  $IP_3$  is then used to determine the spurious free dynamic range ( $DR_{\rm f}$ ), defined as the difference between the output power at the fundamental and the output power at the third-order intermodulation product when the output power at the third-order intermodulation frequency is equal to the minimum detectable output signal,  $P_{\rm o,mds}$  [24].  $DR_{\rm f}$  is given by

$$DR_{\rm f} = \frac{2}{3} (IP_{\rm 3} - P_{\rm o,mds}). \tag{7}$$

Thus,  $IP_3$  provides the power-amp designer with a metric for determining a distortion-free operating range for the device.

#### Test site

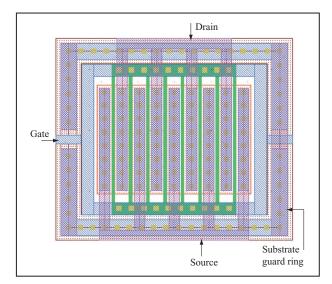

The key to generating accurate, scalable, full-featured models, as described in the next section, lies in the availability of test structures from which to make measurements. For example, test-site characterization macros needed to construct an n-FET model would include

- 1. A length and width array macro for dc extraction/optimization of the Berkeley short-channel IGFET model (BSIM) parameter set.

- 2. A capacitor array to extract gate-oxide, overlap, and source-to-drain capacitance and leakage.

- 3. A set length and width array macros to measure threshold voltage and mobility mismatch.

- 4. A set of rf *S*-parameter structures of varying length, width, and number of finger configurations.

- 5. Open/short "de-embedding" structures to go with the above *S*-parameter macros.

- 6. DC and S-parameter gate resistance extraction macro.

- 7. Macros to gauge proximity to n-type wells and other process-specific effects.

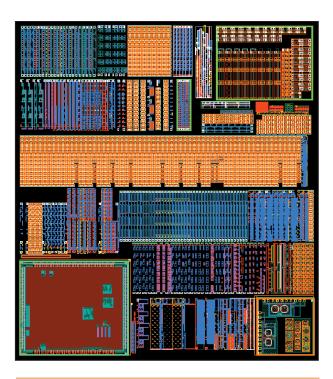

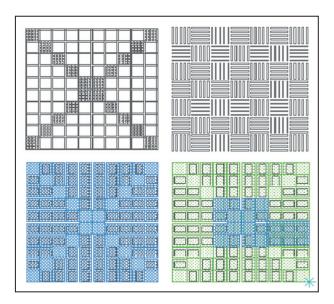

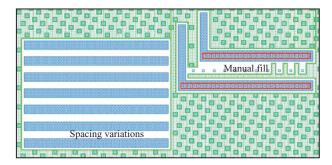

The vast number of structures required to cover the characterization needs of all of the devices in a given chip technology can be enormous. For example, an SiGe or rf CMOS modeling test site might be as large as 20 mm × 20 mm. **Figure 10** shows a top-level view of a test site (designated as the "Granite" test site) which is the primary modeling test site for the IBM rf CMOS technology.

# 4. Compact model development

A mathematical model that predicts the electrical characteristics of a semiconductor device as a function of the conditions and constraints applied to it is designated as a compact model. In the case of the MOSFET device, a compact model predicts the output current  $(I_{de})$  and its derivatives (  $g_{\rm m},\,g_{\rm ds},\,g_{\rm mb})$  as a function of temperature, voltage bias, channel length, and device width. A compact model may be composed of a single element, such as an ideal resistor, or a complex network of interdependent sources, resistors, capacitors, and diodes used to model a bipolar junction transistor (BJT). To analyze a model or circuit containing more than one element, a matrix solver such as HSPICE\*\*4 or Spectre\*\*5 must be used. Implementing the compact model may require the extraction of less than ten parameters, as is the case for a junction diode, or it may require the elaborate extraction and optimization needed to extract the dozens of parameters of a BSIM-based MOSFET model.

The primary goal of a compact model development effort is to provide physics-based, scalable models that are fully integrated into the overall design kit environment. The models must be capable of predicting the full complement of device characteristics and behavior as a function of bias and temperature and must represent the statistical process window of the technology being modeled. Another important consideration is to make use of industry-standard or common elements in building the model to allow for more efficient translation of the models to multiple simulators while maintaining consistency in simulation results.

The emphasis on models which are physics-based dictates that the development effort must employ direct parameter extraction, rather than empirical or numerical optimization, whenever possible. It is also important to make use of process information obtained from technology development, such as vertical profile dimensions or doping concentrations. The use of a more physical model is more effective for predicting results for conditions beyond those used during the initial model parameter extraction, such as different device geometries. The demands of the rf/analog design environment have also led to the use of more complex subcircuit topologies for both active and passive devices to better predict high-frequency behavior. However, it is important to minimize the number of elements required in order to maximize simulation efficiency.

All of the key building blocks for the development of the scalable, statistical, and physics-based models used in IBM are described throughout this section. Note that this information, from the physical device layout and

### Figure 10

"Granite" test-site layout for 0.25-µm rf CMOS chip technology; contains structures for obtaining information on process parameters, interconnect parameters, in-line test macros, modeling macros, etc.

design rules to the development of scaling equations and the incorporation of device characterization and in-line electrical data, is required regardless of the type of device that is being modeled.

# Statistical modeling

The compact device models being developed for the IBM SiGe BiCMOS and rf CMOS technologies have the ability to support standard Monte Carlo (statistical), process corner, and wafer-specific simulations. The basic structure of the model library makes use of a "skew file," which defines all of the statistical distributions, process corner parameters, and other model parameters that are shared across multiple devices. The definition of these distributions is dependent on the cooperation between technology development and compact model teams to determine the most dominant process parameter variations and the proper correlation of process and device model parameters. These correlations account for effects across multiple devices that may share a common process step, as well as multiple parameters within a single device that exhibit a strong physical correlation.

The primary input for specifying nominal and tolerance specifications of process parameters comes from in-line

<sup>&</sup>lt;sup>4</sup> Synopsys, Inc., Mountain View, CA.

<sup>&</sup>lt;sup>5</sup> Cadence Design Systems, San Jose, CA.

wafer (kerf) parametric data. This data provides the necessary statistical sample and establishes a direct connection between skew file parameters and measurements that are used as acceptance criteria for product wafers during manufacturing. Additional wafer characterization is used to supplement the in-line data and provide the basis for correlation of the process parameters and key device metrics, such as  $\operatorname{npn} f_{\mathrm{max}}$ .

The conventional method for process corner simulation has involved using a pair of model parameter sets to represent the process extremes, often referred to as "fast"/"slow" or "high"/"low" corners. The assumption in this method requires that, for a "fast" process corner, the device parameters are skewed so as to maximize active device currents and minimize other capacitances and resistances. While this may be valid for analyzing the process variation of the characteristic time constant of an analog circuit, the drawback of this method for corner-file generation is that this definition of the model parameter combinations will not always yield an extreme in the circuit performance for all types of analog applications.

To enable process corner simulation, the IBM skew file approach (patent pending) includes multiple corner parameters corresponding to each of the device types, such as resistors, capacitors, and BJTs. This structure supports simulation of different combinations beyond a single "fast" and "slow" corner pair and enhances a designer's ability to assess the sensitivity of the circuit performance. This sensitivity analysis can be done by repeating a simulation with each of the individual corner parameters set to +1 and -1 (corresponding to a  $\pm 1\sigma$ variation) and comparing the results against the nominal simulation. With only one corner parameter set to be nonzero at a time, the total number of simulations will be twice the number of corner parameters. These singleparameter simulations are carried out to determine the appropriate sign, positive or negative, for each corner parameter necessary to maximize (or minimize) overall circuit performance. In this methodology, equal weights are given to the variations of all device types, so all of the corner parameters are set to the same magnitude. This magnitude is determined by first finding the  $3\sigma$  variation limits of the circuit performance using a statistical simulation and then setting the magnitude of the corner parameters to match these limits. By using an initial Monte Carlo simulation to calibrate the results from the corner analyses, the designer acquires an efficient means to account for the effects of the process variation and include the necessary design margin. As a result, this approach provides the benefits of both conventional corner and Monte Carlo simulations and requires only a few additional simulation iterations.

In addition to the process statistics in the skew file, the individual model files also include distributions to represent device mismatch effects. The skew file statistics represent the global process variation across all wafers, while the mismatch represents the local variation observed on a typical wafer. Specific test-site structures are used to measure the mismatch and are designed using good layout practices such as use of same orientation of near-adjacent devices with symmetric wiring. As with all other aspects of the modeling, every attempt is made to define these mismatch effects and account for geometric and bias dependence in a manner that is consistent with the physical nature of the devices.

One key aspect of the extraction methodology necessary to maintain the statistical integrity of the final models is the assessment of the hardware used to extract the model parameters. It is important to establish any offset that may exist between the defined nominal process values and the measurements of test-site wafers. Following the device characterization and completion of the model extraction, skew file parameters are then recentered to represent nominal process and device specifications. This concept of "recentering" also enables the models to support simulation analyses using skew file parameter adjustments that are based on a set of process parameters and single bias point measurements that are taken from the in-line wafer parametric data.

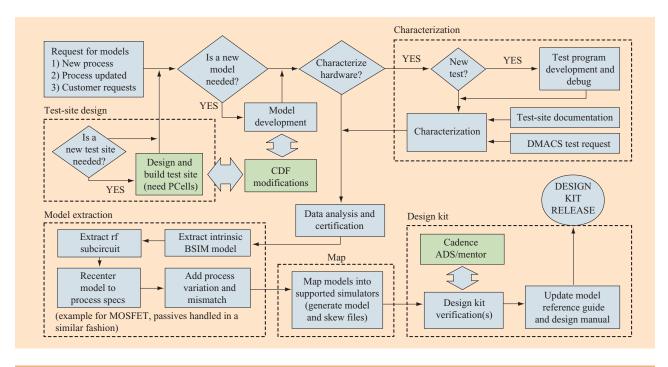

The overall flow of the steps of the compact model development process is illustrated in **Figure 11**. Note that model parameter recentering and the inclusion of the process distributions to enable full statistical simulation follow directly after parameter extraction, as shown in the lower left corner of the figure. Although the figure pertains to the use of the BSIM model in support of MOSFET devices, the overall development flow is applicable to all IBM SiGe and rf CMOS technology devices.

# HBT

Until the mid-1990s, the semiconductor industry relied almost exclusively on the simulation program with integrated circuit emphasis (SPICE) Gummel-Poon (SGP) model for BJT circuit design. The model included effects important in analog design not found in the earlier Ebers-Moll-type models such as low-current nonidealities and high injection effects, and replaced the underlying physical model with equations based on the more complete integral charge-control relation (ICCR) [25]. But recently, with the revival of BJT and HBT technology for high-speed communications and rf applications, the SGP model was found to be increasingly inadequate and had to be revised to include more accurate modeling of the physical effects found in high-speed devices operating at high current densities. These effects include better Earlyeffect modeling (output conductance), quasi-saturation,

150

Figure 11

Overall flow of the steps of the compact model development process.

avalanche multiplication, thermal self-heating, and accurate transit-time modeling.

This needed revision of the SGP model for modern bipolar transistors was addressed at the Bipolar/BiCMOS Circuits and Technology Meeting, which started a committee to establish a public-domain improved bipolar compact model. This resulted in the vertical bipolar intercompany (VBIC) model formally presented in 1995 [17]. The VBIC model was physically based on the same ICCR that underlies the SGP model, but also included several additional model elements built around the core model. Additionally modeled effects include a parasitic pnp, selfheating, bias-dependent Early voltages, temperature scaling, a Kull-based model for quasi-saturation, and additional parasitic capacitances found in aggressively scaled modern devices. Also, in contrast to the SGP model, which used separate equations to model the transistor in each operating regime, the VBIC model was constructed with continuous smooth functions over all bias ranges for enhanced numerical stability. However, in an effort to keep a partial backward compatibility with the SGP model, the extra physical modeling structure increased the internal model node count from 3 to 7 and approximately doubled the required number of parameters to 70. The primary recognized inadequacy of the VBIC model revolves around the poor implementation of the

Kull model for device operation in strong quasi-saturation [26].

IBM SiGe technology design kits currently integrate both SGP and VBIC models for the SiGe HBT, but the rapidly growing suite of SiGe HBT technologies, with an extremely wide range of device performance targets, has placed additional questions on the validity of the physical assumptions used to derive the standard VBIC model. For example, in IBM SiGe technologies, the model must correctly predict the strong quasi-saturation and avalanche breakdown of the IBM SiGe 5PA high-voltage (6.4-V) HBT, as well as model non-quasi-static transport and ac current crowding of the recently announced 200-GHz eight-generation SiGe HBT. This is a difficult task for even the most complex models.

For these reasons, two additional HBT models, HiCUM and MEXTRAM, are currently under evaluation by IBM and the Compact Modeling Council as potential successors to the current VBIC standard. The HiCUM (High CUrrent transistor Model), developed at Ruhr University in Bochum, Germany, and first implemented in 1981, was developed initially for design of high-speed ECL circuits that operate at high current densities [27]. Based on the ICCR, the model was extended to include SiGe HBT structures with the General Integral Charge-Control Relation (GICCR) that now provides the physical basis for the model [28]. A most important impact of the GICCR is

151

**Table 2** Comparison of modeled physical effects and requirements for current HBT compact models. Adapted from [30], with permission; © 2001 IEEE.

|                        | SGP | VBIC         | HiCUM                  | MEXTRAM                |

|------------------------|-----|--------------|------------------------|------------------------|

| HBT/SiGe modeling      | _   | /            | //                     | <b>//</b>              |

| Quasi-saturation       | _   | $\checkmark$ | $\checkmark\checkmark$ | $\checkmark\checkmark$ |

| $f_{_{ m T}}$ modeling | _   | $\checkmark$ | $\checkmark$           | <b>//</b>              |

| Self-heating           | _   | $\checkmark$ | $\checkmark$           | $\checkmark$           |

| Substrate modeling     | _   | $\checkmark$ | $\checkmark$           | _                      |

| $\beta$ -E breakdown   | _   | $\checkmark$ | $\checkmark$           | _                      |

| Parasitic pnp          | _   | $\checkmark$ | _                      | - 🗸                    |

| No. of internal nodes  | 3   | 7            | 4                      | 5                      |

| No. of parameters      | 35  | 80 +         | 90 +                   | 67                     |

the implementation of weighting factors that account for the change in mobility and intrinsic carrier concentrations affecting the charge storage in the neutral regions affected by the high Ge content. Other important effects present in the HiCUM model include accurate modeling of the quasi-saturation region and extensive physical description of bias-dependent transit times and non-quasi-static behavior.

The MEXTRAM (Most EXquisite TRansistor Model) model, developed and implemented at Phillips [29], is also based on the ICCR of the SGP model. The modeling of the collector epilayer differentiates the MEXTRAM model from VBIC. MEXTRAM extends the modified Kull model by adding the effects of velocity saturation in the collector at high current densities, correctly predicting quasi-saturation and the onset of Kirk effect. This collector model is also implemented in a smoother mathematical description that is beneficial to the calculation of higher-order derivatives, important for harmonic distortion analysis. MEXTRAM, like HiCUM, has implemented additional parameters to take into account bandgap grading in SiGe devices, as well as an extra parameter to model the changes in  $I_b$  due to neutralbase recombination.

Table 2 contains a brief summary of the physical effects included in each of the BJT models and a comparison of the number of internal nodes and model parameters required. The existing IBM SiGe design kits have implemented the VBIC model as the primary element within the npn subcircuit for technologies that typically include both high- $f_{\rm T}$  and high-breakdown types of devices. The weak avalanche effect in the VBIC model is based on the assumption that the peak E-field occurs at the base–collector interface, which is valid for the highly doped collector of the high- $f_{\rm T}$  device. For the lower-doped collector of the high-breakdown npn, the peak E-field occurs at the collector–substrate interface. To account for this difference and to overcome this limitation in the VBIC model, the IBM model topology was modified to

move the physical location of the weak avalanche current generator inherent in the VBIC model for high-breakdown devices. The standard VBIC avalanche current is still used for high- $f_{\rm T}$  devices. While there are distinct differences in the performance of these devices, a single model file has been used with an input parameter that is passed in from the circuit netlist to specify which device type is being modeled. This is another way in which the overall modeling methodology tries to reflect the physical realities of the devices, since it allows for commonality in many of the key calculations and model parameters that are derived from the basic process flow.

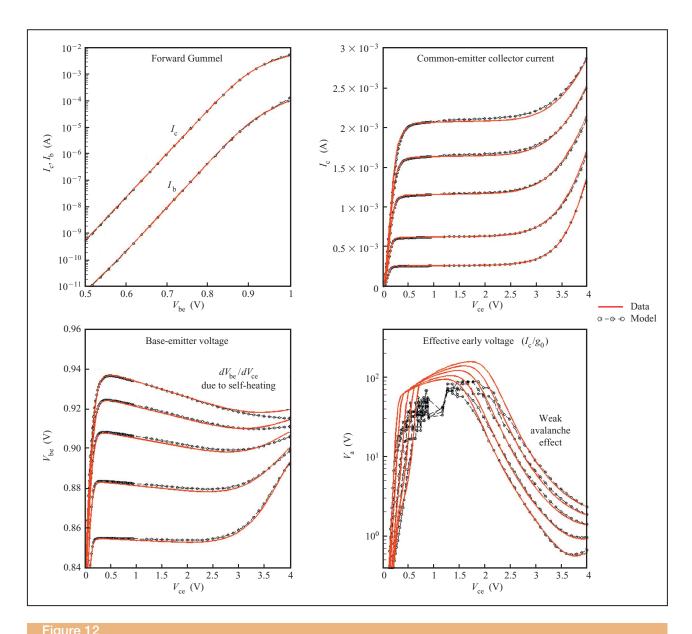

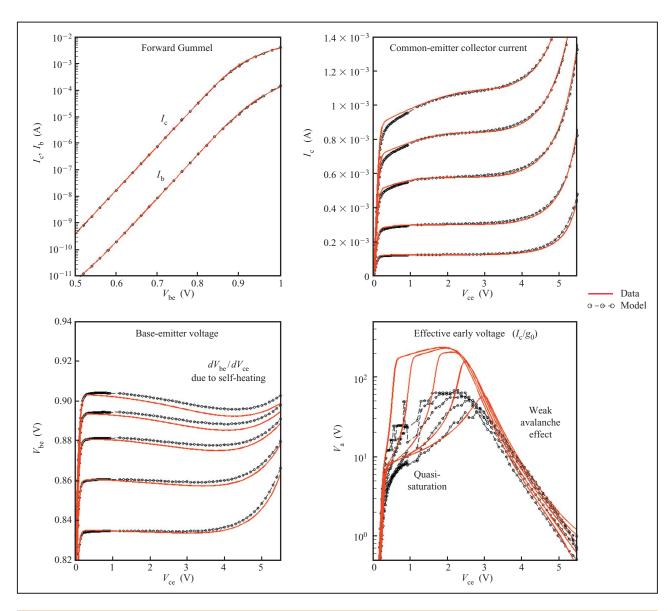

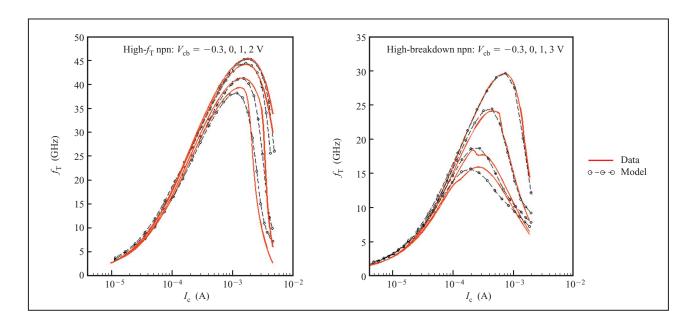

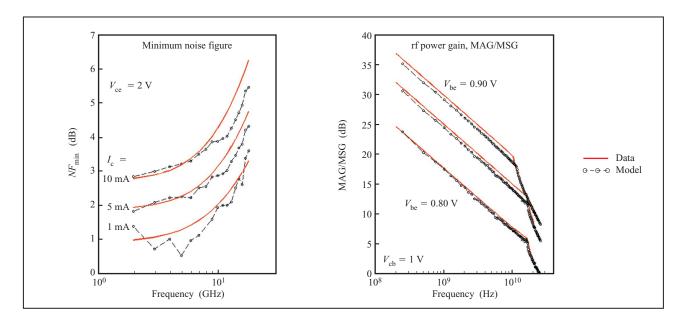

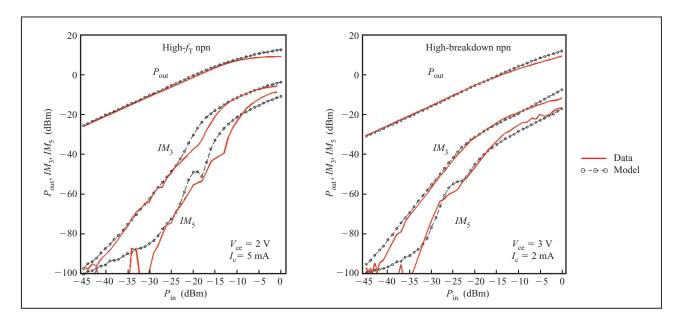

Typical model-to-hardware correlation plots help to illustrate the success achieved in using the VBIC model to represent the various device characteristics of the SiGe HBT npn devices. The dc forward Gummel and output curves for the high- $f_{\rm T}$  npn device in the IBM 0.25- $\mu$ m SiGe process are shown in Figure 12, and for the highbreakdown npn device in the same process in Figure 13. The figures show the effects of self-heating, weak avalanche current, and the difference in the quasisaturation behavior of the two types of devices. Note that the model parameter extraction process begins with fitting of these dc characteristics. Once initial parameter values associated with the basic dc characteristics have been determined, extraction and model optimization continues using S-parameter, noise-figure, and large-signal measurements. Figure 14 shows the  $V_{\rm cb}$  dependence of  $f_{\rm T}$ vs.  $I_c$ , for both high- $f_T$  and high-breakdown devices, as extrapolated from S-parameter data at a fixed frequency using a simple gain-bandwidth product. Examples of minimum noise figure and rf power gain for the high- $f_{\rm T}$ npn are included in Figure 15. Finally, the initial results of the model vs. large-signal data correlation can be seen in Figure 16 for both device types.

Another key aspect in the development of the SiGe HBT models is the inclusion of extensive geometric scaling equations. While the more advanced BSIM-based MOSFET models have multiple parameters to represent short-channel or narrow-channel effects, the built-in scaling of VBIC is not adequate to support the range of layout geometries offered by the IBM SiGe design kit parameterized cells (PCells). The use of a single "area" factor to scale all of the current density, capacitance, and resistance parameters does not provide the flexibility necessary to accurately differentiate the dimensional changes in the various regions within the device. Separate calculations are included as a part of the subcircuit model to determine the proper effective dimensions, such as intrinsic and extrinsic junction areas or perimeters, to generate the final set of VBIC parameters, given a specific emitter size and device layout configuration.

Modeling  $V_{\rm be}$  and  $\beta$  mismatch of the SiGe npn devices is important for providing designers with information

DC characteristics of high- $f_T$  npn SiGe HBT fabricated using the IBM 0.25- $\mu$ m SiGe process.

necessary to assess performance in many typical small-signal analog applications such as high-speed A/D converters, bandgap voltage references, and differential circuits. The scaling equations as implemented also include statistical distributions to represent low-current  $V_{\rm be}$  mismatch as a decreasing function of increasing emitter area. Another factor is defined to account for the increase in  $V_{\rm be}$  mismatch that is observed as the current bias increases. A third distribution is used to represent the  $\beta$  mismatch, which is also modeled as a function of emitter area.

# **MOSFET**

The technical development of the MOSFET compact model has closely followed the increased demands placed on it by circuit designers. As MOSFET-based designs have evolved from purely digital to analog and to analog rf, corresponding MOSFET models have become increasingly more complex.

Traditionally, the first MOSFET model was the so-called digital model. In the development of the digital model, the primary focus was on accurately predicting the on-current ( $I_{\rm ds}$  at  $V_{\rm gs}=V_{\rm ds}=V_{\rm dd}$ ) and the switching

Figure 13

DC characteristics of high-breakdown npn SiGe HBT fabricated using the same IBM process.

speed of the device. Issues such as scalability and  $I_{\rm ds}$  accuracy near threshold were not addressed, since the focus was on minimum-channel-length (i.e., fast) devices that were either on or off. This model served as a good introduction point because the equations comprising the model had their basis in semiconductor device physics. This is in contrast to an empirical model where the equations may be composed of splined polynomials whose coefficients have been optimized to provide the best fit between the measured data and the simulation results. As CMOS technologies have progressed into the submicron region, the limitations of the existing "digital" models

have become much more apparent. The following list highlights many of the physical effects that the existing models are unable to predict [31]:

- Short- and narrow-channel effects on threshold voltage.

- Effects of nonuniform doping.

- Mobility reduction due to vertical field.

- Bulk charge effects.

- Velocity saturation effect.

- Drain-induced barrier lowering (DIBL).

- Channel-length modulation (CLM).

- Substrate-current-induced body effect (SCBE).

154

Associated  $f_{\rm T}$  characteristics vs.  $V_{\rm cb}$  for high- $f_{\rm T}$  and high-breakdown npn devices.

Figure 15

Associated minimum noise figure and rf power gain for high- $f_T$  npn device.

- Subthreshold conduction.

- Source/drain parasitic resistance.

The inability of the digital model to deal with these effects results in a model that does not scale with channel

length and/or width. In fact, because of the operating region and voltage bias dependencies of these effects, the drain current is not accurately modeled even for a fixed-dimension device. Even worse, the derivatives of the drain current ( $g_{\rm m},\,g_{\rm ds},$  and  $g_{\rm mbs})$  can become discontinuous

Figure 16

Associated large-signal characteristics for high- $f_{\rm T}$  and high-breakdown npn devices;  $Z_{\rm in}=Z_{\rm out}=50~\Omega$ .

owing to the "splining" approach that has been applied to the digital model equations. This means that, in addition to the inherent inaccuracies, many analog circuit simulations do not converge to a result when these digital models are used. This results in a severe handicap for the analog designer whose designs depend upon an accurate representation of MOSFET drain current, gain  $(g_{\rm m})$  and output impedance  $(I/g_{\rm ds})$ .

Consequently, several attempts were made through the late 1980s and early 1990s to create an analog model. Of these, the Berkeley short-channel IGFET model (BSIM) and its successors are the most widely accepted and used. In developing the BSIM, a "start from scratch" approach was used that placed an emphasis on three areas of importance:

- 1. *Device physics* The robustness of a compact device model can usually be traced to how much of its fundamental basis is tied to the physics of the device.

- 2. Scalability Width and length scalability is incorporated into nearly all of the equations that compose the structure of the BSIM model. This enables a single model, and thus a single model parameter set, to be used to predict the performance of a device over a wide range of geometries.

- 3. Robustness The equations used to represent the various effects were combined in such a way as to create one continuous expression for  $I_{\rm ds}$ . This eliminated the discontinuous derivative problems found in many of the earlier MOSFET models mentioned

above. From a circuit simulation standpoint, the robustness of the BSIM model can also be tied to its formulation as a charge-conserving model. In a charge-conserving model, the nodal equations are expressed in terms of charge instead of capacitance. These equations are considered balanced when all of the charges sum to 0. Capacitance-based models are not charge-conserving because capacitance is an incremental quantity that accurately predicts the change in charge versus voltage for only infinitesimally small changes in voltage [32]. The development of the BSIM model to the BSIM3v3 model that is in widespread use today is well documented [33].

The MOSFET model used by IBM in its SiGe BiCMOSand rf CMOS-based design kits is the third-generation

BSIM3 model from U.C. Berkeley (BSIM3v3.2). Although

its name implies that it is a continuation of the earlier

BSIM and BSIM2 models, it is really a total rewrite from

scratch. The goal here was to introduce more accurate

physics-based equations into the model in a way that was

still mathematically robust from a simulator standpoint.

In general, the best compact models are those whose

representative equations have their basis in the physics

behind the devices they are representing. These models

tend to scale better and to be more accurate at biases and

geometries outside the bounds being measured. This was

the approach used in developing the BSIM3 model. Where

possible, the equations used to represent the effects

156

listed above were based on the solution of Poisson's 2D equation for the distribution of charge across the channel of a MOSFET. As a result, the fundamental equations for threshold voltage, mobility, and velocity saturation tended to be very physically based.

The semi-empirical nature of the BSIM model dictates that a combined extraction and optimization approach should be used to extract the BSIM parameter values. First, the physical "process" parameters such as oxide thickness, base threshold voltage, channel length and width, and series resistance are extracted from either single- or multi-device measurements. Next, an optimization approach is used to produce a set of BSIM parameters that minimize the model-to-hardware error across the device size, bias range, and temperature space being fit. To date, two different optimization approaches have been used. The more "traditional" approach is the so-called local optimization method. In local optimization, parameters are fitted, a few at a time, by varying their value to minimize the model-to-hardware difference over a very specific range of device sizes and operating regions in which the effects of these parameters are dominant. This "local" optimization approach is preferred over the standard "global" optimization approach because it tends to avoid the local minima phenomena that can occur when very large number of parameters are optimized over a very large space. The second optimization method used more recently at IBM is a genetic algorithm (GA)-based approach [34]. The genetic algorithm avoids using the "stair-climbing" optimization approach that causes other global optimization approaches to become trapped in local minima. The GA is able to optimize all of the BSIM parameters concurrently by means of a "fitness function" that weights its target criteria accordingly. It is very CPUintensive, but minimizes the human effort needed to extract the models. The key to its success lies in the definition of the fitness function.

Length and width scalability have been built into the threshold voltage equation, the effective mobility equation, and most of the other fundamental equations behind the BSIM model. However, if the physical mechanisms underlying the behavior of the device do not match those of the scaling equations, the models may not scale across the entire geometry range being offered in a given technology. To circumvent this problem, a technique known as "binning" has been incorporated into the BSIM model. As its name implies, binning allows the channel width/length geometrical space to be broken up into several regions, or bins. For example, if a model is broken down into three length regions and three width regions, it is said to be composed of nine bins  $(3 \times 3)$ . This approach enables the modeler to extract nine separate BSIM parameter sets to cover the entire width/length space. Since each of the nine BSIM parameter sets only

has to cover its width/length region, the scalability requirements placed on the intrinsic physics-based scaling are relaxed. The downside of using this approach is the increased development overhead associated with creating and maintaining binned models. Although such models are not currently in use in the effort described here, they may be useful in the future, as decreasing channel lengths continue to challenge the intrinsic scalability of the BSIM model.

When designers place a MOSFET device of a given width/length ratio in the schematic, a level of confidence is obtained that the  $I_{ds}$ ,  $g_{m}$ , or  $g_{ds}$  values predicted by the model are valid for that device. If the device they are using has an rf PCell (described below), they have confidence that the device parasitics are also represented accurately within the model. If designers are using a standard "digital" MOSFET PCell, they must rely on an estimation of device parasitics that have been incorporated into the design kit. To predict the source/drain (S/D) parasitic capacitance, an estimate of the area and perimeter of both the source and drain is passed to the S/D diode model contained within the core BSIM model subcircuit. As with any estimate, some assumptions must be made. To estimate the size of the S/D diffusions, we make the following assumptions: 1) Contact sizes and spacing are at a minimum, thus enabling the smallest possible diffusion. 2) In the event of an even number of gate "fingers," there will be one less drain diffusion than source diffusion. 3) Applied photoresist bias is nominal [35]. Within the SiGe BiCMOS 6HP design kit, the designer has the choice of two different parasitic estimation approaches. In the first approach, the S/D area and perimeter estimates are calculated in the Cadence component description format (CDF) associated with each schematic level device instance. The values of drain area (AD), drain perimeter (PD), source area (AS), and source perimeter (PS) are then passed into the device model. In the second approach, the values of AD, PD, AS, and PS are calculated in the device model itself. Each approach has its own advantages and disadvantages. Calculating the area and perimeter values in the CDF simplifies the model code and reduces overall simulation time, since the values are calculated once prior to netlisting. Calculating the area and perimeter in the model enables statistical process variation to be applied to the area and perimeter during Monte Carlo simulation and allows the user to sweep the channel length (or width) as a design variable during simulation and still have the estimated parasitics included.

In addition to increased focus on analog model accuracy, the BSIM generation of compact device models has also placed an increased focus on modeling noise. Prior to the use of BSIM, the noise contributions of a MOSFET were modeled as the standard kT/q thermal noise contribution. In BSIM, flicker noise (1/f noise), channel thermal noise,

Figure 17

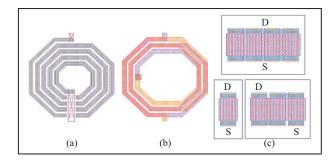

Example of an rf MOSFET PCell-based device layout.

induced gate noise, and the thermal noise associated with parasitic gate and diffusion resistances are all modeled.

At its conception, the IBM rf CMOS technology was intended to be a variation of the base IBM CMOS technology, which offered improved rf-quality models and extra front end of the line (FEOL) passives to give the rf CMOS designer an adequate "toolbox" of devices. RF CMOS is targeted at the cost-sensitive customers whose analog design points enable them to implement their designs in CMOS only. Typically, these design points include rf circuits with relatively little analog content or rf circuits that are well understood and have been implemented using bipolar devices in the SiGe BiCMOS technology.

From a MOSFET model standpoint, the needs of the rf CMOS analog designer are even more critical than the needs of the BiCMOS analog designer. In a BiCMOS technology, a designer would likely use a bipolar device in situations where high speed, high gain, and good matching are important. For an rf CMOS technology, this is not an option. This forces the rf CMOS designer to use more innovation in design—e.g., to use elaborate on-chip timing approaches to minimize signal latency and DSP approaches to "clean up" signal issues related to distortion.

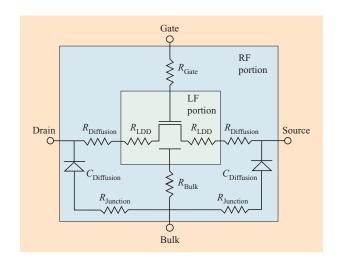

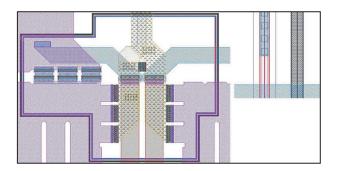

In concept, the transition from an analog model to an rfquality model is not really as big as that from a digital model to an analog model. From a designer's perspective, the rf model really involves extending the analog model accuracy from the low-frequency region into the rf region. At low frequencies, the capacitive load of the gate on the preceding circuit element is important. At high frequencies, the gate capacitance, channel resistance, and diffusion parasitics all combine to form a complex load on the prior stage. From an output impedance standpoint, a similar analogy can be made. At low frequencies, the output resistance is dominated by the channel resistance. At high frequencies, the S/D parasitics and bulk resistance contribute largely to the complex output impedance. This presents a unique problem to MOSFET designers. At low frequencies, the performance of the MOSFET can be adequately represented by modeling the intrinsic device, the overlap capacitance, and the S/D parasitic diode. This can be done because these effects are independent of device layout (as long as the number of fingers and multiplicity are known). At high frequencies, the layout cannot be ignored. The approaches used to wire to the gate and contact the substrate greatly affect the highfrequency performance of the device. This creates a problem for MOSFET designers: Without knowledge of the exact layout of the MOSFET, how can its highfrequency performance be modeled? Our answer is to provide designers with two MOSFET PCell layouts. The first is the standard "digital" layout, in which the designers are free to wire to the gate and to the substrate. The model provided with this device can be verified at lower frequencies. The second PCell is similar to the one shown in Figure 17. In this PCell, the gate wiring and substrate contact scheme are defined and controlled. The model provided with this device scales as a function of channel width, length, and number of "fingers" at both low frequency and high frequency. By using this layout and its associated rf model, designers can be certain that the rf model they are using represents the device they have designed. The purpose of this rf PCell is not to provide the highest-performance layout, but rather to provide a controlled device configuration that has been well characterized and modeled.

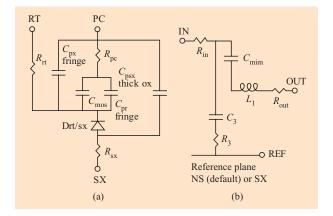

The substrate circuit defined in the model is critical to accuracy at high frequency. A comparison of S-parameter measurements for identically sized devices with varying substrate contact schemes has demonstrated two key points. First, the output impedance at the drain of the device can vary significantly depending upon the proximity of the substrate contact. Second, this variation can be represented accurately by using a model structure similar to the one shown in **Figure 18**. Note that the model parameters needed to model the substrate resistance effects are layout-dependent, as previously described. Therefore, a unique set of substrate network parameters must be used for the layout shown in Figure 17.

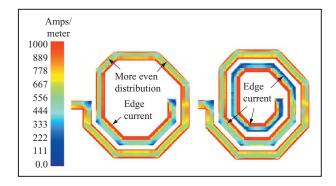

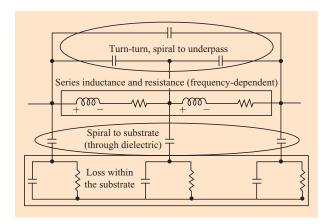

#### Inductors

Inductors are essential devices in many rf circuits (voltage-controlled oscillators, or VCOs, impedance-matching networks, etc.). Their on-chip implementation decreases

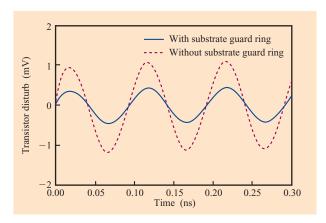

packaging parasitics, reduces the number of pins required, makes possible more compact circuit boards, and paves the way for system-on-a-chip (SoC) solutions. Any design flow for rf applications would be incomplete without adequately optimized and modeled on-chip inductors [36].