# (Ba,Sr)TiO<sub>3</sub> dielectrics for future stacked-capacitor DRAM

by D. E. Kotecki J. D. Baniecki

H. Shen

R. B. Laibowitz

K. L. Saenger

J. J. Lian

T. M. Shaw

S. D. Athavale

C. Cabral, Jr.

P. R. Duncombe

M. Gutsche

G. Kunkel

Y.-J. Park

Y.-Y. Wang

R. Wise

Thin films of barium-strontium titanate (Ba,Sr)TiO<sub>2</sub> (BSTO) have been investigated for use as a capacitor dielectric for future generations of dynamic random-access memory (DRAM). This paper describes progress made in the preparation of BSTO films by liquid-source metal-organic chemical vapor deposition (LS-MOCVD) and the issues related to integrating films of BSTO into a DRAM capacitor. Films of BSTO deposited on planar Pt electrodes meet the electrical requirements needed for future DRAM. The specific capacitance and charge loss are found to be strongly dependent on the details of the BSTO deposition, the choice of the lower electrode structure, the microstructure of the BSTO, the post-electrode thermal treatments, BSTO dopants, and thin-film stress. Films of BSTO deposited on patterned Pt electrodes with a feature size of 0.2  $\mu$ m are found to have degraded properties compared to films on large planar structures, but functional bits have been achieved on a DRAM test site at  $0.20-\mu m$  ground rules. Mechanisms influencing specific capacitance and charge loss of BSTO films are described, as are the

requirements for the electrode and barrier materials used in stacked-capacitor structures, with emphasis given to the properties of the Pt/TaSi(N) electrode/barrier system. Major problems requiring additional investigation are outlined.

# 1. Introduction

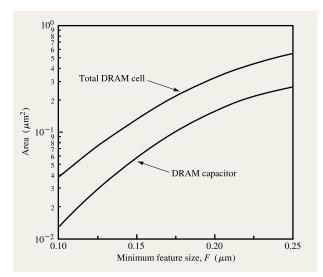

The density of dynamic random-access memory (DRAM) has increased by a factor of  $4\times$  every three years during the past 25 years, and this trend continues today. This remarkable increase in density has been brought about by advances in various areas of technology, including lithography, dry patterning, and thin-film deposition techniques, and by improvements in the DRAM architecture resulting in a more efficient cell utilization. **Figure 1** shows the expected size of a DRAM cell for future generations of DRAM [1]. As the lithographic feature size decreases from 0.25 to 0.10  $\mu$ m, the area of the DRAM cell is expected to decrease by a factor of more than  $10\times$ .

Since DRAM cells contain a single transistor and capacitor and each capacitor must be isolated from adjacent capacitors in the array, only a fraction of the cell area can be occupied by the capacitor. An estimate of the

Copyright 1999 by International Business Machines Corporation. Copying in printed form for private use is permitted without payment of royalty provided that (1) each reproduction is done without alteration and (2) the Journal reference and IBM copyright notice are included on the first page. The title and abstract, but no other portions, of this paper may be copied or distributed royalty free without further permission by computer-based and other information-service systems. Permission to republish any other portion of this paper must be obtained from the Editor.

0018-8646/99/\$5.00 © 1999 IBM

Expected area of a DRAM cell and the area available for the capacitor as a function of the minimum feature size.

# Figure 2

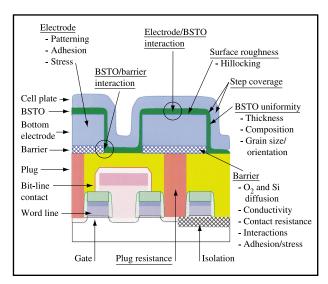

Schematic representation of a simple stacked-capacitor structure with the capacitor above the bit line.

area available for the capacitor is shown by the red line in Figure 1. Here, the capacitor was assumed to be rectangular in shape and separated from the adjacent capacitors by  $0.8\times$  the minimum lithographic feature size.

The minimum amount of charge that must be stored in the capacitor in order to obtain reliable operation of the DRAM is determined by the sensitivity limits of the sense amplifiers, parasitic capacitances, and alpha-particle considerations. This minimum charge has historically decreased by about a third per generation [2]. Similar decreases in operating voltage are expected for future DRAM generations, so that the required DRAM capacitance will remain nearly constant at 25–30 fF/cell. Achieving the required capacitance density while maintaining a charge loss of <10% after one second, corresponding to a current density of approximately 1 fA/cell, will be a major challenge in fabricating future generations of DRAM.

Higher capacitance density can be achieved by the use of 1) complex electrode structures providing a large surface area within a small lateral area; 2) thinner capacitor dielectrics; and 3) higher-permittivity capacitor dielectric materials. In general, increasing the surface area leads to increased complexity and hence increased cost; other papers in this issue discuss the limitations on the dielectric thickness of  $SiO_2$  and  $SiN_x$  (see for example [3, 4]).

Much work in recent years has focused on the development of high-permittivity materials for a DRAM capacitor. DRAM chips manufactured to date contain primarily capacitors utilizing a thin dielectric containing a mixture of silicon dioxide and silicon nitride sandwiched between two electrodes made of doped crystalline or polycrystalline silicon. Modifying this materials set will break a 25-year precedent in which long-term dielectric performance and reliability have been firmly established. Incorporating a high-permittivity material into a DRAM capacitor drives the need not only for new dielectric materials, but also for new electrode and barrier materials. Thin-film barium-strontium titanate (Ba,Sr)TiO<sub>2</sub> (BSTO), with a permittivity in the range 200-350 and a specific capacitance exceeding 125 fF/ $\mu$ m<sup>2</sup>, has emerged as the leading contender as a dielectric for future DRAMs.

This paper introduces the issues involved with integrating high-permittivity thin films of BSTO into a DRAM capacitor. The following section describes the capacitor structure. Section 3 focuses on electrode and barrier issues. Section 4 describes the deposition process for producing thin films of BSTO by liquid-source metalorganic chemical vapor deposition (LS–MOCVD). Sections 5 and 6 focus on the microstructure and electrical properties of Pt/BSTO/Pt capacitors. Conclusions and problem areas requiring additional investigation are described in Section 7.

# 2. Stacked-capacitor structure with (Ba,Sr)TiO<sub>3</sub> dielectrics

Various stacked-capacitor structures have been proposed for high-permittivity dielectrics. A simple stackedcapacitor structure, with the capacitor above the bit line, is illustrated in **Figure 2**. Here, the bottom electrode of the capacitor is connected to the transfer device through a conductive plug. A conductive barrier material is used to separate the electrode from the plug material to prevent electrode–plug interdiffusion and reaction, and to protect the plug against oxygen exposure during the deposition of the BSTO dielectric, which normally occurs in an oxygen environment at temperatures in the range of 450–700°C. The high-permittivity dielectric conformally coats the bottom electrode, and the counter electrode forms a plate which is common to an array of capacitors. The major issues which must be addressed when integrating BSTO dielectrics in this type of DRAM structure are also presented in Figure 2.

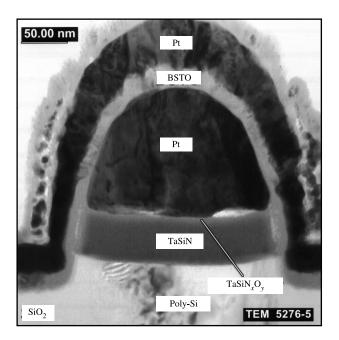

Figure 3 shows a cross-sectional transmission electron micrograph (TEM) of a Pt/BSTO/Pt stacked-capacitor structure, similar to that illustrated in Figure 2. Here, the minimum feature size is 0.2  $\mu$ m. The structure consists of a 250-nm-thick Pt bottom electrode on a 75-nm barrier of TaSiN, over a doped polycrystalline silicon plug embedded in a TEOS dielectric. The BSTO thickness is 27 nm, and the plate electrode is a 50-nm film of Pt. The barrier and electrode layers are deposited by physical vapor deposition (PVD), while the BSTO dielectric is deposited by MOCVD.

The bottom Pt electrode is patterned using dry etching with a hard mask, such as Ti, TiN, or SiO<sub>2</sub>. After the bottom Pt electrode is etched, the remaining hard mask is removed and the TaSiN barrier layer is simultaneously etched to isolate the individual Pt electrodes. The etch rate of the hard mask is higher than the etch rate of TaSiN during the mask-removal step. As a result, the remaining hard mask is removed quickly and the bottom Pt electrode itself acts as a mask during most of the TaSiN-layer etch. Because of the low selectivity of Pt to TaSiN, corner rounding and erosion of Pt occur, leading to a curved shape of the bottom Pt electrode.

The BSTO film is amorphous on the surface of the TaSiN barrier but crystallized on the Pt surface. Microprobe analysis indicates that the amorphous BSTO layer has a higher Ti concentration than the crystallized BSTO film, but no variation in the BSTO composition can be detected along the Pt electrode. The interaction of the BSTO and the barrier layer reveals a drawback to this structure, and it will be beneficial to recess the barrier into the plug or use a spacer to cover the TaSiN surface to avoid direct exposure of the TaSiN to the BSTO film [5, 6].

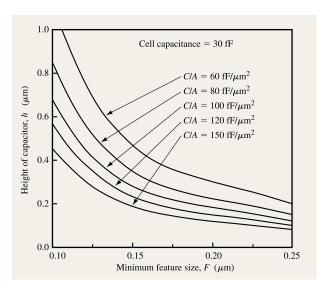

The required height of such a simple stacked-capacitor structure as a function of the minimum feature size and specific capacitance of the dielectric layer is shown in **Figure 4**. Here, the structure was assumed to utilize the area for the capacitor described by the curve in Figure 1, and the bottom electrode was assumed to have vertical sidewalls. Only the surface area on the sides of the

# Figure 3

Cross-sectional TEM image of a stacked-capacitor structure with a BSTO dielectric, Pt electrodes, and a TaSiN barrier layer. The minimum feature size is 0.2  $\mu$ m, and the BSTO dielectric thickness is 27 nm.

# Figure 4

Required height of the bottom electrode in a stacked-capacitor structure as a function of the minimum feature size and the specific capacitance of the dielectric layer.

**Table 1** Candidate materials which can be used as electrodes for BSTO and other high-permittivity dielectrics. Preparation method, permeability to oxygen, work function, and suitability for patterning into small features are indicated.

| Electrode<br>material      | Deposition<br>methods | Permeability<br>to oxygen | Work function<br>(eV) | Dry etch       |

|----------------------------|-----------------------|---------------------------|-----------------------|----------------|

| Pt                         | PVD, CVD              | High                      | 5.6-5.7               | Difficult      |

| Ir                         | PVD                   | Moderate                  | 5.0-5.8               | Difficult      |

| Ru                         | PVD                   |                           | 4.7                   | Easy/dangerous |

| Pd                         | PVD                   | Oxidizes readily          | 5.1-5.6               | Difficult      |

| IrO,                       | Reactive sputtering   | Low                       |                       | Difficult      |

| $Ru\overset{\circ}{O}_{2}$ | Reactive sputtering   | Low                       |                       | Easy/dangerous |

**Table 2** Candidate materials which can be used as a conductive plug between capacitor and the transfer device and their resistivity.

| Plug material     | Resistivity $(\mu\Omega	ext{-cm})$ | Reactivity<br>with Pt | Oxidation<br>resistance |

|-------------------|------------------------------------|-----------------------|-------------------------|

| Doped polysilicon | 500                                | High                  | Good                    |

| W                 | 10                                 | Low                   | Poor                    |

| WSi <sub>x</sub>  | 60                                 | High                  | Good                    |

capacitor is considered in this calculation. As can be seen, to keep the height of the capacitor below 0.5  $\mu$ m as the minimum feature size approaches 0.1  $\mu$ m, a specific capacitance approaching 150 fF/ $\mu$ m<sup>2</sup> is required.

# 3. Electrode and barrier properties

Most integration schemes for perovskite dielectrics use noble-metal or noble-metal-oxide electrodes in combination with a deposited diffusion-barrier material at the electrode/plug interface. In this section we briefly survey electrode and barrier materials under consideration for use with these dielectrics, and focus on the properties of the TaSiN barrier used with Pt electrodes.

Table 1 lists materials potentially suitable for use as electrodes with BSTO and perovskite dielectrics, along with some of their relevant properties. Patterning of Pt (and Ir) electrode materials is complicated by the absence of any low-temperature readily formable volatile etch products. Pt is typically patterned by reactive ion etching (RIE) using a Cl-based chemistry and a patterned hard mask. Physical sputtering is believed to be the dominant etch mechanism when conventional dry-etching techniques are used. Fence-free Pt etching can be achieved with a Pt profile angle close to 70°, as shown in Figure 3. Here, the SEM image is taken after removal of the remaining TiN hard mask; the Pt thickness is 250 nm and the material underlying Pt is SiO<sub>2</sub>.

The diffusion barrier must prevent plug oxidation and electrode/plug reactions and must remain conductive after the deposition and processing of the BSTO dielectric. The degree of oxidation resistance and oxygen diffusion-barrier

function required of the diffusion-barrier material clearly depends on the severity of the oxygen exposure associated with the deposition and post-electrode anneals of the BSTO capacitor.

The choice of stacked-capacitor structure is also a factor. In the simple stacked-capacitor structure, the side of the barrier is directly exposed to the oxygen processing ambient, whereas in structures with a recessed barrier [5] or where the side of the barrier is covered with an insulating or noble-metal [6] layer, the barrier is primarily exposed to oxygen diffusing through the electrode grain boundaries [7].

The oxidation resistance required of the barrier material also depends on the properties of the barrier-material oxide that is formed. Some oxidation may be tolerable if the barrier oxide is not too resistive, but oxidation through the entire thickness of the barrier indicates that the barrier is not protecting underlying structures from exposure to oxygen. Finally, the demands on the barrier material also depend on the choice of electrode and plug materials. For example, an oxygen-permeable electrode material such as Pt would require a more oxidationresistant barrier than the less oxygen-permeable electrode material IrO<sub>2</sub>, and readily oxidizable plug materials such as W would be expected to be less tolerant to oxygen exposure than plug materials of doped polycrystalline Si. Some candidate plug materials are listed in Table 2 along with their properties.

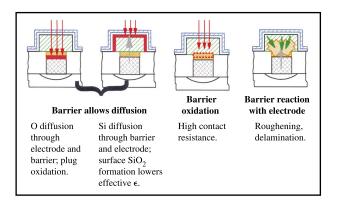

Another key requirement for the barrier material is that it prevent diffusion of plug material and/or silicon into the electrode. This is particularly important for plug materials of potentially "silicon-contributing" materials such as  $WSi_x$  or doped polycrystalline Si, which can react with noblemetal electrodes to form noble-metal silicides. In addition to forming a silicide, silicon may also diffuse to the electrode surface to form an  $SiO_2$  layer which will lower the overall capacitance. These various barrier failure modes are illustrated in **Figure 5**.

Most candidate barrier materials are introduced to the structure as deposited layers. Some representative barrier materials are listed in **Table 3** and consist mostly of various metal nitrides and metal silicon nitrides. More

**Table 3** Candidate materials which can be used as a barrier layer between the lower electrode and the conducting plug in a stacked-capacitor DRAM structure with a BSTO dielectric layer. These films can all be deposited by reactive ion sputtering.

| Barrier<br>material | Processability | Resistivity $(m\Omega\text{-cm})$ | ,         |  |

|---------------------|----------------|-----------------------------------|-----------|--|

| TiN                 | Easy           | 0.2                               | Poor      |  |

| TaN                 | Easy           |                                   | Poor      |  |

| TiAlN, TaAlN        | Moderate       |                                   | Good      |  |

| TaSiN               | Easy           |                                   | Excellent |  |

extensive listings can be found elsewhere [8]. Barriers used with doped polycrystalline Si plugs typically include a metal silicide layer at the barrier/plug interface to lower contact resistance (for example, the silicide TiSi<sub>2</sub> with the barrier TiN).

Barriers incorporated into the device structure in the nonrecessed geometry are typically patterned by RIE. With this patterning method, the barrier and electrode are perfectly aligned, since they are patterned in the same alignment step with the same hard mask. Barriers having the recessed geometry are typically patterned by planarization and self-aligned to recessed plugs. This self-aligned feature is advantageous in cases where a misaligned electrode does not completely cover an underlying plug, since the barrier material will be correctly in place over the plug even when the electrode is not. *In-situ-*formed barriers, a less explored alternative to deposited barriers, also have this self-aligned feature [9].

TaSiN is currently regarded as one of the more promising barrier materials [10–12]. Unlike the other barrier materials listed in Table 2, TaSiN remains amorphous (and thus free of fast-diffusion-path grain boundaries) over a wide range of compositions. Depending on the exact application, the TaSiN composition can be optimized for oxidation resistance, barrier properties, or low resistance. Increasing film nitrogen content typically improves Si diffusion-barrier performance but lowers conductivity, and decreasing Ta content typically improves barrier oxidation resistance.

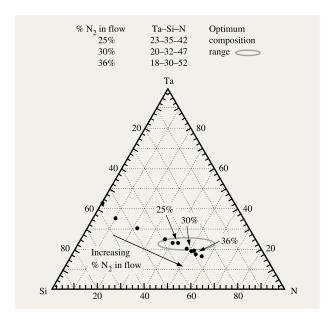

The optimum TaSiN composition range for advanced dielectric barrier applications is indicated by the circled region on the ternary phase diagram of **Figure 6**, where the dots show compositions obtainable by reactive sputtering in Ar/N<sub>2</sub> with a TaSi<sub>2</sub> target. Resistance data for TaSiN films deposited on insulating substrates are given in **Table 4** for various compositions of TaSiN. Resistances were measured before and after oxidation anneals at 650°C in atmospheric-pressure O<sub>2</sub> ambients. As-deposited film resistance clearly increases with film nitrogen content, and the resistance of the annealed films clearly increases with oxygen exposure. However, it can

# Figure 5

Schematic representation showing the possible failure modes of the barrier during thermal processing in an oxidizing ambient.

# Figure 6

Ternary phase diagram showing the range of TaSiN compositions investigated for conductivity and oxidation properties. The compositions in the circled region were found to have the optimal compositions for a barrier application.

be seen that all films remain below 100 k $\Omega$ / $\square$  even after 30-min anneals in an O<sub>2</sub> ambient.

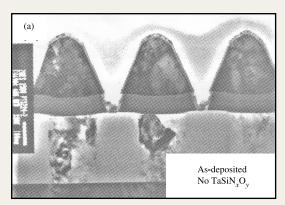

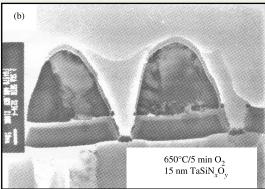

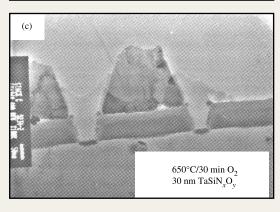

**Figure 7(a)** shows patterned electrode structures as they would look immediately prior to BSTO deposition. The TaSiN is uniform in appearance and shows no oxidation. **Figures 7(b)** and **7(c)** show electrodes from the same wafer after 5- and 30-min anneals at 650°C in

TEM micrographs showing patterned electrode structures (a) on a TaSiN barrier prior to BSTO deposition; (b) after a 650°C anneal in oxygen at atmospheric pressure for 5 min; (c) after a 650°C anneal in oxygen at atmospheric pressure for 30 min. An oxidized surface layer is observed on the top and sides of the TaSiN after the anneals.

atmospheric-pressure  $O_2$  ambients. A uniformly thick oxidized  $TaSiN_xO_y$  layer is clearly present at the sides and top of the TaSiN structure after both anneals. The thickness of this layer is estimated to be about 15 nm for the 5-min anneal and 30 nm for the 30-min anneal. Its

**Table 4** Sheet resistance  $(k\Omega/\square)$  of TaSiN as a function of the composition and oxidation treatment. The samples are 15 nm TaSiN/SiO<sub>2</sub>/Si. All oxidation treatments were performed in an atmospheric pressure of oxygen.

| Ta-Si-N     | Oxidation treatment |                    |                         |  |

|-------------|---------------------|--------------------|-------------------------|--|

| composition | As-<br>deposited    | 650°C/5 min<br>RTA | 650°C/30 min<br>furnace |  |

| 23-34-44    | 1.2                 | 3.3                | 10                      |  |

| 20-30-49    | 2.4                 | 6.8                | 20                      |  |

| 18-30-52    | 12                  | 38                 | 94                      |  |

uniform thickness suggests that oxygen diffusion through the Pt electrode grain boundaries and/or along the Pt/TaSiN interface is extremely rapid. The oxidized layer can also be observed in the TEM micrograph of Figure 3. The absence of an oxidized layer at the bottom TaSiN surface indicates that the TaSiN is an excellent barrier to oxygen diffusion. However, these micrographs clearly indicate that lower-temperature processing or an improved electrode/barrier material is needed if the oxidized TaSiN, Q, material has a high resistance.

# 4. Deposition of BSTO by MOCVD

Because of the three-dimensional nature of the bottom electrode, metal-organic chemical vapor deposition (MOCVD) is the method of choice for preparing a conformal coating of BSTO. In this study, films of (Ba,Sr)TiO<sub>3</sub> are deposited by MOCVD using liquid delivery of the precursors. Ba(thd)<sub>2</sub>(4-glyme), Sr(thd)<sub>2</sub>(4-glyme), and Ti(O-iPr)<sub>2</sub>(thd)<sub>2</sub> are used as the organic sources. Liquid precursors are volumetrically mixed, metered, and delivered to a vaporization zone. The volumetric control of room-temperature liquids allows for high accuracy of mixing, provides precision in tuning the composition of the BSTO, and provides high wafer-to-wafer reproducibility [13].

The BSTO CVD reactor is a single-wafer warm-wall reactor, with the wall temperature maintained at 235°C. During deposition, the vaporized precursor liquid and oxidizer gases, consisting of O2 and N2O, are mixed and transported through a showerhead into the reaction chamber. The wafer is held at a temperature between 550°C and 700°C, and the total gas pressure is maintained at 0.5-1.0 Torr. The BSTO films are deposited at a rate of approximately 0.1 nm/s. The nominal composition of the BSTO films used in this study is  $Ba_{0.65}Sr_{0.35}Ti_xO_3$ , where x is slightly greater than unity, producing a Ti/(Ba + Sr) ratio of 1.02-1.05. The excess Ti is needed to produce BSTO films with low leakage. Film thickness and composition are measured by wavelength-dispersion X-ray fluorescence. The thickness nonuniformity is <5% across a 200-mm-diameter wafer, while the compositional

nonuniformity is within the accuracy of the WDXRF measurement at <0.25 at.%.

# 5. Microstructure of BSTO thin films

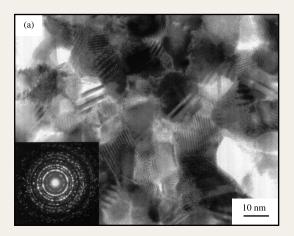

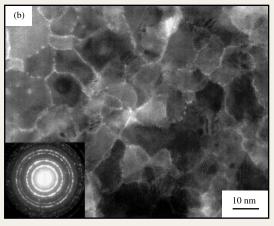

Two distinct microstructures are observed in the MOCVD-grown BSTO films. Examples of typical microstructures are shown in **Figure 8**. In Figure 8(a) the film has a strong (110) fiber texture, with the  $\langle 110 \rangle$ directions aligned normal to the substrate. In this planview image it can be seen that many of the grain boundaries are inclined in the film and thus have an appreciable twist component to their grain-boundary structure. The grains also contain many (111) twin boundaries. In Figure 8(b) the film has a strong (100) fiber texture, with the (100) direction aligned normal to the substrate. In this image it can be seen that the grain boundaries lie almost normal to the substrate; the grain boundaries are thus predominantly tilt boundaries. In several instances the dislocation arrays that make up the tilt boundaries are clearly visible in the image. The grain sizes in the two microstructures are similar, with an average grain size of about 15 nm. Measurements of the grain size of films having different thicknesses and cross sections through the films show that grains grow in a columnar fashion, keeping an almost constant diameter

Studies of microstructure development during early stages of deposition have shown that strong texture is present in the films even before BSTO grains have coalesced to form a continuous film. X-ray diffraction studies indicate that both (110) and (100) textures are present in the film at this stage of growth, and only in the later stages of film development does a dominant texture develop. This suggests that it is the factors that favor the preferential growth of one orientation over the other that control the final texture of the film. One proposal is that faceting of the BSTO on (100) planes could result in sideways spreading of the (110)-oriented grains, occluding the (100) grains. This would result in inclined grain boundaries in the film, as observed in the (110)-textured films. However, the processing factors that control the competitive growth between the two textures are poorly understood.

The underlying bottom Pt electrode has a strong (111) texture and a grain size of about 80 nm. Thus, many BSTO grains nucleate and grow on each Pt grain. Examination of the diffraction from individual grains shows that there was no preferred orientation relationship between the Pt and BST grains. High-resolution imaging of cross sections through the Pt BST interface shows that the BST perovskite lattice extends right up to the Pt grains, indicating that no intermediate phase formed at the electrode interfaces.

Figure 8

Plan-view TEM images of (a) (110)- and (b) (100)-textured 30-nm BSTO films.

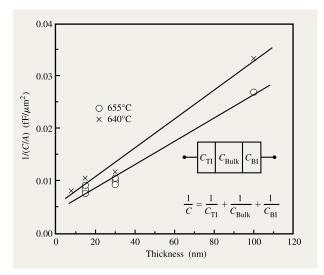

Measurements of the capacitance of different MOCVDgrown films indicate that texture and microstructural differences have only a secondary effect on the permittivity of the films. Other factors such as composition, electrode heat treatment, and stress tend to dominate the variations in capacitance that are observed from film to film. Studies of fine-grained barium titanate have recently shown that the grain boundaries can act as low-dielectric-constant capacitive elements in series with the capacitance of the grains [15]. However, in the columnar grain structure produced by the MOCVD process, most grain boundaries lie perpendicular to the electrodes and hence do not act in series with the BSTO grains. The main factor reducing the capacitance of the thin films is the electrode interface capacitance, which results in strong thickness dependence to the effective dielectric constant of the films (discussed in Section 6).

Plots of 1/(C/A) vs. thickness for MOCVD BSTO thin films deposited at substrate temperatures of 655°C and 640°C. The terms  $C_{\rm TI}$  and  $C_{\rm BI}$  respectively indicate top and bottom interfacial layer capacitance.

Leakage currents in the films are also dominated by the electrode interface properties. Small- and large-grained films show similar leakage currents. Grain boundaries in the films have only a minor effect on leakage. If anything, grain boundaries are thought to have the beneficial effect of depleting the grains of free charge and hence reducing the leakage of the films [15]. One effect of the grain structure that has been observed is that (100)-textured films show evidence of a time dependence to the leakage currents at high fields. This behavior is characterized by a steady decrease in leakage with time. In (110)-textured films, the effect is greatly reduced or absent. Preliminary studies of this phenomenon suggest that the time dependence is caused by charge trapping in the films, and it is possible that the effect grain texture has on this behavior is due to changes in trap density at the grain boundaries in the different films [16].

# 6. Electrical properties of BSTO thin-film capacitors

Before BSTO can be used as a storage-node dielectric in high-density DRAMs, electrical properties such as capacitance density, dielectric relaxation, leakage current, and resistance degradation must be characterized and understood. It may also be necessary to optimize the electrical properties by doping. Another important issue is determining the impact of these electrical properties,

which differ from those found in conventional silicon oxide/nitride dielectrics, on DRAM performance.

# • Specific capacitance

In addition to processing and microstructure considerations, the capacitance of BSTO thin films depends on film thickness, applied electric field, frequency, and temperature. Figure 9 shows the capacitance density plotted as 1/(C/A) vs. thickness for MOCVD BSTO thin films deposited at substrate temperatures of 655°C and 640°C. Pt electrodes were used for the electrical measurements. The decrease in capacitance is well described by a model in which an interfacial capacitance acts in series with the bulk of the film. Such a model predicts a linear relationship of 1/(C/A) vs. thickness, with the intercept corresponding to the effective capacitance of the interface. This model is seen to hold for films as thin as 8 nm, indicating that any interfacial layer present is thinner than 4 nm. The capacitance density in thin films is limited by the interfacial capacitance, making it an important factor in obtaining high-capacitance-density thin films. The origin of the interfacial layer is not currently understood. TEM images of the interface rule out the possibility that a thin layer of low-permittivity material is formed at the interface. An interfacial capacitance could result from depletion layers formed at the Pt/BSTO Schottky barrier, but photoemission measurements by Copel et al. [18] indicate depletion depths of 70 nm for MOCVD BSTO films; thus, as proposed by Waser [19], the films in this thickness range are completely depleted. Mechanisms other than a series-connected capacitance, such as finite size effects and stress, can also give rise to the behavior shown in Figure 9. BSTO thin films are under a biaxial stress due to different thermal expansion coefficients between the film and electrodes [20-21] and intrinsic deposition stress. A biaxial tensile stress shifts the Curie temperature  $(T_s)$  to lower values. Increasing stress in thinner films would then result in decreasing capacitance density with decreasing film thickness. Measurements of the stress in BSTO thin films on Pt electrodes reveal that the observed shift in  $T_c$ , determined from extrapolation of the Curie-Weiss behavior, for different thicknesses of BSTO is greater than that expected on the basis of stress alone. The postulation of a series barrier capacitance, probably between electrode and film, is required to account for the data. It has also been shown that residual porosity in the film cannot account for the large shift in  $T_{a}$ [22]. Such an interfacial layer may result from an intrinsic subpolarized layer ("dead layer") at the surface of a thin ferroelectric film [23], but further studies are needed to establish the precise cause.

T. M. Shaw, J. D. Baniecki, and R. B. Laibowitz, unpublished results.

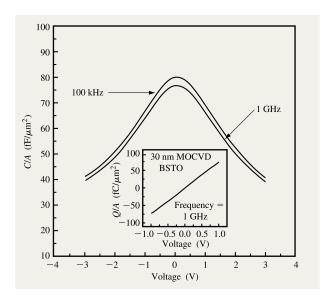

Capacitance density vs. voltage for 30-nm BSTO films with Pt electrodes at 100 kHz and 1 GHz. The inset shows the charge density vs. voltage obtained by integrating the small-signal *C*–*V* characteristic at 1 GHz.

Figure 10 shows the capacitance density vs. voltage for 30-nm BSTO with Pt electrodes at 100 kHz and 1 GHz. The variation of capacitance with voltage is not a thinfilm property, but an intrinsic property of the material resulting from the soft-phonon characteristics [24]. The field and temperature dependence of BSTO thin films is well described in terms of the Landau-Ginzberg-Devonshire theory of ferroelectrics [20]. Owing to the nonlinearity in capacitance, the available charge for DRAM applications is less than that determined at zero volts from the small-signal C–V characteristic. The available charge at a given capacitor voltage can be found by integrating the C–V characteristic, as shown in the inset in Figure 10. A slight nonlinearity is observed in the Q-V characteristic, resulting in less charge at a given voltage than would be obtained with a linear capacitor. For 30-nm MOCVD BSTO (assuming that  $V_{\rm CC} = 2 \text{ V}$  and half of  $V_{CC}$  is dropped across the capacitor) this results in about 4% less charge.

# • Dielectric relaxation

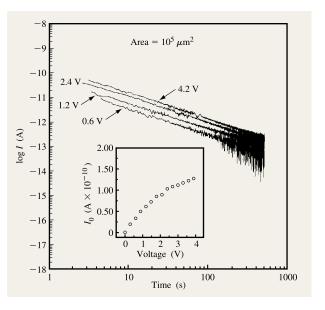

In addition to an instantaneous dielectric response, BSTO thin films have a slow polarization component which follows a power-law dependence in both the time  $[J_R(t)=J_0t^{-n}]$  and frequency  $(C_T-C_\infty=C_0f^{n-1})$  domains [25, 26]. **Figure 11** shows the depolarization currents for 100-nm MOCVD BSTO with Pt electrodes.

# Figure 11

Depolarization currents *I* for 100-nm BSTO films with Pt electrodes. The inset shows the voltage dependence of the magnitude of the relaxation currents.

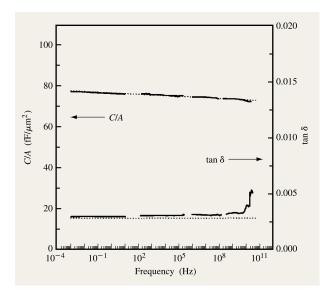

A voltage step technique [27] was used to record the charging and discharging transients, with the voltage being stepped in 0.1-V increments. A subset of voltages is shown in the figure for clarity. As shown in Figure 11, the depolarization currents follow a power-law time dependence known as the Curie-von Schweidler law [28], with an exponent slightly less than 1. The power-law time dependence of the relaxation currents has been measured to times as short as 10  $\mu$ s [26, 29]. The inset in Figure 11 shows the voltage dependence of the magnitude of the relaxation current after 1 s; for low voltages it is approximately linear, but a marked departure from linearity occurs at higher voltages. The relaxation currents are sensitive to doping [30], deposition temperature [31], annealing conditions [32], and stoichiometry [31]. Acceptor doping (Mn), lower deposition temperatures, and post-topelectrode annealing in forming gas (95% Ar 5% H<sub>2</sub>) were shown to increase relaxation currents, while a decrease in the relaxation currents was observed for films with increasing Ti concentration. Figure 12 shows the capacitance density and loss tangent for 30-nm MOCVD BSTO from 1 mHz to 20 GHz. The capacitance follows a power-law frequency dependence, as indicated by the dotted lines, over the entire measurement range. Because the frequency and time domains are related through Fourier transformation, the data in Figure 12 imply that

Capacitance density and loss tangent for 30-nm BSTO films from 1 mHz to 20 GHz.

the power-law relaxation currents extend back to the nanosecond regime of DRAM read/write pulses.

A power-law time dependence of polarization currents has been observed in a wide range of disordered solids, both crystalline and glassy [28]. Often the relaxation mechanism invoked to explain this behavior is the hopping of charge carriers between localized sites, where a distribution of hopping times, energies, or distances accounts for the distribution of relaxation times necessary for the power-law dependence. Localization of charge carriers can occur because of impurities, defects, disorder (Anderson localization), and electron-phonon coupling (polarons) [33]. The origin of localized charge carriers in BSTO thin films is currently under debate. Fukuda et al. [34] have proposed that electrons being thermally trapped/detrapped from oxygen vacancies (with a defect level of about 0.3 eV below the conduction band edge) in an interfacial depletion region is the origin of the phenomena. This explanation does not appear to apply to completely depleted MOCVD BSTO thin films, where the temperature dependence of the relaxation currents is different from that expected on the basis of thermal trapping/detrapping from a single defect level. Arrhenius plots of the magnitude of the relaxation currents reveal a break in the slope of  $log(J_R)$  versus reciprocal temperature. At high temperatures ( $T \gtrsim 300 \text{ K}$ ), activation energies of 0.3-0.76 eV as determined by the slope of the Arrhenius plot have been reported [31, 34, 35]; however, at low temperatures ( $T \leq 300 \text{ K}$ )

the activation energy drops to the meV range, and the relaxation currents persist down to 4.2 K [35]. Schumacher has suggested a model based on electronic hopping between localized states arising from impurity defects and disorder as the origin for the Curie-von Schweidler law in BSTO thin films [31]. At low temperatures the polarization currents result from hopping of carriers between localized states near the Fermi level, while hopping by carriers thermally excited into localized states near the conduction band edge occurs at higher temperatures.

# Leakage

Care must be taken when interpreting I-V data in BSTO thin films, since the slow polarization currents can mask the true leakage behavior. The best method of separating polarization and leakage currents is the use of a voltage step technique. The conduction mechanism for charge transport through metal–BSTO–metal thin-film capacitors is dominated by thermionic emission of electrons from the cathode [36]. This model is strongly supported by the dependence of the barrier height on the cathode metal work function and deposition conditions. The completely depleted nature of films less than about 140 nm leads to leakage currents that are relatively independent of film thickness. The temperature and field dependence for thermionic emission over a reverse-biased Schottky barrier are given by

$$J_{\rm L} = A * T^2 \exp\left(\frac{-W_{\rm B}}{kT}\right) \exp\left(\frac{q}{kT} \sqrt{\frac{q}{4\pi\varepsilon}E}\right),\tag{1}$$

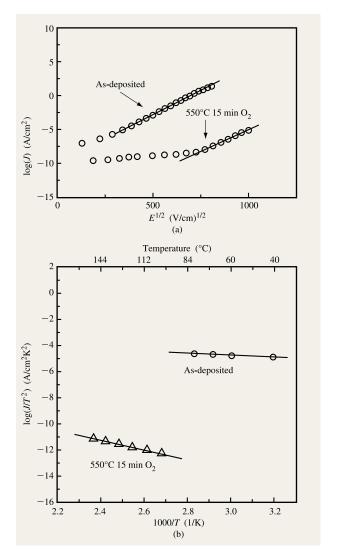

where  $A^*$  is the effective Richardson's constant, which incorporates carrier mobility, q is the electronic charge,  $\varepsilon$  is the permittivity (which may be different from the static permittivity), and k is Boltzmann's constant. If the conduction mechanism is thermionic emission, plots of  $\log(J/T^2)$  vs. 1000/T and  $\log(J)$  vs.  $E^{1/2}$  yield straight lines. The barrier height,  $W_{\rm R}$ , is then extracted from either the slope or the intercepts of the plots. Figures 13(a) and 13(b) show the field and temperature dependence of the leakage current for as-deposited and annealed 30-nm MOCVD BSTO with Pt electrodes. The sample was annealed at 550°C for 15 minutes in O<sub>2</sub>. In both films, as-deposited and annealed, good linear fits are obtained above a threshold voltage, even though the leakage through the films differs by as much as eight orders of magnitude. The leakage current at 1 V in the annealed film is  $1.7 \times 10^{-9}$  A/cm<sup>2</sup>. Below the knee in the Schottky plot, the field dependence is approximately ohmic. Dietz and Waser [37] have reported a similar low-field behavior in SrTiO, thin films and used the more general quantummechanical charge injection model of Murphy and Good to predict both the low- and high-field behavior and to

376

extend the theory to cover all temperature ranges. The data in Figure 13 yield a barrier height of about 0.64 eV in the as-deposited state and 1.22 eV after a rapid thermal anneal at 550°C for 15 minutes in O<sub>2</sub>. The lower barrier height in the as-deposited state may result from a high density of surface states in the as-deposited film, although further studies are needed to determine the precise cause. If the standard Schottky expression [Equation (1)] is used, parameters other than the barrier height extracted from the data analysis are typically unrealistic. As discussed by Simmons [38], the standard Schottky expression [Equation (1)] is valid for long electron mean free paths in the insulator. The condition of long electronic mean free paths in BSTO thin films may not be valid owing to a high density of surface states, traps in the film bulk, or strong electron-phonon coupling. A modified Schottky expression derived by Simmons, taking into account short mean free path, has been used which yielded better values for the Richardson constant and permittivity for sputter-deposited BSTO thin films on Pt electrodes [39]. The modified Schottky expression does not appear to yield better results for MOCVD BSTO thin-film capacitors with Pt electrodes after a post-top-electrode anneal in oxygen.<sup>2</sup>

# • Influence of dopants

The electrical properties of BSTO thin films, such as leakage and resistance degradation, are significantly affected by the addition of dopants. Nominally undoped MOCVD BSTO thin films are n-type. The addition of lower-valence substitutions, such as Mn or Fe on Ti sites. compensates the charge density in undoped films, leading to greatly increased depletion depths. Higher-valence substitutions, such as La on Ba or Sr sites, act as donors. Small doses of Mn (<0.5 at.%) have been found to reduce leakage currents in BSTO thin films by up to an order of magnitude while increasing relaxation currents and dielectric loss only slightly. At higher doses, the leakage and relaxation currents were found to increase. There is also evidence that acceptor-doped films have an increased barrier to thermionic emission, which may explain the decrease in leakage observed in Mn-doped BSTO thin films [40]. The addition of donor (La) or acceptor (Mn, Fe) impurities to SrTiO, thin films leads to reduced resistance degradation [41].

• Slow polarization as a charge-loss mechanism

The slow polarization currents in BSTO thin films are a charge-loss mechanism that must be considered in addition to the dc leakage through the film [32, 42–44]. Only polarization components that are able to respond within the read/write times projected for future DRAMs

# Figure 13

(a) Field dependence of the leakage current density for asdeposited and annealed 30-nm BSTO films with Pt electrodes at 23°C. The sample was annealed at 550°C for 15 min in O<sub>2</sub>. (b) Temperature dependence of the leakage current density for asdeposited and annealed 30-nm BSTO films with Pt electrodes. The sample was annealed at 550°C for 15 min in O<sub>2</sub>. A voltage of 1.4 V was applied to the as-deposited sample and 2.2 V to the annealed sample.

$(t_{

m write} \approx t_{

m refresh} \leq 10$  ns) result in usable charge storage. Polarization components that cannot respond within the read/write time result in charge loss. The greatest charge loss due to the relaxation currents occurs during the first read after a refresh time following a write to the opposite state for a capacitor that has been written to the same state for many refresh cycles (steady state) [44]. This can be estimated by calculating the ratio of usable free charge

<sup>&</sup>lt;sup>2</sup> J. D. Baniecki, R. B. Laibowitz, and T. M. Shaw, unpublished results.

**Table 5** Worse-case charge loss due to the relaxation currents for BSTO films with thicknesses of 15, 30, and 100 nm, assuming  $V_{\rm CC}=2$  V,  $t_{\rm write}=10$  ns, and  $t_{\rm refresh}=1$  s. The value of  $C_{\rm HF}/A$  is that at  $f=1/t_{\rm write}=0.1$  GHz and is 4% smaller than that measured at 0 V, owing to the nonlinearity of the C-V characteristic (see Figure 10).

| BSTO<br>thickness<br>(nm) | $(fF/\mu m^2)s^{n-1}$ | n    | $C_{\rm HF}/A \ ({\rm fF}/{\rm \mu m}^2)$ | $Q_{ m lost} \ (\%)$ |

|---------------------------|-----------------------|------|-------------------------------------------|----------------------|

| 100                       | 0.14                  | 0.99 | 40.41                                     | 10.9                 |

| 30                        | 0.26                  | 0.99 | 80.01                                     | 10.3                 |

| 15                        | 0.21                  | 0.99 | 92.39                                     | 7.3                  |

(free charge on the capacitor plate that has not been compensated by slow polarization currents) after a refresh time, to the initial usable charge just following the opposite-state write [32]:

$$\% \ Q_{\text{lost}} \approx \frac{2a[(t_{\text{refresh}})^{1-n} - (t_{\text{write}})^{1-n}]}{C_{\text{HF}}(1-n) + a[(t_{\text{refresh}})^{1-n} - (t_{\text{write}})^{1-n}]} \times 100,$$

(2)

where a and n are the magnitude and exponent of the power-law relaxation current defined by  $J_{R}(t) = aVt^{-n}$ , and  $C_{\mathrm{HF}}$  is the capacitance per unit area measured at a frequency of  $1/t_{\text{write}}$ . For  $t_{\text{write}} \le 10$  ns, this frequency is in the low microwave region. In deriving Equation (2), the capacitor has been assumed to be perfectly isolated, and the leakage currents through the film have been neglected. In addition, the relaxation currents are assumed to be linear. Table 5 shows the charge loss due to the relaxation currents for MOCVD BSTO capacitors with film thicknesses of 100, 30, and 15 nm, assuming  $V_{\rm CC}$  = 2 V,  $t_{\rm write} = 10$  ns, and  $t_{\rm refresh} = 1$  s. It is important to note that the calculated charge loss due to dielectric relaxation is for large ( $10^4 \mu m^2$ ) planar capacitors and may not reflect the charge loss for submicron stack BSTO capacitors in actual DRAM circuits. It is interesting to compare the loss due to the relaxation currents to that due to leakage. For 30-nm MOCVD BSTO capacitors, the steady-state leakage is in the range of  $10^{-9}$ – $10^{-8}$  A/cm<sup>2</sup>. The voltage drop (proportional to charge loss) can be estimated by  $\Delta V \approx$  $J\Delta t/(C/A)$ , which gives a drop of 0.0125%-0.125% for  $V_{CC} = 2 \text{ V}$  and  $C/A = 80 \text{ fF/}\mu\text{m}^2$ , with a refresh time  $\Delta t$ of 1 s. This is well below the 7-10% worst-case charge loss due to dielectric relaxation.

# • Reliability issues

In addition to a high capacitance density and low leakage, a BSTO thin-film capacitor must be reliable. There are various failure modes possible for BSTO thin-film devices, including time-dependent dielectric breakdown (TDDB) and resistance degradation. Most experimental studies

show that the onset of resistance degradation occurs before TDDB [45-47]. Resistance degradation is a slow increase in leakage under a prolonged dc voltage stress [48-50] and is influenced by parameters such as doping, stoichiometry [51], and grain size [52]. The predicted lifetimes reported in the literature vary, but recent data on MOCVD BSTO thin films predict lifetimes >> ten years for 24-nm films under the operating conditions of 85°C and 1.6 V. For DRAM applications, the voltage stress conditions on the capacitor are dynamic rather than static; thus, the reliability of the material should be tested under dynamic stress conditions. Horikawa et al. [47] have reported that the degradation in BSTO thin films is greater under a bipolar voltage stress than under a dc stress, and therefore bipolar stress conditions should be used to evaluate BSTO reliability. The estimated breakdown time for 30-nm MOCVD BSTO under a bipolar voltage stress under the operating conditions of 85°C and 1 V was reported to be in excess of ten years.

# 7. Conclusions

Much progress has been made in the development of processes for generating high-quality dielectric films of BSTO, and in the development of suitable electrode and barrier materials needed for integrating the BSTO dielectric in a DRAM capacitor. Planar capacitors of BSTO with Pt electrodes have been fabricated with a specific capacitance greater than 90 fF/ $\mu$ m<sup>2</sup> and a total charge loss of less than 10% after 1 s. Though the interrelationships among the details of the process parameters and integration sequence, the microstructure of the BSTO films, and the mechanisms which affect the specific capacitance and charge loss of a BSTO capacitor are becoming better understood, additional work is required to refine and optimize the details of the processes and integration scheme to achieve threedimensional stacked-capacitor structures which meet the performance objectives for future generations of DRAM. Particular emphasis must be placed on elimination of interfacial layers, reduction of defects caused by plasma processing and hydrogen annealing after BSTO capacitor formation, and a more detailed investigation of the reliability of stacked-capacitor structures with a dielectric of BSTO.

# **Acknowledgments**

The authors wish to acknowledge the members of the IBM/Siemens DRAM Development Alliance for many fruitful discussions, the Advanced Semiconductor Technology Center for processing wafers, and the Analytical Services Group for physical characterization.

# References

- 1. The National Technology Roadmap for Semiconductors, Semiconductor Industry Association, San Jose, CA, 1997.

- C. W. Teng, "DRAM Technology Trend," Proceedings of the 1995 International Symposium on VLSI Technology, Systems, and Applications, 1995, p. 295.

- 3. E. P. Gusev, H.-C. Lu, E. L. Garfunkel, T. Gustafsson, and M. L. Green, "Growth and Characterization of Ultrathin Nitrided Silicon Oxide Films," *IBM J. Res. Develop.* 43, 265 (1999, this issue).

- 4. D. A. Buchanan, "Scaling the Gate Dielectric: Materials, Integration, and Reliability," *IBM J. Res. Develop.* **43**, 245 (1999, this issue).

- P. C. Fazan, U.S. Patent 5,478,772, December 26, 1995;

G. S. Sandhu and P. C. Fazan, U.S. Patent 5,506,166,

April 9, 1996.

- Y. Nishioka, S. R. Summerfelt, K. Park, and P. Bhattacharya, U.S. Patent 5,656,852, August 12, 1997.

- P. C. McIntyre and S. R. Summerfelt, "Kinetics and Mechanisms of TiN Oxidation Beneath Pt Thin Films," J. Appl. Phys. 82, 4577 (1997).

- 8. S. R. Summerfelt, U.S. Patent 5,504,041, April 2, 1996.

- K. L. Saenger, A. Grill, and D. E. Kotecki, "Oxygen-Induced Inhibition of Noble Metal Silicide Formation: Implications for Electrode/Barrier Structures Used with Perovskite Materials," *Mater. Res. Soc. Symp. Proc.* 493, 143 (1998).

- T. Hara, M. Tanaka, K. Sakiyama, S. Onishi, K. Ishihara, and J. Kudo, "Barrier Properties for Oxygen Diffusion in a TaSiN Layer," *Jpn. J. Appl. Phys.* 36 (Part 2), L893 (1997).

- T. Hara, T. Kitamura, M. Tanaka, T. Kobayashi, K. Sakiyama, S. Onishi, K. Ishihara, J. Kudo, Y. Kino, and N. Yamashita, "Barrier Effect of TaSiN Layer for Oxygen Diffusion," J. Electrochem. Soc. 143, L264 (1996).

- P. D. Agnello, C. Cabral, Jr., A. Grill, C. V. Jahnes, T. J. Licata, and R. A. Roy, U.S. Patent 5,576,579, November 19, 1996; A. Grill, C. Jahnes, and C. Cabral, Jr., "Layered TaSiN as an Oxidation Resistant Electrically Conductive Barrier," J. Mater. Res. 14, 1604 (1999).

- 13. S. M. Bilodeau, R. Carl, P. VanBuskirk, and J. Ward, "MOCVD BaSrTiO<sub>3</sub> for 1-Gbit DRAMs," *Solid State Technol.* **40**, 235 (1997).

- 14. H. Shen, D. E. Kotecki, R. J. Murphy, M. Zaitz, R. B. Laibowitz, T. M. Shaw, K. L. Saenger, J. Baniecki, G. Beitel, V. Kueppel, and H. Cerva, "Microstructural Control of (Ba,Sr)TiO<sub>3</sub> Films for Gigabit DRAM Application," *Mater. Res. Soc. Symp. Proc.* 493, 33 (1997).

- 15. M. H. Frey, Z. Xu, P. Han, and D. A. Payne, "The Role of Interfaces on Apparent Grain Size Effect on the Dielectric Properties for Ferroelectric Barium Titanate Ceramics," Ferroelect. 206, 337 (1998).

- 16. R. Waser and M. Klee, "Undoped and Doped Perovskite Films: Sol Gel Processing and Characterization," *Integr. Ferroelect.* **2**, 23–40 (1992).

- 17. T. M. Shaw, R. B. Laibowitz, J. D. Baniecki, M. Copel, P. R. Duncombe, H. Shen, and D. E. Kotecki, "The Effect of Electrode and Grain Boundary Interfaces on the Properties of Barium Strontium Titanate Thin Films," Proceedings of the U.S.-Japan Workshop on Electrically Active Interfaces, March 17, 1998, pp. 57–60.

- 18. M. Copel, P. R. Duncombe, D. A. Neumayer, T. M. Shaw, and R. M. Tromp, "Metallization Induced Band Bending of SrTiO<sub>3</sub> (100) and Ba<sub>0.7</sub>Sr<sub>0.3</sub>TiO<sub>3</sub>," *Appl. Phys. Lett.* **70**, 3227 (1997).

- 19. R. Waser, "Dielectric Analysis of Integrated Ceramic Thin Film Capacitors," *Integr. Ferroelect.* **15**, 39–51 (1997).

- C. Basceri, S. K. Streiffer, A. I. Kingon, and R. Waser, "The Dielectric Response as a Function of Temperature and Film Thickness of Fiber-Textured (Ba,Sr)TiO<sub>3</sub> Thin Films Grown by Chemical Vapor Deposition," *J. Appl. Phys.* 82, 2497 (1997).

- 21. S. K. Streifer, C. Basceri, C. B. Parker, S. E. Lash, J. Christman, H. Maiwa, and A. I. Kingon, "The Influence of Strain on the Dielectric Behavior of (Ba,Sr)TiO<sub>3</sub> Thin Films Grown by LS-MOCVD on Pt/SiO<sub>2</sub>/Si," *Proceedings* of the International Symposium on the Application of Ferroelectrics, in press, 1999.

- S. Hoffmann and Rainer Waser, "Curie-Weiss Law of (Ba<sub>1-x</sub>,Sr<sub>x</sub>)TiO<sub>3</sub> Thin Films Prepared by Chemical Solution Deposition," presented at the Second European Meeting on Integrated Ferroelectrics, EMIF2, September 29-30, 1997.

- C. Zhou and D. M. Newns, "Intrinsic Dead Layer Effect and the Performance of Ferroelectric Thin Film Capacitors," J. Appl. Phys. 82, 3081 (1997).

- 24. G. Rupprecht, R. O. Bell, and B. D. Silverman, "Nonlinearity and Microwave Losses in Cubic Strontium-Titanate," *Phys. Rev.* **123**, 97 (1961).

- S. K. Streiffer, C. Basceri, A. I. Kingon, S. Lipa,

S. Bilodeau, R. Carl, and P. C. van Buskirk, "Dielectric Behavior of CVD (Ba,Sr)TiO<sub>3</sub> Thin Films on Pt/Si," *Mater. Res. Soc. Symp. Proc.* 415, 219 (1996).

- J. D. Baniecki, R. B. Laibowitz, T. M. Shaw, P. R. Duncombe, D. A. Neumayer, D. E. Kotecki, H. Shen, and Q. Y. Ma, "Dielectric Relaxation of Ba<sub>0.7</sub>Sr<sub>0.3</sub>TiO<sub>3</sub> Thin Films from 1 mHz to 20 GHz," *Appl. Phys. Lett.* 72, 498 (1998).

- 27. G. W. Dietz and Rainer Waser, "How to Analyze Relaxation and Leakage Currents of Dielectric Thin Films: Simulation of Voltage-Step and Voltage-Ramp Techniques," *Integr. Ferroelect.* 10, 39–51 (1995).

- 28. A. K. Jonscher, *Dielectric Relaxation in Solids*, Chelsea Dielectrics Press, London, 1983.

- 29. T. Horikawa, T. Makita, T. Kuroiwa, and N. Mikami, "Dielectric Properties of (Ba,Sr)TiO<sub>3</sub> Thin Films," *Extended Abstracts, 7th U.S.-Japan Seminar on Dielectric and Piezoelectric Ceramics*, 1995, pp. 24–27.

- 30. J. D. Baniecki, R. B. Laibowitz, T. M. Shaw, P. R. Duncombe, D. A. Neumayer, D. E. Kotecki, H. Shen, and Q. Y. Ma, "Electrical and Microwave Properties of Mn Implanted (Ba,Sr)TiO<sub>3</sub> Thin Films," *Mater. Res. Soc. Symp. Proc.* 493 (Ferroelectric Thin Films VI), 27–32 (1998).

- M. Schumacher and R. Waser, "Curie-von Schweidler Behavior Observed in Ferroelectric Thin Films and Comparison to Superparaelectric Thin Film Materials," *Integr. Ferroelect.* 22, 109-121 (1998).

- 32. J. D. Baniecki, R. B. Laibowitz, T. M. Shaw, K. L. Saenger, P. R. Duncombe, C. Cabral, D. E. Kotecki, H. Shen, J. Lian, and Q. Y. Ma, "Effects of Annealing Conditions on Charge Loss Mechanisms in MOCVD Ba<sub>0.7</sub>Sr<sub>0.3</sub>TiO<sub>3</sub> Thin Film Capacitors," *J. Eur. Ceram. Soc.* 19, No. 6-7, 1457 (1999).

- 33. N. E. Mott and E. A. Davis, *Electronic Processes in Non-Crystalline Materials*, Clarendon Press, Oxford, U.K., 1979.

- 34. Y. Fukuda, H. Haneda, I. Sakaguchi, K. Numata, K. Aoki, and A. Nishimura, "Dielectric Properties of (Ba,Sr)TiO<sub>3</sub> Thin Films and Their Correlation with Oxygen Vacancy Density," *Ipn. J. Appl. Phys.* 36, Part 2, No. 11B, L1514–L1516 (1997).

- 35. J. D. Baniecki, R. B. Laibowitz, T. M. Shaw, P. R. Duncombe, D. E. Kotecki, H. Shen, and Q. Y. Ma, "Nonlinear Dielectric Relaxation of Mn-Doped Polycrystalline (Ba,Sr)TiO<sub>3</sub> Thin Films Over the Temperature Range 4.2 K-496 K," Ferroelectric Thin Films VII, Mater. Res. Soc. Symp. Proc., 1998, in press.

- W. Dietz, M. Schumacher, R. Waser, S. K. Streiffer,

C. Basceri, and A. I. Kingon, "Leakage Currents in Ba<sub>0.7</sub>Sr<sub>0.3</sub>TiO<sub>3</sub> Thin Films for Ultrahigh-Density Dynamic Random Access Memories," *J. Appl. Phys.* 82, 2359 (1997).

- G. W. Dietz and R. Waser, "Charge Injection into SrTiO<sub>3</sub> Thin Films," *Thin Solid Films* 299, 53–58 (1997).

- J. G. Simmons, "Richardson–Schottky Effect in Solids," *Phys. Rev. Lett.* 15, 967–968 (1965).

- S. Zafir, R. E. Jones, B. Jiang, B. White, V. Kaushik, and S. Gillespie, "The Electronic Conduction Mechanism in Barium Strontium Titanate Thin Films," *Appl. Phys. Lett.* 73, 3533 (1998).

- M. Copel, J. D. Baniecki, P. R. Duncombe, D. Kotecki, R. Laibowitz, D. A. Neumayer, and T. M. Shaw, "Compensation Doping of Ba<sub>0.7</sub>Sr<sub>0.3</sub>TiO<sub>3</sub> Thin Films," *Appl. Phys. Lett.* 73, 1832 (1998).

- W. Hofman, S. Hoffmann, and Rainer Waser, "Dopant Influence on Dielectric Losses, Leakage Behavior and Resistance Degradation of SrTiO<sub>3</sub> Thin Films," *Thin Solid Films* 305, 66 (1997).

- R. E. Jones, Jr., P. D. Maniar, A. C. Campbell,

R. Moazzami, and C. J. Mogab, "High Permittivity Lead Based Perovskite Dielectrics for DRAM Applications," *Integr. Ferroelect.* 5, 235 (1994).

- T. Horikawa, T. Makita, T. Kuroiwa, and N. Mikami, "Dielectric Relaxation of (Ba,Sr)TiO<sub>3</sub> Thin Films," *Jpn. J. Appl. Phys.* 34, 27 (1995).

- 44. K. Numata, Y. Fukuda, K. Aoki, Y. Okuno, and A. Nishimura, "Influence of the Relaxation Current in Ba<sub>0.7</sub>Sr<sub>0.3</sub>TiO<sub>3</sub> Thin Film Capacitors on DRAM Operation," *IEICE Trans. Electron.* E80-C, 1043 (1997).

- 45. K. Numata, Y. Fukuda, K. Aoki, and A. Nishimura, "Analysis of Resistance Degradation of SrTiO<sub>3</sub> and Ba<sub>x</sub>Sr<sub>1-x</sub>TiO<sub>3</sub> Thin Films," *Jpn. J. Appl. Phys.* **34**, 5425 (1995).

- C. Basceri, S. E. Lash, C. B. Parker, S. K. Streiffer, A. I. Kingon, M. Grossmann, M. Hoffmann, M. Schumacher, R. Waser, S. Bilodeau, R. Carl, P. C. Van Buskirk, and S. R. Summerfelt, "An Important Failure Mechanism in MOCVD (Ba,Sr)TiO<sub>3</sub> Thin Films: Resistance Degradation," *Mater. Res. Soc. Symp. Proc.* 493, 9 (1998).

- 47. T. Horikawa, T. Kawahara, M. Yamamuka, and K. Ono, "Degradation in (Ba,Sr)TiO<sub>3</sub> Thin Films Under DC and Dynamic Stress Conditions," *Proceedings of the 35th Annual IEEE International Reliability Physics Symposium*, 1997, pp. 82–89.

- R. Waser, T. Baiatu, and K.-H. Hardtl, "DC Electrical Degradation of Perovskite-Type Titanates: I, Ceramics," J. Amer. Ceram. Soc. 73, 1645–1653 (1990).

- R. Waser, T. Baiatu, and K.-H. Hardtl, "DC Electrical Degradation of Perovskite-Type Titanates: II, Single Crystals," J. Amer. Ceram. Soc. 73, 1654–1662 (1990).

- T. Baiatu, R. Waser, and K.-H. Hardtl, "DC Electrical Degradation of Perovskite-Type Titanates: III, A Model of the Mechanism, Ceramics," *J. Amer. Ceram. Soc.* 73, 1663–1673 (1990).

- 51. M. P. Harmer, Y. H. Hu, M. Lai, and D. M. Smyth, "The Effects of Composition and Microstructure on Electrical Degradation in BaTiO<sub>4</sub>," *Ferroelect.* **49**, 71–74 (1983).

- H. Neumann and G. Arlt, "Maxwell-Wagner Relaxation and Degradation of SrTiO<sub>3</sub> and BaTiO<sub>3</sub> Ceramics," Ferroelect. 69, 179-186 (1986).

Received October 2, 1998; accepted for publication February 2, 1999

David E. Kotecki IBM Microelectronics Division, East Fishkill facility, Route 52, Hopewell Junction, New York 12533 (kotecki@us.ibm.com). Dr. Kotecki is a Senior Engineer in the IBM Microelectronics Division at Hopewell Junction, New York. He joined IBM in 1988 after receiving a Ph.D. in applied science from the University of California at Davis. He is a member of the Process Integration Department in the IBM/Siemens DRAM Development Alliance, working in the area of high-dielectric-constant materials for stacked-capacitor DRAM. Dr. Kotecki has received 14 Invention Achievement Awards from IBM, holds 23 U.S. patents, and has authored or coauthored more than 40 publications.

John D. Baniecki Columbia University, New York, New York 10027 and IBM Thomas J. Watson Research Center, P.O. Box 218, Yorktown Heights, New York 10598 (baniecki@us.ibm.com). Mr. Baniecki is a Ph.D. candidate in the Department of Electrical Engineering at Columbia University, where he is involved in a joint research project on the development of high-dielectric-constant thin films for DRAM applications at the IBM Thomas J. Watson Research Center in Yorktown Heights, New York. He received his B.S. in physics from Purdue University in 1991, his M.S. in physics from Northeastern University in 1993, and his M. Phil. in electrical engineering from Columbia University in 1998. His research interests include the physics and modeling of highpermittivity thin films for use in integrated-circuit memories. He has authored or coauthored more than a dozen papers and is a member of the IEEE and Materials Research Society.

Hua Shen Siemens Microelectronics Inc., Route 52, Hopewell Junction, New York 12533 (hshen@dda.siemens.com). Dr. Shen is a Senior Engineer at Siemens Microelectronics Inc. He received an M.S. in applied science from Yale University in 1991 and a Ph.D. in materials engineering from the Massachusetts Institute of Technology in 1995. He has published 14 papers and filed nine patents in the areas of semiconductor technology and materials processing. Currently he is a member of the Gigabit Integration group in the IBM/Siemens DRAM Development Alliance.

Robert B. Laibowitz IBM Research Division, Thomas J. Watson Research Center, P.O. Box 218, Yorktown Heights, New York 10598 (laibow@us.ibm.com). Dr. Laibowitz is a Research Staff Member at the Thomas J. Watson Research Center. He received his B.A. from Columbia College in 1959, his B.S. and M.S. in electrical engineering from Columbia University in 1960 and 1963, and the Ph.D. in applied physics from Cornell University in 1967. During 1975 he was on assignment at the IBM Zurich Laboratory, where he worked on Josephson effects and other tunneling projects. He has been an Adjunct Professor at Stevens Institute of Technology and Columbia University and is a Fellow of the American Physical Society and a Senior Member of the IEEE. Dr. Laibowitz has worked extensively on applications of both high- and low-transitiontemperature superconductivity, metal-oxide-semiconductor effects, nanostructures, percolation, and the fractal nature of ultrathin films. His present efforts concern the development and utilization of perovskite-based, high-dielectric-constant thin films for DRAM and other storage projects.

Katherine L. Saenger IBM Research Division, Thomas J. Watson Research Center, P.O. Box 218, Yorktown Heights, New York 10598 (saenger@watson.ibm.com). Dr. Saenger has been at the Thomas J. Watson Research Center since 1983, and is currently a Research Staff Member in the Electronic Materials and Structures group. She received an A.B. degree in physics from Barnard College in 1975 and a Ph.D. in chemical physics from Harvard University in 1981. At IBM she has worked in the areas of optical emission diagnostics

of processing plasmas, pulsed laser deposition, and titanium silicide formation. Her current research is directed toward finding electrodes and barrier materials for use with novel ferroelectric and high-epsilon perovskites. Dr. Saenger has authored or coauthored several dozen papers, and she holds nine patents.

Jingyu Jenny Lian Siemens Microelectronics Inc., Route 52, Hopewell Junction, New York 12533 (jlian@dda.siemens.com). Dr. Lian is a Development Engineer at Siemens Microelectronics Inc. and a member of the IBM/Siemens DRAM Development Alliance. She received her Ph.D. in electrical engineering from Kyoto University, Japan, in 1991 for a study of the electrical properties of ferroelectric phase transition. Dr. Lian received an M.S. in materials science and engineering from the Chinese Academy of Science in China in 1985 and a B.S. in chemistry and inorganic materials engineering from Shanghai University of Science and Technology in 1982. Prior to joining Siemens, she was an Adjunct Professor at the University of Cincinnati. Before that, she was a research member of the TDK Corporation R&D Center in Japan. Her work currently is focused on the development of high-dielectric-constant film for DRAM applications.

**Thomas M. Shaw** *IBM Research Division, Thomas J.* Watson Research Center, P.O. Box 218, Yorktown Heights, New York 10598 (tmshaw@us.ibm.com). Dr. Shaw is a Research Staff Member at the IBM Thomas J. Watson Research Center, working in the field of materials science. He received a B.Eng. in metallurgy and materials science from the University of Liverpool in 1975 and a Ph.D. in materials science from the University of California at Berkeley in 1981. In 1984 he joined IBM at the Thomas J. Watson Research Center to work in the Physical Sciences Department. While at IBM he has worked on understanding how the physical properties of ceramic and metals can be controlled through processing. Recent interests include studies of the properties of high-dielectric-constant and ferroelectric thin films and of failure mechanisms in chip interconnects. Dr. Shaw is a Fellow of the American Ceramics Society.

Satish D. Athavale IBM Microelectronics Division, Route 52, Hopewell Junction, New York 12533 (sathaval@us.ibm.com). Dr. Athavale is a Development Engineer in the IBM Microelectronics Division and a member of the Plasma Etch group in the IBM/Siemens DRAM Development Alliance. He is currently working on plasma etching of noblemetal-electrode materials for stacked-capacitor DRAM. Prior to joining IBM, he worked as a Senior Process Engineer in the technology development and process engineering area at Tegal Corporation in Petaluma, California. Dr. Athavale received his Ph.D. in chemical engineering from the University of Houston, where he worked on plasma etching and CVD. He holds an M.S. degree in chemical engineering from Syracuse University and was a gold medalist at the University of Bombay, where he graduated with a bachelor's degree in chemical engineering. Dr. Athavale has authored or coauthored several technical papers. He is currently pursuing an M.B.A. at the Stern School of Business of New York University.

Cyril Cabral, Jr. IBM Thomas J. Watson Research Center, P.O. Box 218, Yorktown Heights, New York 10598 (cabral@watson.ibm.com). Mr. Cabral is an Advisory Engineer at the IBM Thomas J. Watson Research Center in Yorktown Heights, New York. Mr. Cabral received his M.S.E.E. degree from Polytechnic University, Brooklyn, New York, in 1992 and his B.S.E.E. degree from Manhattan College, Riverdale, New York, in 1989. He received a B.S. degree in physics/ mathematics from Pace University, Pleasantville, New York, in 1988. Mr. Cabral joined IBM in 1989 as an engineer in the Thin Film Metallurgy and Interconnections group in the Silicon Technology Department. His focus has been in the area of silicides (metal/silicon reactions) used for contacts to CMOS devices, diffusion barriers (metallic thin films used to prevent interdiffusion of materials), intermetallic reactions, and copper interconnect technology. Mr. Cabral holds 15 U.S. patents and is first author of eleven publications and coauthor of more than fifty additional publications.

Peter R. Duncombe IBM Thomas J. Watson Research Center, P.O. Box 218, Yorktown Heights, New York 10598 (prd@us.ibm.com). Mr. Duncombe is a Senior Associate Engineer in the Exploratory Silicon Science and Technology Department at the IBM Thomas J. Watson Research Center, working on thin-film materials and processes for DRAM, MRAM, NVFRAM, and other applications of ferroelectric and high-permittivity ceramics and low-k dielectrics. Since joining IBM in 1985, he has worked on sintering, superconductivity, GMR, and ceramic packaging. Mr. Duncombe received a Research Division Award for his contributions to the glass ceramic composite via in 1992 and a Third Plateau Invention Achievement Award in 1998. He received a B.A. in chemistry from SUNY New Paltz in 1980 and an M.S. in chemical engineering from SUNY Buffalo in 1983. Mr. Duncombe is a member of the American Chemical Society.

Martin Gutsche Siemens Perlach, Geb. 10723, Otto-Hahn-Ring 6, 81739 Munich, Germany (Martin.Gutsche@siemens-scg.com). Dr. Gutsche is a member of the research and development group at the Siemens semiconductor facility in Munich-Perlach, Germany. His current responsibilities include the development and characterization of new semiconductor materials and processes. From 1996 to 1998 he was a process engineer with Siemens Microelectronics in Hopewell Junction, New York, and a member of the IBM/Siemens DRAM Development Alliance. During that time, he worked on various dry-etch applications, with a major focus on conventional metal etch and platinum etch. Dr. Gutsche received his Ph.D. in physics from the Technical University of Munich, Germany. He is the author or coauthor of several technical papers.

Gerhard Kunkel Siemens Microelectronics Inc., Route 52, Hopewell Junction, New York 12533 (gkunkel@dda.siemens.com). Dr. Kunkel received his degree in physics from the Munich Technical University in 1992. He received his Ph.D. in 1995 from the research center in Juelich, where he worked on fabrications of high-temperature superconducting circuits for high-frequency applications. Since 1997, Dr. Kunkel has worked for the IBM/Siemens DRAM Development Alliance in advanced lithography development for product applications in DRAM memory.

Young-Jin Park Siemens, Microelectronics Inc., Route 52, Hopewell Junction, New York 12533 (ypark@dda.siemens.com). Dr. Park is a Lead Engineer at Siemens Microelectronics Inc. He received M.S. and Ph.D. degrees in materials science from KAIST (Korea Advanced Institute of Science and Technology) in 1987 and 1990, respectively. From 1990 to 1997, he worked in the Memory R&D Division at Hyundai Electronics Ind. Co., Ltd., as a principal technical staff and section manager. At the end of 1997 he joined Siemens Microelectronics Inc., as a member of the Process Integration Department in the IBM/Siemens DDA (DRAM Development Alliance). Dr. Park is currently working in the area of stacked-capacitor development with high-dielectric-constant materials.

Yun-Yu Wang IBM Microelectronics Division, Route 52, Hopewell Junction, New York 12533 (wangyy@us.ibm.com). Dr. Wang received a Ph.D. in physics from the Virginia Polytechnic Institute and State University in 1990. He spent two years as a Research Associate in the Physiology Department at the University of Virginia. From 1992 to 1996, Dr. Wang was a Research Associate in the Materials Science and Engineering Department at Northwestern University. He is currently an Advisory Engineer in the Analytical Department of the Microelectronics Division at IBM.

Richard Wise IBM Microelectronics Division, East Fishkill facility, Route 52, Hopewell Junction, New York 12533 (richwise@us.ibm.com). Dr. Wise is a Development Engineer with the IBM Microelectronics Division in Hopewell Junction, New York. He joined the IBM/Siemens DRAM Development Alliance in July 1996 and currently works in the Dry Etch Department. His primary responsibility is dielectric etching, with a major focus on the application of high-density-plasma tools. Dr. Wise received his Ph.D. in chemical engineering from the University of Houston, where he studied plasma diagnostics and simulation.