# Plasma processing in the fabrication of amorphous silicon thin-film-transistor arrays

by Y. Kuo K. Okajima M. Takeichi

Plasma deposition and etching are two critical processes in the fabrication of the arrays of thin-film transistors (TFTs) in active-matrix liquid crystal displays. The processes fulfill three important production requirements: suitability for use at relatively low substrate temperatures, suitability for large substrates, and high throughput capability. We present an overview of our recent studies on the plasmaprocessing aspects of the fabrication of largearea arrays of TFTs in which use is made of thin films of amorphous silicon containing hydrogen (a-Si:H). Subjects covered include the plasma-enhanced chemical vapor deposition (PECVD) of a-Si:H films, SiN, films, and heavily phosphorus-doped Si films; the influence of the films on TFT characteristics; associated plasma-etching and edge-profile aspects; plasma-etching-induced damage to TFTs and repair of the damage; and equipment aspects.

# Introduction

Active-matrix liquid crystal displays (AMLCDs) have experienced phenomenal growth in the past few years. Their market value is estimated to reach about 10 billion dollars by the year 2000, at an average yearly growth rate of 21%. Although LCDs have been used for decades, the introduction of thin-film transistors (TFTs) has drastically improved their resolution and performance. Figure 1 shows a 13.3-in. XGA (1024 by 768 resolution) TFT LCD module manufactured by Display Technologies Inc. Since each pixel is driven by an individual TFT, the display has superior characteristics, such as the absence of a ghost-shadow image, a gray-scale capability, and a large viewing angle, compared to a conventional (passive-matrix) LCD.

Although the major application of the TFT technology is currently in LCDs, there are many other microelectronic products that could benefit from this technology. For example, the large-area X-ray imager has been successfully

0018-8646/99/\$5.00 © 1999 IBM

Display Technologies Inc. is a joint venture of IBM and Toshiba.

<sup>\*</sup>Copyright 1999 by International Business Machines Corporation. Copying in printed form for private use is permitted without payment of royalty provided that (1) each reproduction is done without alteration and (2) the Journal reference and IBM copyright notice are included on the first page. The title and abstract, but no other portions, of this paper may be copied or distributed royalty free without further permission by computer-based and other information-service systems. Permission to republish any other portion of this paper must be obtained from the Editor.

74

# Figure 1

High-resolution (1024 by 768) 13.3-in. thin-film transistor liquid crystal display. Reproduced with permission from Display Technologies Inc.

Table 1 TFT thin-film materials and deposition methods.

| Thin-film materials                                                                     | Deposition methods                          |

|-----------------------------------------------------------------------------------------|---------------------------------------------|

| a-Si:H, polysilicon, CdSe, etc.                                                         | PECVD, LPCVD, evaporation, etc.             |

| $SiN_x$ , $SiO_2$ , $SiO_xN_y$ , $Ta_2O_5$ , $Al_2O_3$ , dual dielectrics, etc.         | PECVD, APCVD, sputtering, anodization, etc. |

| Mo, Ta, Cr, Ti, Al, Cu,<br>Ta–Mo, Mo–W, Cr–Ni,<br>dual layers, ITO, etc.                | Sputtering, evaporation, etc.               |

| Amorphous or microcrystalline n <sup>+</sup> silicon, etc. (for forming ohmic contacts) | PECVD, ion-shower doping, etc.              |

| Low-temperature, low-Na glass (substrates)                                              |                                             |

fabricated by integrating amorphous silicon (a-Si:H) TFTs with p-i-n photodiodes over a glass substrate coated with an X-ray converter material. High-resolution phantoms of the foot and the head can be recorded with this type of imager [1]. In addition, p-channel TFTs have been used to replace high-resistance loads in static random access memory (SRAM) devices [2], leading to improved cell stability, low standby current, and reduced cell area. In another example, high-density and high-response-speed printer and fax machines fabricated with TFTs have also been demonstrated [3]. By varying the gate-metal material

and the operation condition, the TFT can be used as a chemical sensor, e.g., to detect changes in gas-phase hydrogen concentration or liquid-phase potassium concentration [4]. Many other novel devices based on TFT technology, such as the artificial retina or the EEPROM, have also been demonstrated [5, 6].

# • TFT structures and device aspects

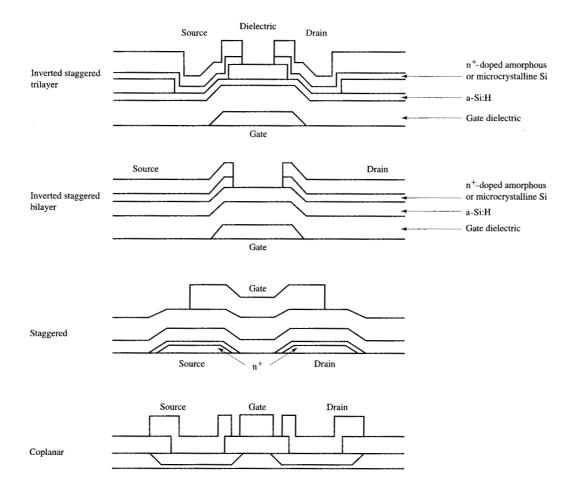

Figure 2 shows cross-sectional views of some of the most common TFT structures [7]. The thickness of each layer is usually in the range of 500 Å to 4000 Å. The coplanar structure, for which the gate and source/drain are located on the same side of the semiconductor layer, is most popular in polycrystalline silicon (polysilicon) TFTs. The other structures, for which the gate and source/drain are located on opposite sides of the semiconductor layer, are commonly used in a-Si:H TFTs. Among the latter, the inverted, staggered trilayer structure is the most popular, because it gives the best transistor characteristics and can be prepared with wide process windows in several steps [8]. The inverted, staggered bilayer structure requires one less masking step to fabricate than the trilayer structure. It has found some use because of this simplification. However, the inverted, staggered, trilayer TFT can be fabricated with a relatively simple process requiring only two photomasks [9].

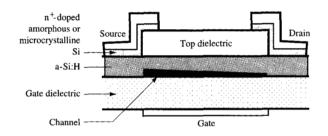

Figure 3 shows the channel current path of an inverted, staggered, trilayer TFT when turned on. The majority of the current flows within a narrow region adjacent to the a-Si:H/gate dielectric interface [10]. Since the a-Si:H layer is thin (usually about 500 Å) for the inverted, staggered TFT, properties of its adjacent interfaces such as chemical composition, morphology, fixed charges, and stress have a tremendous influence on the current density. Therefore, its characteristics, such as field-effect mobility ( $\mu_{\rm eff}$ ), on and off current ( $I_{\rm on}$  and  $I_{\rm off}$ ), threshold voltage ( $V_{\rm th}$ ), and photoleakage current, are a function of the interface properties. More detailed discussions of the influence of structure on TFTs can be found in References [11] and [12].

# • TFT materials and fabrication

**Table 1** lists common thin-film materials for TFTs and their deposition methods. For direct-view LCDs, a-Si:H is used exclusively as the semiconductor material, although it has the lowest mobility among those listed. Its deposition process can be tightly controlled, and the material from which it is produced,  $SiH_4$ , is readily available. Silicon nitride  $(SiN_x)$  is the most popular gate dielectric material because it leads to a lower interface density of states with a-Si:H than can be achieved with other dielectrics, such as silicon oxide  $(SiO_2)$  or metal oxides [13]. A redundant gate dielectric structure is often used to minimize shorting between gate and source/drain metal layers, with SiN\_

# Figure 2

Inverted staggered, staggered, and coplanar TFTs. From [7], reproduced with permission.

used as the interface layer. The ohmic contact is composed of a deposited heavily phosphorus-doped n<sup>+</sup> silicon layer that is either amorphous or microcrystalline. Refractory metals and their alloys are the most commonly used gate materials because of their high temperature stability. However, for relatively large-area TFT arrays, metals having a lower resistivity, such as aluminum or copper, must be used. Indium-tin oxide (ITO) is the dominant pixel material because of its low resistivity, high light transmittance in the visible-wavelength region, and long-term stability.

For small-area LCDs, polysilicon, which can be used in the periphery driver circuit during the fabrication of pixel TFTs, is commonly used as the semiconductor layer, and SiO<sub>2</sub> is the preferred gate dielectric. Cadmium selenide (CdSe) was initially used as the semiconductor

material for TFTs. Although CdSe TFTs have a high mobility (e.g., greater than 100 cm<sup>2</sup>/V-s), deposition of CdSe is more complicated than that of amorphous or polycrystalline silicon. The common gate dielectric is SiO, in combination with Al<sub>2</sub>O<sub>3</sub> [14].

The fabrication of TFTs involves three types of processes: deposition, etching, and lithography. Each process must be applicable at a relatively low temperature, be suitable for large-area coverage, and provide high throughput. The low softening temperature of the glass substrates limits their practical process temperature to less than 500°C. In addition, from the thermal budget point of view, the process temperature should be as low as possible. The maximum process temperature for a-Si:H TFTs is typically below 400°C. On the other hand, substrate size should be maximized in order to lower the

Figure 4

Simplified plasma thin-film process. From [17], reproduced with permission.

production cost and to increase throughput. For example, the current state-of-the-art production glass size is 550 mm by 650 mm, which is expected to increase to nearly 1 m by 1 m in the near future. Since each TFT fabrication step involves several lithography steps, the bottleneck of the throughput is usually those steps. TFT performance is not affected by the lithography processing because it takes place at relatively low temperatures. As for deposition and etching processes, they influence the TFT performance directly through various physical (temperature, material properties, large-area film uniformity, etc.) and chemical (reactions, ion bombardment, radiation exposure, etc.) aspects.

# • Importance of plasma processes

Three types of materials—semiconductors, dielectrics, and conductors—must be deposited in order to fabricate TFTs. The conductors are usually deposited by sputtering. The resistivity of conductors is the major concern because it affects the contact characteristics as well as the signal

delay through a long gate or data line. However, the semiconductor and dielectric deposition processes have a direct impact on each transistor. Plasma-enhanced chemical vapor deposition (PECVD) is the preferred method for preparing these two types of films. It can be used to prepare films having a wide range of chemical compositions, hydrogen content, bond structures, and related stress, topography, morphology, defect-density, and step-coverage characteristics. The interface property, which is critical to TFT characteristics, can be tailored using plasma parameters [15]. Wet etching has been used extensively in TFT fabrication in the past. Recently, plasma etching has become important for its advantages regarding critical dimension control, smaller geometry definition, sloped profile formation, residue deposition, and contamination elimination. However, TFTs can be damaged by a plasma-etching process [16], necessitating repair if feasible. In general, plasma technology is critical to the fabrication of large-area

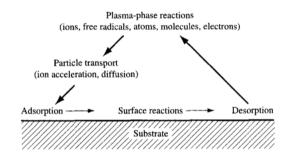

# Plasma processes and goals of this paper Although plasma deposition and etching are used for different purposes, they are based on the same principles.

Figure 4 shows a simplified diagram of a plasma thin-film process. The process is composed of three interrelated mechanisms: plasma-phase reactions, particle transport, and surface-related reactions. The feed stream of the process usually contains several complex gases. The plasma-phase chemical reactions are difficult to predict using conventional reaction mechanisms because the system is a thermodynamically nonequilibrium system having nonstoichiometric reactants. There are two types of particles in the plasma phase: charged (ions and electrons) and neutral (radicals, atoms, and molecules). They are transported to the substrate surface by different mechanisms, the former by ion acceleration and the latter by diffusion. The surface reactions are complicated by the ion bombardment, the nonstoichiometric reactants, and the surface temperature. The activation energies of the surface reactions are a function of both temperature and ion bombardment energy. The ion bombardment also affects the film's morphology and physical structure. Although plasma processes have been routinely used in the fabrication of TFTs and other microelectronic devices, a detailed understanding of relevant phenomena is lacking. So far, most of our knowledge in that regard is empirical. In this paper, we present an overview of some of our recent studies in the PECVD and plasma-etching areas. The main object is to examine issues related to the fabrication of relatively large-area inverted, staggered, trilayer a-Si:H TFT arrays. Materials properties and surface reaction mechanisms are discussed.

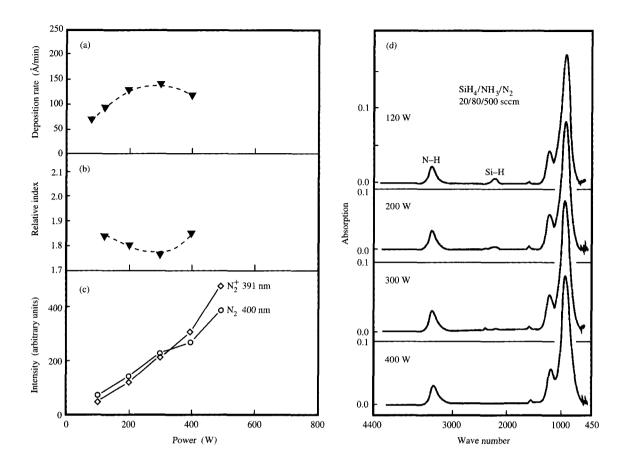

# Figure 5

Variation of PECVD  $SiN_x$  deposition rate (a), refractive index (b), plasma-phase  $N_2$  and  $N_2^+$  intensities (c), and FTIR spectra (d) as a function of plasma power. From [15, 19-21], reproduced with permission.

# PECVD applications in TFT fabrication

# • SiN, dielectric

Silicon nitride  $(SiN_x)$  is the most commonly used dielectric for a-Si:H TFTs. It is used as the gate dielectric, the channel, or the final passivation layer.  $SiN_x$  is part of the device active area when it is in direct contact with the channel region. For example, when  $SiN_x$  is used as the gate dielectric layer, it influences the channel current path; when it is used as the channel passivation layer, it can affect the off current and the photoleakage current [18]. The fixed charge at the a-Si:H/SiN<sub>x</sub> interface can bend the band at the gate dielectric/a-Si:H interface, which influences most of the important transistor characteristics. The  $SiN_x$  passivation layer is passive because it is not in direct contact with the channel region. Relevant materials requirements pertain to the N/Si ratio, hydrogen concentration, SiH/SiH, ratio, stress, and

potential damage to adjacent a-Si:H. However, since PECVD is a complicated process, many process parameters, such as power, temperature, pressure, rf frequency, and plasma power source, can influence the bulk and interface film properties. They are further complicated by the use of a relatively large substrate. Although there are many studies on this subject, contradictory reports are frequently observed. More systematic studies are needed in order to elucidate the various relationships among the PECVD deposition process, materials properties, and array characteristics.

# • PECVD SiN,

Plasma power (W) is one of the most important process parameters in the deposition of  $SiN_x$  films because it influences both the microscopic and the macroscopic properties of the films as well as their large-area uniformity. **Figures 5(a)-(d)** show the deposition rate,

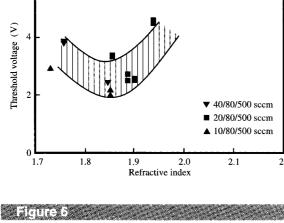

# TFT threshold voltage $(V_{\rm th})$ as a function of the refractive index of PECVD SiN<sub>x</sub> gate dielectric films. The data are for films produced via SiH<sub>4</sub>/NH<sub>3</sub>/N<sub>2</sub> at the indicated flow rates. From [21], reproduced with permission.

refractive index, plasma-phase optical emission spectroscopy, and FTIR (Fourier transform infrared) spectroscopy of SiN, films deposited by means of PECVD (hereafter designated mainly as PECVD SiN, films, or simply PECVD SiN<sub>2</sub>) as a function of plasma power [15, 19–21]. The films were deposited with a parallel-plate electrode configuration and a 13.56-MHz rf power source. The same results have been observed in the temperature range of 250°C to 350°C at a SiH<sub>4</sub> flow rate of 10 to 40 sccm [19]. All of these relationships can be correlated with the critical power  $(W_{\text{critical}})$ , which is dependent on reactor design, cathode area, and operation parameters. In this experiment, the cathode area was 18 in. by 18 in. and the pressure was 500 mTorr. For each feed stream, below  $W_{\text{critical}}$ , the deposition rate increased and the refractive index decreased with increasing power. Above  $W_{\text{critical}}$ , the reverse relation was observed.  $W_{\rm critical}$  is also the transitional point for the following properties: film uniformity, stress, SiH concentration, and the  $N_2/N_2^+$ intensity ratio in the plasma phase. These phenomena can be explained by the simultaneous deposition-etching mechanism of PECVD [20, 22]. When SiH<sub>4</sub>, NH<sub>3</sub>, and N<sub>2</sub> are introduced into the plasma chamber, they are dissociated into precursors of the film, such as SiH, and NH, hydrogen free radicals, and ions. In general, the dissociation efficiency increases with increasing plasma power. However, the dissociation efficiency depends on factors such as bond strength, cross-sectional area, and gas concentration. The relative efficiencies among the gases used vary with power. Also, hydrogen radicals and ions are effective etchants of SiN, [22]. When the plasma power is below  $W_{\text{critical}}$ , the deposition process is controlled by the precursor concentrations, which is consistent with changes in the deposition rate and film characteristics. When the plasma power is higher than  $W_{\text{critical}}$ , the hydrogen-etching mechanism becomes obvious. In addition, the etching process is selective for different elements and functional groups. For example, Auger results show that the Si/N ratio increases with the increase of power. The disappearance of the SiH peak in Figure 5(d) indicates that H attached to Si is removed, e.g., probably by the hydrogen radical. The film stress changes from tensile to compressive when the power is increased from below to above  $W_{\text{critical}}$  [15]. This is also consistent with changes observed in the Si and N concentrations. In summary, the PECVD SiN, process and film characteristics can be explained on the basis of the two competitive PECVD mechanisms: deposition and etching.

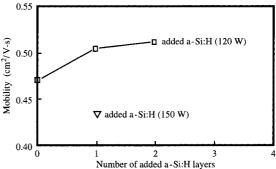

# • SiN, as a gate dielectric for TFTs

In general, SiN is the most popular gate dielectric for TFTs. However, PECVD SiN, has a complicated structure; its hydrogen concentration, bond states, Si/N ratio, and stress vary with deposition conditions. These factors affect TFT performance. For example, a high hydrogen concentration (e.g., greater than 20%) is critical to the low threshold voltage  $(V_{th})$  because it can passivate dangling bonds. Recently, a simple relationship between the threshold voltage of a TFT and the refractive index of its SiN, gate dielectric film has been observed, as shown in Figure 6 [21]. It is clear that despite the wide range of flow rates, the lowest  $V_{\rm th}$  is obtained within a narrow range of the refractive index, i.e., between 1.85 and 1.90. Compared with the stoichiometric Si<sub>3</sub>N<sub>4</sub> film deposited by low-pressure chemical vapor deposition (LPCVD), this type of film is slightly nitrogen-rich. In addition, examination by extended X-ray absorption fine-structure spectroscopy (EXAFS) shows that this kind of film has 1) a mixed structure composed of alpha-SiN and amorphousphase SiN, 2) a shorter Si-N bond than Si<sub>3</sub>N<sub>4</sub> due to the electron affinity of hydrogen attached to N and Si, and 3) a lower coordination number than 3, due to the presence of hydrogen bonds [23]. FTIR spectra show that different SiN, films contain different concentrations of SiH and NH groups, which trap different types of charges. It is possible that with a refractive index between 1.85 and 19.0, SiN, films contain an optimum combination of charge-trapping centers, which is responsible for the lowest  $V_{th}$ . This unified relationship has been used as a guideline in developing new a-Si:H TFT processes.

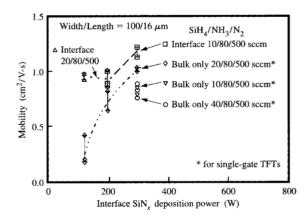

In the manufacture of TFT arrays, the gate dielectric also serves as the interlayer insulator between the gate and the data lines. In order to minimize the possibility of their shorting, a dual-gate dielectric structure (e.g., an

interface SiN, layer in combination with a SiO, or a metal oxide layer) is often applied. This complicates the deposition process, because either an additional deposition chamber (with a different configuration) or an anodization step must be used. Since SiN films with a wide range of materials properties can be deposited using PECVD with minor changes in processing conditions, the dual-gate dielectric structure can be prepared with a graded SiN dielectric. Figure 7 shows the mobilities of TFTs having a graded-gate dielectric and a single-gate dielectric [24]. A graded TFT can have a higher mobility than its corresponding single-gate-dielectric TFT. The thickness of the interface layer can also influence TFT characteristics [25], because the interface SiN, functions as a stressrelaxation layer between the bulk SiN, dielectric and the a-Si:H layers. Therefore, the TFT process can be simplified and its performance improved using the gradedgate SiN dielectric structure.

# • Properties of a-Si:H films

The properties [density of states (DOS), Si-H bond structure, morphology, etc.] and interface characteristics (interface states, chemical composition, sharpness, etc.) of an a-Si:H film can affect transistor performance. These properties are dependent on deposition conditions. For example, it is known that when both a-Si:H and gate SiN<sub>x</sub> films are deposited by the same processes, the inverted, staggered TFT displays better transistor characteristics than the staggered TFT [8]. This is because the former has better interface properties (e.g., lower interface density of states) than the latter. Therefore, when we discuss the influence of the a-Si:H deposition process on TFT characteristics, the dielectric properties of the gate insulator cannot be neglected.

# • PECVD of a-Si:H films

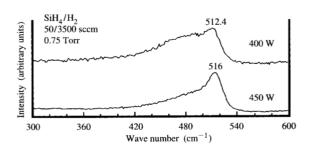

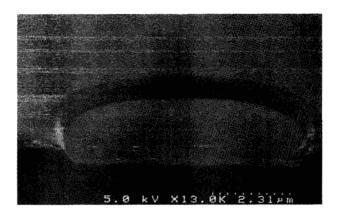

A high a-Si:H deposition rate is desirable for mass production. The deposition rate can be increased by increasing the plasma power or the SiH, concentration in the feed-gas stream. Since the dissociation efficiency of SiH, increases with the plasma power, concentrations of the film's precursors (such as SiH<sub>2</sub>) increase with power. Therefore, the deposition rate increases with power. However, the characteristics of an a-Si:H film also change with plasma power. For example, it has been reported that the SiH<sub>2</sub>/SiH ratio increases with the power [26]. In addition, as shown in Figure 8, the film's morphology, as indicated by Raman scattering, changes with plasma power. The indicated power levels were high, causing both of the films of Figure 8 to contain microcrystals. However, the film deposited at 450 W contained the larger volume fraction of microcrystals, most likely because the concentration of hydrogen and the ion bombardment energy were higher. Since hydrogen preferentially etches

the amorphous phase of the film [27], a higher fraction of crystalline phase was left in the high-power-deposited film.

# • Effects of a-Si:H deposition conditions on TFT characteristics

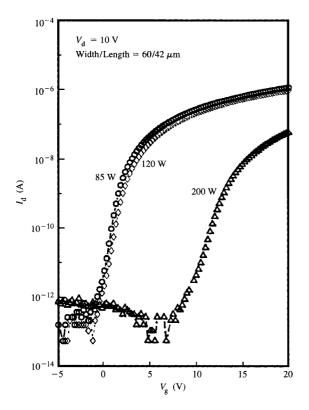

Figure 9 illustrates the effects of a-Si:H deposition conditions on TFT performance. The use of the higher deposition power leads to a higher  $V_{\rm th}$ , a lower on current, and a higher subthreshold slope [7]. Several factors can contribute to this. For example, the high  ${\rm SiH_2/SiH}$  ratio in the film deposited at the higher power may be responsible for the high  $V_{\rm th}$  [26]. The surface of the  ${\rm SiN_x}$  beneath the gate becomes rough when the a-Si:H deposition power is high [28], which could contribute to the low on current and high  $V_{\rm th}$ .

# Bioline 9

TFT transfer characteristics as a function of a-Si:H deposition power. From [7], reproduced with permission.

# Figure 10

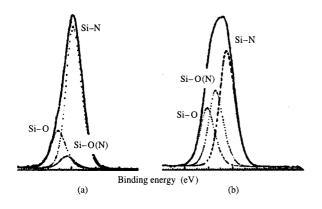

ESCA spectra of  $SiN_x$  surfaces (a) before and (b) after being exposed to  $H_2$  plasma at 250°C, followed by room-temperature oxidation in air.

The high-power plasma could alter the surface chemistry of the gate SiN.. Figure 10 shows ESCA spectra of SiN surfaces before and after being exposed to a H, plasma at 250°C, followed by room-temperature oxidation in air. The nonexposed surface displays small peaks of Si-O and Si-O(N) due to the oxidation of Si dangling bonds. The size of these two peaks increases appreciably if the SiN is exposed to the hydrogen plasma before being exposed to air. This is because the hydrogen plasma etches the surface and makes it more active. When this kind of surface is exposed to air, it is easily oxidized. A highpower a-Si:H deposition condition generates a high concentration of hydrogen, which can etch the previously deposited SiN, surface and generate Si dangling bonds at the a-Si:H/SiN interface. The interface density of states increases with the increase of the number of dangling bonds. For an a-Si:H TFT, the high interface density of states causes a high threshold voltage and a high subthreshold slope. Therefore, the power dependence in Figure 9 can be explained by the hydrogen-etching mechanism indicated by Figure 10.

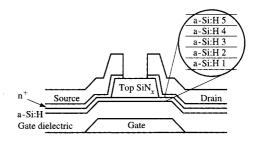

The influence of the a-Si:H deposition conditions can extend to regions that are not in direct contact with the plasma. For example, Figure 11 shows the variation of the field-effect mobility of a multilayer a-Si:H TFT as a function of the number of added a-Si:H layers and the plasma power [29, 30]. The TFT had a conventional inverted, staggered structure, except that its a-Si:H film was composed of several layers. The two interface a-Si:H layers (adjacent to the bottom and the top dielectrics) and the odd-numbered layers were deposited under the same conditions used for the single-layered a-Si:H TFT. The even-numbered layers were deposited by the same process except at higher power levels. Therefore, if the a-Si:H deposition conditions do not affect the interface and gate dielectric characteristics, all TFTs should have had the same mobility. However, Figure 11 shows a different result. The mobility improves when the deposition power of the inner layer is moderately higher than that of the interface layer; the mobility deteriorates when the power is too high. The discrepancy can be explained as follows: When the power is increased, in addition to the increase of concentrations of film precursors such as SiH, other major plasma properties such as ion bombardment energy, hydrogen concentration, and short-wavelength light intensity are also enhanced. The effects of the ion bombardment extend to a depth of less than 100 Å, which is thinner than the thickness of the interface a-Si:H layer. On the other hand, the hydrogen diffusion rate is greatly facilitated by the high deposition temperature, i.e., 250°C. The extra hydrogen at high power can penetrate through the interface a-Si:H layer and into gate SiN, layers. It passivates dangling bonds in the bulk of the film and at the interface, improving the mobility of the TFT [31].

However, when the plasma power is very high, the intensity of the short-wavelength light can penetrate through all the films and generate dangling bonds [16, 32]. When the radiation effect is more pronounced than the hydrogenation effect, the TFT deteriorates. In summary, a-Si:H film deposition conditions can influence TFT performance through two competitive mechanisms: hydrogenation and radiation.

• PECVD of heavily phosphorus-doped n<sup>+</sup> silicon films

Ohmic contacts are important parts of a transistor because they affect the total resistance of the current path. For a-Si:H TFTs, the ohmic contact is usually formed by depositing via PECVD a heavily phosphorus-doped (P-doped) silicon film between the a-Si:H and the metallic interconnection lines. There are two key items affecting the quality of the ohmic contact: the resistivity of the n<sup>+</sup> silicon films and the cleanness of their interfaces with the a-Si:H. The former depends on the concentration and activation efficiency of the dopant. The latter depends on the concentration of native oxide on the a-Si:H surface before the deposition of n<sup>+</sup> silicon.

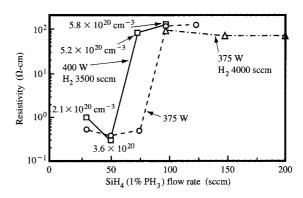

Figure 12 shows the resistivity of heavily phosphorusdoped (n<sup>+</sup>) silicon films (hereafter designated mainly as n<sup>+</sup> films) as a function of gas-flow rate [33]. The films were deposited at 330°C in a parallel PECVD reactor operating at 60 MHz. The phosphorus (P) concentrations were very high, e.g., above the saturation value. Most of these dopant atoms were electrically inactive with respect to the following. Since P atoms come from the plasmadissociated PH<sub>3</sub>, a large portion of them are attached with hydrogen. This lowers the efficiency of the dopant. In addition, since the deposition temperature is low (330°C), most of the dopants are not activated even if they are in the substitutional sites of the silicon network. This also contributes to the low efficiency of the dopant. On the other hand, the resistivity increased by two orders of magnitude with a small increase of the SiH<sub>4</sub> (1% PH<sub>3</sub>) flow rate. This is contradictory to the change in the phosphorus content of the films, which increased monotonically with the increase of the flow rate. However, their morphology change was consistent with the resistivity change; i.e., the volume fraction of microcrystals in the films decreased with a decrease in their resistivity. This could be attributed to the segregation of dopants at grain boundaries, which increases the activation efficiency. In addition, an unusual phenomenon in the PECVD n<sup>-</sup> silicon deposition process has been observed. The n<sup>+</sup> film deposition rate is higher than that of intrinsic silicon, e.g., by a factor of 2, while the P concentration is relatively low, e.g., less than 5% [33]. It is highly improbable that the drastic increase of the deposition rate is due to the chemical influence of PH adsorption. However, it is well known in the chlorine plasma etching of intrinsic silicon

TFT field-effect mobility of a layered a-Si:H structure as a function of the number of added a-Si:H layers (at two power levels). From [29, 30], reproduced with permission.

Resistivity of a heavily phosphorus-doped (n<sup>+</sup>) silicon film deposited by PECVD as a function of the SiH<sub>4</sub> (1% PH<sub>3</sub>) flow rate. As indicated, phosphorus concentrations ranged from 2.1 to  $5.8 \times 10^{20}$  cm<sup>-3</sup>. From [33], reproduced with permission.

that the etching rate is drastically increased when a small amount of P dopant is added into the silicon [34]. The enhancement of the etching rate has been attributed to the change of the electronic properties instead of the change of chemical composition or physical structure. The same mechanism can be used to explain the enhancement of the deposition rate in the n<sup>+</sup> deposition case. Therefore, the PECVD of n<sup>+</sup> films is different from that of a-Si:H films because of the complicated doping-gas effects.

The microcrystalline n<sup>+</sup> film deposition process involves the use of a high hydrogenation concentration and a high plasma power. Both factors favor the etching of the native oxide on the silicon surface. Ohmic contacts can be consistently formed with this type of process. The contact resistance of an 11-µm-channel-length a-Si:H TFT with microcrystalline n<sup>+</sup> ohmic contacts contributes to about 10% of the total resistance at the on state [35]. When the channel length shrinks, the contribution of the source and drain contact resistance to the total resistance increases. The highly conductive microcrystalline n<sup>+</sup> film deposition process is indispensable for short-channel TFTs.

# • Equipment considerations

One of the main advantages of PECVD is its suitability for depositing various types of amorphous silicon and dielectric films on large-area substrates at relatively low substrate temperatures. However, there are consistent challenges in this process with regard to increasing substrate size and decreasing particle contamination. Many attempts have been made to address these objectives, for example by using a high-frequency power supply, a gated rf-discharge scheme, or a plasma box [7, 36, 37]. Devices fabricated in such reactors are as good as those prepared from conventional PECVD reactors. However, these systems require a nonstandard (i.e., not 13.56-MHz) rf generator, a complicated rf-driving method, or a doublewall reactor design. On the other hand, the current parallel-plate reactor design and the 13.56-MHz rf power supply can be used for substrates as large as 1 m by 1 m with high deposition rate and good uniformity. Other common issues for large-substrate PECVD equipment are their bulky size and high cost. A large portion of the equipment is occupied by the automatic substrate-handling system rather than the deposition chamber. These robotics also contribute to their high cost. The size and cost of the equipment have to be reduced, for example, through a new design of a simpler and cheaper substrate-handling system.

# Plasma-etching applications in TFT fabrication

There are two issues that have to be considered in the plasma etching of TFTs: process capability and device effects. In the process area, the etching rate, selectivity, profile control, and film damage must be examined. In the device area, the TFT damage mechanism must be understood and a corresponding repair method established.

# • Etching rate and selectivity

Thin-film materials for a-Si:H TFTs have properties that differ from those used in silicon integrated circuits. For example, an a-Si:H film is amorphous and usually contains about 10% hydrogen. It forms a slightly thicker native oxide than that on single-crystal silicon. Both a-Si:H and single-crystal silicon can be effectively etched with the same plasmas, e.g., fluorine- or chlorine-containing plasmas. The a-Si:H film can be etched slightly faster than the crystalline silicon because of its high hydrogen content. PECVD SiN, films are slightly nitrogen-rich compared to LPCVD Si<sub>3</sub>N<sub>4</sub> films. They also contain a very large amount of hydrogen (more than 20%). These two factors are responsible for their extremely high etching rates (e.g., more than 3000 Å/min) in fluorine-based systems [38]. In a chlorine-containing plasma, an a-Si:Hto-SiN etch-rate ratio greater than 5 can be achieved [39]. A similar type of high selectivity can be obtained between single-crystalline silicon and Si<sub>3</sub>N<sub>4</sub>. In a fluorine-containing plasma, the reverse selectivity is observed between a-Si:H and SiN.. However, the same selectivity still exists between single-crystal silicon and Si<sub>2</sub>N<sub>4</sub>.

The dopant content in a-Si:H can influence its etching rate. For example, in a  $CF_2Cl_2$  or  $CF_3Cl$  plasma, the etchrate ratio of  $n^+$  silicon to intrinsic a-Si:H can be higher than 2 [40]. The same kind of relationship has been observed between heavily doped and intrinsic crystalline films. The selectivity is due to the difference in their electrical properties rather than their dopant concentrations. The high etching selectivity between  $n^+$  and intrinsic a-Si:H films is critical in the fabrication of the bilayer TFT.

Since a metal oxide layer is sometimes used as the gate dielectric layer in the dual-dielectric structure, it must be etched to expose the gate metal underneath. If the metal oxide is formed from anodization of the gate line, a high etching selectivity between them is required. Under the same halogen plasma condition, the metal etching rate is usually much lower than that of the silicon because the vapor pressure of a metal halide is lower than that of a corresponding silicon halide [41]. The metal oxide is even more difficult to etch because it contains a strong metal-oxygen bond which must be broken. However, a high metal oxide etching rate can be obtained with a combination of a high ion bombardment energy and a high substrate temperature [42]. In addition, when a proper feed gas is used, the metal oxide can be etched more rapidly than the metal. For example, in a CF<sub>4</sub> plasma, tantalum (Ta) etches more rapidly than tantalum oxide (Ta<sub>2</sub>O<sub>5</sub>). However, in a CHF<sub>3</sub> plasma, the reverse is true [42]. This is because a Teflon-type polymer is formed on the Ta metal surface, drastically reducing its etching rate. At the same time, oxygen in the Ta<sub>2</sub>O<sub>5</sub> consumes hydrogen and prevents polymer formation. A similar type

of relationship (but with lower selectivity) has been observed between titanium (Ti) and titanium oxide (TiO<sub>2</sub>) [43]. The difference in surface reactions between Ti and TiO<sub>2</sub> is less than that between Ta and Ta<sub>2</sub>O<sub>5</sub>. Therefore, in principle, the high etching selectivity between a metal oxide and a metal is achievable if nonvolatile products are formed on the metal surface rather than on the metal oxide surface. In addition to plasma-phase reactions, substrate temperature plays an important role in metal oxide etching.

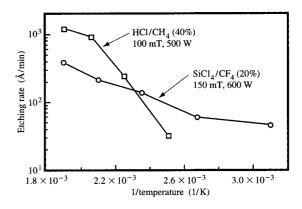

Indium-tin oxide (ITO) films are widely used in all TFT LCDs because of their relatively low resistivity (e.g., 300  $\mu\Omega$ -cm) and high light transmittance (e.g., >80%) in the visible wavelength range. They are conventionally etched with an aqua-regia type of solution that is a mixture of hydrochloric acid and nitric acid. This solution attacks all metals and requires special waste-water treatment. Plasma etching of ITO has been studied for many years. The major problem is its low etching rate (e.g., less than 200 Å/min) if use is made of a conventional etching process. This is because 1) the In-O and Sn-O bonds are strong; 2) In- and Sn-halides have very low volatilities; and 3) In and Sn have high boiling points. There are two solutions for this problem: increasing the ion bombardment energy or ion flux, or increasing the substrate temperature [44]. The former requires the use of a high-density plasma source or an extreme etching condition; it is not feasible for current large-area substrates. The latter requires the use of a milder etching condition and additional substrate heating. Figure 13 shows the effect of substrate temperature on ITO RIE (reactive ion etching), using HCl/CH<sub>4</sub> and SiCl<sub>4</sub>/CF<sub>4</sub> as the feed gases [45]. The substrate was etched with a PlasmaTherm 700 reactor in the RIE mode (containing a parallel-plate electrode and a shower-head anode). The etching rate increased by two orders of magnitude as the substrate temperature was increased from 120°C to 250°C in a HCl/40% CH<sub>4</sub> plasma; it increased by one order of magnitude as the substrate temperature was increased from 25°C to 250°C in a SiCl<sub>2</sub>/20% CF<sub>4</sub> plasma (maintained at a higher power). Since the ion bombardment energy does not change with the substrate temperature, the improvement in etching rate was attributed primarily to the increase of the surface reaction rate.

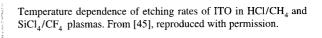

In addition, the feed gas has a profound influence on the etching rate. **Figure 14** shows the ITO etching rate as a function of the  $\mathrm{CH_4}$  concentration in  $\mathrm{HCl/CH_4}$  and  $\mathrm{SiCl_4/CF_4}$  mixtures [46, 47]. The rate peaks at about 40%  $\mathrm{CH_4}$  in the  $\mathrm{HCl/CH_4}$  mixture; it is almost constant in the range of 0% to 40%  $\mathrm{CH_4}$  and drops with a further increase of the  $\mathrm{CH_4}$  concentration in the  $\mathrm{HBr/CH_4}$  mixture. The etching process is composed of several mechanisms: reduction of metal oxides, removal of metals,

Etching rate of ITO as a function of  $\rm CH_4$  concentration in  $\rm HCl/CH_4$  and  $\rm HBr/CH_4$  plasmas. From [46,47], reproduced with permission.

and residue formation. If the first two mechanisms are enhanced and the last mechanism is suppressed, the maximum rate is obtained. Therefore, a high ITO etching rate is achievable with a high substrate temperature and a proper feed-gas composition. However, under certain etching conditions, the plasma-generated etchants react with the photoresist pattern. The etching rate becomes a function of the distance from the edge of the photoresist, which is usually designated as the "loading factor" effect. When the substrate temperature is high, the effect becomes serious [47].

# Figure 15

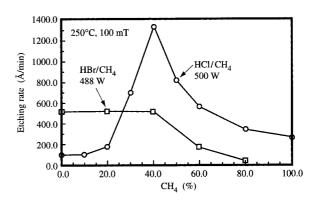

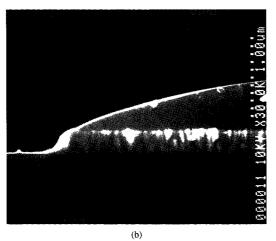

SEM cross-section micrographs of the edges of MoW films after (a) etching, (b) over-etching, and (c) etching by means of a two-step process.

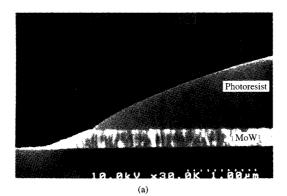

# • Edge profile control

The a-Si:H TFT contains a layered structure similar to the multilayer interconnection portion of a typical silicon integrated circuit. In such circuits, planarization is used to

improve step coverage. Typically, the planarization is carried out on the intermetal dielectric layers because the metal conductor lines are usually narrow and their cross-sectional area must be maximized. In the inverted, staggered TFT structure, since the metal lines are the major source of the step coverage problem and they usually have widths of several micrometers, the planarization is achieved by sloping their edges.

For certain designs, the contact holes through thick multilayer film must be sloped. The typical plasma sloping process is based on the photoresist erosion principle, in which the photoresist layer is purposely consumed during the etching [48, 49]. Therefore, the initial photoresist profile is an important factor in the process. For example, if the photoresist has a vertical profile, the layer beneath cannot be sloped unless the radial etching rate at the photoresist/film interface is much higher than the vertical etching rate. The photoresist profile can be controlled by the lithography method or by flowing the photoresist at a high temperature. The latter is a preferred method because the process is easy to control. It has been predicted by simulation and demonstrated experimentally that the etch-rate ratio between the photoresist and the film determines the final slope of the etched film [50]. A ratio greater than 1 is required if the slope of the etched film is shallower than that of the original photoresist layer. The etch-rate ratio is a function of the plasma composition. For example, when molybdenum is etched in a fluorine-containing plasma, the molybdenum-tophotoresist etch-rate ratio varies with parameters such as O<sub>2</sub> concentration, pressure, and power [48, 50]. In addition, the consumption of etchants depends on factors such as substrate size, ratio of photoesist to exposed film area, and pattern layout. In some cases, the loading factor, i.e., the differential etching of a film along the radial distance from the edge of the photoresist layer, shows up because of a change in the above factors. This can affect the film profile. Figures 15(a) and 15(b) show profiles of molybdenum-tungsten (MoW) films after they were etched for two different periods. After etching (a), the film edges displayed a shallow angle. However, upon over-etching (b) the edges steepened. The change in slope was due to the change in consumption of the etchant. During the etching of MoW, a large amount of fluorine is consumed. The slope is obtained through proper balance of the etchant concentrations for photoresist and MoW. When MoW in the open area is etched away, the etchant concentrations change; e.g., the consumption of fluorine decreases [51]. The sidewall of the MoW profile is excessively etched, and a steep profile is formed. Since the over-etching step is necessary for large-area etching, the etching condition must be changed to avoid an extra supply of the fluorine radical. Figure 15(c) shows the MoW profile after a twostep etching process. The first step resulted in the sloped

profile; in the second step, use was made of a feed stream that had a higher O<sub>2</sub> concentration than the first step. Although that resulted in a lower MoW etching rate, it produced a higher photoresist etching rate, thus preserving the sloped profile.

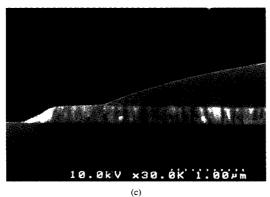

The photoresist erosion method can be applied to etch a via through a multilayer structure. Figure 16 shows a sloped via obtained using a two-step process. The film was composed of two layers (600 Å n<sup>+</sup>/700 Å a-Si:H/4000 Å SiN) above an ITO layer. In the previous section, it was noted that the use of a chlorine-containing plasma results in a high etching rate for either n<sup>+</sup> or a-Si:H as well as a high etch-rate ratio to SiN. On the other hand, the use of a fluorine-containing plasma results in the opposite effect. Therefore, it is difficult to use one plasma step to etch through this stacked layer and, at the same time, supply a sloped profile. However, if the first two layers are etched in a chlorine-based plasma containing a proper amount of O,, the upper two layers can be sloped and the lower SiN, layer slightly etched. The use of a fluorine-containing mixture (e.g., one containing CF<sub>4</sub>) results in slight etching of the upper two layers and anisotropic etching of the SiN layer. Therefore, such a mixture can be used as the second step. As indicated in the figure, the via thus obtained contains a sloped shape on its upper part and a near-vertical shape below, without undercutting in the SiN layer.

# Plasma-etching damage

Plasma etching can damage TFTs and associated films through various mechanisms. For example, it has been observed that after RIE followed by exposure to air, PECVD SiN contains a high oxygen concentration within 60 Å of its surface [40]. This is caused by ion bombardment. The film also displays a high electron spin resonance (ESR) signal. This is due to the shortwavelength radiation (generated in the plasma phase) exposure. In the fabrication of silicon integrated circuits, another plasma-etching damage mechanism [the breakdown of the thin gate oxide in metal-oxidesemiconductor field-effect transistors (MOSFETs) due to charge buildup] has often been observed (see for example [52]). This type of damage has not been observed in TFTs, probably because of their inverted, staggered structure, in which the gate dielectric is not in direct contact with the plasma. In addition, the TFT gate dielectric is much thicker than the gate oxide of the MOSFET—typically about 3500 Å vs. about 100 Å. However, the plasma radiation is the major cause of TFT damage [16]. For example, after an RIE process, the TFT usually displays a high off current and a large threshold voltage [16, 40]. The same kind of device deterioration has been confirmed by exposing a TFT to a laser beam, i.e., 257-nm Ar laser, with the frequency being doubled [32]. The damaged TFT

SEM of a via etched into an  $ITO/a-Si:H/SiN_x$  composite layer, using a two-step process.

can be repaired by a high-temperature (e.g., 250°C) annealing step. The short-wavelength light penetrates through the channel region (channel passivation, a-Si:H, and gate dielectric layers) and generates dangling bonds in the films as well as at the film interfaces. The broken bonds are probably from the loosely bonded hydrogen. Since no hydrogen is lost from the films during the process, these bonds can be restored by annealing at a relatively low temperature.

# • Equipment considerations

Major considerations with respect to large-substrate plasma-etching equipment are cost and size. As for PECVD, the automatic handling system required takes a large portion of the total cost and size. A novel design is required to lower the cost and the size. In addition, plasma-etching systems are usually designed for one-step etching. If the etching step could be integrated with other steps (e.g., photoresist stripping and plasma damage repair), the production throughput could be increased. High-etching-rate production equipment for plasma etching of ITO is not yet available. Since conventional etching systems are not suitable for this application, a new design, for example, adding a high-temperature heater or a high-density plasma source, is required. The hightemperature etching of ITO has been discussed in a previous section. High-density plasma systems, such as the inductively coupled plasma source, have also shown some promising results [53]. For any new system, issues regarding large-area-substrate process capability (uniformity across the substrate, selectivity between films, etc.) must be considered.

# Summary

Plasma deposition and etching are used extensively in the fabrication of large-area a-S:H TFT arrays. This is because the processes can fulfill the three important production requirements: suitability for use at relatively low substrate temperatures, large-substrate-area capability, and high throughput. The PECVD process can supply materials with varying characteristics to fit the unique structure and materials requirements of TFTs. Plasma etching can be used to solve several critical problems in TFT fabrication. In this paper, the authors have reviewed issues in PECVD (i.e., gate SiN<sub>x</sub>, a-Si:H, and n<sup>+</sup> silicon) and plasma etching (i.e., rate, selectivity, profile control, and damage mechanisms).

Although current plasma technology can be used to fabricate a-Si:H TFTs with satisfactory performance, there are several areas that require further improvement. For example, the a-Si:H TFT has a low mobility and high photosensitivity. These characteristics can be improved with a better control of the PECVD processes, e.g., lowering the interface defect density, improving morphology, or relaxing the stress mismatch between TFT films. A polycrystalline silicon TFT displays a high mobility and low photosensitivity. However, there is currently no polycrystalline silicon TFT process that satisfies all three of the production requirements mentioned above. Therefore, advances in the PECVD aspects of the process may be the most viable means to achieve higher-performance TFTs. In the plasma-etching area, since new materials and structures are constantly being introduced, etching advances are frequently needed—for example, advances in recent years to increase the ITO etching rate. In addition, the ongoing need for edge profile control of composite layers of different materials presents continuing challenges.

In this overview, we have discussed a number of means for improving the fabrication of large-area arrays of inverted, staggered, trilayer a-Si:H TFTs by controlling relevant plasma-related phenomena. In our view, however, in order to ensure continuing improvement, more efforts will have to be devoted to developing an in-depth understanding of the effects of such phenomena on the TFTs and other portions of the arrays.

# References

- L. E. Antonuk, J. Yorkston, and R. A. Street, "Two-Dimensional, TFT + Sensor Arrays for Medical Imaging,"

*Proceedings of the First Symposium on Thin Film Transistor Technologies*, Y. Kuo, Ed., PV 92-24, The Electrochemical Society, Pennington, NJ, 1992, pp. 252-265.

- M. Kinugawa, "TFT Cell Technology for High Density SRAMs," *Ibid.*, pp. 145–153.

- 3. T. Ozawa, "Key Technologies to Provide High Performance a-Si:H TFT Image Sensor," *Ibid.*, pp. 244–251.

- G. Fortunato and A. Pecora, "Application of Metal/Insulator/Hydrogenated Amorphous Silicon

- Structures to the Field of Chemical Sensors," *Proceedings of the Second Symposium on Thin Film Transistor Technologies*, Y. Kuo, Ed., **PV 94-35**, The Electrochemical Society, Pennington, NJ, 1994, pp. 341–355.

- D. Horst, E. Lueder, M. Habibi, T. Kallfass, and J. Siegordner, "A Thin Film Retina Addressed by Arrays of TFTs," *Ibid.*, pp. 381–391.

- S. G. Burns, H. R. Shanks, A. P. Constant, C. Gruber, D. Schmidt, A. Landin, C. Thielen, F. Olympie, T. Schumacher, and J. Cobbs, "Design and Fabrication of α-Si:H-Based EEPROM Cells," *Ibid.*, pp. 370–380.

- Y. Kuo, "Plasma Etching and Deposition for a-Si:H Thin Film Transistors," J. Electrochem. Soc. 142, No. 7, 2486 (1995).

- 8. K. Hiranaka, T. Yoshimura, and T. Yamaguchi, "Effects of the Deposition Sequence on Amorphous Silicon Thin-Film Transistors," *Jpn. J. Appl. Phys.* **28**, No. 11, 2197 (1989).

- 9. Y. Kuo, "A New Process Using Two Masks to Prepare Tri-Layer Thin Film Transistors," *J. Electrochem. Soc.* **138**, No. 2, 637 (1991).

- M. Shur and M. Hack, "Physics of Amorphous Silicon Based Alloy Field-Effect Transistors," J. Appl. Phys. 55, 769 (1984).

- R. A. Street and M. J. Thompson, "Electronic States at the Hydrogenated Amorphous Silicon/Silicon Nitride Interface," Appl. Phys. Lett. 45, 769 (1984).

- M. J. Powell, J. A. Chapman, A. G. Knapp, I. D. French, J. R. Hughes, A. D. Pearson, M. Allinson, M. J. Edwards, R. A. Ford, M. C. Hemings, O. F. Hill, D. H. Nicholls, and N. K. Wright, "Active Matrix-Addressed LC Television Using a-Si Thin Film Transistors," *Proceedings* of EuroDisplay, Institution of Electrical Engineers, London, 1987, pp. 63-66.

- M. Powell, C. van Berkel, A. R. Franklin, S. C. Deane, and W. I. Milne, "Defect Pool in Amorphous-Silicon Thin-Film Transistors," *Phys. Rev. B* 45, No. 8, 4160 (1992).

- 14. J. De Baets, A. Van Calster, A.-M. De Cubber, H. De Smet, and J. Vanfleteren, "Modelling Poly-CdSe TFTs for AMLCD," Proceedings of the Second Symposium on Thin Film Transistor Technologies, Y. Kuo, Ed., The Electrochemical Society, Pennington, NJ, 1994, pp. 228-232.

- Y. Kuo, "Large Area Plasma Enhanced Chemical Vapor Deposition of Nonstoichiometric Silicon Nitride," *Mater. Res. Soc. Symp. Proc.* 282, 623 (1993).

- Y. Kuo, "Reactive Ion Etch Damages in Inverted, Staggered, Tri-Layer Thin-Film Transistor," Appl. Phys. Lett. 61, 2790 (1992).

- Y. Kuo, "Deposition and Etching Mechanisms in Plasma Thin Film Processes," Application of Particle and Laser Beams in Materials Technology, P. Misaelides, Ed., NATO ASI Series E: Applied Sciences, Vol. 283, Kluwer Academic Publishers, Dordrecht, 1995, pp. 581–593.

- J. Robertson and M. J. Powell, "Defect Model of Charge Transfer Doping at a-SiN<sub>2</sub>:H/a-Si:H Interfaces," J. Non-Cryst. Solids 77/78, 1007 (1985).

- Y. Kuo, "Plasma Enhanced Chemical Vapor Deposition of SiN, for Thin Film Transistors," Proceedings of the Twelfth International Symposium on Chemical Vapor Deposition, PV 93-2, The Electrochemical Society, Pennington, NJ, 1993, pp. 350-356.

- Y. Kuo, E. C. Paloura, and C. Dziobkowski, "Characterization of PECVD Sin Process and Material for TFT Gate Dielectric Applications," *Proceedings of the Tenth Symposium on Plasma Processing*, G. S. Mathad and D. W. Hess, Eds., PV 94-20, The Electrochemical Society, Pennington, NJ, 1994, pp. 513-524.

- Y. Kuo, "PECVD Silicon Nitride as a Gate Dielectric for Amorphous Silicon Thin Film Transistor—Process and

- Device Performance," J. Electrochem. Soc. 142, No. 1, 186 (1995).

- Y. Kuo, "Etch Mechanism in the Low Refractive Index Silicon Nitride Plasma-Enhanced Chemical Vapor Deposition Process," Appl. Phys. Lett. 63, No. 2, 144 (1993).

- E. C. Paloura, Y. Kuo, and W. Braun, "On the Effect of Bonded Hydrogen in the Local Microstructure of PECVD SiN: H Films," *Physica B* 208 & 209, 562 (1995).

- 24. Y. Kuo, "Thin Film Transistors with Graded SiN, Gate Dielectrics," J. Electrochem. Soc. 141, No. 4, 1061 (1994).

- 25. Y. Kuo and F. R. Libsch, "a-Si:H TFTs with a Graded Gate SiN Dielectric Structure—Interfacial Layer Thickness Effects and Characterization," Proceedings of the Second Symposium on Thin Film Transistor Technologies, Y. Kuo, Ed., PV 94-35, The Electrochemical Society, Pennington, NJ, 1994, pp. 41-51.

- H. Miki, S. Kawamoto, T. Horikawa, T. Maejima, H. Sakamoto, M. Hayama, and Y. Onishi, "Large Scale and Large Area Amorphous Silicon Thin Film Transistor Arrays for Active Matrix Liquid Crystal Displays," *Mater. Res. Soc. Symp. Proc.* 95, 431 (1987).

- C. C. Tsai, G. B. Anderson, R. Thompson, and B. Wacker, "Control of Silicon Network Structure in Plasma Deposition," *J. Non-Cryst. Solids* 114, 151 (1989).

- K. Takechi, H. Uchida, and S. Kaneko, "Mobility Improvement Mechanism in a-Si:H TFTs with Smooth a-Si:H/SiN<sub>x</sub> Interface," *Mater. Res. Soc. Symp. Proc.* 258, 956 (1992).

- Y. Kuo, "Thin Film Transistors with Layered a-Si:H Structure," Mater. Res. Soc. Symp. Proc. 377, 701 (1995).

- Y. Kuo, "Thin-Film Transistors with Multistep Deposited Amorphous Silicon Layers," *Appl. Phys. Lett.* 67, No. 15, 2173 (1995).

- Y. Uchida, H. Kanoh, O. Sugiura, and M. Matsumura, "Hydrogen-Radical Annealing of Chemical Vapor-Deposited Amorphous Silicon Films," *Jpn. J. Appl. Phys.* 29, L2171 (1990).

- Y. Kuo, F. R. Libsch, and A. Gosh, "Electrical and Optical Stress of Self-Aligned a-Photomask Thin Film Transistors," *Proceedings of the First Symposium on Thin* Film Transistor Technologies, Y. Kuo, Ed., PV 92-24, The Electrochemical Society, Pennington, NJ, 1992, pp. 59-69.

- pp. 59-69.

33. Y. Kuo, "Doping Gas Effects on Plasma Enhanced Chemical Vapor Deposition of Heavily Phosphorus-Doped n<sup>+</sup> Silicon Film," *Appl. Phys. Lett.* 71, No. 19 (1997).

- C. J. Mogab and J. H. Levinstein, "Anisotropic Plasma Etching of Polysilicon," J. Vac. Sci. Technol. 17, 721 (1980)

- Y. Kuo and K. Latzko, "Deposition of Highly Conductive n Silicon Film for a-Si:H Thin-Film Transistor," to appear in Mater. Res. Soc. Symp. Proc.—Amorphous and Microcrystalline Silicon Technology, 1998.

- K. Takechi and H. Hayama, "Gated RF-Discharge Plasma-CVD Technology for a-Si:H TFT Fabrication," Proceedings of the Second Symposium on Thin Film Transistor Technologies, Y. Kuo, Ed., PV 94-35, The Electrochemical Society, Pennington, NJ, 1994, pp. 160-173.

- H. Meiling, W. F. van der Weg, and R. E. I. Schropp, "High-Rate a-Si:H TFTs: A Comparative Study," Proceedings of the Third Symposium on Thin Film Transistor Technologies, Y. Kuo, Ed., PV 96-23, The Electrochemical Society, Pennington, NJ, 1996, pp. 146-157.

- Y. Kuo, "Reactive Ion Etching of PECVD Amorphous Silicon and Silicon Nitride Thin Films with Fluorocarbon Gases," J. Electrochem. Soc. 137, No. 4, 1235 (1990).

- Y. Kuo, "Reactive Ion Etching of Plasma Enhanced Chemical Vapor Deposition Amorphous Silicon and

- Silicon Nitride: Feeding Gas Effects," J. Vac. Sci. Technol. A 8, No. 3, 1702 (1990).

- Y. Kuo and M. S. Crowder, "Reactive Ion Etching of PECVD n<sup>+</sup> a-Si:H—Plasma Damage to PECVD Silicon Nitride Film and Application to Thin Film Transistor Preparation," J. Electrochem. Soc. 139, No. 2, 548 (1992).

- 41. Y. Kuo, "Reactive Ion Etching of Sputter Deposited Tantalum with CF<sub>4</sub>, CF<sub>3</sub>Cl, and CHF<sub>3</sub>," *Jpn. J. Appl. Phys.* **32**, No. 1A, 179 (1993).

- Y. Kuo, "Reactive Ion Etching of Sputter Deposited Tantalum Oxide and Its Etch Selectivity to Tantalum," J. Electrochem. Soc. 139, 579 (1992).

- 43. Y. Kuo, "Plasma Etching Mechanism of Metal Oxides Derived from RIE of Ta<sub>2</sub>O<sub>5</sub> and TiO<sub>2</sub>," Proceedings of the Eleventh Symposium on Plasma Processing, G. S. Mathad and M. Meyappan, Eds., PV 96-12, The Electrochemical Society, Pennington, NJ, 1996, pp. 536-544.

- 44. Y. Kuo, "Fundamentals of Dry Etching of Indium Tin Oxide Thin Film," *Sputtering & Plasma Processes* (Japan Technology Transfer Assoc.) 11, No. 5, 9 (1996).

- 45. Y. Kuo, "High Temperature Reactive Ion Etching of Indium Tin Oxide: The Non-Additive Feed Gas Effect," Proceedings of Thin Film Materials, Processes, Reliability, and Applications: Thin Film Processes, G. S. Mathad, M. Meyappan, and M. Engelhardt, Eds., PV 97-30, The Electrochemical Society, Pennington, NJ, 1997, pp. 71-78.

- Y. Kuo, "Anomalous High Rate Reactive Ion Etching Process for Indium Tin Oxide," *Jpn. J. Appl. Phys.* 36, No. 2(5B), L629 (1997).

- Y. Kuo and T. L. Tai, "High Temperature Reactive Ion Etching of Indium Tin Oxide with HBr and CH<sub>4</sub> Mixtures," J. Electrochem. Soc. 145, No. 12, 4313 (1998).

- 48. Y. Kuo, "Factors Affecting the Molybdenum Line Slope by Reactive Ion Etching," *J. Electrochem. Soc.* **137**, No. 6, 1907 (1990).

- R. J. Saia and B. Gorowitz, "Dry Etching of Tapered Contact Holes Using Multilayer Resist," *J. Electrochem.* Soc. 132, 1954 (1985).

- Y. Kuo and J. R. Crowe, "Slope Control of Molybdenum Lines Etched with Reactive Ion Etching," J. Vac. Sci. Technol. A 8, No. 3, 1529 (1990).

- 51. K. Okajima, T. Sato, T. Dohi, and M. Shibata, "MoW Etching Process Using Chemical Dry Etching for Lower Resistive Gate Metal on TFT Large Glass Substrate," Proceedings of the Fourth International Symposium on Sputtering and Plasma Processes, Japan Technology Transfer Assoc., 1997, p. 369.

- S. J. Fonash, "Plasma Processing Damage in Etching and Deposition," *IBM J. Res. Develop.* 43, 103–107 (1999, this issue).

- K. Nakamura, T. Imura, H. Sugai, M. Ohkubo, and K. Ichihara, "High-Speed Etching of Indium-Tin-Oxide Thin Films Using an Inductively Coupled Plasma," *Jpn. J. Appl. Phys.* 33(7B), No. 1, 4438 (1994).

Received December 2, 1997; accepted for publication September 29, 1998

Yue Kuo Thin Film Microelectronics Research Laboratory, Texas A&M University, College Station, Texas 77843 (yuekuo@tamu.edu). Dr. Kuo is Dow Professor of Thin-Film Microelectronics in the Chemical Engineering Department and Professor in the Electrical Engineering Department, Texas A&M University. Previously, while this paper was being written, he was a Research Staff Member in the Thin Film Transistor Liquid Crystal Display Department of the IBM Thomas J. Watson Research Center in Yorktown Heights, New York, Dr. Kuo received a Ph.D. from Columbia University in 1979 and then worked on VLSI MOS and bipolar research and development. After joining IBM in 1987, he worked on thin-film transistor structures and associated plasma-based materials and processes. As a result of that work, he reached two IBM Invention plateaus. He is the primary author of more than 100 papers and three lecture books, has edited four proceedings volumes, has presented more than 80 talks (including 30 invited talks) at professional societies, universities, and industry laboratories, and has organized and chaired numerous international conferences. Dr. Kuo is a Fellow of the Institute of Electrical and Electronics Engineers and a member of the Electrochemical Society and the Materials Research Society.

Kenji Okajima IBM Japan Ltd., Display Technology Inc., Display Business Unit, 800 Ichimiyake, Yasu-cho, Yasu-gun, Shiga-ken, Japan (okajima@cyberti.co.jp). Mr. Okajima is a Deputy Manager in Array Process Engineering No. 2 at the Yasu manufacturing plant. He received a B.S. degree in 1981 and an M.S. degree in 1983, both in electrical engineering, from Gunma University, joining IBM in 1985 to work on semiconductor assurance. In 1992, Mr. Okajima received an IBM Manufacturing Achievement Award for his work in that area. Since 1994, he has worked on array processing for the installation of the phase-2 line, and is currently working on the DTI phase-3 line.

Masatomo Takeichi IBM Japan Ltd., Display Technology Inc., Display Business Unit, 800 Ichimiyake, Yasu-cho, Yasu-gun, Shiga-ken, Japan (y00898@jp.ibm.com, takeichi@yamato.ibm.co.jp). Mr. Takeichi is a Staff Engineer in the LCD Operation Department of the Display Business Unit. He received a B.S. degree in applied chemistry from Tokushima University in 1980. He joined IBM in 1988 and contributed, as a Manufacturing Engineer, to the installation of several plasma-etching processes in an 8-inch silicon wafer production line. He also contributed to the establishment of a new fabrication line in Display Technology Inc. for large-area (550 mm by 640 mm) glass substrates. Mr. Takeichi is currently working on AMLCD manufacturing engineering.