## A onemegapixel reflective spatial light modulator system for holographic storage

by J. L. Sanford P. F. Greier K. H. Yang

M. Lu

R. S. Olyha, Jr.

C. Narayan

J. A. Hoffnagle

P. M. Alt

R. L. Melcher

A prototype reflective spatial light modulator (SLM) system has been developed for writing megabit pages of data into a holographic medium at a rate of 12 pages per minute. The SLM is based upon a crystalline-silicon reflective active-matrix array with integrated data drivers, using liquid crystal (LC) electroptics and a personal computer system with an interface to provide data. The LC has been optimized for high contrast and efficiency with coherent illumination. The resolution-limited contrast was measured at 4:1, which was high enough to provide bit-error-free charge-coupled-device images using modulation and error-correction codes.

#### Introduction

Recent development in spatial light modulators (SLMs) is helping to make volume holographic storage for digital

data a reality [1, 2]. SLMs consist of one- or twodimensional arrays of light-modulating elements. Silicon technology as used in projection data monitors is now capable of producing small-sized, two-dimensional lightvalve arrays having several hundred thousand to several million light-modulating elements. This allows imaging or writing very large amounts of information at one time. Given high image-update rates, high data-writing rates are possible. With increases in the speed of writing and reading with high-speed charge-coupled-device (CCD) cameras, holographic recording may be able to compete with other recording technologies. Efficient compact recording systems are possible through the use of projection-display reflective-silicon light-valve technology [3]. The reflective-silicon light-valve technology has a high aperture ratio and the ability to match its pixel size with the CCD camera pixel size.

The development focus of our prototype holographicrecording reflective SLM system was aimed at 1) suitable light modulation of the LC; 2) the silicon back-plane or

Copyright 1998 by International Business Machines Corporation. Copying in printed form for private use is permitted without payment of royalty provided that (1) each reproduction is done without alteration and (2) the Journal reference and IBM copyright notice are included on the first page. The title and abstract, but no other portions, of this paper may be copied or distributed royalty free without further permission by computer-based and other information-service systems. Permission to republish any other portion of this paper must be obtained from the Editor.

0018-8646/98/\$5.00 © 1998 IBM

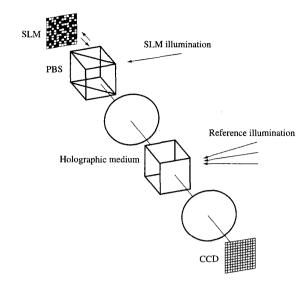

Holographic data storage system diagram in which the SLM is illuminated by and imaged through a polarizing beam splitter into the holographic medium interfering with reference illumination for writing. For reading, only the reference beam is used.

chip design; 3) a system to provide data to the SLM at a sufficient writing rate; and 4) testing of the SLM as it relates to holographic recording.

#### Reflective SLM holographic recording

In developing an SLM system suitable for holographic recording, it is useful to look at how a reflective SLM is used in a holographic recording. Holographic recording is accomplished by the interference of an image beam and a reference laser beam within a holographic recording medium—in this case, a photorefractive material such as LiNbO<sub>3</sub>. The optical interference pattern causes charges to be excited from impurity centers. After diffusion and re-trapping, the redistributed charge forms a grating in the photorefractive medium. Depending upon the medium material, a fixing process for long-term storage of data may be required. When the medium is exposed to only the reference beam, the light will diffract to reproduce the image. Figure 1 shows the basic elements of a holographic data storage system. The spatial light modulator converts the digital data of ones and zeros into a two-dimensional array of bright and dark spots. The Fourier plane image of the array is the image to be stored in the holographic medium. A uniform laser beam is directed in an orthogonal manner onto the reflective surface of the SLM by a polarizing beam splitter (PBS). The PBS allows the polarization-converted image to be focused into the

holographic medium. The reconstructed data are imaged onto a CCD camera system, which detects the reconstructed hologram as digital information. Multiple images comprising a stack can be written separately into the same volume of the holographic medium by changing the angle of the reference beam or by selection of multiple reference beams into the medium. Multiple stacks provide the desired system capacity.

The method of producing the image beam for writing consists of sending data to the SLM while it is addressed by rows from top to bottom. The pixels retain their voltage long enough for the array to be addressed and exposed. The LC must respond to the voltage excitation of the last row in the array before the SLM image is illuminated. To avoid dc voltage across the LC, which may cause image sticking, the polarity of the pixel voltage is reversed in the next frame. The amount of exposure time depends upon the holographic material and on available laser power. The minimum exposure for LiNbO<sub>3</sub> is between 50 and 100 milliseconds.

#### Reflective twisted nematic liquid crystal

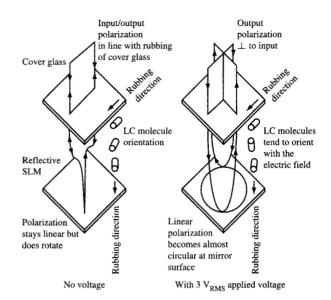

Development was focused on the properties of LC light modulation as it pertains to holographic recording. We concentrated on twisted nematic (TN) normally black (NB) LC modes, since they offer higher contrast with low drive voltages as compared to normally white (NW) modes [4]. The PBS allows efficient illumination and crosspolarization for NB operation with reflective SLMs. The normally black LC crystal mode provides electro-optic modulation by changing the polarization of reflected light by  $90^{\circ}$  with about 3  $V_{\text{RMS}}$  applied, while leaving the polarization unchanged for zero (or low) applied voltage. The cover glass has a transparent indium-tin oxide (ITO) conductor on the inside surface. On the cover-glass ITO and on the SLM mirror surfaces, thin polyimide layers are deposited and rubbed to provide for LC alignment. The LC molecules align with the rubbing direction. The ITO voltage is held constant at 3 V, and a 0-6-V square-wave voltage is applied to the pixel mirrors for LC electro-optic modulation. The equivalent of a transmissive 90°-twisted nematic LC mode is the reflective 45°-twisted nematic LC mode. Figure 2 depicts the reflective 45°-twisted nematic LC operation. The rubbing direction on the mirrors is rotated 45° relative to the rubbing direction on the cover glass, providing a 45° twist in LC alignment between the two surfaces. The incoming polarized illumination is aligned with the rubbing direction of the cover glass. As the incoming illumination passes through the LC, the polarization is rotated 45°. After reflection, the direction of polarization and its rotation are reversed. Upon exiting the SLM, the polarization is the same as the incoming polarization. With applied voltage, the LC molecules try to orient with the electric field, which is perpendicular to

the cover-glass and SLM surfaces. The incident light theoretically becomes nearly circularly polarized as it reaches the mirror. After reflection, polarization becomes nearly linear again as it exits the cell, but is rotated 90°. If perfectly linear, the polarization conversion would be 100% efficient. Efficient polarization conversion for wavelengths and LC materials of interest was obtained by detailed LC modeling, cell fabrication, and evaluation.

#### • LC modeling

Modeling of the electro-optical properties of LC spatial light modulators in order to optimize the modulator qualities in terms of contrast ratio, polarization conversion, and cell-gap fabrication tolerances has become increasingly important, because all relevant parameters may be varied easily and certain relations may be investigated specifically. The computer simulation of the static electro-optical behavior has been done in two steps. First, the orientation of the nematic director as a function of distance from each cell surface has to be computed. The theoretical analysis of the LC director profile in a cell with an applied field has been well documented in the literature [5–7]. We followed the papers by Deuling [6, 7] for the computations of the nematic director profile in the LC cell as a function of applied voltage.

The second step of the simulation deals with light propagation in the quiescent and deformed LC media, which are inhomogeneous and uniaxial. Although many methods have been developed for this application, we have made our computations based on the Jones-matrix method [8] and the  $4 \times 4$  matrix method described by Berreman [9] and by Wohler et al. [10]. We have found that at near normal incidence, the computed polarizationconversion efficiency of the Jones-matrix method, which ignores the reflection due to the interface between any two dielectric media, has a negligible difference from the result of the  $4 \times 4$  matrix method, provided that the reflective SLM has less than 0.5% reflection between the air and the cover-glass window. This is achieved by using antireflection coatings on the glass window and by making the ITO thickness approximately equal to half of the incident wavelength. We have constructed our SLMs to satisfy the latter two conditions. Hence, we have used the Jones-matrix method for both quiescent and deformed SLM states to take advantage of the polarizationconversion efficiency of the quiescent state of the SLM offered by the Jones-matrix method [4]. This facilitates our analysis of the quiescent state as the dark state of the SLM, to estimate the contrast ratio as well as the cell-gap tolerance.

#### Quiescent (uniformly twisted) states

The LC polarization-conversion efficiency is determined by the bright or "on" state behavior, while the LC contrast

### Figure 2

The 45°-twisted reflective LC mode. With no voltage, the LC molecules are aligned parallel with the cover glass and SLM surfaces, and the polarization rotates about 45° from the cover glass to the mirror. The rotation reverses its direction in the reflected path. With applied voltage the LC molecules tend to orient with the electric field, giving nearly circular polarization at the mirror surface. Upon exiting, the polarization rotates 90° and is nearly linear.

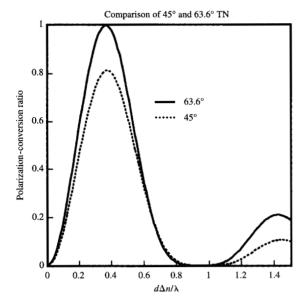

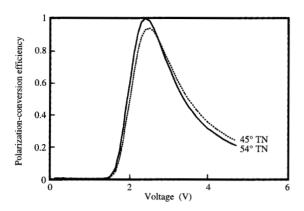

ratio is mostly determined by the dark or "off" state. The dark state of the reflective twisted nematic LC normally black mode is determined by the twist angle and the quantity  $d\Delta n/\lambda$ , where d is the cell gap,  $\Delta n$  is the anisotropy of the index of refraction of the LC material, and  $\lambda$  is the wavelength of the illuminating light. The Jones matrix is used to find an initial design point for different LC twist angles, assuming uniform twisting of LC molecules between the SLM mirror and the cover-glass surfaces. We also assumed that the LC molecules have a small uniform tilt angle (about 2°) from the substrate surface across the LC cell. Figure 3 shows calculated polarization-conversion efficiencies as a function  $d\Delta n/\lambda$ for the 45°- and 63.6°-twisted angles. The polarizationconversion efficiencies are approximately 82% and 100%, respectively. For operation in the normally black mode, liquid crystal cells should be fabricated at the first minimum, where  $d\Delta n/\lambda = \sqrt{1 - (\alpha/\pi)^2}$  and  $\alpha$  is the twist angle; i.e., for  $\alpha = \pi/4$ ,  $d\Delta n/\lambda \simeq 1$ . Test cells built and measured in the deformed states or "field-on" states showed that the 45°-twisted cells had higher polarization-conversion efficiency than 63.6°-twisted cells. This indicated to us that

Quiescent-state simulation of polarization-conversion efficiency with  $d\Delta n/\lambda$ . The 63.6°-twisted nematic LC has nearly 100% conversion efficiency. However, the 63.6°-twisted case has a greater insensitivity to parameter variations in the off state at  $d\Delta n/\lambda = 1$ .

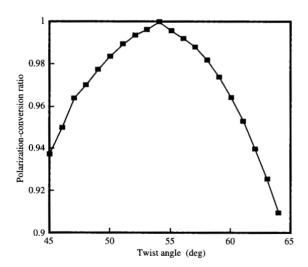

#### Figure 4

Polarization-conversion ratio as function of twist angle using the deformed and tilted-state model. Maximum polarization conversion for LC material chosen occurred at 54°.

we cannot optimize the LC performance on the basis of the quiescent state alone.

Deformed and tilted state (nonuniformly twisted)

The deformed state is characterized by nonuniform tilting and twisting of the LC director. The director tries to align with the applied electric field but is constrained at the surfaces, so the orientation in the middle of the cell is a balance between the electric driving force and the elastic restraining forces. The resulting configuration is different from the quiescent configuration, as is the polarizationconversion behavior. The polarization-conversion efficiencies based upon deformed states as a function of the twist angle of the quiescent LC cell are shown in Figure 4. The conversion efficiency as a function of voltage is shown in Figure 5. Both figures show a polarization-conversion efficiency of approximately 93% and 100% for the 45°- and 54°-twisted angles, respectively. Both twist angles have contrast better than 200:1 with ±7% dark-state assembly tolerance. Assembled SLMs have also shown that the 54°-twisted nematic LC has excellent efficiency, as well as large-area contrast with good assembly tolerance.

#### Resolution-limited contrast

Large-area contrast is an important measure of cell uniformity and process control and is very important in display applications. For holographic storage, resolution-limited contrast rather than large-area contrast is a more useful design criterion, since the data being stored may not be images and may lack spatial correlation. The use of modulation, interleaving, and error-correction codes further reduces the spatial coherence of the SLM image.

Typically, even SLMs having high large-area (all-on to all-off) contrast (>100:1) will have much lower (about 4:1) pixel-resolution-limited (adjacent-pixel-on-to-off) contrast. The difference is due to a variety of effects, including scattered light from irregularities in the cell at the subpixel level; three-dimensional effects due to size and placement of spacer posts and to LC disclinations arising from the resulting fringing electric field at the pixel edges; electrical crosstalk between adjacent pixels; and index mismatching of the layers within the LC cell with the use of coherent illumination. Scattering, index mismatching, and three-dimensional effects appear to dominate the resolution-limited contrast in twisted nematic liquid crystal SLMs.

- Scattered light from irregularities in the cell can be reduced with improvements in via design, mirror design, metallurgy, and fabrication [11].

- The decision to use the normally black mode was fundamental to reducing the impact of three-

#### Flattre 5

Deformed and tilted-state polarization-conversion efficiency as a function of voltage. The  $54^{\circ}$ -twisted reflectance is nearly 100% compared to 93% for the  $45^{\circ}$ -twisted case.

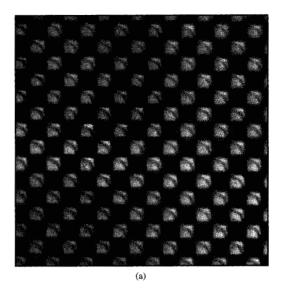

dimensional effects (disclinations) on the large-area contrast ratio. The disclinations affect the on-pixel brightness but not the off-pixel dark level. In addition, we have observed that the impact of disclinations on resolution-limited contrast is a function of the field difference between adjacent on and off pixels. Improvement in resolution-limited contrast has been obtained by driving all of the pixels in one frame with the same polarity and optimizing the off-pixel voltage to reduce the on-to-off-pixel voltage difference. Unlike displays, holographic storage is not sensitive to flicker, eliminating the need for row-, column-, or pixel-voltage polarity inversion. As a result, the zero electric field between pixels having the same optical state provided by frame inversion is used to eliminate the disclinations. As shown in Figure 6, if the off-pixel voltage is increased from  $0 V_{RMS}$  to 1.5  $V_{RMS}$ , the disclinations are reduced in size and move into the space between the mirrors. The disclinations are virtually eliminated while providing an improvement in the resolution-limited contrast.

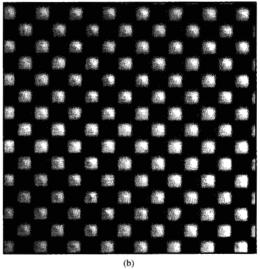

To further understand and quantify the sources of scattered light, confocal microscopy [12] has been used. The confocal microscope provides very high-resolution images using a scanning laser and a linear CCD array. The very low numerical aperture of the system does not allow most of the scattered light to be detected. To first order, the point-by-point variation in intensity of the sum of images with and without a quarter-wave plate is due to absorption and scattering. Lasertech Model 1LM21 H confocal microscope images of a 45° TN SLM with and

#### Elemen.

One-pixel checkerboard pattern shown with off-state voltages of (a) 0  $V_{RMS}$  and (b) 1.5  $V_{RMS}$ . The on-pixel disclinations are virtually eliminated and the image is 50% brighter in (b).

without a quarter-wave plate at best focus are shown in Figure 7. A repeated pattern having one pixel driven on at 3.1  $V_{RMS}$  with surrounding pixels driven at 0  $V_{RMS}$  is shown. The disclinations through the pixel and field-effect-illuminated regions around the pixel can be seen in the image without the quarter-wave plate. The via connecting the mirror and hillocks in the aluminum mirror surface are clearly shown in the quarter-wave-plate image. A bitmap-image-manipulation software program was used to

# (a) Confocal microscope image of a 3.1-V<sub>RMS</sub> on pixel surrounded by 0-V<sub>RMS</sub> off pixels. (b) Same image but with a quarter-wave plate.

produce the scattered and absorbed light image in Figure 8. On an image point-by-point basis, the two images in Figure 7 were added and the difference from maximum intensity obtained. The outline of the mirrors, disclinations, mirror via, mirror hillocks, and leading-edge rubbing-direction effects at the left and bottom edges of the on-pixels are seen as bright areas. The circular object visible in the lower left corner of the image is a spacer post used to control the cell gap. The edges of the spacer post also contribute to scattered light.

Pixel-to-pixel electrical crosstalk is not observed in our SLMs, apparently owing to the use of a fixed-potential-connected conductive light-absorbing layer just under the mirrors and a ground-connected substrate.

Initial characterization of 45°-twisted SLMs using coherent illumination revealed nonuniformity as high as 25%. Adding a broadband antireflection coating to the top glass virtually eliminated the interference of long-

Computed image showing scattered and absorbed light (lighter areas) using confocal microscope image with and without a quarterwave plate. (See text for further discussion.)

coherence-length light that reflected off the SLM cover glass and the bottom surface of the polarizing beam splitter. However, 5% ringlike nonuniformity remained. A second source of interference was found to be a result of cell-gap variation. A spectral scan was performed on an unexcited 45°-twisted SLM using an analyzer parallel to the polarized incident illumination. It showed 10-20% intensity ripples with a peak-to-peak spacing of 7% of the wavelength. These are Fabry-Perot peaks arising within the SLM due to optical index mismatch at the LC/ITO interface. The ripple intensity was a minimum at about 550 nm, which corresponds to the half-wave design thickness of the ITO. Similarly, if the cell gap varies with a single wavelength, this is equivalent to a wavelength shift and can produce similar levels of nonuniformity. We performed an interference analysis as a function of wavelength and cell-gap variation. The optical pathdifference analysis with wavelength gave  $\Delta \lambda = \lambda^2/(2nd)$ = 0.041  $\mu$ m for interference for a cell gap  $d = 3 \mu$ m, wavelength  $\lambda = 0.6 \mu m$ , and LC index of refraction n = 1.5. This agrees well with the observed peak-to-peak ripple spacing observed. Similarly, interference occurs with a change in cell gap,  $\Delta d = \lambda/(2n)$ , or 0.2  $\mu$ m. The variation in cell gap corresponds to a 6.9% change in cell gap, which implies a need for cell-gap control of better than 3.5%. When voltage is applied to produce an on state, the effective LC index of refraction changes from 1.5 to 1.6, resulting in both  $\Delta\lambda$  and  $\Delta d$  values that are 6% lower. Improved cell-gap control to within the above tolerances has eliminated the remaining 5% nonuniformity.

#### Switching times

The LC switching time is also important since, along with the SLM addressing and exposure times, it determines the SLM image-writing rate. The 45°-twisted-angle TN LC mode was found to have a 0%–90% or 100%–10% response time of about 20 ms at room temperature. At present, this LC speed is consistent with the requirements of the holographic storage media, but with need in the future for higher writing speed, faster LC modes will be required. The TN LC switching speed increases with rising temperature, and LC-response-limited frame rates up to 100 Hz at 50°C appear possible with the 54° TN mode.

While other nematic LCs with faster switching times have been reported [13, 14], the fastest LC switching times are achieved with ferroelectric liquid crystal (FLC) materials [15]. Surface-stabilized FLC materials have binary optical states and high contrast, and do not have twisted nematic disclination-like structures. However, the submicron gaps for FLC cells are very difficult to fabricate. FLC is also difficult to drive with an ordinary active-matrix array, since the cell capacitor must provide the polarization charge for complete switching. The requirement for an inverted or complementary image for charge compensation requires that the illumination be shuttered off during the image-reversal period, which reduces the effective page-writing rate by half. Since higher-recording-speed materials do not exist at this time, these issues have not been fully addressed.

#### Chip design

The fabrication technology used for the one-megapixel SLM is identical to the reflective liquid crystal light-valve-array technology developed for projection displays [16]. Unlike gray-scale-display light-valve designs, the design of an SLM suitable for holographic data storage uses only bilevel information. This simplifies the integration of both row and column drivers with the array. The potential for contrast, efficiency, speed, and uniformity in the LC is constrained by silicon technology voltage limits and pixel size requirements.

The technology used for fabricating the SLM chip was based upon a 1.2-\$\mu m\$, 5-V CMOS process modified for 10 V and two levels of polysilicon. A 10-V gate driver was needed to write 0-6-V pixel voltages. A modified 0.8-\$\mu m\$ process was incorporated for the second- and third-level metal. The second-level metal was dedicated to absorbing light passing through the spacing between mirrors. The third-level metal was dedicated for the mirrors. This left only one level of metal for general-purpose wiring. The thin-film patterning of the chip fabrication produces nearly 1 \$\mu m\$ of bow in the chip. Patterned SiO\_2 spacers were chosen for LC gap control for their strength and precise dimensional control. Design rules were also modified for 1× lithography, which allowed the fabrication of large chips.

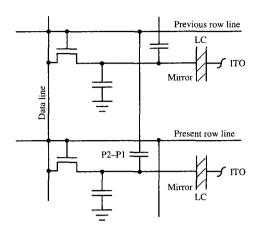

#### anne s

Equivalent pixel cell circuit consisting of an n-FET and two capacitors. The grounded capacitance is composed of stray and diffusion capacitance. The P2-P1 capacitor is a second-layer-polysilicon capacitance to the first-layer-polysilicon previous row line

The holographic spatial light-modulator chip consists of an active-matrix array, row drivers at both the left and right sides of the array, and column drivers. In conventional active-matrix addressing, the rows are selected one at a time from top to bottom of the array. The data presented on the column lines are written in the pixels of the selected row. As shown in Figure 9, the active-matrix pixel circuit is essentially a DRAM circuit. It consists of a single n-FET transistor whose gate is connected to a row line. The source is connected to a data line and the drain is connected to the mirror electrode. Approximately half of the drain-connected storage capacitance is formed by coupling the second level of polysilicon to a first polysilicon layer that functions as the previous row line. The cell storage capacitance was estimated to be about 75 fF. The cell size was minimized, given the process ground rules. The resulting cell pitch was 15.6 µm. Both row- and column-driver circuits were designed to match that cell pitch.

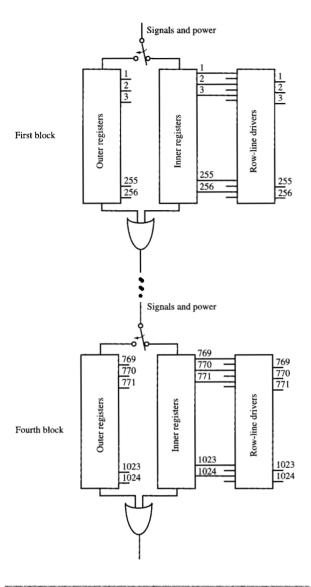

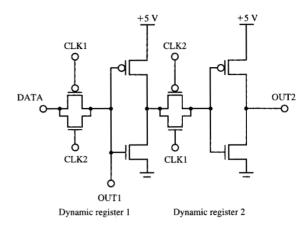

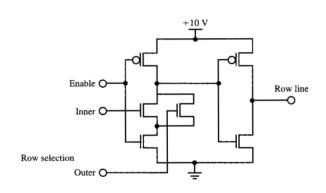

Row drivers drive both ends of each row to maximize the addressing rate using resistive polysilicon row lines. An improvement in line settling time by a factor of 4 is obtained by driving both ends. Redundancy was used in the row-selection data path. As shown in **Figure 10**, the row-driver circuit has four blocks of 256-row-selection circuitry. Each block has two groups of row-selection circuits. The inner group is used by default, but if it does not function, the outer group can be selected by grounding the appropriate input. The output of each

The row-selection circuitry is composed of one dynamic register per row. The odd-row selection is achieved by using the inverter input of the dynamic register, while the even-row register output is the inverter output.

#### Figure 10

Overall arrangement of the row-driver circuitry. The row-selection circuitry consists of four 256-row-selection blocks, each containing an inner and outer group. The inner group is selected by default. An input signal can select the outer group if the inner group of registers fail.

group's row-selection data path is connected to an OR gate for signal propagation to the next block. One dynamic register is used for each row-selection circuit. The dynamic register consists of a complementary-clocked transmission gate for coupling data to an inverter. As shown in **Figure 11**, for odd-numbered rows, the inverter input is used for row-selection output, while for even rows, the inverter output is used. Use of the inverter input is possible if no other asynchronous transmission gates are

### Figure 12

The row-line driver circuit is a clocked OR gate. The enable input provides the clocking function. When both enable input and either of the inner or outer row-selection inputs are high, the inverter input is pulled low, driving the row line high to 10 V. To pull the row line low, the enable input must be low.

connected. Out-of-phase clock signals to the odd and even dynamic registers are used to shift the row-selection data. This arrangement inherently provides for row-line precharging, since row-selection data exist in two adjacent circuits.

The row-line driver circuit consists of an ENABLE-signal clocked-OR level-shifting circuit, as shown in **Figure 12**. The dynamic circuit relies on a low-level ENABLE signal to reset the circuit by pulling up the input

to the output inverter, thereby maintaining a low state on the row line. The high-level ENABLE state allows the row line to be driven high with a high row-selection input state. Edge control of two ENABLE signals, one for odd and one for even lines, allows control of row-line precharging and row-line turnoff.

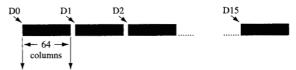

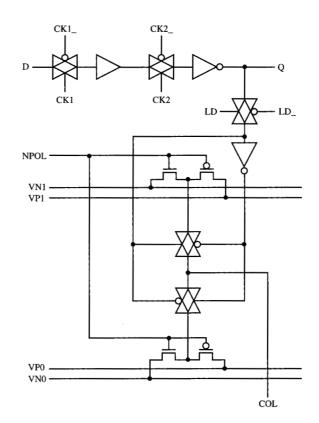

The function of the column driver is to connect one of four reference voltages to the column line. Which reference is selected depends upon whether the data bit is logical 1 or 0 and whether the polarity input is 1 or 0. The overall organization of the row drivers is shown in Figure 13. Sixteen inputs provide data to sixteen 64-bit shift registers. Each bit in the 64-bit shift register provides data for an adjacent column line. The data-shifting direction is from left to right. To address 100 frames per second with data continuously supplied, a relatively low (6.5-MHz) clock rate is required. Two polarity-controlling inputs, each connecting only even- or odd-numbered columns, were incorporated to allow frame, row, column, or pixel inversion. Figure 14 shows the data-driver circuit. The data shift register consists of two dynamic registers connected in series. Each dynamic register consists of a complementary transmission gate and an inverter. CK2 is the inversion of CK1. The data-loading register uses the same dynamic register design as that used in the data shift register. Both the input and the output of the inverter in the load register are used to drive transmission gates for the reference-selection circuitry. Two p-FET transistors are used for positive-reference selection, and the two n-FETs are used for negative-reference selection. If NPOL is high, the negative frame references are selected; otherwise, the positive frame references are selected. Two complementary transmission gates were used to connect the "on" (VN1 or VP1) or "off" (VP0 or VN0) reference to the data line.

Simulations of the row-driver circuits driving the polysilicon row lines gave a worst-case row rise and fall time of approximately 1 µs. The 0%-90% rise time and 100%-10% fall time at the ends of the row lines were each less than 100 ns. However, the row-line skew time, the end-to-middle row-line transition time difference, was approximately 1  $\mu$ s. Data-driver simulations show that the 0-7-V, 0%-90% rise time was also 1  $\mu$ s. Using just the rise time as the time needed for the LC voltage would not deliver the full RMS voltage to the pixel. The data-driver circuit takes nearly 3 µs to settle to within 10 mV, which would be sufficient for 4-bit gray-level operation. However, such accuracy may not be needed in a binary holographic storage application. An error of 100 mV corresponding to 2  $\mu$ s may be acceptable. The data driver was simulated with 20-MHz clock rates.

If not limited by data-driver shift rates, the sum of rowline skew (1  $\mu$ s) and data-line settling time (2  $\mu$ s) times the number of rows (1024) determines the minimum Shift-register column drivers

- 1. Shift in 16 data blocks in parallel (64 clocks).

- 2. Generate load pulse to output data to drivers.

#### Figure 13

Diagram of data- or column-driver arrangement. The 16 groups of drivers have 64 adjacent drivers each. Data are shifted in from left to right and loaded to the column-driver output circuitry. Row addressing is incremented for writing to subsequent rows.

#### Figure 14

The integrated column-driver circuit consists of two dynamic registers forming a two-phase shift register; a dynamic register functioning as a holding latch; NPOL input-gate-driven transistors for positive (VP) or negative (VN) polarity reference selection; and two transmission gates for high (on or 1) and low (off or 0) state reference selection.

Photograph of the SLM card, in which epoxy is used to attach the SLM to a black anodized aluminum holder (not visible) held in place with screws. Wire bonds are used to connect the SLM chip to the card, and epoxy on the wire bonds is used for protection.

time (3.1 ms) required to address the array. The minimum address time provides a writing rate of about 300 frames per second using continuously clocked data at 20 MHz.

#### Assembly and packaging

The LC cell process steps for the cover glass and silicon chip are, in sequence, inspection, cleaning, polyimide (PI) coating, PI pre-baking, PI final baking, buffing the PI films with a cotton cloth on a wheel, and cleaning. Peripheral sealant is then dispensed on the cover glass to form the surround for the LC cavity. The cover glass and the silicon chip are assembled into the LC cell with a bottom glass support for the silicon chip with a UV-curable glue between the support and the chip. Pressure is applied to the cover and bottom glass during curing. The cell gap is measured at the four corners and in the center by spectral interference [17]. The assembly is placed in a vacuum chamber for LC fill. The next step is the sealing of the injection hole with UV-curable glue. Afterward, cell-gap uniformity is checked using normally incident monochromatic light with a sheet polarizer placed on top of the cell and observing the fringes. One fringe corresponds to a variation in cell gap of about 0.2  $\mu$ m.

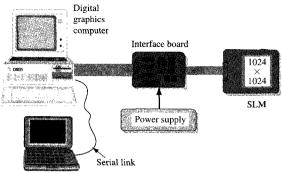

User interface computer

#### Figura 18

System configuration showing a remote-user-interface portable computer linked to a host computer via a serial link. The host computer has the digital and CRT-out display adapter and data-translation software running to supply data to the SLM in an appropriate manner.

Finally, the cell is tested as a function of applied voltage in which the reflected polarization conversion is measured with a photodiode.

The packaging of the SLM involves integrating the assembled liquid crystal cell onto an electronic card having a connector that is used for communication between an interface card and the SLM. The SLM is housed on an aluminum base assembly and anchored in place with a low-temperature-curing epoxy. This subassembly is attached to the card with four screws that have adequate clearance to permit the relative positioning of the card with respect to the SLM so that the wire-bonding pads on the two parts are aligned. The screws are then tightened to hold the pieces in alignment. The electrical connection between the silicon chip and the card is accomplished by wire bonding directly from the aluminum pads on the chip to gold-coated wire-bond pads on the card. This is the first example of a simplified light-valve or SLM package in which the SLM is directly connected to the gold-coated pads on the circuit board, eliminating the need for an intermediate flex circuit. Figure 15 is a photograph of the packaged assembly. A black anodized aluminum frame and base plate serve not only to mechanically attach the SLM to the card but as a means to mount and align the SLM in an optical system.

#### Data control and interface electronics

As shown in **Figure 16**, the approach for supplying data uses two computers; a remote-user-interface computer is connected by an RS-232 interface to a host PCI bus

One row of display pixel data (raster-scan format)

Shift-register column drivers

#### Figure 17

The 64th bit in each image block is translated to the first position in the frame-buffer image to account for the SLM data-driver data shifting direction.

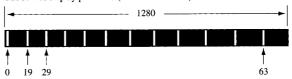

computer with an SXGA graphics display adapter having both digital and analog outputs. A laptop running Visual Basic graphical user interface programs under Windows\*\* 3.1, 95, or NT was used as the remote computer. The display adapter software on the host computer runs from DOS and requires no other operating system. A host program was written to map or translate an SLM image into the frame-buffer image in the display adapter. This allows data to be written correctly to the SLM. The twostep process required that the proper 16 bits for the SLM data-driver inputs be extracted from the  $1024 \times 1024 \times 1$ SLM data image and positioned properly in the 1280  $\times$  $1024 \times 24$ -bit frame buffer for transfer. Figure 17 shows that the left-to-right shift direction of the SLM columndriver data requires the data to be reversed in the frame buffer, since the frame-buffer contents are output in raster fashion from left to right. The 16 bits of SLM input data are remapped as a single 24-bit frame-buffer pixel.

Figure 18 illustrates that the SLM frame-buffer pixel data for one SLM row are separated every 20 frame-buffer pixels across the frame-buffer row. Reduction in the data separation has allowed encoding three and four SLM lines into a single frame-buffer line.

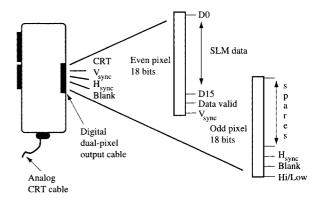

As shown in **Figure 19**, the digital output of the graphics card supplies dual, adjacent-color pixel data at 55 MHz. Only the even-pixel data outputs are used to provide data to the SLM. Each pixel output contains 24 bits of data; 16 are assigned as SLM data bits, two bits are used for the data-valid signal (providing clock edges for the SLM data) and SLM vertical sync, and the rest are unused. Two bits from the odd-pixel outputs are used for SLM horizontal sync and blanking. The third bit is

One row of display pixel data (raster-scan format)

Locate 16 bits of SLM data at every 20th pixel in VRAM (64 locations  $\times$  16 bits = one row of SLM data) Repeat the above for 1024 rows of SLM data

#### Entre 14

SLM data spacing relative to frame-buffer pixels for one SLM frame encoded into the frame buffer. The SLM pixel data are separated by 20 frame-buffer pixels.

Digital output of the display adapter card. Only even pixel-bit outputs are used with SLM pixel data. Four other signals are used for SLM timing. The Hi/Low signal is used here to indicate high-or low-speed SLM addressing.

optional and is used for low- and high-speed addressing rates. Shown in Figure 20 is the method used to provide two SLM data and timing-signal frames in the frame buffer. Each frame-buffer row provides three rows of SLM data. The SLM horizontal synchronizing signal (H) precedes each SLM data row, the SLM blanking signal (B) appears at the end of the frame buffer, and the SLM vertical sync signal is a full frame-buffer row preceding each frame of SLM data.

An interface card between the display adapter and the SLM is needed to convert the SLM horizontal, vertical, and blanking signals into row-selection data, row-clock, row-enable, data-clock, data-load, and frame-polarity

Method by which the SLM data and timing signals are written to the frame buffer of a PCI bus SXGA display adapter. The data for 16 SLM pixels are written to one 24-bit frame-buffer pixel. The SLM timing horizontal sync (H), vertical sync, and blanking (B) signals are interspersed.

signals. This is accomplished using a field-programmable gate array. A shutdown feature is provided to protect for over and under +5-V and +10-V input power. The interface card also contains the four reference voltages for the data drivers.

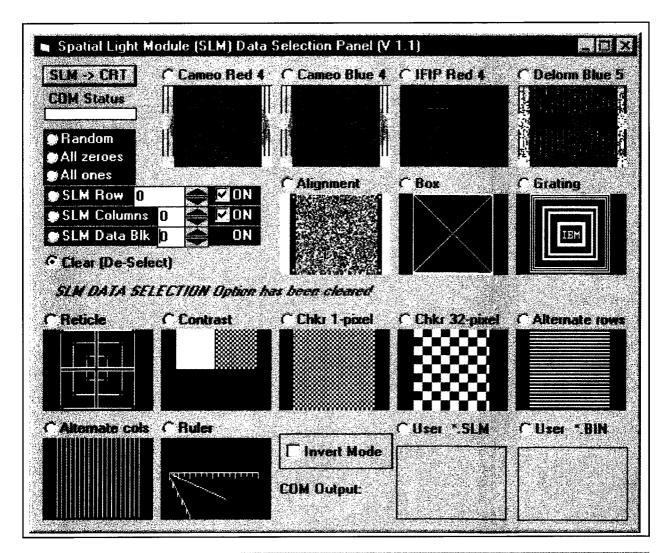

The remote-host graphical user interface consists of three screens. The first is the SLM User Interface, which is used to translate different image data types into a frame-buffer SLM data image. The second and most useful interface is the SLM Data Selection Panel, as shown in Figure 21. Most of the data-selection options were used for testing the SLM system. The user \*.SLM and \*.BIN options allow the user to specify lists of image files to be displayed. A third user interface panel is the SLM Pixel Write Utility for manually writing any arbitrary

pixel data pattern anywhere in the  $1024 \times 1024$  array, pixel by pixel.

The data translation software, graphical user interfaces, and an SLM interface card allow dynamic SLM verification with arbitrary images. With two SLM frames loaded into the frame buffer, an update of five different images per second has been demonstrated using a 90-MHz Pentium computer. With one SLM image loaded into the frame buffer, rates of 12 different images per second have been demonstrated. The rate is higher, since less information is written to the display adapter. However, since the frame-buffer writing process is asynchronous and does not take exactly an even number of frames, LC charge imbalance could occur. To avoid this, a 50% on/off-pixel data requirement over some predetermined

422

Graphical user interface developed for controlling data patterns to SLM. Sequential page patterns are obtained by selecting the User \*.SLM or \*.BIN buttons.

number of images would have to be encoded. This restriction can be circumvented by encoding two (one positive- and one negative-polarity) SLM frames into the frame buffer and updating both positive- and negative-polarity SLM pixel data simultaneously. Finally, three SLM frames were loaded into the frame buffer and were used to determine whether the SLM would function properly with a 180-Hz frame addressing rate and a 28-MHz data clock. If data could be provided continuously, the 28-MHz clock rate would correspond to an addressing rate of 430 frames per second. At this rate, nearly perfect images were obtained, but data chatter and data-driver block boundaries were observed.

This system is not limited to just encoding three SLM frames into the frame buffer. The SLM interface card can be modified to allow the odd-pixel spares in the adapter to be used for SLM data. If the data-valid signal edges were used, SLM data could be positioned on adjacent frame-buffer pixel positions. This would allow up to 12 SLM frames to be written for each frame image. The 12 SLM frames could comprise six separate images for a burst writing rate of 240 pages per second. However, the average page-writing rate is limited by being able to write only one byte at a time to the frame buffer and associated adapter card, and also by PC system clock rates.

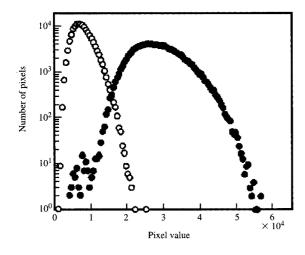

Histogram of the CCD 16-bit digital output pixel value to a 256-kilobit data page, displayed on the SLM and pixel-matched to a CCD camera. Open circles denote off pixels; closed circles denote on pixels.

#### **CCD** imaging test results

To test the suitability of the SLMs for holographic data storage, two SLM assemblies were viewed under conditions similar to those of a holographic storage system with a pixel-matched CCD camera. The collimated beam from an argon-ion laser (514 nm) illuminated the SLMs through a polarizing beam-splitting cube, which served as both polarizer and analyzer, and the light transmitted through the analyzer was imaged onto a CCD camera with  $1536 \times 1024$  pixels, a 100% pixel fill factor, and 16-bit gray-scale resolution. Because the pixel pitch of the CCD  $(9 \mu m)$  did not match that of the SLM, a commercial photographic macro lens (f = 60 mm, aperture f/2.8) was used to demagnify the SLM image by a factor of 15.6/9, so that each SLM pixel was imaged onto one CCD pixel. In principle, this approach allows the inspection of the entire SLM in one operation. By applying various test patterns, it is possible to characterize response uniformity and contrast at all spatial frequencies. In this experiment, the use of an off-the-shelf objective lens limited the performance of the test system: The observed uniformity and point-spread function were degraded because of vignetting in the lens and uncompensated spherical aberration introduced by the beam-splitting cube. Also, the optical magnification was adjusted to an accuracy of only about 0.05%, or one quarter of a pixel. With custom optics and careful optomechanical design, it is possible to achieve considerably more accurate pixel matching

and more uniform illumination [18]. Hence, these measurements represent a lower limit for the performance of which the SLM is capable.

Despite the limitations of the optics, it was possible to show that the performance of the SLMs at high spatial frequencies was adequate to encode binary data for holographic storage. To minimize the impact of the imperfections in the viewing optics, and to avoid a few defective pixels on the SLMs, data patterns were programmed in a 512  $\times$  512-pixel region at the center of the SLMs. This represents an error of about one tenth of a pixel, assuming perfect alignment of the SLM pixels to the CCD pixels. Restricting the measurements to a  $512 \times 512$ -pixel region in this test setup is representative of an actual recording system having registration to one tenth of a pixel. Figure 22 shows the response of the CCD camera to a data pattern encoded using a balanced modulation code [19] and a Reed-Solomon errorcorrecting code. Comparable results were obtained for both of the tested SLMs. Ideally, the CCD pixels viewing "on" SLM pixels (closed circles) would see a uniformly high light level, while those viewing "off" SLM pixels (open circles) would see a uniformly low light level. In reality, finite SLM contrast, optical imperfections, misalignment, and diffraction all act to broaden the ideal response. Where the on and off distributions overlap, the input data cannot be reconstructed on the basis of CCD response alone; this applies to 0.8% of the pixels in Figure 22. However, by using the information in the modulation and error-correcting codes, the original data could be recovered without any errors.

#### **Concluding remarks**

A one-megapixel SLM specifically designed for the holographic storage application has been designed and built. The writing capability of the reflective SLM produced bit-error-free CCD images using error-correction and modulation codes. Special antireflection coatings and cell-gap control of better than 0.1  $\mu$ m are needed to minimize interference using coherent monochromatic illumination. Adequate (4:1) resolution-limited contrast has been achieved by using frame inversion and minimizing the on-to-off-state voltage difference. While the 54° TN LC response speed is only about 20 ms. present holographic material recording rates are even slower. Data were clocked into the SLM at an equivalent rate of 300 frames per second. A system providing SLM data using a display adapter and an interface card was used to write arbitrary data to the SLM. SLM page-writing rates of up to 12 pages per second were demonstrated, which is also about the maximum page-writing rate for iron-doped LiNbO<sub>3</sub>.

#### **Acknowledgments**

Several individuals helped make the one-megapixel SLM system possible: Jagat Mavani, Steven Kosonocky, and Arthur Bright helped with chip design and layout. Steven Lovas, Harold Ifill, Ray Horton, and Keith Fogel provided assistance with the SLM packaging design and assembly. Evan Colgan arranged and operated the confocal microscope, and Ken Ho helped with the scattered-light confocal microscope image manipulation.

This research was performed as part of the Holographic Data Storage System (HDSS) consortium for the National Storage Industry Consortium. We wish to thank the other members of the HDSS consortium for numerous technical discussions and the Defense Advanced Research Projects Agency for financial support under Contract No. MDA-972-95-3-0004.

#### References

- John F. Heanue, Matthew C. Bashaw, and Lambertus Hesselink, "Volume Holographic Storage and Retrieval of Digital Data," Science 26, 749-752 (August 5, 1994).

- Demetri Psaltis and Fai Mok, "Holographic Memories," Scientific American, pp. 70-76 (November 1995).

- R. L. Melcher, P. M. Alt, D. B. Dove, T. M. Cipolla, E. G. Colgan, F. E. Doany, K. Enami, K. C. Ho, I. Lovas, C. Narayan, R. S. Olyha, Jr., C. G. Powell, A. E. Rosenbluth, J. L. Sanford, E. S. Schlig, R. N. Singh, T. Tomooka, M. Uda, and K. H. Yang, "Design and Fabrication of a Prototype Projection Data Monitor with High Information Content," *IBM J. Res. Develop.* 42, 321–338 (1998, this issue).

- K. H. Yang and M. Lu, "Nematic LC Modes and LC Phase Gratings for Reflective Spatial Light Modulators," IBM J. Res. Develop. 42, 401-410 (1998, this issue).

- 5. D. W. Berreman, Phil. Trans. R. Soc. A 309, 203 (1983).

- 6. H. J. Deuling, Mol. Cryst. Liq. Cryst. 19, 123 (1972).

- 7. H. J. Deuling, Mol. Cryst. Liq. Cryst. 27, 81 (1983).

- 8. R. C. Jones, J. Opt. Soc. Amer. 32, 486 (1942).

- D. W. Berreman, J. Opt. Soc. Amer. 62, 502 (1972); Ibid. 63, 1374 (1973).

- H. Wohler, G. Haas, M. Fritsch, and D. A. Mlynski, J. Opt. Soc. Amer. A 5, 1554 (1988).

- 11. E. G. Colgan and M. Uda, "On-Chip Metallization Layers for Reflective Light Valves," *IBM J. Res. Develop.* **42**, 339-345 (1998, this issue).

- 12. D. Awamura, T. Ode, and M. Yonezawa, "Scanning Color Laser Microscope," *Proc. SPIE* **921**, 388–394 (1988).

- S.-T. Wu and C.-S. Wu, "High-Brightness Projection Displays Using Mixed-Mode Twisted-Nematic Liquid-Crystal Cells," *Digest of Technical Papers*, Society for Information Display International Symposium, May 12–17, 1966, pp. 763–766.

- Peter Janssen, Viktor Konovalov, Anatoli Muravski, and Sergei Yakoevnko, "Fast Responding Liquid Crystal Light Valve Technology for Color Sequential Display Applications," *Proc. SPIE* 2795, 141–149 (1996).

- N. A. Clark and S. T. Lagerwall, Appl. Phys. Lett. 36, 899 (1980).

- J. L. Sanford, E. S. Schlig, T. Tomooka, K. Enami, and F. R. Libsch, "Silicon Light-Valve Array Chip for High-Resolution Reflective Liquid Crystal Projection Displays," *IBM J. Res. Develop.* 42, 347–358 (1998, this issue).

- 17. K. H. Yang, J. Appl. Phys. 64, 4780 (1988).

- M.-P. Bernal, H. Coufal, R. K. Grygier, J. A. Hoffnagle, C. M. Jefferson, R. M. Macfarlane, R. M. Shelby, P. Wimmer, and G. Witmann, "A Precision Tester for Studies of Holographic Optical Storage Materials and Recording Physics," Appl. Opt. 35, 2360 (1996).

- G. W. Burr, J. Ashley, H. Coufal, R. K. Grygier, J. A. Hoffnagle, C. M. Jefferson, and B. Marcus, "Modulation Coding for Pixel-Matched Holographic Data Storage," Opt. Lett., in press.

Received March 17, 1997; accepted for publication March 16, 1998

James L. Sanford IBM Research Division, Thomas J. Watson Research Center, P.O. Box 218, Yorktown Heights, New York 10598 (sanfordj@us.ibm.com). Mr. Sanford is a Senior Engineer in the Flat Panel Display Technologies Department at the IBM Thomas J. Watson Research Center. He received a B.S.E.E. degree from the Ohio State University in 1972, joining IBM that same year at the Office Products Division, Lexington, Kentucky. His work has involved various aspects of electronic circuits, printers, and displays. His present interests are in circuits for active-matrix displays, projection displays, and related applications. IBM honors received by him include an Outstanding Technical Achievement Award, a Research Division Group Award, and two Invention Achievement Awards. He is a member of the Society for Information Display.

Paul F. Greier IBM Research Division, Thomas J. Watson Research Center, P.O. Box 218, Yorktown Heights, New York 10598 (greier@us.ibm.com). Mr. Greier joined IBM at the Thomas J. Watson Research Center in 1966, and was engaged in digital interface logic design and laboratory automation. He moved to systems programming in 1978, developing VM host bi-synch communications software for distributed dataacquisition systems. He received the B.S. in mathematics from Mercy College in 1980 and the M.S. in computer science from the Polytechnic Institute of New York in 1982. Mr. Greier became involved in automated testing, developing test software for Josephson devices in 1982 and 1983; he was responsible for the functional testing of VLSI memories and logic until accepting an appointment to the Computer Science Department of New Mexico State University through IBM's Faculty Loan Program for the 1989-1990 academic year, teaching computer programming and computer architecture. Mr. Greier returned to Yorktown and was responsible for software development in various advanced development projects until becoming involved in the hardware and software support of flat-panel display systems in 1994.

Kei-Hsiung Yang (K. H. Yang) IBM Research Division, Thomas J. Watson Research Center, P.O. Box 218, Yorktown Heights, New York 10598 (kyang@us.ibm.com). Dr. Yang received his B.S. in physics from the National Taiwan University, his M.S. from the University of Notre Dame, and his Ph.D. from the University of California at Berkeley in 1974. He joined the IBM Thomas J. Watson Research Center in 1979 as a Research Staff Member; his work in LCD research has included wide-viewing-angle technologies for TFT/LCD, Si-wafer-based LCLVs for reflective projection displays and holographic optical storage, ferroelectric LC devices, TN electro-optics, LC-to-surface anchoring

properties, and the transport properties of LC cells. In 1987, he worked at Toshiba Development Laboratories at Shin-Sugita, Japan, for three months as a member of the IBM-Toshiba TFT/LCD joint development team. Prior to joining IBM, Dr. Yang worked at the General Electric R&D Center (1973-1979) in Schenectady, New York; at the Bell Telephone Laboratories (1969) in Murray Hill, New Jersey; and at the Lawrence Livermore Laboratories (1969-1973) in Berkeley, California. Dr. Yang has received a GE Centennial Patent Award, four IBM Invention Achievement Awards, and an IBM Research Division Group Award. He has 16 U.S. patents and nine patents pending, and more than 50 publications in the fields of liquid crystal devices, electrophoretic displays, VUV-fluorescent solids, X-ray imagers for breast cancer diagnosis, and nonlinear optics. Dr. Yang is a member of SID and SPIE.

Minhua Lu IBM Research Division, Thomas J. Watson Research Center, P.O. Box 218, Yorktown Heights, New York 10598 (minhua@us.ibm.com). Dr. Lu received a B.S. in physics from the University of Science and Technology of China (1984), an M.S. in materials science from the Chinese Academy of Sciences (1987), an M.S. in physics from Case Western Reserve University (1990), and a Ph.D. in physics from Case Western Reserve University (1992). She joined the IBM Thomas J. Watson Research Center in 1995 as a Research Staff Member and has been working on Si-waferbased LCLVs for reflective projection displays and holographic optical storage. Prior to joining IBM, she worked for two years as an R&D manager at Kent Display Systems, Kent, Ohio, and for more than half a year as a Postdoctoral Fellow at the Liquid Crystal Institute of Kent State University. She has three U.S. patents and four patents pending, and more than 15 publications in the fields of reflective TN LC devices, fast-switching surface-stabilized cholesteric LCDs including driving, material, and process, polymer-dispersed LC for AMLCDs, and the usage of light scattering to study the polarization and elastic properties of ferroelectric LC and the formation of phospholipid tubules. She is a member of SID and SPIE.

Robert S. Olyha, Jr. IBM Research Division, Thomas J. Watson Research Center, P.O. Box 218, Yorktown Heights, New York 10598 (rolyha@us.ibm.com). Mr. Olyha received his master's and bachelor's degrees in electrical engineering from the Massachusetts Institute of Technology, Cambridge, in 1984. Following graduation, he joined IBM in the Central Scientific Services Department of the Thomas J. Watson Research Center, where he is currently a Senior Engineer and team leader. In 1992 and 1994 he received an IBM Outstanding Innovation Award and an IBM Corporate Award for his development of the TrackPoint family of pointing devices; he holds numerous patents in this area. Mr. Olyha was also named a finalist for the Outstanding Young Electrical Engineer of 1994 by Eta Kappa Nu. His current activities involve high-performance microcontroller and FPGA designs targeting computer input devices and display systems.

Chandrasekhar Narayan IBM Research Division, East Fishkill facility, Hopewell Junction, New York 12533 (narayanc@us.ibm.com). Dr. Narayan received his B.Tech degree in metallurgy from the Indian Institute of Technology and his M.S. and Ph.D. degrees in materials science and engineering from Lehigh University. He joined the IBM Research Division in 1983 and is currently a Research Staff Member working on redundancy activation in DRAMs and high-speed packaging of DRAMs. His research areas include thin-film processing, multilayer thin-film structures, packaging for multichip modules, and flat-panel displays. Dr. Narayan has written many technical papers and holds more than 12 U.S. patents; he has received three IBM Research Division Awards. He is a member of ASM International and the Society for Information Display.

John A. Hoffnagle IBM Almaden Research Center, 650 Harry Road, San Jose, California 95120 (hoffnagl@almaden.ibm.com). Dr. Hoffnagle received his Ph.D. in 1982 from the Swiss Federal Institute of Technology, Zurich. He joined IBM in 1985, working on spectroscopy and nonlinear dynamics of trapped ions. His current interests are applications of coherent optical technology for holographic data storage and interferometric lithography. He received a Research Division Award in 1997 for contributions to holographic data storage. Dr. Hoffnagle is a member of the American Physical Society and the Optical Society of America.

Paul M. Alt IBM Research Division, Thomas J. Watson Research Center, P.O. Box 218, Yorktown Heights, New York 10598 (alt@us.ibm.com). Dr. Alt is a Senior Manager in the Subsystems Technologies Department at the IBM Thomas J. Watson Research Center, where he has been a Research Staff Member since 1970, concentrating on display technologies and display systems. He is a Fellow of the Society for Information Display, a Senior Member of the Institute of Electrical and Electronics Engineers, and a member of the IBM Academy of Technology.

Robert L. Melcher IBM Research Division, Thomas J. Watson Research Center, P.O. Box 218, Yorktown Heights, New York 10598 (rmelcher@us.ibm.com). Dr. Melcher studied physics and mathematics at Southern Methodist University, Universitaet zu Koeln, and Washington University, where he received a Ph.D. in physics. He was a research associate at Cornell University before joining IBM Research in 1970. At IBM his work has been in the fields of condensed-matter physics, semiconductor laser technology, and display technology. Dr. Melcher has held several senior-level management positions in IBM Research. He is a Fellow of the American Physical Society, a Senior Member of the IEEE, and a member of SMPTE and SID.