# A submicron MOSFET parameter extraction technique

by B. El-Kareh W. R. Tonti S. L. Titcomb

A technique is introduced for measuring electron and hole mobilities as a function of temperature and normal field in inverted silicon surfaces. We also introduce a new definition of threshold voltage which allows the method to measure mobility independent of channel dimensions and resistance in series with the channel. The results are used to extract the resistance in series with the channel, the effective channel dimensions, and the intrinsic MOSFET transconductance. The technique is demonstrated on MOSFETs with channel lengths ranging from 0.25  $\mu m$  to 20  $\mu m$ .

#### Introduction

Several methods of determining the surface mobility from MOSFET transfer characteristics have been reported [1, 2]. These techniques rely on the definition of effective channel length  $L_{\rm EFF}$  and width  $W_{\rm EFF}$ , and on the measurement of source and drain resistances in series

<sup>®</sup>Copyright 1990 by International Business Machines Corporation. Copying in printed form for private use is permitted without payment of royalty provided that (1) each reproduction is done without alteration and (2) the *Journal* reference and IBM copyright notice are included on the first page. The title and abstract, but no other portions, of this paper may be copied or distributed royalty free without further permission by computer-based and other information-service systems. Permission to *republish* any other portion of this paper must be obtained from the Editor.

with the channel, which we will call the extrinsic resistances  $R_{\rm EX}$ . Though satisfactory for most technologies, these methods become inaccurate as the device dimensions are reduced below ~0.5  $\mu$ m and the ratio of  $R_{\rm EX}$  to channel resistance increases. Errors are particularly acute when the difference between designed and effective channel dimensions and the magnitude of extrinsic resistance depend on device size and applied bias conditions. The problem becomes more severe with lightly doped drains and at low temperature because of carrier freeze-out.

In this paper we introduce a measurement technique for determining the surface mobility as a function of normal field, temperature, and threshold voltage for arbitrary channel dimensions and  $R_{\rm EX}$ . The results are then used to extract the effective device dimensions, the extrinsic resistance, and the intrinsic device transconductance in submicron MOSFETs.

#### Threshold voltage

This section briefly describes three methods of defining and measuring the threshold voltage  $V_{\rm T}$ .

#### • Linear extrapolation method

A widely used method is to extrapolate to  $I_{\rm D}=0$  the linear part of the curve representing drain current  $I_{\rm D}$  versus gate voltage  $V_{\rm G}$ . The extrapolated threshold voltage may, however, change significantly because of variations in the extrinsic resistance.

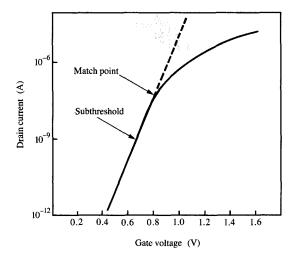

#### Figure

Definition of  $V_{\rm T}$  at match point where the measured drain current deviates by 5% from the exponential subthreshold extrapolation.

ullet Constant inversion charge density method In another common technique, the gate voltage is measured at a constant inversion charge density  $Q_{\mathrm{INV}}$ . This is typically done in the linear mode at a constant drain current per unit channel area,

$$I_{\rm VT} = I_{\rm SQ} \frac{W_{\rm eff}}{L_{\rm off}},\tag{1}$$

where  $I_{\rm SQ}$  is the drain current per square of channel corresponding to a constant inversion charge density, which is chosen in the  $10^9 q~{\rm cm}^{-2}$  range. This method, however, requires the ability to define the device dimensions and  $I_{\rm SQ}$  before threshold voltage measurement.

#### • Match-point method

We introduce a new definition of threshold voltage as the gate voltage for which the exponential extrapolation of subthreshold current deviates by 5% from the measured current (see Figure 1). In this method, known as the match-point method,  $V_{\rm T}$  is determined from subthreshold slope measurements independent of tolerances in channel dimensions and extrinsic resistance.

#### Mobility as a function of normal field

The surface mobility decreases as the field at the silicon surface increases [3–5]. Its dependence on normal field is determined by measuring the mobility as a function of

gate voltage above threshold and solving Poisson's equation to define the field in silicon for each measurement.

#### • Channel conductance method

The surface mobility is commonly determined from measurements of drain current in the linear mode by the relationship

$$\mu_{\rm EFF} \simeq \frac{I_{\rm D}}{V_{\rm D}} \left(\frac{L_{\rm EFF}}{W_{\rm EFF}}\right) \frac{1}{C_{\rm OX} \left(V_{\rm G} - V_{\rm T} - \frac{V_{\rm D}}{2}\right)},\tag{2}$$

where  $C_{\rm OX}$  is the gate-oxide capacitance, and  $V_{\rm D}$ ,  $V_{\rm G}$  are the drain-to-source and gate-to-source voltages, respectively.

This method is satisfactory when the relative tolerance in device dimensions and the magnitude of extrinsic resistance are known or negligible. In the presence of high values of  $R_{\rm EX}$ , the voltage drop outside the channel must be taken into account. Also, the magnitude of threshold voltage may increase due to the body effect. In this case,  $V_{\rm G}$  is replaced by  $V_{\rm G}' - I_{\rm D}R_{\rm EX}$  and  $V_{\rm D}$  by  $V_{\rm D}' - 2I_{\rm D}R_{\rm EX}$ , where  $V_{\rm G}'$  and  $V_{\rm D}'$  are the externally applied gate and drain voltages, respectively.

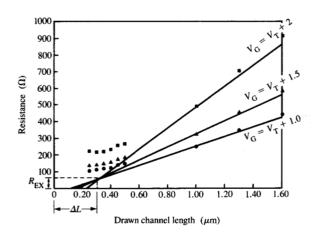

A typical method of determining the extrinsic resistance and effective channel length is described in [6]. It consists in measuring the MOSFET resistance, which includes the channel and extrinsic resistances, in the linear mode on devices having the same channel width and different design channel lengths. The measurements are made for different gate voltages above threshold. The extrinsic resistance and  $\Delta L$ , the deviation in channel length from the design value, are found graphically or analytically from the intersection of the plots. A similar technique is used to find the deviation in channel width  $\Delta W$ . This method, however, assumes that  $R_{\rm EX}$ ,  $\Delta L$ , and  $\Delta W$  are constant in a set of adjacent devices, and are independent of gate voltage. Our measurements on submicron devices show that this is not always the case (see Figure 2). It is evident that the plots cannot be approximated by single straight lines, and their intersection is not well defined; this precludes a unique definition of  $R_{\rm EX}$  and  $\Delta L$ .

#### Van der Pauw method

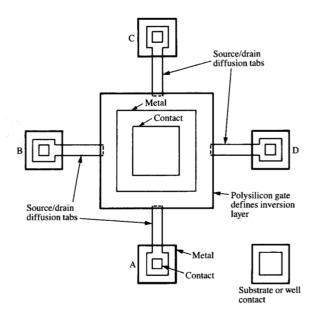

We introduce a surface mobility measurement technique which uses an inversion-layer Van der Pauw structure, as illustrated in Figure 3. Details of the Van der Pauw structure can be found in [7, 8]. The structure allows the measurement of surface mobility as a function of normal field and temperature, for arbitrary extrinsic resistance and device dimensions. It comprises four diffusion tabs defined during source/drain diffusion, a gate electrode, and a substrate or well contact.

#### Figure 2

Determination of  $R_{\rm EX}$  and  $\Delta L$  using the method described in Equation (6). The values obtained from the intersection are not uniquely defined in the submicron range.

The threshold voltage is first measured using the match-point technique described above. The sheet resistance  $R_{\rm s}$  of the inversion layer is then measured as a function of gate voltage above threshold by forcing a current  $\Delta I$  between two adjacent diffusions and measuring the voltage  $\Delta V$  between the two other diffusions. The following well-known relationship holds for the sheet resistance:

$$R_{\rm S} = \frac{\pi}{\ln 2} \left( \frac{\Delta V}{\Delta I} \right). \tag{3}$$

The effective surface mobility is determined from the calculated inversion-layer charge density  $Q_{\rm INV}$  and the measured sheet resistance:

$$\mu_{\rm EFF} = \frac{1}{|Q_{\rm INV}| R_{\rm s}}.\tag{4}$$

#### Extraction of $R_{\rm EX}$ , $L_{\rm EFF}$ , and transconductance

The effective surface mobility found from Van der Pauw measurements is used to determine the MOSFET extrinsic resistance, effective channel length, and transconductance for a given device.

#### • Extrinsic resistance

In the linear mode, the drain current may be approximated as

$$I_{\rm D} = \gamma \frac{W_{\rm EFF}}{L_{\rm EFF}} \left( V_{\rm G}' - V_{\rm T} - \Delta V_{\rm T} - \frac{V_{\rm D}'}{2} \right) (V_{\rm D}' - 2I_{\rm D}R_{\rm EX}), \quad (5)$$

#### Figure 3

Inversion-layer Van der Pauw structure.

where  $\gamma = \mu_{\rm EFF} C_{\rm EFF}$ ,  $C_{\rm EFF} = (C_{\rm OX} C_{\rm INV})/(C_{\rm OX} + C_{\rm INV})$ , and  $\Delta V_{\rm T}$  is the increase in threshold voltage due to the body effect. The inversion layer capacitance  $C_{\rm INV}$  is approximated from [9, 10]. Its effect, however, is negligible when  $|V_{\rm G} - V_{\rm T}| \ge 2$  V and the gate-oxide thickness  $t_{\rm ox} \ge 15$  nm.

For all structures analyzed, it was found that the increase in threshold voltage  $\Delta V_{\rm T}$  due to the body effect was negligible in the linear but not in the saturation mode. In this case, the extrinsic resistance was found by taking the ratio of drain currents for two gate voltages,

$$R_{\rm EX} = \frac{V_{\rm D}'(K\Delta V_{\rm G1} - \Delta V_{\rm G2})}{2(K\Delta V_{\rm G1}I_{\rm D1} - \Delta V_{\rm G2}I_{\rm D2})},\tag{6}$$

where  $K = I_{D2}\gamma_1/I_{D1}\gamma_2$  and  $\Delta V_G = V_G' - V_T - V_D'/2$ . The subscripts 1 and 2 refer to the two applied gate voltages.

#### • Effective channel dimensions

To determine the effective channel length, measurements were made on a wide MOSFET where it could be assumed that the tolerance on  $W_{\rm eff}$  was negligible. The nominal width was determined from scanning electron microscope (SEM) measurements. The effective channel length was then found by substituting  $R_{\rm EX}$  from (6) into (5). Similarly, the effective channel width was found by

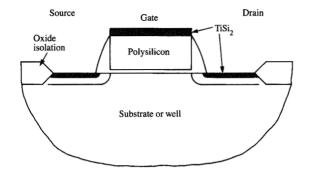

#### Figure 4

MOSFET cross section typical of CMOS-A and CMOS-B technologies.

Table 1 Main features of two CMOS n-well technologies.

| Parameter              | СМО       | OS-A      | CMOS-B    |           |

|------------------------|-----------|-----------|-----------|-----------|

|                        | n-channel | p-channel | n-channel | p-channel |

| t <sub>ox</sub> (nm)   | 15        | 15        | 11        | 11        |

| $\tilde{V}_{T}(V)$     | 0.75      | -0.75     | 0.65      | -0.65     |

| Gate                   | n-type    | n-type    | n-type    | p-type    |

| $X_{\rm J}$ ( $\mu$ m) | 0.40      | 0.45      | 0.15      | 0.15      |

**Table 2** Measured mobility parameters of two CMOS n-well technologies.

| Parameter | СМО       | CMOS-A    |           | CMOS-B    |  |

|-----------|-----------|-----------|-----------|-----------|--|

|           | n-channel | p-channel | n-channel | p-channel |  |

| $\mu_0$   | 433       | 193       | 356       | 90        |  |

| $\theta$  | 0.065     | 0.147     | 0.073     | 0.085     |  |

**Table 3** Extraction of  $R_{\rm EX}$ ,  $L_{\rm EFF}$ , and  $g_{\rm m}$  (measurements made on p-channel MOSFETs in CMOS-B).

| $L_{	ext{DESIGN}} \ (\mu 	ext{m})$ | $R_{EX} \ (\Omega)$ | $L_{	t EFF} \ (\mu 	t m)$ | $g'_{m}$ (ms/mm) | g <sub>m</sub><br>(ms/mm) |

|------------------------------------|---------------------|---------------------------|------------------|---------------------------|

| 5.00                               | 168                 | 5.058                     | 9.38             | 9.54                      |

| 2.00                               | 141                 | 2.069                     | 21.50            | 22.35                     |

| 1.00                               | 129                 | 0.711                     | 48.96            | 53.90                     |

| 0.80                               | 154                 | 0.758                     | 45.83            | 51.78                     |

| 0.65                               | 125                 | 0.601                     | 55.70            | 64.50                     |

| 0.50                               | 164                 | 0.429                     | 66.70            | 85.38                     |

| 0.35                               | 112                 | 0.266                     | 91.67            | 117.90                    |

characterizing a long MOSFET where the tolerance on channel length might be neglected.

#### • Saturation transconductance

When the device does not operate at scattering-limited velocity, the saturation transconductance per unit channel width is measured as

$$g_{\rm m}' = \frac{1}{W_{\rm EFF}} \left( \frac{\delta I_{\rm D}}{\delta V_{\rm G}'} \right). \tag{7}$$

The modulation of the effective channel length by the drain field and the effect of  $R_{\rm EX}$  on  $\gamma$  were neglected for the bias voltage conditions used in this study. This was justified by two-dimensional simulations of the structures. The measured  $g'_{\rm m}$  was typically smaller than the intrinsic  $g_{\rm m}$  because of the voltage drops outside the channel. The ratio of intrinsic to measured transconductance is approximated by

$$\frac{g_{\rm m}}{g_{\rm m}'} \simeq \frac{V_{\rm G}' - V_{\rm T}}{V_{\rm G}' - V_{\rm T} - \Delta V_{\rm T} - I_{\rm D} R_{\rm EX}}.$$

(8)

#### Sample preparation

The samples were fabricated in two CMOS n-well technologies we call CMOS-A and CMOS-B. The main features of the technologies are summarized in **Table 1**.

The structures were fabricated on p<sup>+</sup> substrates upon which a 2-3-µm-thick p-type epitaxial layer was deposited. A buried channel was implanted in CMOS-A p-channel MOSFETs to adjust for the work function of the gate material. A MOSFET cross section which is typical for both technologies is shown in Figure 4. The Van der Pauw structures were comprised of 100-µm × 100- $\mu$ m inversion layers with 1- $\mu$ m tab widths. For  $\Delta L$ measurements, the MOSFETs were designed with a 20-µm channel width and channel lengths varying from  $0.25 \mu m$  to  $20 \mu m$ ; the nominal channel width was determined from SEM measurements as  $W_{\text{EFF}} \simeq 19.4 \, \mu \text{m}$ . For  $\Delta W$  measurements, the channel length was 20  $\mu$ m, and the width was varied from 0.8  $\mu$ m to 20  $\mu$ m; the nominal channel length was determined from SEM measurements as 19.8  $\mu$ m. The polysilicon gates were defined in photolithography for CMOS-A and in e-beam lithography for CMOS-B.

#### Results

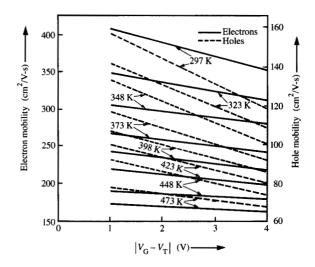

The results obtained for surface mobility as a function of gate voltage above threshold and temperature in the range 297 K to 473 K are summarized for CMOS-A in Figure 5. The following semi-empirical relation is used to approximate the surface mobility [5]:

$$\mu_{\rm EFF} \simeq \frac{\mu_0}{1 + \theta(|V_G - V_T|)},\tag{9}$$

where  $\mu_0$  and  $\theta$  are extracted from measurements; a suggested model for their physical interpretation is described in the Appendix.

The temperature dependence of  $\mu_0$  is approximated from Figure 5 for n-channels as

$$\mu_{0T} \simeq \mu_0(297) \left(\frac{T}{297}\right)^{-1.74},$$

(10)

and for p-channels as

$$\mu_{0T} \simeq \mu_0(297) \left(\frac{T}{297}\right)^{-1.21}$$

(11)

Similar results were found for CMOS-B. Table 2 summarizes the measured room-temperature values of  $\mu_0$  and  $\theta$  for the two technologies. The effective mobilities are smaller in CMOS-B than in CMOS-A. This is caused by the difference in the gate oxide thickness and channel impurity profile, as discussed in the Appendix. The larger difference in the p-channel mobility is caused by the p-type buried layer present in CMOS-A (n-type gate, buried channel) but not in CMOS-B (p-type gate, surface channel).

The MOSFET drain current is measured in the linear mode at  $|V_{\rm D}'|=0.2~{\rm V}$  and  $|V_{\rm G}'-V_{\rm T}|=2~{\rm V}$  and 3 V. In the saturation mode the bias conditions were  $|V_{\rm D}'|=3.4~{\rm V}$  and  $|V_{\rm G}'|=3.0$  and 3.1 V. The substrate or well was maintained at ground potential. The saturated transconductance was measured for  $V_{\rm D}'=3.4~{\rm V}$  and  $\delta V_{\rm G}'=0.1~{\rm V}$ .

Values for  $R_{\rm EX}$ ,  $L_{\rm EFF}$ , and  $g_{\rm m}$  obtained for p-channel structures in CMOS-B at 297 K are shown in Table 3. The corresponding values for  $\gamma$  are found from Van der Pauw measurements as  $\gamma_1=27.13~\mu{\rm S/V}$  and  $\gamma_2=25.70~\mu{\rm S/V}$ . It can be seen from the table that the structures exhibit a large extrinsic resistance that varies between 2.2 k $\Omega$ - $\mu{\rm m}$  and 3.3 k $\Omega$ - $\mu{\rm m}$ . It was also found that  $\Delta L$  is not constant but varies between -0.069  $\mu{\rm m}$  and +0.29  $\mu{\rm m}$ . Finally, the table shows an increasing difference between measured and intrinsic transconductance as the channel length is decreased. This is caused by an increase in the ratio of extrinsic to channel resistance.

Similar results were obtained for CMOS-A and for n-channel structures in both technologies.

#### **Conclusions**

A technique which uses a specially designed Van der Pauw structure was introduced to measure electron and hole mobilities in an inverted silicon surface as a function of normal field and temperature. A new definition of threshold voltage is introduced, which allows the method to measure surface mobility, independent of variations in channel size and resistance

## Figure 5 Electron and hole surface mobilities as a function of $|V_G - V_T|$ for $|V_D| = 0.2 \text{ V}$ (temperature as parameter).

outside the channel, referred to here as the extrinsic resistance.

The measured mobility and threshold voltage were used to extract the extrinsic resistance, effective channel dimensions, and intrinsic transconductance in submicron n-channel and p-channel MOSFETs. The method was successfully demonstrated on submicron MOSFETs fabricated in CMOS technologies having different gate oxide thicknesses and channel impurity profiles. The surface mobility as a function of gate voltage above threshold was approximated in terms of two parameters ( $\mu_0$  and  $\theta$ ), which were determined empirically. A model was suggested to relate the two parameters to the gate oxide thickness, channel impurity profile, and temperature.

### Appendix: Model for dependence of mobility on normal field

The dependence of surface mobility on gate voltage above threshold is given in Equation (9) as

$$\mu_{\rm EFF} \simeq \frac{\mu_0}{1 + \theta(V_G - V_T)},\tag{A1}$$

where  $\mu_0$  and  $\theta$  are determined empirically [5]. In this section we suggest a model that relates  $\mu_0$  and  $\theta$  to the oxide thickness, channel impurity profile, and temperature. We begin with the following assumption on

the degradation of surface mobility due to normal field:

$$\frac{1}{\mu_{\text{EFF}}} \simeq \frac{1}{\mu_{\text{I}}} + \frac{1}{\mu_{\text{I}}} + \frac{1 + C_1 |E_{\text{Si}}|}{\mu_{\text{S}}},\tag{A2}$$

where

$\mu_{\rm L}$  = lattice-limited mobility,

$\mu_{I}$  = impurity-limited mobility,

$E_{\rm Si}$  = normal field at the silicon surface,

$\mu_{\rm S}=$  surface-scattering-limited mobility extrapolated to  $E_{\rm Si}=0.$

In this analysis it is assumed that for a given process technology,  $C_1$  is constant and  $\mu_S$  depends only on temperature.  $C_1$  and  $\mu_S$  are determined empirically. Equation (A2) may be rewritten as

$$\mu_{\text{EFF}} \simeq \frac{\mu_{\text{S}}}{1 + \frac{\mu_{\text{S}}}{\mu_{\text{B}}} + C_1 |E_{\text{Si}}|},$$

(A3)

where

$$\frac{1}{\mu_{\rm B}} \simeq \frac{1}{\mu_{\rm L}} + \frac{1}{\mu_{\rm I}}.\tag{A4}$$

In [11],  $\mu_1$  is defined as

$$\mu_{\rm I} = \frac{AT^{1.5}}{N_{\rm I} \ln\left(1 + \frac{BT^2}{N_{\rm I}^{2/3}}\right)},\tag{A5}$$

where A is a constant that depends on the carrier effective mass, T is the temperature in K,  $N_I$  is the ionized impurity concentration at the silicon surface, and B is expressed in terms of universal constants as

$$B = \left(\frac{3\epsilon_{\rm Si}k}{a^2}\right)^2 \simeq 2.81 \times 10^6 \text{ cm}^{-2}\text{-K}^{-2},\tag{A6}$$

where  $\varepsilon_{\rm Si}$  is the dielectric constant of silicon and k is the Boltzmann constant. From independent measurements on specially designed structures, we find  $A \simeq 1.5 \times 10^{16}$  for electrons and  $A \simeq 7.3 \times 10^{15}$  for holes. The lattice-scattering-limited mobility is given by [12] as

(electrons)

$$\mu_L \simeq 2.1 \times 10^9 T^{-2.5} \text{cm}^2/\text{V-s}$$

(A7)

and

(holes)

$$\mu_1 \simeq 2.3 \times 10^9 T^{-2.7} \text{cm}^2/\text{V-s}.$$

(A8)

We now rewrite (A3) as

$$\mu_{\text{EFF}} \simeq \frac{\mu_{\text{max}}}{1 + C_2 |E_{\text{Si}}|},\tag{A9}$$

where

$$\mu_{\text{max}} = \frac{\mu_{\text{B}}\mu_{\text{S}}}{\mu_{\text{D}} + \mu_{\text{C}}}$$

and

(A2)

$$C_2 = \frac{C_1 \mu_B}{\mu_S + \mu_B}$$

.

The electric field in silicon  $E_{si}$  is approximated from [3] as

$$E_{\rm Si} = \frac{Q_{\rm B} + \frac{Q_{\rm INV}}{2}}{\varepsilon_{\rm Si}},\tag{A10}$$

where  $Q_{\rm B}$  is the bulk charge density which is found by solving Poisson's equation for a given channel profile. The inversion charge density is approximated as

$$Q_{\text{INV}} = C_{\text{OX}}(V_{\text{G}} - V_{\text{T}}). \tag{A11}$$

Equation (A9) is finally rewritten in the form of Equation (A1), with

$$\mu_0 = \frac{\mu_{\text{max}}}{1 + \frac{C_2 |Q_B|}{\epsilon_{\text{cr}}}} \tag{A12}$$

and

$$\theta = \frac{C_2 C_{\text{OX}}}{2(\epsilon_{\text{Si}} + C_2 | Q_{\text{B}}|)}.$$

(A13)

When substituted into Equation (A1), Equations (A11) and (A12) allow the prediction of surface mobility as a function of oxide thickness, temperature, and channel impurity profile.

#### **Acknowledgments**

We thank G. Gravenites for the design and initial characterization of the inversion layer Van der Pauw structure, N. Jones for successfully carrying out the experiments, and the advanced technology group at IBM, Essex Junction, Vermont, for preparing the samples. Discussions with M. Wordeman of the IBM Thomas J. Watson Research Center are greatly appreciated.

#### References

- H. I. Hanafi, L. H. Camnitz, and A. I. Dally, "An Accurate and Simple MOSFET Model for Computer-Aided Design," *IEEE J. Solid State Circuits* SC-17, 882 (1982).

- S. C. Sun and J. D. Plummer, "Electron Mobility in Inversion and Accumulation Layers on Thermally Oxidized Silicon Surfaces," *IEEE Trans. Electron Devices* ED-27, 1497 (1980).

- A. S. Sabnis and J. J. Clemens, "Characterization of the Electron Mobility in the Inverted (100) Silicon Surface," 1979 IEDM Tech Digest, p. 18 (1979).

- K. Yamaguchi, "Field-Dependent Mobility Model for Two-Dimensional Numerical Analysis of MOSFETs," *IEEE Trans. Electron Devices* ED-26, 1068 (1979).

- K. Y. Fu, "Mobility Degradation Due to Gate Field in the Inversion Layer of MOSFETs," *IEEE Trans. Electron Device* Lett. EDL-3, 292 (1982).

- J. Chern, P. Chang, R. Motta, and N. Godinho, "A New Method to Determine MOSFET Channel Length," *IEEE Electron Device Lett.* EDL-1, 170, 1980.

- L. J. Van der Pauw, "A Method for Measuring Specific Resistivity and Hall Effect of Disc of Arbitrary Shape," *Phillips Res. Repts.* 13, 1 (1958).

- 8. W. R. Tonti, "Field and Temperature Dependence of Surface Mobility," Ph.D. Dissertation, University of Vermont, Burlington, Vermont, 1987.

- 9. G. Baccarani and M. R. Wordeman, "Transconductance Degradation in Thin Oxide MOSFETs," *1982 IEDM Tech. Digest*, p. 278 (1982).

- M. S. Liang, J. Y. Choi, P. K. Ko, and C. Hu, "Inversion-Layer Capacitance and Mobility of Very Thin Gate-Oxide MOSFETs," *IEEE Trans. Electron Devices* ED-33, 409 (1986).

- E. M. Conwell, "Properties of Silicon and Germanium," Proc. IRE 40, 1327 (1952).

- 12. G. W. Ludwig and R. L. Watters, "Drift and Conductivity Mobility in Silicon," *Phys. Rev.* **101**, 1699 (1956).

Received May 26, 1989; accepted for publication September 4, 1989

Badih El-Kareh IBM General Technology Division, Essex Junction, Vermont 05452. Dr. El-Kareh received the M.S. degree in physics from the University of Hamburg, FRG, and the Ph.D. degree in physics from the University of Stuttgart, FRG, in 1963 and 1966, respectively. After working for Robert Bosch in Stuttgart, he joined the IBM laboratory in Boeblingen, FRG, to work on the design of bipolar devices and MOSFETs. In 1971 Dr. El-Kareh transferred to the IBM General Technology Division laboratory in Essex Junction, Vermont, where he has worked extensively on the development of CMOS and bipolar devices for memory and logic. Dr. El-Kareh is a member of the IEEE.

William R. Tonti IBM General Technology Division, Essex Junction, Vermont 05452. Dr. Tonti received a B.S. in electrical engineering in 1978 from Northeastern University, Boston. After graduation he joined the IBM General Technology Division in Essex Junction, Vermont, where he now works in the Advanced Technology CMOS Device Design area. Dr. Tonti received an M.S. in electrical engineering in 1982 from the University of Vermont, an M.B.A. in 1983 from Saint Michael's College, and a Ph.D. in electrical engineering from the University of Vermont in 1988 under the auspices of the IBM resident study program.

Stephen L. Titcomb CS/EE Department, University of Vermont, Burlington, Vermont 05405. Dr. Titcomb received the B.S. degree in physics from Moravian College in 1976 and the M.S. and Ph.D. degrees in physics from Lehigh University in 1978 and 1983, respectively. Since 1983 he has been an Assistant Professor of Electrical Engineering at the University of Vermont, Burlington. He is currently engaged in research on low-temperature operation of semiconductor devices. Dr. Titcomb is a member of the American Physical Society and the IEEE.