# Electrical and microstructural investigation of polysilicon emitter contacts for high-performance bipolar VLSI

by J. M. C. Stork

E. Ganin

J. D. Cressler

G. L. Patton

G. A. Sai-Halasz

Key electrical characteristics of polysilicon emitter contacts in bipolar transistors, such as contact resistance and recombination velocity, are extremely sensitive to the microstructure of the polysilicon/single-crystal silicon interface. In this study, we correlated the microstructural and electrical characteristics of this interface by performing cross-sectional transmission electron microscopy (XTEM) on actual transistors on the same chip where ringoscillator speeds were measured. The base current and emitter resistance of the fastest devices approached values typical of single-crystal silicon emitters. Interpretation of these electrical data and of the SIMS impurity profile

indicates that significant restructuring of the polysilicon/single-crystal interface had taken place. This conclusion was indeed confirmed by the XTEM results. Although the low-current performance was degraded because of higher junction capacitances, the high-current switching speed was improved because of the minimal emitter contact resistance. Since the current gain was sufficiently high and very uniform, it is concluded from this work that minimization of both junction depth and contact resistance is the most important design consideration for high-performance submicron transistors, rather than maximization of the gain enhancement of the polysilicon/single-crystal interface.

<sup>®</sup>Copyright 1987 by International Business Machines Corporation. Copying in printed form for private use is permitted without payment of royalty provided that (1) each reproduction is done without alteration and (2) the *Journal* reference and IBM copyright notice are included on the first page. The title and abstract, but no other portions, of this paper may be copied or distributed royalty free without further permission by computer-based and other information-service systems. Permission to *republish* any other portion of this paper must be obtained from the Editor.

# Introduction

The maximum speed (frequency) at which bipolar transistor circuits can operate is largely limited by base resistance and base-emitter diffusion capacitance ( $C_{\rm d}=G_{\rm m}\times\tau_{\rm F}$ , the product of transconductance and transit time). Shorter transit time can be obtained by a thinner base and shallower emitter, without compromising controllability. Scaling in the

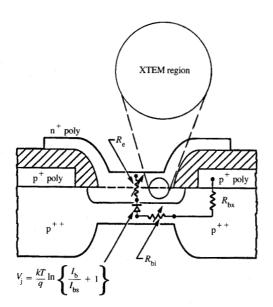

# Figure 1

Schematic cross section of self-aligned double-polysilicon bipolar transistor.

Table 1 Transistor parameters.

| Emitter area                                    | $A_{\rm E} \simeq 10 \ \mu {\rm m}^2$ |                       |                   |

|-------------------------------------------------|---------------------------------------|-----------------------|-------------------|

| Emitter anneal                                  | 800°C                                 | 900°C                 |                   |

| $J_{ m cs} \ J_{ m bs} \ V_{ m CE_0}$           | $7.2 \times 10^{-19}$                 | $8.3 \times 10^{-19}$ | $A/\mu m_2^2$     |

| $J_{ m bs}$                                     | $1.6 \times 10^{-21}$                 | $6.6 \times 10^{-21}$ | $A/\mu m^2$       |

| $V_{CE_0}$                                      | 6.0                                   | 5.5                   | V                 |

| $V_{\mathrm{BE}_0}$                             | 5.3                                   | 3.5                   | V                 |

| $ ho_{bi}$                                      | $5.6 \pm 1.2$                         | $6.1 \pm 0.17$        | $k\Omega/\square$ |

| $egin{aligned}  ho_{bi} \ R_{bx} \end{aligned}$ | 110                                   | 85                    | Ω                 |

| $R_e^{0}$ (at 2 mA)                             | 20                                    | 5                     | $\Omega$          |

| $C_{\mathbf{L}}$                                | 3.9                                   | 3.7                   | $fF/\mu m^2$      |

| $C_{bc}^{\infty}$                               | 0.48                                  | 1.1                   | $fF/\mu m^2$      |

| $C_{be}$ $C_{bc}$ $C_{cs}$ (area)               | 0.14                                  | 0.13                  | $fF/\mu m^2$      |

| $C_{\infty}$ (perimeter)                        | 4.0                                   | 3.9                   | fF/μm             |

| $f_{\rm T}$ (at 4 mA)                           | 5                                     | 6.2                   | GHz               |

| Collector saturation current density Base saturation current density Collector-emitter punchthrough voltage                                                                                                                                    | $J_{cs}$ $J_{bs}$ $V_{CE_0}$                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Base-emitter breakdown voltage                                                                                                                                                                                                                 | $V_{ m BE_0}$                                                                                |

| Intrinsic base sheet resistance Extrinsic base resistance Emitter resistance (at 2 mA) Base-emitter junction capacitance Base-collector junction capacitance Collector-substrate capacitance Collector-substrate capacitance Transit frequency | $\rho_{bi}$ $R_{bx}$ $R_{e}$ $C_{be}$ $C_{cs}$ (area) $C_{cs}$ (perimeter) $f_{T}$ (at 4 mA) |

lateral dimension also requires a shallow base-emitter junction. When only the emitter width is reduced, the contribution of the lateral sidewall junction can degrade high-frequency performance. However, reducing the base-emitter junction depth in conventional metal-contacted transistors causes the base current to be unacceptably high and very sensitive to the contact properties. Polysilicon emitter contacts significantly improve bipolar device performance, because they produce a highly abrupt, shallow base-emitter profile without a reduction in current gain since the metal contact is moved away from the junction [1].

By using polysilicon both as the contact and as the diffusion source for the emitter, very shallow, highly abrupt junctions can be obtained by limiting the outdiffusion of As into the single-crystal silicon. In addition, the reduced mobility in the polysilicon [2,3] and the presence of an interfacial tunneling barrier [4] at the polysiliconmonosilicon interface result in a base current density (holes for an npn transistor) that is reduced by a factor of 3 or more. The polysilicon/monocrystalline silicon interface, however, not only acts as a barrier to hole transport (base current), but also increases the resistance for electrons (emitter current) [5,6]. Since the largest current density in the device passes through the emitter contact, the specific contact resistivity must be kept as low as possible to prevent a degradation in transconductance. Although the exact electrical properties of the polysilicon/silicon interface are still under investigation, it is known that the interface structure changes significantly as a result of high-temperature annealing, and that these changes are enhanced at high doping levels [7–11]. Specifically, the "native" interface oxide layer "balls up" and the polysilicon tends to realign to the underlying substrate, thereby extending the single-crystal emitter up into the polysilicon layer. This type of structural change has been expected to result in the following trade-off: Although a lower emitter resistance can be obtained by a higher-temperature treatment and/or higher doping level, the junction depth and base current would then be increased.

In order to determine the potential performance trade-off between base current and emitter resistance, this paper compares the structural and electrical aspects of advancedtechnology bipolar transistors which differ only in the annealing treatment of the polysilicon emitter contact. In the following sections, the sample preparation is described, followed by the dc electrical transistor characteristics. Next, XTEM results of the polysilicon/single-crystal silicon interface are presented, showing significant restructuring of the poly-emitter interface for the devices with the lowest emitter resistance. In the final section, switching performance is addressed. Measurements on ring-oscillators show a strong correlation between speed and low emitter contact resistance. Simulation is used to analyze the increasing importance of low contact resistance for high-speed, submicron bipolar transistors.

# Sample preparation

The devices used in our experiment were self-aligned doublepolysilicon bipolar transistors, whose schematic cross section is shown in Figure 1. Relaxed geometries (2.5  $\mu$ m) were used, and isolation was achieved by a combination of recessed oxide isolation and p<sup>+</sup> channel-stop implantation. The epitaxial layer was kept thin to prevent high-current degradation due to basewidening [12]. The base contact was in situ, boron-doped polysilicon with a (measured) thickness of 0.26 µm. The emitter opening was etched using a selective chemical wet etch, so as to prevent surface contamination from reactive ion etching (RIE) that might alter the condition of the emitter surface. The base contact was diffused into the silicon to provide a self-aligned connection to the intrinsic device. After formation of an oxide sidewall on the base contact polysilicon, in situ, arsenic-doped polysilicon was deposited at 650°C in an AM 704 reactor, using N<sub>2</sub> as the carrier gas. The emitter surface was given a 4-s buffered hydrofluoric acid (BHF) cleaning prior to this deposition to minimize any residual native oxide on the surface. The as-deposited grain size of the emitter polysilicon was measured by TEM to be approximately 20 nm. The arsenic content was measured by Rutherford backscattering spectroscopy (RBS) to be about 3 atomic percent, resulting in a sheet resistance after annealing of 1-3 k $\Omega/\Box$ . Two different emitter anneals were used: 900°C for 10 min or 800°C for 45 min. The second anneal condition was designed to result in approximately the same integrated base doping while minimizing the base-emitter junction depth, as is discussed later. Metallization consisted of a Ti/Al/Si sandwich, which was annealed in forming gas at 400°C.

# Transistor de electrical characteristics

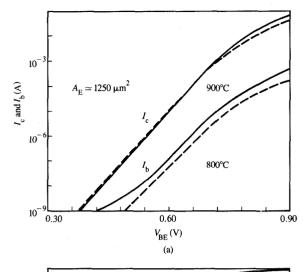

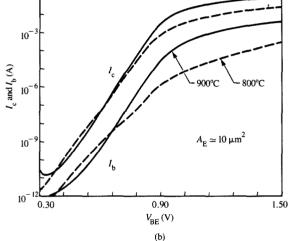

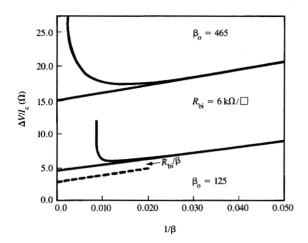

The results of extensive dc and ac characterizations are summarized in Table 1. From large transistors [see Figure 2(a)] it was found that the base current for the devices annealed at 800°C was lower than that of the devices annealed at 900°C by about a factor of two. The collector currents were approximately the same, indicating that the integrated base charge was indeed equivalent for both types of devices. This was confirmed by the base-emitter junction capacitance measurements shown in Figure 3, which were in good agreement with secondary ion mass spectroscopy (SIMS) profiles taken on monitor wafers. The peak doping was slightly higher for the lower-temperature anneal, but the base thickness was estimated to be about the same. These observations were further supported by measurements of the sheet resistance of the active base of 6 and 5 k $\Omega/\Box$ , for the high- and low-temperature anneals, respectively (see Table 1).

The I-V curves for small devices ( $A_{\rm E} \le 10~\mu{\rm m}^2$ ) are shown in Figure 2(b). The curves indicate that the series resistance was substantially higher for the device given the 800°C anneal. In order to assess whether this was due to base or

Figure 2  $I_{\rm c}, I_{\rm b}$  versus  $V_{\rm BE}$  curves for (a) large devices:  $A_{\rm E} \simeq 1200~{\rm \mu m}^2$ ; (b) small devices:  $A_{\rm E} \simeq 10~{\rm \mu m}^2$ .

emitter resistance, the method of Ning [13] was used. In this approach, the total series voltage drop at high currents is extracted by extrapolating the ideal exponential behavior of the base current  $I_{\rm b}\left(V_{\rm j}\right)$  versus the junction voltage  $V_{\rm j}$  to high currents. Then, subtracting this from the base current  $I_{\rm b}\left(V_{\rm BE}\right)$  versus the emitter voltage  $V_{\rm BE}$ , the total series voltage drop is

$$\Delta V = V_{\rm BE} - V_{\rm i} = R_{\rm e}(I_{\rm c} + I_{\rm b}) + (R_{\rm bi} + R_{\rm bx})I_{\rm b}, \tag{1}$$

where the extrinsic base resistance  $R_{\rm bx}$  is constant and associated with the contact area, and the intrinsic base resistance  $R_{\rm bi}$  is modulated by the injection level in the active

619

Figure 6

Base doping profile extracted from C-V measurement of the base-emitter junction.  $X_{bc}$  is the extracted base-emitter junction width at zero bias. The base profiles are evidently nearly equal for both emitter anneals: (a)  $900^{\circ}$ C; (b)  $800^{\circ}$ C.

device. Since  $I_c = \beta I_b$ , the base resistances can be separated from the emitter resistance by dividing  $\Delta V$  by  $I_c$ ,

$$\frac{\Delta V}{I_{\rm c}} = R_{\rm tot} = R_{\rm e} \left( 1 + \frac{1}{\beta} \right) + (R_{\rm bi} + R_{\rm bx}) \frac{1}{\beta}.$$

(2)

In order to uniquely determine  $R_{\rm bx}$ , the assumption was made in [13] that  $R_{\rm bi}/\beta$  is small and approximately constant as a function of collector current. In typical devices, however, the intrinsic base resistance produces a lateral voltage drop, which "crowds" the current injection toward the perimeter of the base-emitter junction because the largest forward bias is there. When the intrinsic base resistance is large (because of a high sheet resistivity or because of layout) this crowding reduces the effective resistance (without a degradation in current gain) so that the lateral voltage is overestimated when the low-current value of  $R_{bi}$  is used. Further complications arise from the reduction in current gain that results from high-injection effects; this had led to confusion about the interpretation of nonohmic emitter resistance [14]. An extensive treatment of the impact of current crowding on the extraction of base and emitter resistance can be found in [15].

For the devices of this study annealed at 800°C, the crowding effect of *intrinsic* base resistance is negligible, however: The lateral voltage drop never exceeds kT/q

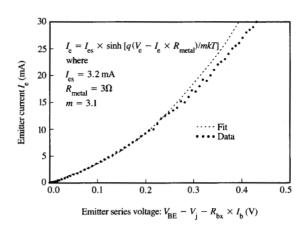

because of the high  $\beta$  and low base sheet resistance. The extrinsic base component from the slope in Figure 4 having been determined, the net voltage drop across the emitter contact can then be extracted. In Figure 5 it is shown that the emitter current depends in a sine-hyperbolic manner on the voltage across the polysilicon/single-crystal silicon interface. Such behavior is expected when transport through the contact is barrier-limited [16], as has been verified elsewhere [17]. The contribution of the metal-to-polysilicon contact resistance was estimated at 3  $\Omega$ , which gave very good agreement for the sine-hyperbolic fit. (The quoted resistance data were measured on bonded devices to minimize probe and cable parasitics.) This is also consistent with the emitter resistance measured on devices given the 900°C emitter anneal. For such 900°C devices, the extracted emitter resistance is ohmic and extremely small ( $\approx$ 5  $\Omega$ ). Due to the low intrinsic base resistance, little crowding takes place, so that  $R_{bi}$  and  $\beta$  degrade at the same rate and their ratio remains constant at  $R_{\rm bi}/\beta \simeq 2~\Omega$ . Therefore, most of the emitter resistance can be estimated to be contact resistance between the polysilicon and the metal. Again, this is consistent with the constant component in the total resistance of the 800°C transistor. In addition to the very low resistance of the 900°C anneal, the base current density was a factor of 2 higher than that of the 800°C device and its

620

Total series resistance versus inverse  $\beta$ . The slope at low  $\beta$  gives  $R_{\rm bx}$ , while  $R_{\rm e}$  is extracted from the intercept. Although there is a slight difference in  $R_{\rm bx}$ , the emitter resistance is a factor of 4 or more larger for the 800°C emitter anneal.

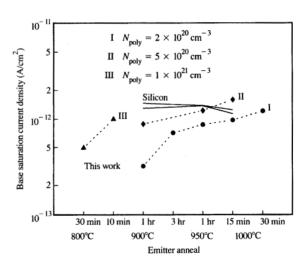

magnitude ( $\approx 1 \text{ pA/cm}^2$ ) is comparable to values obtained with deep, single-crystal emitters [7]. Despite the higher-temperature anneal, the emitter junction depth was less than 50 nm in these devices (from SIMS). Indeed, simulation of a single-crystal silicon layer with an ideal box-like doping profile results after the same anneal in a shallower but slightly more graded junction compared to a polysilicon diffusion source. This effect has been observed before [18] and is explained by epitaxial regrowth, which moves the fast grain-boundary diffusion sites away from the substrate.

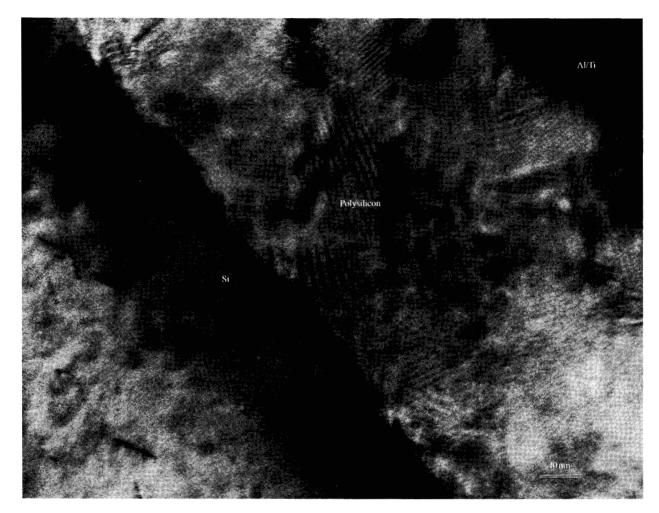

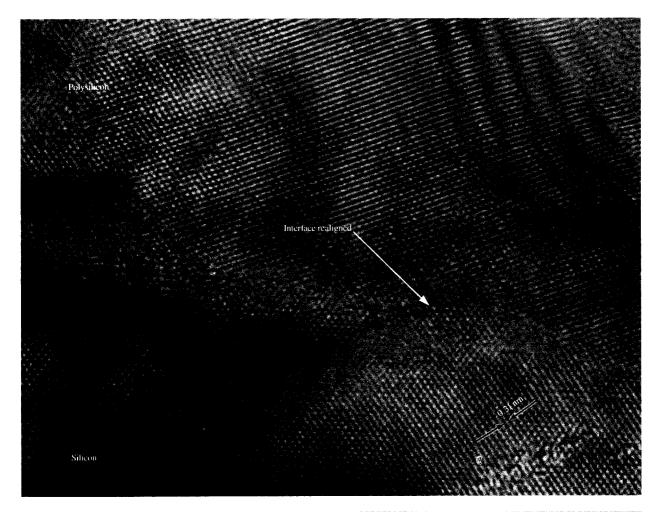

## **Cross-sectional TEM**

The high base-current density, low emitter resistance, and relatively shallow junction depth of the 900°C device mentioned in the previous section all indicate that the effect of the polysilicon/single-crystal interface on the device characteristics is minimal. The very high in situ doping level  $(1 \times 10^{21} \text{ cm}^{-3} \text{ from SIMS})$ , wet-etched emitter opening, and BHF cleaning before polysilicon deposition are favorable conditions for epitaxial realignment of the polysilicon. As shown in [8, 10] and [7, 9, 11], high doping levels reduce the critical temperature for realignment and result in an increase in I<sub>b</sub>. Indeed, as shown in Figure 6, the base-current density of the emitter annealed at 900°C has reached a value close to what can be expected when the polysilicon is perfectly aligned to form an extended single-crystal emitter. For the other devices shown in Figure 6, which were annealed at higher temperatures or for longer times, it was shown [7]

### 37.777.78.3

Sine-hyperbolic *I-V* relation of the poly-emitter contact annealed at 800°C. The 900°C transistor showed ohmic behavior.

Base current for various emitter annealing conditions. It appears that the "saturation" value of an extended single-crystal emitter is obtained for lower and shorter annealing conditions when the effective doping of the poly  $(N_{\rm poly} = {\rm doping\ concentration})$  is increased.

that a noticeable increase in base current occurs when the residual native interface *begins* to break up. Although annealed in an oxygen ambient (shown to favor realignment of boron-doped poly [19]), the low-temperature (900°C)

XTEM photograph of the polysilicon/single-crystal interface: (a) Low magnification, showing global features of the polysilicon layer.

emitter anneal was short enough to cause us to question the amount of interface restructuring. To determine whether restructuring had occurred in the devices annealed at 900°C, an actual transistor was examined by cross-sectional TEM. The results are shown in Figures 7(a) and 7(b). The high-magnification lattice image in Figure 7(b) clearly shows realignment at the interface. No evidence is present of any remaining interfacial oxide: Because of the low annealing temperature the oxide might not have "balled" sufficiently to become visible. However, because a lattice image is visible for almost all grains, these polysilicon grains must have aligned to some degree.

# Switching performance

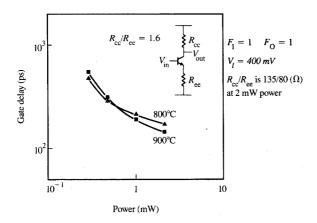

The essential device parameters for switching performance, such as the junction capacitances and  $f_{\rm T}$ , are also summarized in Table 1. The extrinsic base capacitance for the 900°C devices was substantially higher because the

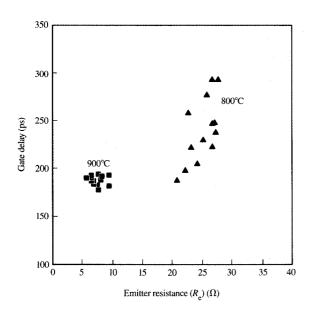

extrinsic base drive-in was different for the two types of devices. The intrinsic base delay, which was extracted by plotting  $1/f_T$  versus  $1/I_c$ , was equivalent and was not affected by high injection effects at the measured power levels because of the thin epitaxial layer used. The impact on switching performance was addressed by measuring both emitter-coupled logic (ECL) and non-threshold logic (NTL) ring-oscillators. The power delay curves in Figure 8 show the impact of the principal delay components: The smaller extrinsic base-collector capacitance (shallower junction) for the transistors annealed at 800°C allows faster operation at low power levels, but the larger emitter resistance leads to a considerable increase in delay at higher currents. This high current delay for an NTL circuit is plotted in Figure 9 versus emitter resistance. Similar results are obtained for ECL circuits. The large spread in delay for the high-resistance data is a result of a wider spread in the dc characteristics of the high-resistance devices. The large variability in resistance is

Figure 7(b)

XTEM photograph of the polysilicon/single-crystal interface: (b) Highest magnification-lattice fringes are visible and are clearly continuous through the interface at many places.

actually more of a concern, because that prevents accurate tracking and adds to the noise margin. Although it would be more appropriate to use the resistance averaged over the voltage swing, it is difficult to eliminate measurement-induced disturbances of the waveform to extract the actual voltage-versus-time behavior. Thus, only the resistance for one particular current level is given, as this is not expected to change the observed correlation between resistance and gate delay.

# Implications for further scaling

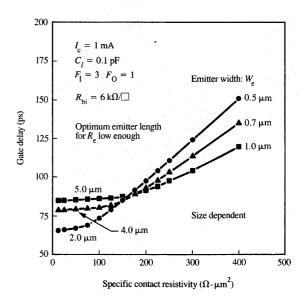

As a result of the use of polysilicon emitter contacts to achieve advanced profiles, circuit performance is now more sensitive to device and contact geometry. An increase in specific emitter contact resistance reduces transconductance and precludes optimum performance at high current densities [20]. In Figure 10, calculation results demonstrate

the effect of high contact resistance on ECL gate delay. Starting with zero contact resistance, the emitter length was adjusted to obtain maximum speed for a given minimum emitter width. As the specific contact resistivity increased, the emitter length was adjusted to keep the voltage drop across the emitter contact below one kT/q. It can be seen that enlarging the contact area results in speed degradation: Even though the length-to-width aspect ratio of the emitter reduces the base resistance, all capacitances increase such that narrow emitters become the slowest. These results indicate that a specific contact resistivity of less than 150–200 Ω- $\mu$ m<sup>2</sup> is required to take advantage of the highcurrent-speed potential of emitter widths less than 1.0  $\mu$ m. Even lower values will be needed for 0.5- $\mu$ m technologies. Even if the effect of the polysilicon/single-crystal interface were negligible, a contact resistivity below 100  $\Omega$ - $\mu$ m<sup>2</sup> would be difficult to obtain. For example, this would require an

Measured power-delay curves for NTL circuits. ( $F_{\rm I}$  and  $F_{\rm O}$  are the fan-in and fan-out for the circuit, respectively.)

### Harrie S

NTL delay versus emitter resistance. Delay was measured at constant current (logic swing varied from 0.35–0.43 V). Total power was approximately 1.1 mW per gate.

active doping concentration of  $4 \times 10^{20}$  cm<sup>-3</sup> for an n<sup>+</sup>-Si-Al contact potential. Because of the clustering of As atoms at lower processing temperatures (and segregation to the grain boundaries in the case of polysilicon), either *in situ*

### Same III

Impact of emitter resistance on delay for scaled devices. The specific contact resistance of the 800°C emitter anneal would be unusable for submicron devices.

doping or  $1000^{\circ}$ C rapid thermal anneals are required to obtain such low contact resistivities. Moreover, the data of Figure 10 clearly indicate that the specific contact resistance of  $200~\Omega$ - $\mu$ m<sup>2</sup> (see Table 1) attained by annealing at  $800^{\circ}$ C precludes the use of this annealing temperature for the fabrication of submicron devices. In any case, very tight control is needed to prevent emitter resistance variations from determining the minimum usable emitter area in circuit design.

### **Conclusions**

From both dc and ac electrical characteristics, as well as XTEM analysis, we conclude that the microstructure of highly As-doped ( $1 \times 10^{21} \text{ cm}^{-3}$ ) polysilicon, annealed at temperatures as low as 900°C, results in emitter electrical characteristics resembling those of extended single-crystal silicon. The base current in these recrystallized polysilicon emitters was higher in comparison with a more-or-less continuous polysilicon/single-crystal interface, but appears tolerable for circuit design, in particular because of the smaller spread in device characteristics. The better reproducibility of the emitter as a diffusion source with lower and more tightly controlled contact resistance leads to greater reliability and superior speed performance in highcurrent switching applications. Simulation shows that increasingly lower specific contact resistivity is demanded at design rules for smaller circuits. Any residual effects of the

native oxide between the polysilicon/single-crystal silicon interface are expected to be intolerable for submicron, high-performance digital devices. In order to obtain the very highly doped, abrupt emitter profiles of the future, other alternatives for emitter doping and dopant activation have to be explored.

# **Acknowledgment**

Many discussions with M. Arienzo and C. Y. Wong of the Yorktown Research Center during the early stages of this work are greatly appreciated. Special thanks also go to M. J. Smyth and B. J. Ginsberg for the sample preparation.

### References

- 1. M. Takagi, K. Nakayama, C. Terada, and H. Kamioka, "Improvement of Shallow Base Transistor Technology by Using a Doped Poly-Silicon Diffusion Source," J. Jpn. Soc. Appl. Phys. (Suppl.) 42, 101-109 (1973).

- T. H. Ning and R. D. Isaac, "Effect of Emitter Contact on Current Gain of Silicon Bipolar Devices," *IEEE Trans. Electron Devices* ED-27, 2051–2055 (November 1980).

- A. Neugroschel, M. Arienzo, Y. Komem, and R. D. Isaac, "Experimental Study of the Minority-Carrier Transport at the Polysilicon-Monosilicon Interface," *IEEE Trans. Electron Devices* ED-32, 807–816 (April 1985).

- H. C. de Graaff and J. G. de Groot, "The SIS Tunnel Emitter: A Theory for Emitters with Thin Interface Layers," *IEEE Trans. Electron Devices* ED-26, 1771–1776 (November 1979).

- J. M. C. Stork, C. Y. Wong, and M. Arienzo, "Polysilicon Emitter Resistance and Carrier Transport Studies," Symposium on VLSI Technology, Digest of Technical Papers, May 1985, pp. 54-55; IEEE, 345 E. 47th St., New York, NY 10017.

- J. M. C. Stork, M. Arienzo, and C. Y. Wong, "Correlation Between the Diffusive and Electrical Barrier Properties of the Interface in Polysilicon Contacted n<sup>+</sup>/p Junctions," *IEEE Trans. Electron Devices* ED-32, 1766-1770 (September 1985).

- G. L. Patton, J. C. Bravman, and J. D. Plummer, "Physics, Technology, and Modeling of Polysilicon Emitter Contacts for VLSI Bipolar Transistors," *IEEE Trans. Electron Devices* ED-33, 1754–1768 (November 1986).

- N. Jorgensen, J. C. Barry, G. R. Booker, P. Ashburn, G. R. Wolstenholme, M. C. Wilson, and P. C. Hunt, "TEM Investigation of the Effect of Anneal Temperature and Arsenic Concentration on the Polysilicon/Thin-Oxide/Single-Crystal-Silicon Emitter of a New High-Performance Bipolar Transistor," Microscopy of Semiconductor Materials Conference, Digest of Technical Papers, Oxford, England, March 1985.

- G. L. Patton, J. C. Bravman, and J. D. Plummer, "Characterization of Bipolar Transistors with Polysilicon Emitter Contacts," Symposium on VLSI Technology, Digest of Technical Papers, September 1984, pp. 54–55; IEEE, 345 E. 47th St., New York, NY 10017.

- M. C. Wilson, N. Jorgensen, G. R. Booker, and P. C. Hunt, "Electrical and Microstructural Investigation into the Effect of Arsenic Emitter Concentration on the Enhanced Gain Polysilicon Emitter Bipolar Transistor," Symposium on VLSI Technology, Digest of Technical Papers, May 1985, pp. 46–47; IEEE, 345 E. 47th St., New York, NY 10017.

- J. C. Bravman, G. L. Patton, and J. D. Plummer, "Structure and Morphology of Polycrystalline Silicon-Single-Crystal Silicon Interfaces," J. Appl. Phys. 57, 2779–2782 (April 1985).

- D. D. Tang, K. P. MacWilliams, and P. M. Solomon, "Effects of Collector Epitaxial Layer on the Switching Speed of High-Performance Bipolar Transistors," *IEEE Electron Device Lett.* EDL-4, 17-19 (January 1983).

- T. H. Ning and D. D. Tang, "Method for Determining the Emitter and Base Resistances of Bipolar Transistors," *IEEE Trans. Electron Devices* ED-31, 409-412 (April 1984).

- B. Ricco, J. M. C. Stork, and M. Arienzo, "Characterization of Non-Ohmic Behavior of Emitter Contacts of Bipolar Transistors," *IEEE Electron Device Lett.* EDL-5, 221-223 (July 1984).

- J. M. C. Stork, "Non-Ohmic Series Resistance of Advanced Bipolar Transistors: Current Crowding or Poly-Emitter Resistance?" Research Report RC-12412, IBM Thomas J. Watson Research Center, Yorktown Heights, NY, 1986.

- R. Stratton, "Volt-Current Characteristics for Tunneling Through Insulating Films," J. Phys. Chem. Solids 23, 1177-1190 (1962).

- E. Crabbe, S. Swirhun, R. F. Pease, and R. M. Swanson, "Non-Linear Behavior of Polysilicon-Emitter Contacts," Proceedings of the 15th European Solid State Device Research Conference, September 1985.

- W. J. M. J. Josquin, P. R. Boudewijn, and Y. Tamminga, "Effectiveness of Polycrystalline Silicon Diffusion Sources," *Appl. Phys. Lett.* 43, 960–962 (November 1983).

- M. Ghannam and R. W. Dutton, "Characterization and Modeling of Boron Diffusion for Polysilicon-Silicon Interfaces," Proceedings of the 1986 Bipolar Circuits and Technology Meeting, September 1986, pp. 5-6; IEEE, 345 E. 47th St., New York, NY 10017.

- J. M. C. Stork and J. D. Cressler, "The Impact of Non-Ohmic Polysilicon Emitter Resistance on Bipolar Transistor Performance," Symposium on VLSI Technology, Digest of Technical Papers, May 1986, pp. 47-48; IEEE, 345 E. 47th St., New York, NY 10017.

Received March 3, 1987; accepted for publication May 19, 1987

Johannes M. C. (Hans) Stork IBM Thomas J. Watson Research Center, P.O. Box 218, Yorktown Heights, New York 10598. Dr. Stork is currently manager of exploratory device and process modeling activities in the Silicon Technology Department. He joined IBM in 1982, first as a member of the bipolar technology group and later in the device and circuits group. In 1985 he joined the exploratory structures activities, emphasizing thin-base bipolar transistors. Dr. Stork received the Ingenieur degree in electrical engineering (cum laude) from Delft University, The Netherlands, in 1978, and his Ph.D. in electrical engineering from Stanford University, Stanford, California, in 1982. Dr. Stork is a member of the Institute of Electrical and Electronics Engineers.

Eti Ganin IBM Thomas J. Watson Research Center, P.O. Box 218, Yorktown Heights, New York 10598. Dr. Ganin joined IBM as a visiting scientist in 1985. She is currently involved with processing ultrasmall device structures in the exploratory structures group in the Silicon Technology Department. She is also studying ion implantation damage and dopant interaction related to shallow-junction formation for silicon devices. Dr. Ganin graduated from the Leningrad Polytechnical Institute, Faculty of Physics and Mechanics, Leningrad, U.S.S.R. She received her M.S. and D.Sc. degrees from the Technion-Israel Institute of Technology in Haifa, Materials Engineering Department. Her D.Sc. dissertation, completed in 1984, concerned the nature of bonding between explosively welded copper and its alloys. Dr. Ganin is a member of the American Physical Society and the Materials Research Society.

**John D. Cressler** *IBM Thomas J. Watson Research Center, P.O. Box 218, Yorktown Heights, New York 10598.* Mr. Cressler joined the IBM Research Center in 1984 in the bipolar device and circuits

group. His work has centered on the characterization and analysis of advanced bipolar structures. More recently, he has been interested in transport phenomena in heavily doped crystalline and polycrystalline silicon films. Mr. Cressler received the B.S. degree in physics from the Georgia Institute of Technology, Atlanta, in 1984. During his undergraduate studies he was employed as a cooperative student in a FET development group at the IBM Raleigh facility. In 1987 he received the M.S. degree in solid-state physics from Columbia University, New York. He is currently pursuing his doctorate at Columbia, also in solid-state physics. Mr. Cressler is a member of the Institute of Electrical and Electronics Engineers.

Gary L. Patton IBM Thomas J. Watson Research Center, P.O. Box 218, Yorktown Heights, New York 10598. Dr. Patton joined IBM in 1986 and is a member of the exploratory device and process modeling group in the Silicon Technology Department. His work in the exploratory area has emphasized the physics and technology of silicon heterostructure devices. Dr. Patton received the B.S. degree in electrical engineering (summa cum laude) from the University of California, Los Angeles, and the M.S. and Ph.D. degrees in electrical engineering from Stanford University, Stanford, California, the latter in 1986. His Ph.D. dissertation concerned the physics, technology, and modeling of polysilicon emitter contacts for bipolar transistors. Dr. Patton is a member of the American Physical Society, the Electrochemical Society, and the Institute of Electrical and Electronics Engineers.

George A. Sai-Halasz IBM Thomas J. Watson Research Center, P.O. Box 218, Yorktown Heights, New York 10598. Dr. Sai-Halasz joined the research staff of the Watson Research Center in 1974. His scientific contributions are in the fields of ionic transport in quantum solids; nonequilibrium superconductivity; the physics and device aspects of semiconductor superlattices; material improvements in SOS and in phosphorescent substances; statistical modeling of radiation-induced soft-error rates in VLSI circuits; and physics and materials problems associated with downscaling of silicon devices into the submicron regime. Dr. Sai-Halasz graduated in physics from Roland Eötvös Science University, Budapest, Hungary, in 1966. He received the Ph.D degree in physics from Case Western Reserve University, Cleveland, Ohio, in 1972. He spent the following two years, before coming to IBM, as a Postdoctoral Fellow at the Physics Department of the University of Pennsylvania.