# Signal degradation through module pins in VLSI packaging

by Ching-Chao Huang Leon L. Wu

This paper investigates chip-to-chip communication through the modules and board in VLSI packaging. Transmission line models and frequency-dependent transmission line parameters are used in finding the frequency response. The time-domain solution is then obtained through the inverse Fast Fourier Transform. The results show that uncoated module pins, even of relatively short length, can cause severe signal degradation because of their magnetic property. The signal behavior is improved dramatically, however, when the module pins are coated with nonmagnetic conductive material.

# Introduction

The thermal stress caused by the heat dissipation of bipolar integrated circuit chips makes it necessary to match the thermal coefficients of pins attached to the substrate. Many nickel-iron alloys (e.g., Kovar and Invar) have low expansion coefficients and are good candidates for use as module pins. However, with relative permeability ranging up to several thousands [1], the magnetic property of such

<sup>®</sup>Copyright 1987 by International Business Machines Corporation. Copying in printed form for private use is permitted without payment of royalty provided that (1) each reproduction is done without alteration and (2) the *Journal* reference and IBM copyright notice are included on the first page. The title and abstract, but no other portions, of this paper may be copied or distributed royalty free without further permission by computer-based and other information-service systems. Permission to *republish* any other portion of this paper must be obtained from the Editor.

alloys can have an adverse effect on signal propagation. The following study shows that the magnetic module pins, even though of relatively short length, can cause severe signal degradation in chip-to-chip communication. Dramatic improvements are obtained, however, when the pins are coated with even a very thin layer of good nonmagnetic conductor.

# **Analysis**

# Model

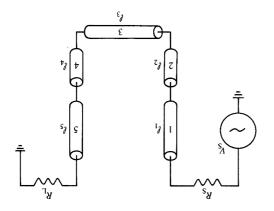

Figure 1 shows an example of a VLSI package in which the integrated circuit chips are mounted on the modules, and the modules are, in turn, mounted on the board. The signal path from one chip to another through the module(1)-pin(2)-board(3)-pin(4)-module(5) connection is now modeled by five sections of transmission lines, as shown in Figure 2. The driver in Chip A is represented by an ideal voltage source in series with a resistor  $R_s$  (= 10 ohms). A terminator  $R_1$  (= 50 ohms) is placed in front of a receiver in Chip B to reduce the signal reflection from a receiver (note that the receiver has a high input impedance). To single out the effect of the pins, it is assumed that ideal 50-ohm lines are achieved in both the modules and the board. The propagation constants are different, however, in that different materials, ceramic (with dielectric constant  $\varepsilon_r = 9.5$ ) and epoxy glass ( $\varepsilon_r = 4.5$ ), are used for the modules and the board, respectively.

The voltage at the receiver,  $V_o$ , is now solved in the frequency domain first. The voltage  $V_i$  and current  $I_i$  (i = 1-5) in each transmission line can be represented by the following [2]:

489

(01)

(6)

(8)

$$V_{o}(\omega) = V_{s}(V_{s})$$

$$V_{o}(\omega) = V_{s}(V_{s})$$

$$V_{o}(\omega) = V_{s}(V_{s})$$

voltage,  $V_o$ , is simply given by  $V_{\rm a}=1.044$  volt. After one finds  $V_{\rm 5}^+$  and  $V_{\rm 5}^-$  the output In the following, we let b = 250 ps, c = 10 ns, and

(6)

$$\int_{\zeta/(2+d)\omega/-2} \frac{(\zeta/2\omega) \operatorname{nis}}{\zeta/2\omega} \frac{(\zeta/4\omega) \operatorname{nis}}{\zeta/4\omega} z_{\mathbb{F}} V = (\omega)_{\mathbb{F}} V$$

as follows:

067

a trapezoidal waveshape  $V_S(t)$ , as shown in Figure 2,  $V_S(\omega)$  is matrix.  $V_{\rm S}$  is the Fourier transform of the source voltage. For  $[V_Q]^{1} = [V_S, 0, 0, \cdots, 0]_{1 \times 10}$ . T denotes the transpose of the where  $[A] = [A_{ij}]_{10 \times 10}$ ,  $[V]^T = [V]^+$ ,  $V_i = [V]^+$ ,  $V_i = [V]$  and

$$(\xi) \qquad \qquad (\xi_Q) = [V][K]$$

between transmission lines, one has (see Appendix A)

By matching the boundary conditions at each interface pin regions are discussed in the next section. The transmission line parameters  $(R_{eff}, L_{eff}, G_{eff}, C_{eff})$  for the

and 0 is  $z \le 0$ ,  $\delta_{1,1,2} = \delta_{1,1,3} = \delta_{1,1,3} = \delta_{1,1,3}$ ;  $\delta_{1,1,2} \le \delta_{1,1,3} = \delta_{1,1,3}$

$$=\sqrt{(R_{eff}+j\omega L_{eff})(G_{eff}+j\omega C_{eff})} \qquad \text{for } i=2, 4, \qquad (4b)$$

$$e \gamma_i = j_\omega \ \sqrt{\epsilon_{ii}}/\epsilon_o$$

for  $i = i$ ,  $3$ ,  $5$ ,  $(4a)$

$$=\sqrt{(G_{eff}+j\omega C_{eff})/(R_{eff}+j\omega L_{eff})} \quad \text{for } i=2, 4, \qquad (3b)$$

$$Y_{ci} = 0.02 \text{ mho} \qquad \text{for } i = i, 3, 5, (3a)$$

se),

$$\xi$$

,  $\xi$ ,  $l = i$  rod often  $10.0 = 10.0$

where

(2)

$$X_{i}^{\prime}(z) = X_{i}^{\prime}(\Lambda_{+}^{+} \delta_{-\lambda iz}^{-} - \Lambda_{-}^{-} \delta_{+\lambda iz}^{+}),$$

$$(z) = X_{i} \left( V_{i}^{\dagger} - V_{i}^{\dagger} - V_{i}^{\dagger} \right), \quad (z)$$

(I)

$${}^{\prime}_{z^{l}\lambda_{+}} \partial_{-}^{l} \Lambda + {}_{z^{l}\lambda_{-}} \partial_{+}^{+} \Lambda = (z)^{l} \Lambda$$

(1)

$$i_{z/y}^{+} + i_{z/y}^{-} + i_{z/y}^{+} = (z)_{z/y}^{+}$$

Chip-to-chip communication through the modules and board.

250 ps, c = 10 ns.

Model of the signal path in Figure 1. Here,  $l_1 = l_3 = l_5 = 0$  cm,  $l_2 = l_3 = l_3$  with,  $l_3 = l_3 = l_3$

# preod иiЧ Module Chip A

$L_{\text{ext}} = \frac{\mu_0}{2\pi} \left( \ln \frac{2\ell}{a} - 1 \right),$

$, \frac{(n\tilde{\chi})_{o}l}{(n\tilde{\chi})_{i}l} \frac{\tilde{\chi}}{nn\pi \Delta} =$

inductance, respectively, and are given by [3, 4]

a finite circular cylinder can be written as

• R, L, G, C of the module pins

where  $Z_{int}$  and  $L_{ext}$  are the internal impedance and external

resistance, the impedance per unit length,  $Z(=R+j\omega L)$ , of

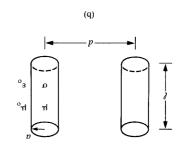

cylinders, as shown in Figure 3. By neglecting the radiation The module pins are now modeled by finite circular

main using the inverse Fast Fourier Transform (FFT) algo-The frequency response is then transformed to the time do-

$\lim_{i \neq j} J_{\omega_i} - \lim_{i \neq j} X = \lim_{i \neq j} X$

$Z = Z_{int} + j\omega L_{ext},$

psvoogisg cass

rithm.

:[4] gniwolloì

inductance is small, and the mutual inductance per unit length,  $M_{\rm s}$  between the module pins is calculated through the

at high frequency. Here,  $\delta_S (= \sqrt{2}/\omega\mu\sigma)$  is the skin depth. The effect of the conductor's permeability on the mutual

$$(21) p/s \delta \zeta \approx T$$

where  $0 \le T \le 1$ ; T = 1 at low frequency, and

(11)

$$T \frac{\mu}{\pi 8} + \left(1 - \frac{12}{b} \pi I\right) \frac{\omega \mu}{\pi \zeta} = \Delta$$

following form [4]:

where  $\zeta = \sqrt{\log \mu \sigma_i}$ ,  $\sum_{i=1}^{n}$  denotes the complex conjugate of that Equation (10) is actually a low-frequency formula, which is independent of frequency. The total self-inductance  $L(=L_{int}+L_{ext})$  per unit length can also be written in the

Module pins modeled by finite circular cylinders.

# g almbig

R<sub>eff</sub>, L<sub>eff</sub>, G<sub>eff</sub>, G<sub>eff</sub> in the pin regions

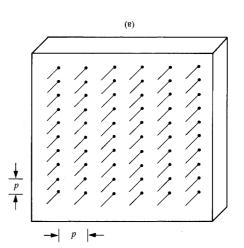

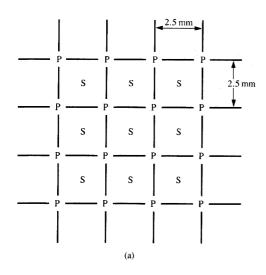

The module pins are assigned to carry both power and

signal. Power pins are usually distributed uniformly to

minimize cross talk between signal pins. Figure 6(a) shows a

typical configuration with a ratio of one signal to one power

pin. To examine the signal degradation through a pin, we

both coated and uncoated circular cylinders.

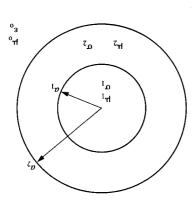

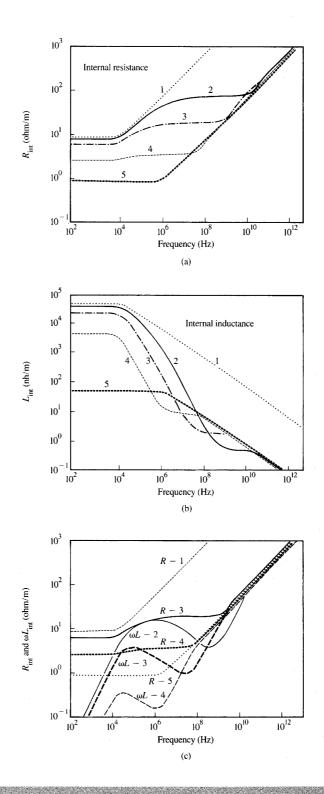

Here,  $\zeta_1 = \sqrt{j\omega\mu_1\sigma_1}$ ,  $\zeta_2 = \sqrt{j\omega\mu_2\sigma_2}$ , and  $N_n(\cdot)$  is the nth order of Neumann's function. Equations (10) and (13) can still be used to calculate  $L_{\rm ext}$  and M except that a is replaced by  $a_2$ . Figure S(a-c) shows the calculated  $R_{\rm int}$ ,  $L_{\rm int}$  and  $\omega L_{\rm int}$  for

(61)

$$\frac{({}_{1}s_{2}\xi)_{1}L({}_{1}s_{1}\xi)_{o}L\frac{\underline{\varsigma}^{\zeta}{}_{1}\mu}{{}_{1}\xi^{\zeta}\underline{\varsigma}\mu} - ({}_{1}s_{1}\xi)_{1}L({}_{1}s_{2}\xi)_{o}L}{({}_{1}s_{2}\xi)_{1}N({}_{1}s_{1}\xi)_{o}L\frac{\underline{\varsigma}^{\zeta}{}_{1}\mu}{{}_{1}\xi^{\zeta}\underline{\varsigma}\mu} - ({}_{1}s_{1}\xi)_{1}L({}_{1}s_{2}\xi)_{o}N} = G$$

put

(51)

$$\frac{\frac{1}{(c_1 c_2 c_3)^{1/N}} C - 1}{\frac{(c_2 c_3)^{1/N}}{(c_3 c_3)^{1/N}} C - 1} = B$$

vnere

(14)

$$k_{\text{ini}} = \frac{1}{\lambda^2 \alpha_2 \lambda_0} \int_{1/2} \frac{\zeta_2}{\lambda_1 (\zeta_2 \alpha_2)} B,$$

(9) is now replaced by

Coated case For a coated cylinder, as shown in Figure 4,  $X_{int}^*$  in Equation

Cross section of a coated circular cylinder.

# t pains

# E Prince E

(a)  $R_{\text{int}}$ , (b)  $L_{\text{int}}$ , and (c)  $R_{\text{int}}$  and  $\omega L_{\text{int}}$  of coated and uncoated circular cylinders: 1—solid Invar (a = 6.80 mils); 2—Invar ( $a_1 = 6.75 \text{ mils}$ ) + Pd coating ( $a_2 - a_1 = 0.05 \text{ mil}$ ); 3—Invar ( $a_1 = 6.75 \text{ mils}$ ) + Pd coating ( $a_2 - a_1 = 0.20 \text{ mil}$ ); 4—Invar ( $a_1 = 6.75 \text{ mils}$ ) + Pd coating ( $a_2 - a_1 = 1 \text{ mil}$ ); 5—solid Pd (a = 7.75 mils).  $\mu/\mu_{o} = 1000 \text{ is assumed for Invar}$ .

Signal (S)-power (P) pin pattern

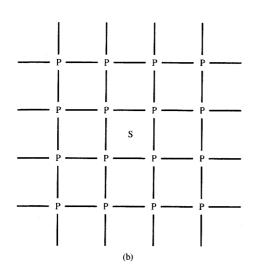

retain only one signal pin and try to include as many power pins as possible for the ground reference. Thus, the pin array for studying the signal degradation is now reduced to that of **Figure 6(b)**. **Figure 7** shows the circuit equivalent (without capacitance) of Figure 6(b), where the power pins are shorted together at both ends. For a two-port system, as in Figure 7, the following equation can be derived:

$$[\tilde{Z}][\tilde{I}] = [\tilde{V}_{Q}], \tag{17a}$$

Partial circuit representation (without capacitance) of module pins.

$$\begin{bmatrix} R + j\omega L & j\omega M_{S1} & j\omega M_{S2} & \cdots & j\omega M_{SN} \\ j\omega M_{S1} & R + j\omega L & j\omega M_{12} & \cdots & j\omega M_{1N} \\ j\omega M_{S2} & j\omega M_{12} & R + j\omega L & \cdots & j\omega M_{2N} \\ \vdots & \vdots & \ddots & \vdots \\ j\omega M_{SN} & j\omega M_{1N} & j\omega M_{2N} & \cdots & R + j\omega L \end{bmatrix}$$

(17b)

and

$$[\tilde{I}] = [\tilde{I}_{S}, \tilde{I}_{1}, \tilde{I}_{2}, \dots, \tilde{I}_{N}]_{1 \times (N+1)}^{T},$$

(17c)

$$[\tilde{V}_{O}] = [\tilde{V}_{S}, \, \tilde{V}, \, \tilde{V}, \, \cdots, \, \tilde{V}]_{1 \times (N+1)}^{T}, \tag{17d}$$

In turn, Equations (17a-d) can be reduced to the following (see Appendix B):

$$\begin{bmatrix} Z_{11} & Z_{12} \\ Z_{12} & Z_{22} \end{bmatrix} \quad \begin{bmatrix} \tilde{I}_{S} \\ \sum_{n=1}^{N} \tilde{I}_{n} \end{bmatrix} = \begin{bmatrix} \tilde{V}_{S} \\ \tilde{V} \end{bmatrix}. \tag{18}$$

Note that  $\tilde{I}_{\rm S} = -\sum_{n=1}^N \tilde{I}_n$ . The effective impedance,  $Z_{\rm eff}$  (=  $R_{\rm eff} + j\omega L_{\rm eff}$ ), of the pin region is then given by

$$Z_{\text{eff}} = Z_{11} + Z_{22} - 2Z_{12}. \tag{19}$$

Assuming a TEM mode propagation in the air medium,  $C_{\rm eff}$  is then given by

$$(17a) \quad C_{\text{eff}} = \frac{\mu_0 \varepsilon_0}{L_{\text{eff}}} \bigg|_{\omega \to \infty}. \tag{20}$$

493

Same

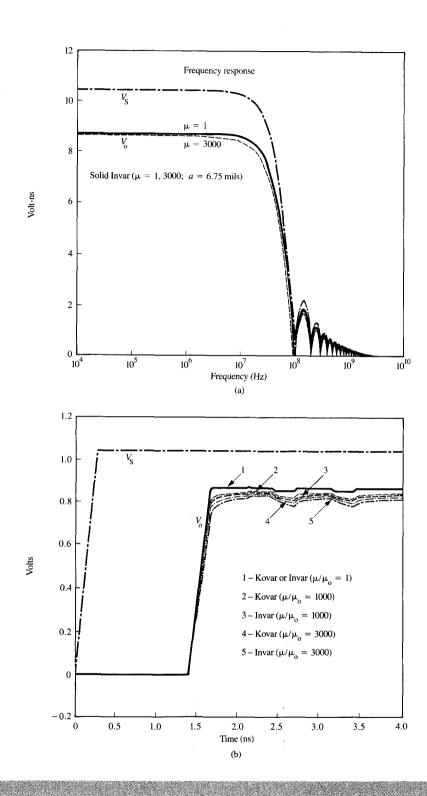

(a) Frequency and (b) time response of  $V_0$  where solid Invar and Kovar pins (a = 6.75 mils) are used, respectively.

Note that as  $\omega \to \infty$ ,  $L_{\rm int} \to 0$ ,  $L \approx L_{\rm ext}$ , and  $R \ll \omega L$ . Also, the air medium is assumed to be lossless, and thus  $G_{\rm eff} = 0$ .

**Table 1** shows an example of the calculated  $L_{\text{eff}}$  as a function of frequency and the number of power pins included. The power pins are chosen to be located symmetrically around the signal pin in a square pattern. The signal to power current ratios are also shown for comparison. Apparently, the lower the frequency, the more power pins must be included to get high accuracy. Here,  $L_{\text{eff}}$  at f = 5 MHz is of interest because it is the lowest harmonic that we used in the inverse FFT (the frequency response is sampled every 5 MHz). Besides the harmonics, a dc value is required in the inverse FFT. Note that at dc an infinite number of power pins (or, more realistically, all power pins in a module) should be included because the ground return current will flow uniformly through all power pins. Fortunately, the above procedures need not be followed at dc because as  $\omega \to 0$ ,  $R_{\rm eff} \to R$  and  $\omega L_{\rm eff} \ll R_{\rm eff}$ , and  $V_{\rm o}$  is simply given by

$$V_{\rm o}(\omega = 0) \approx V_{\rm a} c \, \frac{R_{\rm L}}{R_{\rm S} + R_{\rm L} + 2R}.$$

(21)

Except at dc, all the results shown in the following section were calculated with 16 power pins included.

# Results

Figure 8 shows the frequency and time response of  $V_0$  when solid Invar ( $\sigma = 1.215 \text{ mho}/\mu\text{m}$ ) and Kovar ( $\sigma = 2.041$ mho/ $\mu$ m), respectively [1], are used for the module pins (a = 6.75 mils). The frequency response, sampled at 5 MHz, was converted to the time response using a 16 384-point inverse FFT algorithm. Generally speaking, more attenuation and slower rise time are observed as  $\mu$  is increased. In a high-speed computer package environment, false switching and excessive delay have to be avoided [5]. The seemingly extra dc voltage drop for larger  $\mu$  in Figure 8, actually caused by the RC delay, can make the receiver more susceptible to noise. The voltage dip, caused by the reflection from the impedance mismatch between the pins and the modules/board, in conjunction with the coupled noise and delta-I noise [5], if large enough, may penetrate the receiver's threshold band and make it false-switch. One observes that the signal degradation in Figure 8 is less dependent on  $\mu$  when the more conductive material is used. Thus, when uncoated, the more conductive Kovar will be better than Invar electrically. In fact, if a perfect conductor  $(\sigma \rightarrow \infty)$  were used,  $\mu$  would have no effect on the signal response at all. [One may note in Equation (8) that, as  $\sigma \to \infty$ ,  $Z \approx j\omega L_{\rm ext}$ .

Figure 9 shows the signal behavior when the Invar module pins are coated with 0.2 mil of Pd ( $\sigma = 9.259 \text{ mho/}\mu\text{m}$ ). One

**Table 1**  $L_{\text{eff}}$  vs. number of power pins (solid Invar pins are assumed, with a = 6.75 mils,  $\ell = 85$  mils, and  $\mu/\mu_0 = 1$ ).

| No. of power pins | Frequency<br>(MHz) | Current ratio*   | $L_{ m eff} \ (\mu { m h/m})$ |

|-------------------|--------------------|------------------|-------------------------------|

| 4                 | 5                  | 1:0.25:0.25      | 0.452                         |

|                   | ∞                  | 1:0.25:0.25      | 0.390                         |

| 16                | 5                  | 1:0.1275:0.03940 | 0.4286                        |

|                   | <b>∞</b>           | 1:0.1538:0.02665 | 0.369                         |

| 36                | 5                  | 1:0.1199:0.01296 | 0.42773                       |

|                   | ∞                  | 1:0.1466:0.00842 | 0.3674                        |

| 64                | 5                  | 1:0.1189:0.00563 | 0.42771                       |

|                   | ∞                  | 1:0.1452:0.00341 | 0.36703                       |

| 100               | 5                  | 1:0.1186:0.00273 | 0.427726                      |

|                   | œ                  | 1:0.1447:0.00157 | 0.366895                      |

◆Current ratio = signal current: maximum power current: minimum power current.

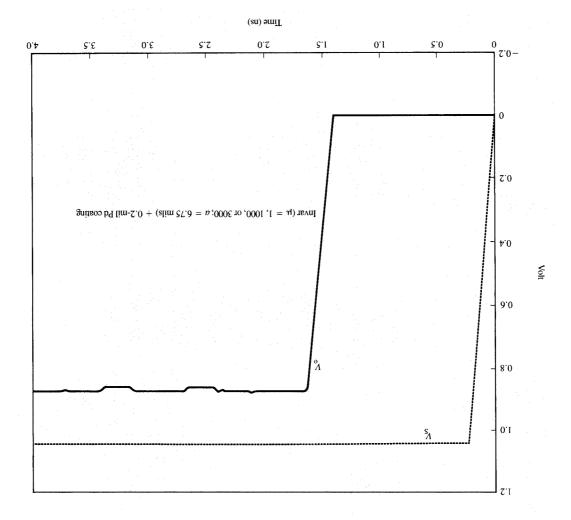

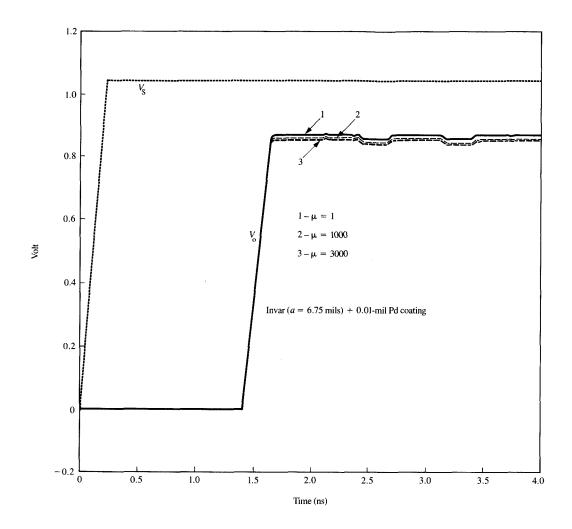

observes that the signal response is improved dramatically when the pins are coated with even a thin layer of nonmagnetic conductor ( $\mu = \mu_o$ ). The difference in the resultant signal response becomes negligible when both Kovar and Invar pins are suitably coated. Thus, one may choose freely between coated Kovar and coated Invar pins, so far as the electrical design is concerned. **Figure 10** shows the result with 0.01 mil of Pd plating, just to illustrate that an extremely thin layer of coating, which is not common, may not be good enough.

# **Conclusions**

This paper has studied signal behavior in chip-to-chip communication due to the discontinuity of the module pins. The module pins, made of nickel-iron alloy (either Kovar or Invar), are of concern because of their magnetic property. In this analysis, the frequency-dependent transmission line parameters in the pin regions are calculated analytically for both uncoated and coated cases. The effect of the number of power pins to be included as the ground reference was also demonstrated. The signal response was illustrated in both the frequency and time domains. It was shown that the severe signal degradation due to the magnetic module pins can be eliminated by even a thin coating of good nonmagnetic conductor. That the signal response becomes relatively insensitive to the inner conductor's magnetic property  $(\mu)$ can be understood, because at low frequency, R is independent of  $\mu$ , and  $R \gg \omega L$ , while at high frequency, R is mostly due to the outer layer, and  $L \approx L_{\rm ext}$ , which is also independent of  $\mu$ . Finally, it is noted that  $\mu$  has been assumed to be a frequency-independent constant in the foregoing analysis. A worst-case scenario was attempted in that  $\mu$  was chosen deliberately large in the calculation. The complex permeability as a function of frequency and magnetic field strength can be easily included in the analysis when such information is available.

Time response of  $V_0$  where the Invar pins (a=6.75 mils) are coated with 0.2 mil of Pd. No difference is observed whether  $\mu/\mu_o=1$ , 1000, or 3000 for Invar.

lines, and (c) between transmission line  $\delta$  and the load. That

$$(1A) \qquad \qquad (1A) \qquad (1B)^{1} + {}_{S}\mathbf{A}(0), \qquad (1A)$$

$$(0)_{i+1}V = (i)_{i}V$$

$$I_{i}(t_{i}) = I_{i+1}(t_{i}),$$

$$V_{s}(\ell_{s}) = I_{s}(\ell_{s})R_{L},$$

In matrix form, one has

where  $1 \le i \le 4$ .

# **Acknowledgment**

Thanks are due to M. Potter for providing information on the module pins. B. J. Rubin's careful review of the manuscript is also appreciated.

# Appendix A: Matrix of [A] to xinteM :A xibneqqA

The boundary conditions in Figure 2 require that the voltage and current be continuous at the interfaces (a) between the source and transmission line 1, (b) between transmission

# Figure 10

Time response of  $V_0$  where the Invar pins (a=6.75 mils) are coated with 0.01 mil of Pd. More signal degradation is observed when Invar has a higher  $\mu$ .

# Appendix B: Reduction of Equation (17)

Equation (17) can be reduced to Equation (18) through the following. Let  $[\tilde{Y}] = [\tilde{Z}]^{-1}$ ; then

$$[\tilde{I}] = [\tilde{Y}]_{(N+1)\times(N+1)} [\tilde{V}_{o}]. \tag{B1}$$

Adding the columns and rows of  $[\tilde{Y}]$  (=  $[\tilde{Y}_{ii}]$ ), one has

$$\begin{bmatrix} \hat{I}_{S} \\ \sum_{n=1}^{N} \hat{I}_{n} \end{bmatrix} = \begin{bmatrix} \hat{Y}_{11} & \sum_{j=2}^{N+1} \hat{Y}_{ij} \\ \sum_{i=2}^{N+1} \hat{Y}_{i1} & \sum_{i=2}^{N+1} \sum_{j=2}^{N+1} \hat{Y}_{ij} \end{bmatrix} \begin{bmatrix} \hat{V}_{S} \\ \hat{V} \end{bmatrix}.$$

(B2)

# References

- Alloy Digest, Engineering Alloys Digest, Inc., Upper Montclair, NJ, August and October 1953.

- 2. R. E. Collin, Foundations for Microwave Engineering, McGraw-Hill Book Co., Inc., New York, 1966.

- J. A. Stratton, Electromagnetic Theory, McGraw-Hill Book Co., Inc., New York, 1941.

- 4. F. Grover, *Inductance Calculations: Working Formulas and Tables*, Dover Publications, New York, 1962.

- E. E. Davidson, "Electrical Design of a High Speed Computer Package," IBM J. Res. Develop. 26, No. 3, 349–361 (May 1982).

Received November 5, 1986; accepted for publication March 24, 1987

Ching-Chao Huang IBM General Technology Division, East Fishkill facility, Route 52, Hopewell Junction, New York 12533. Dr. Huang received the B.S. degree from the National Taiwan University, Taipei, Taiwan, in 1976, and the M.S. and Ph.D. degrees, all in electrical engineering, from Ohio State University, Columbus, Ohio, in 1980 and 1982, respectively. He joined IBM in 1983, and is currently an advisory engineer. His research interests include VLSI package modeling, inductance and capacitance calculation, numerical techniques in electromagnetics, and diffraction theory. Dr. Huang is a member of the Institute of Electrical and Electronics Engineers.

**Leon Li-Heng Wu** *IBM General Technology Division, East Fishkill facility, Route 52, Hopewell Junction, New York 12533.*Dr. Wu is a senior engineer working on advanced package modeling and design. After joining IBM in 1968, he worked on diffusion profile modeling, silicon defect studies, device modeling, and thermal printer design. In 1962, he received his B.S. in electrical engineering from the National Taiwan University, Taipei, Taiwan. Dr. Wu received his M.S. in 1965 and his Ph.D. in 1968, both in electrical engineering, from Carnegie-Mellon University, Pittsburgh, Pennsylvania.