# Analysis of the holding current in CMOS latch-up

by Haruhiro Matino

The holding current in CMOS latch-up with or without well and/or substrate bias has been examined. Measurements indicate that the holding current increases significantly with reverse bias and low shunting base resistance. It is shown that a previous equation for the holding current is inaccurate, and a new equation for holding current with bias is presented.

### 1. Introduction

One of the major problems encountered in implementing the use of CMOS integrated circuits has been the occurrence of latch-up. Various methods to reduce or eliminate latch-up have been discussed [1, 2], but not completely resolved. Estreich [2] has discussed the condition for triggering latch-up in some detail, and in [1, 2] an equation for the holding current is given in terms of the *forward* base-emitter voltage  $V_{\rm BE}$  as

$$I_{\rm H} = \frac{1}{\beta_{\rm npn}\beta_{\rm pnp} - 1} \times \left[ \frac{\beta_{\rm npn}(1 + \beta_{\rm pnp})V_{\rm BEn}}{R_{\rm w}} + \frac{\beta_{\rm pnp}(1 + \beta_{\rm npn})V_{\rm BEp}}{R_{\rm s}} \right], \tag{1}$$

where  $V_{\rm BEn}$  and  $V_{\rm BEp}$  are the external forward voltages necessary for latch-up to occur for the npn and pnp transistors, respectively. This is incorrect physically. The

<sup>®</sup>Copyright 1985 by International Business Machines Corporation. Copying in printed form for private use is permitted without payment of royalty provided that (1) each reproduction is done without alteration and (2) the *Journal* reference and IBM copyright notice are included on the first page. The title and abstract, but no other portions, of this paper may be copied or distributed royalty free without further permission by computer-based and other information-service systems. Permission to *republish* any other portion of this paper must be obtained from the Editor.

holding current is related to the total reverse base-emitter voltage, including the built-in junction potential, as discussed in Section 3.

In addition, the base current direction in the triggering of latch-up and in the sustaining of latch-up has not been made clear in the literature [1–5]. Most authors have considered the triggering condition when the base-emitter is forward-biased by noise, or have confused the triggering and the sustained latch-up condition. However, the sustained latch-up condition after elimination of the noise which triggers latch-up is more important, because holding current is defined only for the sustained latch-up condition after elimination of the triggering signal.

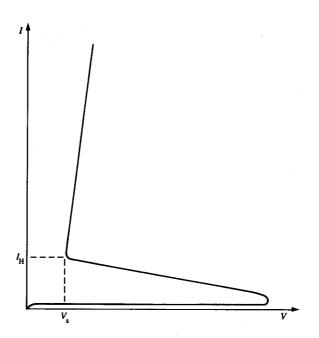

The effects of the substrate or well bias on the holding current and transient triggering conditions have been studied recently [3, 5, 6]. A typical current-voltage latch-up characteristic is shown in **Figure 1**. The holding current  $I_H$  is defined as the current at the sustaining voltage  $V_S$ . In this study, holding current has been measured as a function of the bias voltage for the following: discrete transistor pairs, simulating the case of high current gains for both npn and pnp devices, and integrated n-well CMOS structures in which the npn and pnp devices have relatively low current gain. A physical model and a holding current equation applicable both with and without bias are also presented.

# 2. Experimental results

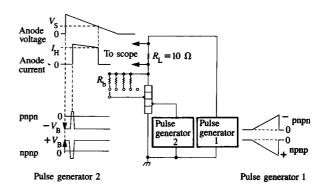

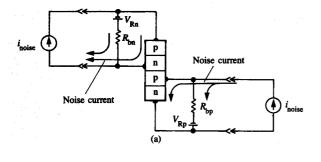

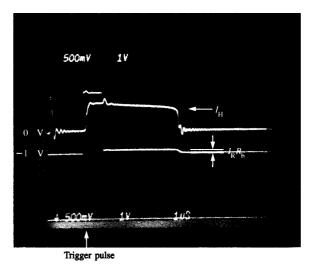

The circuit for measuring the holding current  $I_{\rm H}$  is shown in Figure 2. Pulse generator 2 is used for triggering into the *on* state; the dc *off* set bias is provided as indicated. The external base-emitter shunting resistance  $R_{\rm b}$  can be varied. A sawtooth wave is applied across the structure in order to obtain precise  $I_{\rm H}$  values. After application of the anode voltage by means of pulse generator 1, a triggering pulse sufficient to cause latch-up is applied to the base by means of

pulse generator 2. After the trigger pulse, the base-emitter junction voltage of the device connected to pulse generator 2 returns to the original dc bias voltage. When the anode voltage, which is decreasing gradually, as shown in Fig. 2, drops below the sustaining voltage  $V_{\rm S}$  of the pnpn device, the anode current decreases suddenly to the leakage current of that device. The holding current is measured through  $R_{\rm L}$  as the minimum value in the on state.

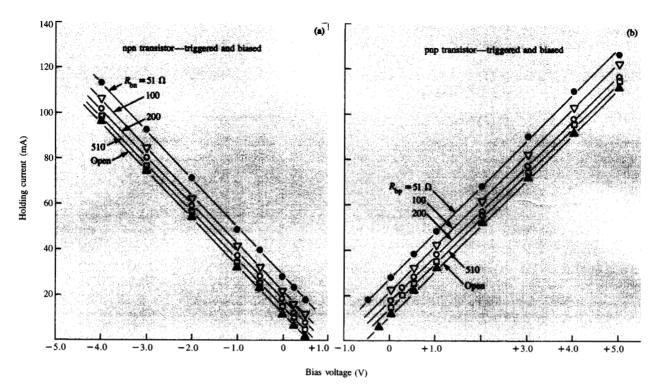

**Figure 3** shows measured values of  $I_{\rm H}$  as a function of the bias voltage for a discrete transistor pair. The common-base current gains of the pair are 0.974 for the npn transistor and 0.995 for the pnp transistor. Note that the holding current approaches zero at forward bias conditions when  $R_{\rm bp}$  or  $R_{\rm bn}$  is open.

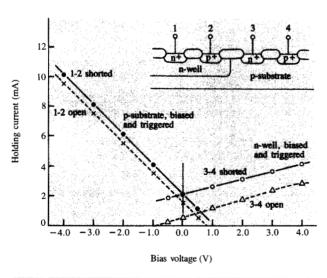

**Figure 4** shows measured values of  $I_{\rm H}$  vs. bias voltage for the n-well CMOS devices [7]; current gains were 0.5 for the npn structures and 0.83 for the pnp structures. Again, there is a significant linear increase of the holding current with reverse bias. Estimated intrinsic base resistances obtained from Fig. 4 are 750 ohms for the npn portion and 3.96 kilohms for the pnp portion.

In both cases, the holding current at the forward bias conditions approaches zero or very small values.

## 3. Discussion and conclusions

Equation (1), given previously [1, 2] in terms of  $\beta$ , has been applied to the triggering of latch-up. Equation (1) also shows that the higher forward bias  $V_{\rm BE}$  gives the higher  $I_{\rm H}$  values, and that  $I_{\rm H}=0$  at  $V_{\rm BE}=0$ .

The experimental results given above indicate that contrary to Eq. (1), the holding current in CMOS latch-up should be proportional to the reverse bias voltage instead of the forward bias voltage, and the holding current is not zero at zero bias; it reaches zero in the forward bias state.

In the triggering condition of Figure 5(a), an external noise source, such as a constant current source, drives the base-emitter junction in the forward direction. The pnpn device is easily triggered into the on state because the holding current at the forward-biased condition is very small, as shown in the experimental results. After the noise source is removed, the base-emitter junctions become reverse-biased by  $V_{\rm Rp}$  and  $V_{\rm Rn}$ . The reverse current through  $R_{\rm b}$  results from the minority-carrier-storage effect and is given by

$$I_{\rm R} = \frac{\phi_{\rm B} + V_{\rm R}}{R_{\rm b}} \,, \tag{2}$$

where  $\phi_{\rm B}$  is the built-in potential of the junction,  $V_{\rm R}$  is the bias voltage in the reverse direction, and  $R_{\rm b}$  is the total series resistance of the circuit. The reverse-direction minority-carrier-storage current is observed during the on state, as shown in **Figure 6**.

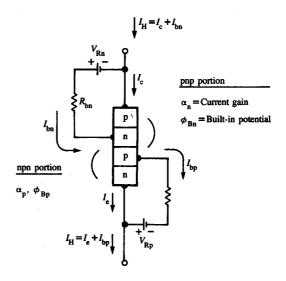

Previously, several authors have discussed the gate turn-off of pnpn devices (GTO or gate turn-off thyristor) [8–11]. The off condition for the pnpn device shown in **Figure 7** is

# Figure 1

Typical current-voltage latch-up characteristic

### Fourter-

Circuit configuration for measurement of holding current

$$I_{c} < \frac{\alpha_{p}I_{bp} + (1 - \alpha_{p})I_{bn}}{\alpha_{p} + \alpha_{p} - 1}$$

$$(3a)$$

or

$$I_{\rm e} < \frac{\alpha_{\rm n} I_{\rm bn} + (1 - \alpha_{\rm n}) I_{\rm bp}}{\alpha_{\rm n} + \alpha_{\rm p} - 1},\tag{3b}$$

where  $I_{\rm bn}$ ,  $I_{\rm bp}$ ,  $I_{\rm c}$ ,  $I_{\rm e}$ ,  $\alpha_{\rm n}$ , and  $\alpha_{\rm p}$  are defined as shown in Fig. 7.

# Figure 3

Holding current vs. bias voltage for a discrete npn (a) and pnp (b) transistor pair.

### Floure 4

Holding current vs. bias voltage for n-well CMOS devices.

The holding current  $I_{\rm H}$  is given by the summation of  $I_{\rm c}$  and  $I_{\rm bn}$ , or  $I_{\rm e}$  and  $I_{\rm bp}$ , so that

$$I_{\rm H} = \frac{\alpha_{\rm p} I_{\rm bp} + \alpha_{\rm n} I_{\rm bn}}{\alpha_{\rm n} + \alpha_{\rm n} - 1} \,. \tag{4}$$

This equation shows that the larger the magnitude of  $I_{\rm bp}$  or  $I_{\rm bn}$ , the larger the holding current. These are external base currents and their direction is opposite to that in the forward bias condition. Of course,  $I_{\rm H}$  is infinite when  $\alpha_{\rm n}+\alpha_{\rm p}$  is equal to unity, which is a condition completely free from latch-up. These equations are valid only in the sustained latch-up mode after triggering, when the pnpn device is *on*. Minority carriers are continuously being injected and recombining in this mode. In the absence of latch-up,  $I_{\rm bn}$  or  $I_{\rm bp}$  is zero before triggering.

By using Eq. (2), Eq. (4) can be written as

$$I_{\rm H} = \frac{1}{\alpha_{\rm n} + \alpha_{\rm p} - 1} \left[ \frac{\alpha_{\rm n}(\phi_{\rm Bn} + V_{\rm Rn})}{R_{\rm bn}} + \frac{\alpha_{\rm p}(\phi_{\rm Bp} + V_{\rm Rp})}{R_{\rm bp}} \right], \quad (5)$$

where  $\alpha_{\rm p}$ ,  $\phi_{\rm Bp}$ ,  $V_{\rm Rp}$ , and  $R_{\rm bp}$  are the current gain, built-in potential, reverse bias voltage, and base-emitter resistance, respectively, for the npn transistor, and  $\alpha_{\rm n}$ ,  $\phi_{\rm Bn}$ ,  $V_{\rm Rn}$ , and  $R_{\rm bn}$  are the equivalent quantities for the pnp transistor. Equation (1) is similar in form to Eq. (5) but incorrectly includes the forward base-emitter voltage  $V_{\rm BE}$  instead of the total reverse potential  $\phi_{\rm B}+V_{\rm R}$ , which includes the built-in potential.

Equation (5) gives a steady-state holding current, because minority carriers are being injected and recombining in the base regions continuously in the on state. Note that  $I_{\rm H}$  becomes larger when the pnp or the npn transistor is reverse-

# Figure

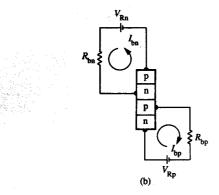

Equivalent circuit for triggering latch-up in (a), and for sustained latch-up after triggering in (b).

biased and becomes very small under forward bias. Equation (5) also predicts that the holding current reaches zero if (1)  $R_{\rm bn}$  and  $R_{\rm bp}$  are infinite, or (2)  $V_{\rm Rn} = -\phi_{\rm Bn}$  and  $V_{\rm Rp} = -\phi_{\rm Bp}$ , i.e., when the transistors are forward-biased.

The physical models representing the states before and after triggering are quite different. The equivalent circuits for the sustained latch-up mode after triggering and for triggering latch-up are shown in Fig. 5. Equation (5) gives the holding current for the sustained latch-up model after triggering, in which  $I_H$  is determined by reverse-direction currents in the base junctions of the transistors required to sustain carrier injections from the emitters, as shown in Figure 5(b).

In the triggering condition of Fig. 5(a), the direction of  $I_{\rm bp}$  or  $I_{\rm bn}$  is opposite to that in the sustaining condition, and thus they are not inversely proportional to  $R_{\rm bp}$  or  $R_{\rm bn}$ . External noise sources, such as constant current sources, drive both the base-emitter junctions (in the forward direction) and their associated resistors. Of course, small values of those resistors lead to a small voltage drop and hence to a suppression of triggering. For the same reason, shunting the base-emitter junction with a Schottky-barrier diode, or a tunnel or backward diode in parallel, is very effective in improving the immunity to latch-up. After

# Figure 6

Typical experimental waveforms of the anode current (upper curve, 10 mA/division) and of the base voltage (lower curve, 1 V/division). The reverse-direction minority-carrier-storage current is observed as  $I_{\text{R}}R_{\text{b}}$  during the on state. The holding current  $I_{\text{H}}$  is the minimum value of the anode current in the on state.

### Fellier

Simplified equivalent circuit of a pnpn device.

triggering caused by noise, the holding current increases to the value defined by Eq. (5). Clearly, reverse bias is very effective in increasing the holding current and, hence, in substantially increasing the immunity to latch-up.

# **Acknowledgments**

The author thanks Tak H. Ning and Lewis M. Terman for helpful discussions.

# References

- A. Ochoa, W. Dawes, and D. Estreich, "Latch-Up Control in CMOS Integrated Circuits," *IEEE Trans. Nucl. Sci.* NS-26, No. 6, 5065–5068 (1979).

- D. B. Estreich, "The Physics and Modeling of Latch-Up and CMOS Integrated Circuits," Ph.D. dissertation, Stanford University, Stanford, CA, October 1980.

- 3. R. D. Rung and H. Momose, "DC Holding and Dynamic Triggering Characteristics of Bulk CMOS Latch-Up," *IEEE Trans. Electron Devices* **ED-30**, No. 12, 1647–1655 (1983).

- 4. G. J. Hu, "A Better Understanding of CMOS Latch-Up," *IEEE Trans. Electron Devices* **ED-31**, No. 1, 62–67 (1984).

- R. C.-Y. Fang and J. L. Moll, "Latch-Up Model for the Parasitic p-n-p-n Path in Bulk CMOS," *IEEE Trans. Electron Devices* ED-31, No. 1, 113-120 (1984).

- R. R. Troutman and H. P. Zappe, "Layout and Bias Considerations for Preventing Transiently Triggered Latch-Up in CMOS," *IEEE Trans. Electron Devices* ED-31, No. 3, 315– 321 (1984).

- R. H. van Ligten and D. Navon, "Base Turn-Off of pnpn Switches," 1960 IRE WESCON Convention Record, Part 3, pp. 49-52.

- J. M. Goldey, I. M. Mackintosh, and I. M. Ross, "Turn-Off Gain in pnpn Triodes," Solid-State Electron. 3, 119–122 (1961).

- D. R. Muss and C. Goldberg, "Switching Mechanism in the npnp Silicon Controlled Rectifier," *IEEE Trans. Electron Devices* ED-10, 113–120 (1963).

- 10. E. Duane Wolley, "Gate Turn-Off in pnpn Devices," *IEEE Trans. Electron Devices* **ED-13**, No. 7, 590–597 (1966).

- R. H. Kingston, "Switching Time in Junction Diodes and Junction Transistors," Proc. IRE 42, No. 5, 829–834 (1954).

- 12. For example, see S. M. Sze, *Physics of Semiconductor Devices*, 2nd Ed., John Wiley & Sons, Inc., New York, 1981, p. 108.

- G. J. Hu, Y. Taur, R. H. Dennard, L. M. Terman, and C. Y. Ting, "A Self-Aligned 1-μm CMOS Technology for VLSI," *IEDM Tech. Digest*, pp. 739–741 (1983).

Received January 2, 1985; revised May 1, 1985

Haruhiro Matino IBM Japan, Ltd. Yamato Laboratory; 1623-14, Shimotsuruma, Yamato-shi, Kanagawa-ken 242, Japan. Dr. Matino received a B.S. degree in physics and a Ph.D. degree in electronics from the Tokyo Institute of Technology in 1961 and 1973. respectively. From 1961 to 1973, he participated in various research and development efforts at the Central Research Laboratory of the Tokyo Shibaura (Toshiba) Electric Co., Kawasaki, Japan, in a supervisory capacity from 1969 to 1973. In 1973, he joined the IBM Fujisawa Development Laboratory, where, as a manager, he worked on silicon devices, fiber optic communication devices, magnetic devices, printing heads, and displays. He was on leave from 1977 to 1978 at the IBM Thomas J. Watson Research Center, Yorktown Heights, New York, to work on new printing head technology, and again from 1982 to 1984 to investigate CMOS latch-up. Dr. Matino is a member of the Institute of Electronics and Communication Engineers of Japan and the Japan Society of Applied Physics.