# **Multi-Layer Ceramics Manufacturing**

Multi-layer ceramics (MLC) is an advanced packaging technology developed by IBM and used in the IBM 4300 and IBM 3081 processor models to significantly improve the module circuit density, reliability, and performance over those of previous packages. A key element in this package is the MLC substrate, which is capable of supporting more than 100 semiconductor chips in some design uses. The MLC manufacturing facility requires that sophisticated processing and inspection/test equipment operate within a hierarchically integrated system. This paper provides an overview of the manufacturing process that has been implemented to satisfy the high-volume manufacturing needs of this complex package. It also describes the data handling systems.

### Introduction

The multi-chip module (MCM) which utilizes the multi-layer ceramic (MLC) technology has been described elsewhere [1-4]. It was developed to satisfy the ever-increasing quality, reliability, and performance demands of large-scale computers. The manufacture of the modules in large volumes required development of a complex manufacturing system to satisfy not only the technical requirements of this product, but also the cycle time.

This paper briefly describes the product to be fabricated (the MLC), together with its manufacturing process flow, the tools that were designed to satisfy the product and process requirements, and how the manufacturing control system is applied to provide for tool sequence control, product and tool status information to key operating and management personnel, and the establishment and monitoring of interrelationships among the processing operations.

#### **Product**

The MLC manufacturing system was implemented to produce high volumes of multi-layer, multi-chip ceramic substrates. These substrates represent a significant advance in semiconductor packaging developed by IBM. MLC improves the module circuit density, reliability, and performance over those of previous packages, and complements the advances

made in large-scale integrated semiconductor technology as used in the IBM 4300 and IBM 3081 processor models. Overall dimensions, chip carrying, and input/output (I/O) capability vary significantly depending on the product type and the particular system application. Some designs of the MLC substrate are capable of supporting more than 100 semiconductor chips. The substrate contains signal planes for intra-module circuit connections and for routing wires to I/O for external connections. Other layers are provided for power distribution and for achieving the proper electrical performance characteristics.

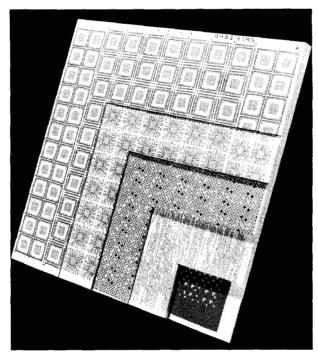

The substrate is composed of 17 to 32 layers of molybdenum-metallized alumina, with a total thickness of 4 to 5 mm, depending on the product type. An example of a multi-chip air-cooled substrate used in the IBM 4300 processor line is shown in Fig. 1. A cutaway view of a water-cooled thermal conduction module (TCM) used in the IBM 3081 processor line is shown in Fig. 2.

## MLC manufacturing line

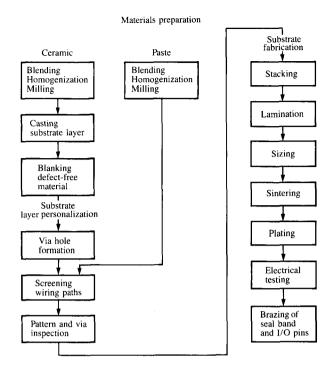

The basic process of manufacturing the MLC substrates is outlined in Fig. 3. Some highly automated computer-controlled tools are required to implement the operations shown. Data links between the tools and a central host computer are

• Copyright 1983 by International Business Machines Corporation. Copying in printed form for private use is permitted without payment of royalty provided that (1) each reproduction is done without alteration and (2) the *Journal* reference and IBM copyright notice are included on the first page. The title and abstract, but no other portions, of this paper may be copied or distributed royalty free without further permission by computer-based and other information-service systems. Permission to *republish* any other portion of this paper must be obtained from the Editor.

Figure 1 Multi-layer ceramic air-cooled modules (MCMs).

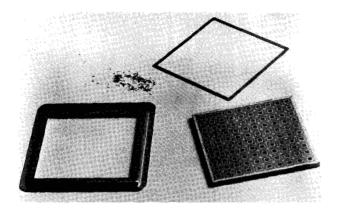

Figure 2 Cutaway view of multi-layer ceramic water-cooled module, the thermal conduction module (TCM), and a fully populated MLC substrate.

necessary to supply numerical control (N/C) data and to allow product tracking data, process data, and measurement results to be collected.

An intermediate-level computer between the tool and host levels was defined. This system was established to permit decoupling of the host system from individual manufacturing

Figure 3 MLC process flow.

tools for servicing each level separately. This system, called the area controller, serves a major processing area on the manufacturing line. It can also be used to implement personalized product-tracking functions and data transfers within an area. A backup system also exists at this level to prevent significant production loss in case an area controller fails, and redundant on-line disks are available for use in case a primary disk fails. A detailed discussion of the hierarchical distributed manufacturing control system which supports the MLC line is given by Mescia and Woods [5].

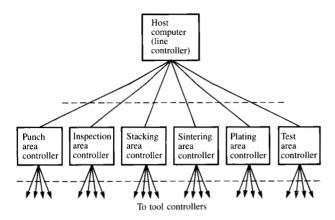

Area controllers have been implemented across the MLC line as shown in Fig. 4, and a typical area controller installation, a stacking area controller, is shown in Fig. 5. The area boundaries were chosen to contain all the tools in a particular processing area while ensuring sufficient unused capacity to allow for future expansion. The inspection-area and test-area controller functions are discussed in more detail later.

As Fig. 3 indicated, there are three phases in the MLC manufacturing process: materials preparation, substrate layer personalization (described later), and composite substrate fabrication. Before each process step is separately detailed, the characteristics of the unfired substrate layer ("pre-ceramic" sheet before metallization) that are required to make the MLC technology possible are reviewed.

Figure 4 Subdivision of MLC line into process areas.

Figure 5 Stacking area controller.

# Substrate layer characteristics

Since the substrate layer is the building block of the MLC substrate, rigid controls must be imposed on the chemical and physical properties of the raw materials and the process parameters. Very precise control of dimensions (thickness and width) is required. The material must have the proper density and shrinkage characteristics and must be free of surface and subsurface defects. It must exhibit the proper degree of deformation under load conditions and must have the ability to be handled in subsequent process steps without losing any of these properties.

The casting process had to be refined to minimize variations which could cause dimensional stability problems in subsequent processes, principally during via hole formation and screening of circuit patterns. Variations can cause sheet movement, which can result in the inability to maintain registration tolerances between layers. This can lead to shorts or opens in the signal paths. Thus, a number of product characteristics must be checked to ensure that the casting process is tightly controlled.

#### Materials preparation

The MLC manufacturing process begins with the preparation of materials for two basic elements of the package, the substrate sheets and the metallized paste. The substrate sheets consist of aluminum oxide and glass powder which are combined with an organic binder and a plasticizer; these hold the material together until the ceramic is fired, providing reasonable flexibility and handling characteristics to the unfired sheets during the processing operations.

The constituents are precisely weighed and blended and then milled in a ball mill to ensure proper particle size and uniform suspension. The resulting slurry is formed into a uniform-thickness "tape" by casting the mixture onto a continuous plastic carrier roll which acts as a transport vehicle during the drying process. Since very precise control of the drying environment is necessary to ensure proper removal of solvent, special monitoring systems have been designed both to control the process and to ensure conformance to safety specifications.

Stability of the substrate sheet, another critical characteristic, is a function of the induced stresses. Samples from each casting batch are tested to ensure proper stability. Layer-to-layer bond strength and shrinkage are measured for each casting lot. Variability of these properties must be tightly controlled. Shrinkage data are used to determine the proper lamination pressure for the lot.

The tape, cast in strip form, is stored on large spools after casting and drying. Square blanks are then stamped from the strips. These blanks are used throughout the various processing steps until they are finally laminated into a composite substrate. The tool which cuts the blanks contains an inspection system which scans the strips for defects (pinholes, contamination, localized variations in thickness, depressions, etc.) and selects only defect-free areas for blanking.

The second basic element of the package is the metallized paste used to form the circuit patterns. Its constituents are molybdenum and various organic compounds. These are blended, homogenized, and milled to produce a uniform mixture with consistent screening characteristics.

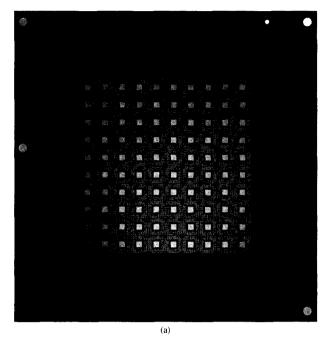

Figure 6 Substrate sheet after punching. (a) Large round locating holes are on the periphery. The interplane via holes are clustered within the chip sites. (b) Close-up view of interplane via holes.

## Personalization

The unique circuit patterns and via holes required to produce different substrate layer part numbers are imparted during personalization. This is accomplished in two major steps.

The first step, punching of interlevel via holes, begins with the punching of location holes in the four corners of the sheets. These holes are used to register precisely the sheets for punching and subsequent processing operations (screening, stacking, etc.). The interlevel via holes are then punched. A high-speed mechanical punch system capable of punching these via holes has been developed [2]. The second step involves the screening of surface patterns and subsequent filling of the via holes with metallized paste. Absolute location accuracy must be maintained using the location holes as a reference to ensure complete filling of the via holes at the circuit pattern screening operation and thereby ensuring signal path integrity from layer to layer after the stacking operation.

Tool control data for different sheet patterns are transmitted from a host computer system (which contains the design data), via the punch area controller, to the tool control computer. The punch tool controller, using approximately 400 interconnecting lines, controls all mechanical movements of the punching tool and verifies the successful completion of each move. It buffers the unique via hole-location data for a microprocessor which, in turn, controls a highspeed precision x-y table and synchronizes the individually activated punches to the table movement. As one sheet is being punched, the previously punched sheet is simultaneously inspected to ensure that the proper hole pattern has been punched. This is accomplished by using a light detector matrix which detects the presence or absence of the light transmitted through each hole location. The tool controller compares the data obtained from the light detector to those required for the particular hole location. Any defective sheets are placed in a separate tray. At the same time, the controller stores any error data for later analysis. Closeups of a section of a punched sheet are shown in Figs. 6(a) and (b).

The punch tool controller is a typical example of the use of computer-controlled tools within the MLC line. All sequential tool control logic is contained in the computer software. This technique results in ease of replication across similar tools, providing capabilities for rapid change and good error diagnostics.

Formation of the wiring patterns and filling of the interlayer via holes are very important operations in the fabrication of the MLC substrate. The paste is extruded through metal masks (Fig. 7), which are unique for each different layer pattern. These masks are accurately aligned in a frame which is referenced to a glass master standard. Figure 8 shows the extrusion nozzle of the high-speed screening system.

Nominal screened linewidths are on the order of 0.12 mm. The substrate sheet and circuit paste formulation parameters must be precisely controlled to ensure proper interaction at this screening operation (e.g., stability of sheet dimensions, complete filling of via holes, paste line dimension control,

Figure 7 Extrusion screen mask.

and paste-to-ceramic bonding). A solvent cleaning system is incorporated into the screening system to ensure that the masks are thoroughly cleaned of paste after screening. Examples of screened sheets are shown in Fig. 9.

In order to identify the unique personality of the substrate layers, two forms of identification are used: a bar code identification and an operator-readable identification. These are added to each sheet as part of the personalization process. By this means, subsequent processes can routinely "read" the identification before continuing a process. An operator can read the serialized part numbers where required.

# Inspection

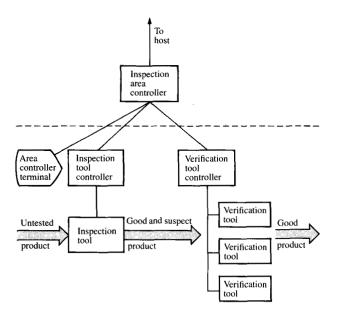

An automatic inspection system was developed to verify the integrity of the screened patterns on the substrate sheets. The system utilizes the principles of character recognition; it compares data from the scanned sheet to reference design data. Improper linewidths, misplaced pattern locations, opens, and shorts are detected and recorded by an IBM System/370 Model 138. It sometimes requires up to 4.5 megabytes of data to describe one sheet surface. This inspection operation is extremely important at this stage of the process, because a pattern defect detected at the substrate sheet level, prior to layer-to-layer lamination, prevents building a defective composite substrate. Sheet inspection is a key process application of the hierarchical control system supporting the MLC line. The flow of product and data within the inspection area is critical. Major functional elements of this area are shown in Fig. 10.

Figure 8 Screening system extrusion head.

Figure 9 Cross section of the TCM laminate showing screened patterns on substrate sheet.

Figure 10 Inspection area.

Figure 11 Oblique view of chip sites and a cross section of the MLC substrate. The dots in the middle of the picture are the I/Os to which the semiconductor chips are joined. The square pads with tails on the top surface are engineering change (EC) pads. By severing the tails, interconnections between the substrate and the chips may be interrupted. By bonding external wires to the EC pads, new interconnections may be established. Some interconnect circuit patterns run horizontally on adjacent ceramic layers, while some run clear through to the other side of the substrate, between 17 and 32 ceramic layers deep.

Product arrives at the inspection area in a job, which can contain 200-400 individually serialized sheets. The job is logged into the area controller from a terminal. This transaction causes the area controller to communicate with the host

computer, which updates its product tracking files and sends the area controller a complete description of the product within the job [6]. The job is then logged into a particular inspection tester, which signals the area controller to send the necessary job data to the tester's tool controller. The tool controller selects the correct pattern inspection data and directs the inspection process of each sheet in the job. When the job has completed inspection, it is logged off the tool, thereby causing the collected data (identified by job number and serial numbers) to be sent to the area controller.

The job is next moved to a verification tool, where suspected defective sheets are further analyzed. Logging the job in causes data gathered at the inspection tool to be transferred automatically from the area controller to the verification tool controller. An operator places a suspected defective sheet on the inspection table and enters the sheet serial number, and the verification tool controller then moves the inspection table to each of the suspected defects, pausing at each to allow the operator to inspect and accept or reject the sheet.

The defect is displayed for the operator on a video terminal as a *snapshot* made from the digital inspection data gathered during the initial inspection. With it and the aid of a microscope the operator makes a decision to accept or reject the sheet. The job is logged off the verification tool when all defective sheets in the job have been processed.

An additional transaction through the inspection area control terminal results in the job being logged out of the entire inspection area. The updated job information is then sent back to the host system. The completed job is finally forwarded to the stacking and laminating processes.

# Stacking and laminating

The stacking operation is the first step in the process of forming unique substrates by selectively compiling different combinations of personalized sheets. The stacker sorts the sheets in the proper sequence and precisely aligns stacks of 17 to 32 sheets, depending on the product type. The stacking system contains three key features which are necessary to ensure high substrate yields in this phase of the fabrication process. First, prior to alignment, a cleaner removes all foreign matter or ceramic particulates that may have resulted from product handling. Second, using the bar code identification number, an automatic reading system determines whether the correct sheet is at the stacker station. Third, a self-alignment checking system ensures that wiring patterns on each sheet are aligned to required tolerances with reference to the master.

A stacking carrier, which utilizes precision-located pins and registration holes in the sheets, is used for transporting and locating the stack during the lamination process. The function of the laminating process is to fuse the layers into a monolithic unit by the application of heat and pressure. Lamination parameters are determined from casting lot shrinkage data, as indicated previously. Up to 40 000 via holes must be maintained in precise layer-to-layer alignment during this process (see Fig. 11).

# Sizing

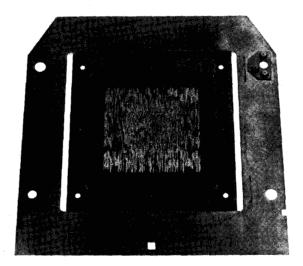

The laminates are now in a semi-hard state, approximately the consistency of hard rubber, and can be machined with relative ease. They are cut into individual substrates; see Fig. 12 for examples.

The overall dimensions of the substrates and the positions of the wiring patterns relative to the substrate edges (centrality) are important for subsequent processing steps, such as brazing, testing, and the assembly of chips and wires. These dimensions must therefore be tightly controlled.

#### **Sintering**

Organic materials are volatilized from the laminate during the sintering operation. The laminates are heated in a hydrogen atmosphere from 1250 to 1560°C, resulting in a hard damage-resistant substrate. The important product parameters in this operation are the overall substrate shrinkage and localized variations in shrinkage. The linear shrinkage must be held to approximately 17% and overall volume shrinkage to about 50%.

# **Plating**

The molybdenum patterns on the top and bottom surfaces of the substrate are next plated with nickel and gold to prepare the substrate for the attachment of integrated circuit chips, pins, wires, and caps used in module assembly. Process times in each plating step are controlled by a programmable automatic transport system. Key process parameters are either directly computer controlled or monitored to indicate out-of-specification conditions. Product is stopped in a fail-safe mode until the condition is corrected. Process data are stored by specific product serial numbers for correlation to subsequent manufacturing operations.

Filling and disposal of tank chemicals are accomplished through a specially designed bulk handling system. The plating line is controlled by IBM Series/1 computers.

# Testing and repair

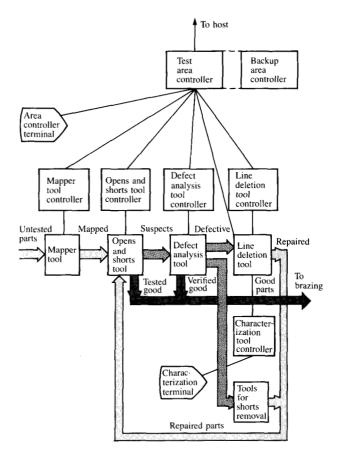

In the substrate electrical test area shown in Fig. 13, a series of operations are performed to test for electrical opens and shorts on all of the substrate internal wiring nets. This is difficult because of the small contact area available for probing and the total number of contacts to be made (some 14 000 in the most complex product). Due to the shrinkage

Figure 12 Nine-chip MCM laminate before and after sizing.

Figure 13 Schematic of the test area.

which occurs in the sintering operation preceding testing, the locations of the top surface pads are not predictable with sufficient accuracy for high-speed automatic probing; they must therefore be individually determined. This is accom-

Figure 14 Brazing components for a thermal conduction module, showing the frame, substrate, preform, and module pins.

plished by an automatic mapper tool which optically measures and stores specific numerical control data for each chip site on a substrate [4]. Specially designed buckling-beam probe assemblies are used to contact a large number of test points simultaneously, enabling a computer-driven tester to perform the opens/shorts measurements. The test sequences are precalculated from design data which accompany each substrate type on its release to manufacturing. These data are generated in such a way as to minimize the total number of tests performed while still guaranteeing a complete substrate test.

In addition to the mapper and the opens/shorts testers, other tools are necessary in the test area to diagnose and repair the defective substrates. For example, the defect analysis tester (DAT) is used to analyze defective nets individually after they are found on the opens/shorts tester. A precise point-to-point resistance measurement is made by using two accurately located individual probes. When required, open circuits can be repaired by the addition of discrete wires. Similarly, it is possible to eliminate some short circuits by deleting top-surface connecting patterns (see Fig. 11 caption) by the use of a laser beam system with a precision substrate-positioning system.

The complexity of product flow and data transfer within the test area highlights the capability of the manufacturing control system. The area controller serves as a focal point for gathering, analyzing, and distributing many types of data; see Fig. 13.

Jobs containing up to 400 identical parts are initially logged into a test area via an area controller terminal (IBM 4979 display). This causes the host computer to transfer the

previously generated test data patterns. The area controller then establishes a serial number history file for each substrate in the job. This file is updated as each part progresses through the test area.

The job is then passed on to the mapper tool. Successful logon results in the area controller transmitting part number, serial number, and nominal site location information for each chip site on the individual substrates for the entire job. The area controller, at this time, also checks that the job is at the correct test step within the test area, as it will do on all subsequent test steps. Missed or duplicated test steps are detected by the area controller and are prevented. An operator enters the serial number of each substrate as it is being mapped, and this, together with the precisely measured pad-location information, is added to the area controller serial number history file for use by subsequent tools.

The job then proceeds to the opens/shorts tester, where the part number identifies which tests to run. The serial number of the substrate identifies the exact locations of the pads to be contacted. This tester now adds raw error data into the history file; these data are analyzed and reduced by the area controller upon completion of the job. Data reduction is necessary because a single defect can result in other apparent defects due to the multi-point nature of the electrical nets being tested. Substrates suspected of being defective are transferred to the DAT, where the reduced error data are used to decide whether the defects are valid, and what the repair strategy for each defect should be. For defective parts containing internal signal wire shorts, the area controller calculates the coordinates of the top surface patterns to be deleted to remove the shorts.

After having undergone successful removal of shorts, the parts are returned once again to the opens/shorts tester to ensure that the faults were removed and that no new ones were introduced by the repair process. As before, the individual serial number history files of the substrates are updated by the area controller as each of the operations is performed. After all substrates have been successfully acted upon and tested "good," the job is logged out of the test area, and the serial number history files are stored.

# Brazing and finishing

The final operation in the MLC substrate fabrication process is the assembly of pins and a preform for attaching the module cover to the substrate. The Ni/Au-plated \*Kovar [7] pins are brazed to the substrate metallurgy with Au-Sn brazing material. Figure 14 shows the major components mounted in the brazing operation. Subsequently, semiconductor chips are mounted on the MLC substrate to form either an MCM [1] or a TCM [3] for use in an IBM computer system.

# Received June 23, 1981; revised September 8, 1982

# **Summary**

Implementation of a high-volume multi-layer ceramic manufacturing line has required the development of a wide range of sophisticated processing and testing tools, as well as a flexible computer-controlled manufacturing system. The resultant tools, processes, and interconnecting data network described in this paper form a reliable integrated manufacturing line, which is used to produce the parts for the IBM 4300 and IBM 3081 processor lines.

# **Acknowledgments**

The authors wish to thank D. R. Barbour for assistance in preparing this paper and T. A. Berghahn and G. E. Melvin for providing some of the information included.

#### References and notes

- A. J. Blodgett, Jr., "A Multilayer Ceramic Multichip Module," IEEE Trans. Components, Hybrids, Manuf. Technol. CHMT-3, 634-637 (1980).

- Alan Hall and Felix Zykoff, "Multi-Layer Ceramic Via Formation Technology," Proceedings of the 32nd Electronic Components Conference, Washington, DC, IEEE Cat. CH1781-4/82/0000-051, April 1982, pp. 518-526.

- 3. A. J. Blodgett and D. R. Barbour, "Thermal Conduction Module: A High-Performance Multilayer Ceramic Package," *IBM J. Res. Develop.* **26**, 30-36 (1982).

- M. A. Sanborn, "Precise NC Data Generation for the TCM," IBM J. Res. Develop. 27, 20-26 (1983, this issue).

- N. C. Mescia and C. D. Woods, "Plant Automation in a Structured Distributed System Environment," IBM J. Res. Develop. 26, 497-505 (1982).

- 6. If necessary, any supervisory personnel can easily locate a job which has been logged into an area, by using any terminal connected to the host system. The status of a job can then be more precisely determined by further interrogation through the appropriate area controller terminal.

- 7. ®Kovar is a registered trademark of Westinghouse Electric, Pittsburgh, PA.

William G. Burger IBM General Technology Division, East Fishkill facility, Hopewell Junction, New York 12533. Mr. Burger is manufacturing engineering manager in multi-layer ceramics. He is responsible for providing engineering support to advanced semiconductor packaging manufacturing, including definition of manufacturing processes and design and development of process and test equipment. He joined IBM in 1969 in East Fishkill. His past managerial positions have been in mechanical/optical analysis in technology assurance, architecture, design and implementation of photolithographic process equipment, design and implementation of all process and measurement equipment on the semiconductor manufacturing line, and design and implementation of process measurement and test equipment. Mr. Burger received his B.S. in mechanical engineering from Manhattan College, New York, in 1961 and his M.S. in mechanical engineering from New York University in 1965.

IBM General Technology Division, East Charles W. Weigel Fishkill facility, Hopewell Junction, New York 12533. Mr. Weigel is an advisory engineer currently involved in the application of computerized control systems for the new wafer manufacturing lines. After receiving his B.S. from Lehigh University, Bethlehem, Pennsylvania, in 1964, he joined IBM at Endicott, New York, as a quality engineer assigned to SLT and MST card electrical test operations. He moved to East Fishkill in 1970 to accept a management position in corporate procurement quality engineering, responsible for vendor quality of integrated circuits. In 1972, Mr. Weigel accepted a technical assignment to assist in the architecture and design of a fully automated wafer manufacturing line. These efforts culminated in the implementation of the advanced QTAT (Quick-Turn-Around-Time) line in 1978. From 1979 to 1981, he worked as a systems engineer assisting in the implementation of the manufacturing support and tool control systems for the multi-layer ceramic