# A New Set of Printed-Circuit Technologies for the IBM 3081 Processor Unit

A new set of printed-circuit technologies have been developed which permit construction of printed-circuit panels with several kilometers of controlled-impedance interconnections. Communications between internal layers of signal planes are achieved through small plated vias (drilled with a laser), while plated through-holes are used for the logic service terminals for cable terminations and module terminals. The panels are the largest currently known in the industry,  $600 \times 700$  mm, and have the most layers, 20. This paper describes new LSI package designs which are achievable with the exceptional versatility that the new technologies provide. These technologies encompass vacuum lamination, electroless plating, photosensitive dielectric, laser drilling, automatic twisted-pair wire bonding, and other new approaches to printed circuits.

#### Introduction

The functional circuit capacity and physical size of printedcircuit boards for large systems continue to increase in response to performance demands. In earlier papers [1, 2] the author describes how the complexity of the circuit board responds to increasing integration on the chips and on the module level of package. The demand for interconnection on the printed-circuit board increases in proportion to the number of modules placed on the board and in proportion to the number of component pins and the pitch between modules. In the present case, the thermal conduction modules (TCMs), as discussed by A. J. Blodgett and D. R. Barbour [3] and by A. J. Blodgett [4, 5], which are plugged into the board we are describing, contain an unprecedented large number of pins, 1800, and are very large in size, 90  $\times$ 90 mm. The interconnections on the printed-circuit board must service up to nine of these modules, a set of terminating resistors, and the input-output terminals for cabling connections between boards.

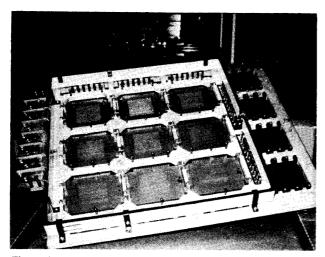

Earlier packaging systems have been largely [2] cardon-board (COB) with the printed-circuit cards containing single and multichip modules. The package system here is a "planar" one containing multichip modules directly on the board, and is referred to as the "TCM board" or the "3081 printed-circuit board," Fig. 1. A kilometer or more of printed wiring interconnections is required, and the board houses slightly under 1000 chips, each chip containing an average of about 500 circuits in the nine large pluggable thermal conduction modules. With this capability, each of the two central processors of the IBM 3081 Processor Unit is built on one board. In total, some 20 000 pluggable connections are made for signal and power contacts to modules and cables. All signal interconnections are interchangeable between internal printed-circuit wiring and twisted-pair wires, which can be automatically bonded to the surface of the printed-circuit board.

The large size,  $90 \times 90$  mm, of the modules and the requirement for nine of them, including a cache memory, to be placed on a printed-circuit board minimizes printed-circuit board-to-board crossings. These requirements resulted in a board size of  $600 \times 700$  mm ( $24 \times 28$  in.).

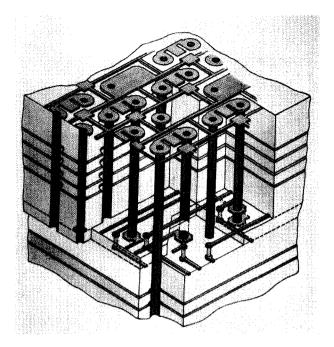

A power supply requirement of 600 A with minimal voltage drop (15 mV) for circuit requirements was satisfied by layering in 12 copper power-reference planes. The printed-circuit signal interconnections were completed with three pairs of printed-circuit planes, placed internally, and two surface planes. The 20 total layers of printed circuits, a fraction of which are shown in Fig. 2, are contained within a thickness of 4.6 mm (175 mils).

Some of the new technologies, the high-aspect-ratio plated through-holes [6] and the plated laser vias [7], have been

Copyright 1982 by International Business Machines Corporation. Copying is permitted without payment of royalty provided that (1) each reproduction is done without alteration and (2) the *Journal* reference and IBM copyright notice are included on the first page. The title and abstract may be used without further permission in computer-based and other information-service systems. Permission to *republish* other excerpts should be obtained from the Editor.

Figure 1 Assembled 3081 printed-circuit board containing nine TCM sites. The tabs on the left side are the power bus contacts. The voltage terminals enter the board around the periphery. Nine plastic connector housings are in place between the ribs of the stiffener. The input-output connector housing can be seen on the right side of the board.

described previously. The early application of many of the new technologies to the 4300 series of computers was discussed by Werbizky et al. [8, 9].

In this paper we begin by discussing the approach to holding dimensional tolerances in the large board. Then we progress to a discussion of the processing to make the power cores, the signal layers, and the 20-layer composite. Assembly is discussed briefly, along with the connector technology, twisted-pair wiring, and testing. In this paper, we focus on the numerous developments and challenges faced in the release of this new technology.

# Basic approach to fabrication of the 20-layer composite

To build such a large printed-circuit board ( $600 \times 700$  mm), it was first necessary to develop a strategy to control the dimensional tolerances over the full area and over all layers of laminate material. It is well known that the laminate materials stretch and shrink during processing. The requirement here is to laminate the 20 layers together in proper reference to each other and then to drill through the laminate on the basic grid of 1.25 mm (50 mils), making connections where desired while guaranteeing adequate insulation between circuits. In order to ensure this, a substantial data base is required for every production board. This data base includes

1. The dimensional changes which accumulate in each circuitized layer, from the process point at which the artwork is applied through the sequence of etching,

- plating lamination, and drilling (the dimensional changes are measured at a variety of points in individual layers by x-ray technique).

- 2. The effects of humidity and temperature over extended periods of time.

- The drilling tolerances, which include the accuracy of entry and the uncontrolled wander (bending) as the drill penetrates the laminate.

The data from 1) and 3) are analyzed by computer techniques to guarantee dimensions.

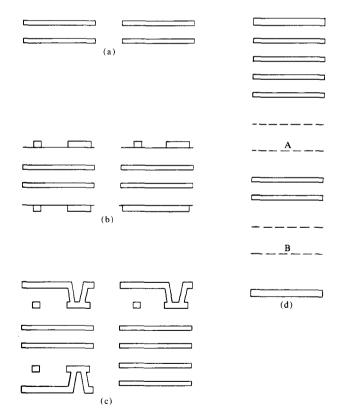

The first two effects noted can be made consistent and can be controlled to a large degree by using a sturdy laminate base for processing the circuitry. In contrast to building each very thin layer separately and then laminating 20 layers together, a strong copper power core, two layers of copper insulated by two layers of epoxy-glass, is built sequentially into a power laminate with four layers of epoxy-glass on each side prior to adding printed-circuit planes. A laminate this thick, 0.75 mm, fully cured by lamination, is a firm base for handling in manufacturing operations prior to and during the processing of the first circuit layers on each side [see Fig. 3(b)].

A second insulating pair of layers and a second copper circuit layer are added sequentially on both sides to form a subassembly. Two varieties of subassembly are made: one type includes two pairs of signal-interconnection planes, while the other includes one pair of signal-interconnection planes on one side and a pair of power planes on the other side [Fig. 3(c)]. Finally, a composite is built from the two types of subassemblies laminated together with appropriate spacing of insulation layers and power planes [Fig. 3(d)]. The composite is drilled and plated to complete the interconnections to the internal layers. The steps in the construction are illustrated by Figs. 3(a-d).

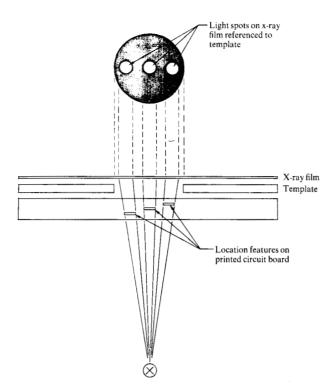

Each layer of circuitry contains a set of copper reference dots spread over the  $600 \times 700$ -mm area. These are x-rayed (Fig. 4) through a template referenced to the boards to determine the precise location of each element of the board. Thus, after collecting data on a large number of composites it is possible to derive consistent projections of dimensional change in each layer.

Accordingly, it is possible to make appropriate adjustments in the location of the elements of the artwork and in the processing treatments, including dimensional stabilization of the board at each stage, by controlling temperature and humidity prior to application of artwork. Indeed, sublaminates can be rejected for lack of proper dimensional tolerance as detected by x-raying before they cause the loss of an expensive composite. More importantly, with the added knowledge of the drilling tolerance, insulation dimen-

sions can be guaranteed, or the composite can be rejected prior to assembly.

The strategy to control the dimensional tolerances of the printed-circuit board includes a referencing technique consisting of a highly accurate measuring system and a precision artwork generator. The referencing system depends on punching precise slots, four of them on the median orthogonal axis of the power core. These slots are maintained as the multilayer subassemblies are built. The slot system provides freedom for expansion and contraction of the material as it absorbs and desorbs moisture, or as stresses are relaxed in glass-epoxy by heating and curing. Each tool (for example, a drill) contains four referencing posts onto which the slots can be snugly fitted.

Measurements are made on a modified jig bore machine tool fitted with an optical head and a recording mechanism. With this system it is possible to measure artwork, to measure drill-hole locations, and to generally follow dimensional changes throughout processing to an accuracy of approximately 0.0025 mm (0.1 mil). Changes due to moisture absorption may be as much as 0.1 mm (several mils). Thus, the material is intentionally dried prior to building the laminations where sublaminates must register to each other.

As a consequence of this total dimensional control strategy, internal printed-circuit interconnections are guaranteed to statistically meet the nominal design for insulation of 0.275 mm (11 mils), and will, in the worst case, never be closer than 0.05 mm at any site.

#### **Power core construction**

There are approximately 40 000 etched holes per power plane and twelve power planes per board. Thus, there are about 480 000 sites in the printed-circuit board where a drilled hole penetrates within the nominal distance of 0.275 mm (11 mils) of the etched pattern in the power planes. On one hand, it is desirable to statistically guarantee an insulation thickness, as discussed previously in the control of dimensional stability; on the other, it is also desirable to guarantee the insulation.

Guaranteeing the insulation is accomplished with a high-speed TV-like scanning system which automatically locates and scans the perimeter of each etched hole in a power core. The power core insulation is dyed to enhance the contrast between copper and epoxy-glass insulation. The system is computer-controlled to single out contrast sites like residual copper which do not meet predetermined reflection criteria. These sites are later checked by people directed to the site automatically on a separate x-y table in order to repair the site or reject the power core. A plane-to-plane test to 1200 V on the power core also guarantees the insulation quality between them.

Figure 2 Isometric view of a printed-circuit board cross section showing a portion of the thickness, internal signal interconnection, plated through-holes and details of surface interconnection pads for engineering change by wire bonding.

Figure 3 Sequence of construction of a TCM printed-circuit board: (a) power cores, (b) subassembly with one layer of circuit interconnecting both sides, (c) subassemblies with two layers of circuit interconnecting both sides, (d) composite two subassemblies, A and B, with three power cores added and two surface planes.

Figure 4 Configuration for determining by x-ray, locations of individual elements on various layers of the printed-circuit board in reference to a template.

Figure 5 Cross section of an electroless plated interconnection line compared to an etched line.

# Subassembly laminate processing

After the circuit patterns are formed, the subassemblies at the first and second circuit levels are vacuum-laminated to eliminate trapped air which could form internal voids. Conditions of lamination pressure, temperature, and dwell have been optimized, along with the flowability of the partially cured epoxy-impregnated glass cloth, to minimize defects. This has resulted in two orders of magnitude decrease in void-defect density compared with non-vacuum-laminated construction.

#### Interconnection processing

Interconnection lines nearly rectangular in cross section can be made (see Fig. 5) by electroless plating into a pattern in photoresist. However, a viable method of bonding electroless copper to the basic laminate is necessary. One satisfactory method is to use very thin copper with its bonding layer on the base laminate and then to build the resist pattern on the thin copper base. After the electroless copper is deposited into the resist pattern, the resist is stripped and the thin copper is etched away. With this approach, the bonding is identical to that used for normal etched-copper circuitry.

Rounding of the thick copper lines caused by etching away of the thin copper base can be prevented by coating lines with a thin film of tin, electrolessly deposited prior to removal of the photoresist pattern. The tin may be stripped prior to lamination of subsequent layers of insulation.

Using the approach described, and with preparation of the copper for resist adhesion, control is adequate to meet an  $80 \pm 10~\Omega$  characteristic impedance as well as a stringent requirement on tolerance for line resistance. These two factors call for the interconnection cross section to be a nominal 0.0495 mm (1.95 mils) thick by 0.081 mm (3.2 mils) wide.

The next step in the formation of interconnection is to laminate on another layer of epoxy-glass insulation and copper, the beginning of a second layer of a pair of signal planes.

The interconnection between the two signal planes is accomplished by plating the walls of a tiny hole, 0.1375 mm (5.5 mils) in diameter, formed with 30-W, millisecond CO<sub>2</sub> laser pulses. The laser focusing heads are set up on a stepping table much like those for mechanical drilling, with four subassemblies being drilled at a time. The laser pulses enter the subassembly through small windows pre-etched in the thin copper. The laser beam sublimates the insulation while reflecting off the pad formed by the first layer of interconnection. The holes are cleaned with a high-velocity jet containing silica particles.

Subsequently, a second photoresist pattern is applied, and electroless plating completes the via contact between the two layers [Fig. 6; see also Fig. 3(c)] while also plating the second interconnection layer (Fig. 7). Both sides of the

Figure 6 Cross section of a via electroless plated to interconnect two signal printed-circuit layers.

laminate are plated at once on one type of subassembly, thus completing two interconnected pairs of planes.

On a second type of subassembly, a pair of signal planes is completed on one side only while the other side contains a pair of power planes. The perimeter of the interconnection is automatically optically scanned to detect any residual copper within 0.050 mm (2 mils) of the lines. Continuity is also checked by scanning, but the resolution is limited. Thus, all interconnections are electrically tested for continuity and for shorts after the subassembly is completed.

## **Construction of composites**

The two types of subassemblies just described are laminated into a composite, along with three pairs of power planes and a set of surface planes. The total cross section contains 20 planes. The set of surface planes are made of thin copper in readiness for circuit formation as described in the construction of subassemblies.

The composite is drilled in two stages; in the first stage, a short bit is used to set the direction of the hole, while in the second stage, a longer (flexible) drill bit completes the hole. The exit dimensions are held within 0.075 mm (3 mils).

The holes are cleaned with a high-velocity jet of abrasive material and then cleaned with chemicals. The first chemical swells the epoxy while a second bath attacks the epoxy and etches the copper about 0.0125 mm. A second jet of abrasive removes the remnants of the epoxy material.

Plating of the holes, which have an aspect ratio of 11:1, is accomplished in an electroless plating bath. The conditions

Figure 7 Subassembly printed-circuit detail in the neighborhood of a TCM site. Note the extremely high density of interconnection and remember that there are six such layers and nine of these sites on a board. The small dots are pads which contain a plated through-hole structure 0.125 mm (5 mils) in diameter joining two signal layers.

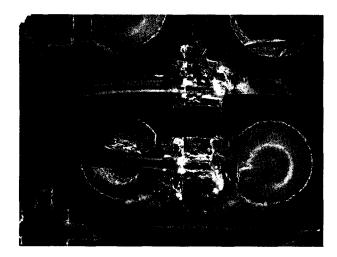

Figure 8 Plated through-hole in a TCM board. Note the uniform thickness of copper throughout. This hole taken at random shows how well centered the drill location is in reference to the etched holes in the power cores. The arrow points to two signal interconnection layers.

Figure 9 Twisted-pair wire bonded to ground pad and signal pad on the surface of the board.

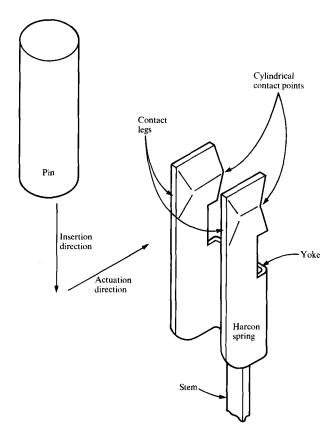

Figure 10 Isometric detail of connector spring and pin.

for plating begin with a compromise which guarantees nucleation. Subsequently, plating is accomplished under high agitation achieved by mechanical means as well as by air sparging to guarantee uniformity over the panels as well as in the holes (Fig. 8).

The ductility of the copper is monitored on special test vehicles. Another important control monitors the impurity level of the copper. Automatic chemical control and feed of the bath aids in achieving a high degree of control in plating rate and purity. As a result, the copper structure and strength are consistently good.

Finally, to detect infrequent isolated defects, all of the holes are scanned by x-ray transmission and recorded on photographic paper. This x-ray screening is applied again after soldering. In this situation, small voids or defects in the plating prevent the solder from wetting the hole wall. Thus, the x-ray screen is used to make a decision on rejection of a net containing a plated through-hole. Subsequently, this net may be deleted and hardwired onto the surface with twisted-pair wire.

In addition to opens-and-shorts testing of all nets at the composite level, all nets are tested for insulation to several hundred volts. This is by and in conjunction with a leakage test in the megohm range. Any nets that do not meet the leakage criteria are deleted at this point.

#### **Assembly**

#### • Solder mask and protective coat

All internal printed-circuit interconnections can be replaced by twisted-pair wires on the surface. A configuration of bonding pads for signal and ground twisted-pair wire interconnection (Fig. 9) is patterned onto the top surface of the printed-circuit board while the through-holes are electroless plated. These patterns are coated with a photosensitive epoxy which is exposed, developed, and cured to provide walls and dams to control the solder height. This material is a negative resist. Cross linking is triggered by exposure to near-ultraviolet light and continues on heating at a low temperature of 50°C. The areas that are not exposed wash away in the developer. Accuracy of the pattern is important in determining the largest possible bonding pads for automatic bonding while still guaranteeing insulation spacing and preventing solder bridging between the pads. This is why a new photosensitive solder mask was developed for this use rather than extending the use of a screened-epoxy coating.

# Connector assembly

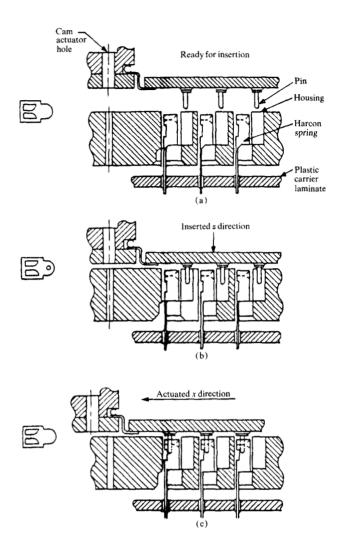

A new connector technology is required to accommodate insertion of 1800 contacts spread over the  $90 \times 90$ -mm (10-to 15-square-inch) TCM extent in an area array. The tolerances of the mating parts are controlled by using a bifurcated spring contacting a pin (Fig. 10). Since both the spring gap and the pin are independently set with dies, the contact force can be controlled within a desired set of limits. In turn, the contact stress is set by shaping the contact area. These stresses are set to exceed 1 GPa (125 000 psi). This

system was adapted to smaller pluggable modules [10] for an earlier product and has performed well in the field since 1975.

The springs are inserted in strips, 30 at a time. Sixty strips complete the assembly of each module site. A long compliant stem on each spring penetrates the 0.40-mm (16-mil)-diameter plated through-hole while the bifurcated spring is held in position above the hole during soldering. A plastic container, shaped like an "egg crate," fits over all springs and aligns them (Fig. 11). The flexible stem allows the springs to "float" to the alignment position. Thus, the locations are contained within the accuracy allowed by the plastic carrier.

A guide positions the module in relation to the springs prior to insertion. The pins from the module fit into a slot in the plastic spring carrier leading into the opening in the bifurcation of the spring. On insertion of the pins, the springs are sustained by the walls of the plastic carrier.

#### Soldering

The soldering technique was developed to fulfill a variety of requirements. One requirement was to prevent excessive strain on the plated through-holes by limiting the soldering temperature. A second requirement was to provide a dross-free soldering environment to permit 40 000 holes and 40 000 bonding pads to be reliably coated simultaneously. A third requirement was to provide a bondable surface over an extended period of time (years). Additional important desirable features were strength, expansion coefficient, wettability of metals, and uniformity in height of the solder pads. These features were realized by using a tin-bismuth alloy in a wave-soldering technique immersed in a bath of glycerine containing a mild chelating flux.

## Wire bonding

In the early phase of any program, extensive engineering changes or substantial rework of interconnections to improve yield may be desired. Accordingly, it is essential to have an automatable wiring technique comparable to that supplied by the single wire wrap used in System/370 printed-circuit boards. The stringent impedance specification in the new generation can be met by twisted-pair or coaxial wires, and since the twisted-pair wiring is by far the easiest to automate, while still performing well, this was the technology chosen.

The machines used to automatically wire with twisted pairs were developed over a 10-year period from a manual technique handling about 10 twisted-pair wires per hour to a prototype automatic head capable of 60 twisted-pair wires per hour. Extensions, which included automatic spreaders to penetrate dense wiring structures, length gauging, and other

Figure 11 Cross section of housing containing connector springs and printed-circuit composite. The insertion of module pins is illustrated by the sequence (a) alignment, (b) insertion of the pins into the "egg crate" in front of the spring, and (c) actuation of the pin into the spring.

features to minimize operator intervention, have increased the base rates well beyond 60 wires per hour.

#### In-process test

The sequence of assembly following soldering of connectors includes bonding of the stiffener, wire bonding, opens and shorts test, soldering of capacitors, soldering of the power bus, assembly of connector housing, and then final test. Since the nets are tested also at the assembly and composite level, by the time the printed-circuit board is completed most nets have been tested for opens and shorts at least four times.

The reasons for testing with high redundancy arise from the need to locate defects as near as possible to their creation in the process. Another possibility is that a repair may be missed by an operator. Still another risk is that a twisted-pair net may be loosened in handling. It may be possible to eliminate some of the testing, but before this is desirable a large data base is required to isolate the process steps responsible for the defects. Once the defects are analyzed, process improvements replace the need for some redundant testing. In fact, the combination of process enhancement and process controls (of which a few examples were discussed in the text), along with redundant in-process testing, ensures the high quality of the TCM printed-circuit board.

#### **Summary**

A new set of printed-circuit board technologies have been developed to allow production of a 600 × 700-mm, 20-layer TCM printed-circuit board containing more than a kilometer of printed wire. The new processes include artwork generation, processes to control dimensional changes, vacuum lamination, high-aspect-ratio mechanical drilling, laser drilling, electroless plating, photosensitive dielectric solder masking, twisted-pair wire bonding, and immersion soldering. A high degree of redundancy for in-process test, including high voltage tests, automated optical scanning, leakage testing to 300 megohms, and opens and shorts testing, ensures a high-quality product.

#### **Acknowledgments**

The author is appreciative of the many individual contributions from the design and process engineering groups involved in the development of the TCM printed-circuit board. During the development an outstanding relationship existed between myself and Bert Stevens, who was responsible for the design, and with Larry Walter and Karl Hermann, responsible for the early manufacturing. I have used diagrams contributed by the design group now reporting to L. K. Schultz and J. Asselta. A good deal of the early

conceptual work was shared with groups reporting to K. Varker, J. Kresge, S. Jensen, D. Napp, J. Bupp, and R. Carlson. Many of the individuals not noted here will be reporting on individual accomplishments. N. Fruci and P. Toole reviewed the manuscript.

#### References

- D. P. Seraphim, "Chip-Module Package Interface," IEEE Trans. Components, Hybrids, Manuf. Technol. CHMT-1, 305-309 (1978).

- D. P. Seraphim and I. Feinberg, "Electronic Packaging Evolution in IBM," IBM J. Res. Develop. 25, 617-629 (1981).

- A. J. Blodgett and D. R. Barbour, "Thermal Conduction Module: A High-Performance Multilayer Ceramic Package," IBM J. Res. Develop. 26, 30-36 (1982, this issue).

- 4. A. J. Blodgett, "A Multilayer Ceramic Multi-Chip Module," Proceedings of the Eletronic Components Conference, San Francisco, CA, 1980, pp. 283-285.

- A. J. Blodgett, "A Multilayer Ceramic Multi-Chip Module," IEEE Trans. Components, Hybrids, Manuf. Technol. CHMT-3, 634-637 (1980).

- W. A. Alpaugh and J. M. McCreary, "Copper Plating Advanced Multilayer Boards," *Insulation/Circ.* 24, No. 3, 27 (1978).

- 7. W. R. Wrenner, "Layer Drilling P.C. Substrates," Circuits Manuf. 17, No. 5 (May 1977).

- G. G. Werbizky, P. E. Winkler, and F. W. Haining, "Making 100 000 Circuits Fit Where at Most 6000 Fit Before," Electronics 32, No. 16, 109-114 (1979).

- G. G. Werbizky, P. E. Winkler, and F. W. Haining, "Packaging Technology for the IBM 4300 Processors," presented at the Twentieth IEEE Computer Conference, San Francisco, CA, Feb. 25-28, 1980.

- J. C. Mollen, "IBM Pluggable Modules," Proceedings of the Electronic Components Conference, San Francisco, CA, 1980, pp. 349-354.

Received September 16, 1980; revised August 13, 1981

The author is located at the IBM General Technology Division laboratory, P. O. Box 6, Endicott, New York 13760.