J. H. Greiner

C. J. Kircher

S. P. Klepner

S. K. Lahiri

A. J. Warnecke

S. Basavaiah

E. T. Yen

John M. Baker

P. R. Brosious

H.-C. W. Huang

M. Murakami

I. Ames

# **Fabrication Process for Josephson Integrated Circuits**

A process for fabricating experimental Josephson integrated circuits is described that is based primarily on the use of vacuum-deposited Pb-alloy and SiO films patterned by photoresist stencil lift-off. The process has evolved from one previously reported, with changes having occurred in junction electrodes, tunnel barrier formation, layer patterning, device geometry, and minimum linewidths. Films of Pb-In(12 wt%)-Au(4 wt%) alloy (200-800 nm thick) are used for forming junction base electrodes, interferometer controls, and interconnection lines. Tunnel barriers are formed on the base electrode films by thermal oxidation and subsequent sputter-etching in an rf-oxygen plasma. Junction counter electrodes are formed from 400-nm-thick Pb-Bi(29 wt%) alloy films. Ground planes are formed from 300-nm-thick Nb films patterned by subtractive etching and insulated in part by a  $Nb_2O_5$  layer formed by liquid anodization. Films of the intermetallic compound  $AuIn_2$  (30-43 nm thick) are used for forming terminating, load, and damping resistors. The SiO films are used for interlayer insulation, for defining junction areas in interferometers, and as protective coatings. Layer patterning is achieved mainly by means of photoresist lift-off stencils. By utilizing this process, experimental logic and memory circuits containing  $\approx$ 100 interferometers with lines as small as 2.5  $\mu$ m in width have been successfully fabricated.

## Introduction

Josephson tunneling devices exhibit fast switching and low power dissipation [1], characteristics that make them attractive for future computer applications [2]. Work is in progress to explore the potential of circuits containing such devices. A process was developed that allowed several initial types of logic and memory circuits to be successfully fabricated [3]. Since that time, improvements have been made in the process, and other investigators have successfully made devices and circuits using adaptations of the process [4].

This paper describes the fabrication process used to prepare recent Josephson devices and circuits. The multi-layer, integrated circuits were formed on oxidized Si substrates primarily through use of vacuum-deposited thin films. Superconducting layers were generally Pb alloys and insulation layers, SiO. These layers were patterned using photoresist stencil lift-off methods and optical lithography with minimum linewidths of 2.5  $\mu$ m. An overview of the fabrication process is presented, and preparation and properties of the various layers are de-

Copyright 1980 by International Business Machines Corporation. Copying is permitted without payment of royalty provided that (1) each reproduction is done without alteration and (2) the *Journal* reference and IBM copyright notice are included on the first page. The title and abstract may be used without further permission in computer-based and other information-service systems. Permission to *republish* other excerpts should be obtained from the Editor.

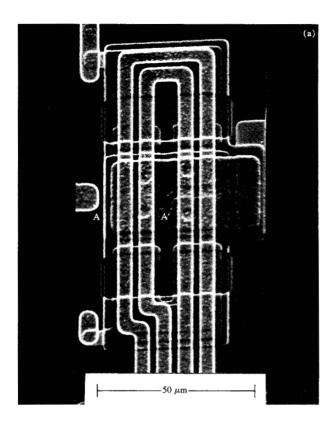

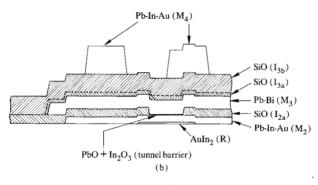

Figure 1 (a) Scanning electron micrograph (SEM) of a Josephson logic interferometer containing 2.5- $\mu$ m-diameter junctions. (b) Associated schematic cross section through A—A'. The cross section illustrates most of the layers present.

scribed. In addition, some relevant characteristics of circuit elements are discussed and examples are given of experimental circuits that have been fabricated. Overviews of associated materials and process studies [5] and circuit studies [1] are contained in accompanying papers in this issue.

# Circuit layers

A scanning electron micrograph (SEM) of a typical device, a logic interferometer, and its schematic cross section are shown in Fig. 1. Layers of Pb-In-Au (M<sub>2</sub>) and Pb-

Bi (M<sub>a</sub>) are used to form the Josephson junction electrodes. The tunnel barrier is an oxide grown on M<sub>2</sub>. The junction areas are defined by openings in an SiO (I22) layer. Damping resistors are formed from an AuIn<sub>a</sub> (R) layer that lies beneath the junctions. The control lines are formed from a Pb-In-Au (M<sub>4</sub>) layer and are insulated from the underlying junction electrodes by SiO  $(I_{3a} + I_{3b})$ . The layers typically serve several functions in the circuits. For example, device interconnections are accomplished with the M, and M<sub>4</sub> layers, using the I<sub>3h</sub> layer where insulated crossovers are required; load and terminating resistors are formed from the R layer; etc. For clarity, several layers have been omitted from the cross section: the interferometer lies above a superconducting Nb ground plane (M<sub>1</sub>) that is covered by Nb<sub>2</sub>O<sub>5</sub> ( $I_{1a}$ ) and SiO ( $I_{1b}$ ) insulation layers; an SiO (I<sub>A</sub>) layer serves as an overlying protective layer. External connections are made to solder terminals [6] or contact pads through openings in the I<sub>4</sub> layer. Where ground-plane contacts are needed, they are established with a Pb-In-Au (C) layer. A typical integrated circuit thus utilizes ≈14 patterned thin-film layers. The various thin-film layers that have been used recently to fabricate logic and memory circuits are listed in Table 1, together with their thicknesses and functions. Several weeks are usually required to fabricate a typical circuit. Details of the fabrication steps are now presented.

## Metal layers

Lead-base materials were selected for forming junction electrodes because the transition temperatures and energy gaps of such materials are relatively insensitive to impurity levels and structure variations, and because, through their use, devices can be prepared with low junction capacitances [7] (the latter are important for highspeed circuits). Alloy additions to Pb were selected to improve its chemical and mechanical stability [8, 9]. Relevant electrical properties of the various metal layers are summarized in Table 2 for representative thicknesses. Included are  $\rho$ , the electrical resistivity at  $\approx 300$  K;  $\rho_0$ , the resistivity at 4.2 K (just above the superconducting transition temperature  $T_a$ );  $\lambda$ , the magnetic penetration depth at 4.2 K [10]; and  $\Delta$ , the superconducting energy gap at 4.2 K. The compositions are as listed in Table 1. Niobium was selected for the ground plane because such films are stable, can be formed with a high  $T_c$ , and can be readily insulated by liquid anodization [11].

The depositions of the  $M_2$ ,  $M_4$ , and R layers are preceded by an oxygen rf sputter-etch cleaning process in order to remove photoresist residues, improve adhesion, and form electrical contacts. These layers are deposited at pressures of  $\approx 5 \times 10^{-5}$  Pa onto substrates held at temperatures near 300 K through the use of water-cooled substrate holders and Ga backing.

Table 1 Layers for logic and memory circuits.

| Layer                                   | Material  Nb                       | Thickness (nm) | Function                                                       |  |  |

|-----------------------------------------|------------------------------------|----------------|----------------------------------------------------------------|--|--|

| М.                                      |                                    |                | Ground plane                                                   |  |  |

| I <sub>1a</sub>                         | $\mathrm{Nb_2O_5}$                 | 25-35          | Ground-plane insulation                                        |  |  |

| T                                       | SiO °                              | 145-275        | Ground-plane insulation                                        |  |  |

| $\overset{\mathbf{I}_{1\mathbf{b}}}{R}$ | AuIn,                              | 30-43          | Terminating, loading, and damping resistors                    |  |  |

| I.                                      | SiO <sup>2</sup>                   | 200            | Logic interferometer isolation and resistor insulation         |  |  |

| $\overset{1_{1c}}{C}$                   | Pb-In-Au*                          | 300            | Ground-plane contacts and logic interferometer inductance      |  |  |

| $\mathbf{M}_2$                          | Pb-In-Au*                          | 200            | Base electrodes, interconnections, and resistor contacts       |  |  |

| $\mathbf{I_{2a}}^2$                     | SiO                                | 275            | Junction definition and insulation                             |  |  |

| $I_{2b}^{2a}$                           | SiO                                | 275            | Memory interferometer inductance and insulation                |  |  |

| Ť                                       | PbO/In <sub>2</sub> O <sub>2</sub> | 6.5            | Tunneling barriers                                             |  |  |

| $\stackrel{\mathbf{I_{2c}}}{M_3}$       | Pb-Bi <sup>†</sup> <sup>°</sup>    | 400            | Counter electrodes                                             |  |  |

| I <sub>3a</sub>                         | SiO                                | 100            | Counter-electrode protection layer                             |  |  |

| I                                       | SiO                                | 500            | Controls and interconnection insulation                        |  |  |

| I <sub>3b</sub><br>M <sub>4</sub>       | Pb-In-Au*                          | 800            | Controls, interconnection, and contacts to R, C, and M, layers |  |  |

| I, T                                    | SiO                                | 2000           | Protective layer                                               |  |  |

<sup>\*12</sup> wt% In and 4 wt% Au.

Table 2 Metal and insulation layer properties.

| Metal<br>layers                | Thickness<br>(nm)    | $ ho \ (\mu \Omega	ext{-cm})$            | $(\mu\Omega	ext{-cm})$ | $T_{\rm c} \ ( m K)$ | λ<br>(nm) | $\Delta$ (meV) |

|--------------------------------|----------------------|------------------------------------------|------------------------|----------------------|-----------|----------------|

|                                | 235                  | 21                                       | 6.3                    | 8.8                  | 85        |                |

| Pb                             | 500                  | 21                                       | 0.014                  | 7.2                  | 49        |                |

| $M_2$                          | 180                  | 26                                       | 7.3                    | 6.8                  | 137       | 1.15           |

| $M_3^2$                        | 400                  | 53                                       | 27                     | 8.3                  | 202       | 1.7            |

| M <sup>°</sup>                 | 900                  | 24                                       | 6.5                    | 7.0                  | 156       |                |

| M <sub>4</sub><br>R            | 43                   | 12                                       | 4.0                    | 0.2                  | _         |                |

| Insulation<br>layers           | $\epsilon_{_{ m r}}$ | $\frac{E_{\mathrm{B}}}{(\mathrm{V/cm})}$ | ρ<br>(Ω-cm)            |                      |           |                |

| Nb <sub>2</sub> O <sub>5</sub> | 29                   | ≥10 <sup>6</sup>                         | $4 \times 10^6$        |                      |           |                |

| SiO "                          | 5.7                  | $\gtrsim 10^6$                           | 1011                   |                      |           |                |

The Nb ground-plane layer ( $M_1$ ) is deposited by rf sputtering in an Ar glow discharge. The substrate support is held at 400°C during deposition (the wafers reach  $\geq$ 500°C) to obtain fine-grained polycrystalline films with low intrinsic stresses. It was necessary to use a small negative substrate bias (75 V) during deposition to obtain films of sufficient purity to have good superconducting properties [12]. Typical values for Nb film properties are given in Table 2.

The base-electrode layer ( $M_2$ ) is formed by sequentially depositing films of Au (4.5 nm), Pb (160 nm), and In (35 nm) [9]. The three films readily interdiffuse (<1 h at 300 K), forming a two-phase alloy consisting of a Pb-In(13 at%) solid solution with  $\approx$ 30-nm-size particles of the intermetallic compound AuIn<sub>2</sub>. Auger spectroscopy

and sputter-etch profile analysis of the  $M_2$  layers show the first evidence of Au  $\approx 30$  nm below the  $M_2$  surface [13]. A two-step, thermally grown  $\rm In_2O_3$  layer ( $\approx 2.5$  nm) is formed on the layer at 2.7 Pa  $\rm O_2$  first at 24° and then at 75°C prior to its removal from the vacuum system [14]. This oxide provides chemical protection during subsequent photoprocessing and a more reproducible surface for subsequent tunnel barrier formation.

The Pb-Bi(29 wt%) counter-electrode layer  $(M_3)$  is deposited in situ after tunnel barrier formation by means of co-evaporation from an alloy source of the same composition. Films thus formed are a single phase  $(\varepsilon)$  of Pb-Bi having a higher  $T_c$  and a larger  $\lambda$  than pure Pb films [10, 15]. Through their use, improved junction cyclability and reduced subgap current levels have been obtained

<sup>†29</sup> wt% Bi.

[15]. However, the Pb-Bi films are susceptible to corrosion during photoprocessing and storage. Thus, a protective 100-nm layer of SiO is deposited onto them prior to stencil lift-off [16].

The control and interconnection layer ( $M_4$ ) has the same composition as the base-electrode layer. In addition to its use for forming device controls, it serves as the primary layer from which interconnection lines are formed. Its thickness is 800 nm to ensure coverage over the edges of underlying layers and line continuity for relatively long lengths of 2.5- $\mu$ m-wide lines [17]. The layer is formed by sequentially depositing films of Pb (250 nm), Au (18 nm), Pb (390 nm), and In (142 nm). Use of this deposition sequence has given good edge coverage without a significant reduction of the critical currents of lines formed from that layer [18].

The resistor layer (R) is formed by sequentially depositing films of Au and In. The films interdiffuse to form  $\operatorname{AuIn_2}$  layers 30 to 43 nm thick with sheet resistivities of 2 to  $1 \,\Omega/\Box$ , respectively. Deposition and annealing are carried out at a substrate temperature of 75°C to form stable layers. Interdiffusion is avoided at R-M<sub>2</sub> or R-M<sub>4</sub> interfaces because  $\operatorname{AuIn_2}$  is a phase of the M<sub>2</sub> and M<sub>4</sub> alloys [19]. The resistivity of  $\operatorname{AuIn_2}$  layers is believed to be determined primarily by grain-boundary scattering [20]. Thus, the control of factors influencing the thickness and grain size (e.g., substrate cleaning, substrate temperature, layer composition, and deposition rates) is important in order to obtain reproducible sheet resistivities.

The ground-plane contact layer (C) is used primarily for forming superconducting contacts to the Nb ground plane. It is 300 nm thick and has the same composition as the base-electrode layer; it is formed by using the same deposition sequence. Prior to deposition, an rf Ar plasma is used to sputter-clean the Nb in order to ensure formation of contacts with adequate current-carrying capability. This layer is also used in logic interferometers to increase loop inductance and to ensure base-electrode continuity across  $I_{\rm tc}$  edges [21] and ground-plane openings.

# • Insulating layers

The low voltage levels and the superconductivity of the signal lines used for Josephson integrated circuits allow the use of thin-film insulators with relatively low values of breakdown voltage ( $\geq 1$  V) and resistivity ( $\rho_0 \geq 10^6 \, \Omega$ -cm). Both the  $\mathrm{Nb_2O_5}$  and SiO layers allow substantial current flow at electric fields that are small compared to the breakdown field. Thus, they should be relatively unsusceptible to breakdown due to static charge buildup. Table 2 also gives, for  $\mathrm{Nb_2O_5}$  [10] and SiO [22] layers, their relative dielectric constants  $\epsilon_r$  at 4.2 K, the typical break-

down fields  $E_{\rm B}$  at 300 K, and their resistivities  $\rho$  at 300 K and at low biases, where conduction through the layers is ohmic. Both materials are amorphous (i.e. noncrystalline) when prepared as described here.

Insulation of the Nb ground plane is achieved by using a  $\mathrm{Nb_2O_5}$  layer ( $\mathrm{I_{1a}}$ ) formed by liquid anodization of the Nb film. The anodization is carried out at  $20^{\circ}\mathrm{C}$  in an electrolyte of ammonium pentaborate, ethylene glycol, and  $\mathrm{H_2O}$  [11]. The thickness of the  $\mathrm{Nb_2O_5}$  layer thus formed is determined by the anodization voltage used (2.2 nm/V). Although  $\mathrm{Nb_2O_5}$  has excellent insulating properties for Josephson circuit applications, only thin layers are used because the high dielectric constant of the material would cause reduction of the line characteristic impedance levels and an increase in propagation delays. Thus, for use in circuits, the  $\mathrm{Nb_2O_5}$  is usually covered with a thicker layer of SiO, the composite serving as the ground-plane insulation. Use of such a composite insulator results in fewer ground-plane insulation shorts.

The SiO layers are deposited in a vacuum of  $\approx 5 \times 10^{-5}$  Pa by using a heated source (either rf or resistance). Deposition is carried out at a substrate temperature of  $\approx 300$  K, with Ga backing and a deposition rate of  $\approx 1$  nm/s. The resulting SiO films are reported to have low stress levels ( $\approx 2 \times 10^7$  Pa) upon deposition [23], thus minimizing the stress to which the Pb-alloy films are subjected. Analysis of evaporated SiO films by nuclear backscattering shows that they have an Si:O atom ratio of approximately  $1 \pm 2\%$  [24]. Electron spectroscopy for chemical analysis (ESCA) indicates that such SiO films are a single phase (*i.e.*, not a two-phase mixture of Si and SiO<sub>2</sub>) and that they are relatively stable up to temperatures of  $\approx 400^{\circ}$ C [25].

## • Tunnel barrier

The formation of the tunnel barrier is the key step in Josephson device fabrication. The Josephson current and the single-electron tunneling current depend exponentially on the product of the tunneling barrier thickness and the square root of the barrier height times the effective mass of tunneling electrons. Basavaiah et al. have confirmed such a dependence for Pb/PbO/Pb junctions [26]. Thus, precise control of the tunnel barrier oxide thickness and composition are required in order to achieve reproducible values of the tunneling current. For Pb-alloy junctions, a method of achieving this reproducibly has been developed; oxide tunnel barriers are formed on the base-electrode layer by sputter-etching its surface in a low-pressure rf oxygen discharge [27] (rf oxidation). See also the accompanying paper by R. F. Broom et al. [4(e)]. In the discharge, two competing processes occur that can be used to control the oxide thickness: oxide

198

growth and sputter-etching. As for thermal oxidation, the oxide growth rate decreases rapidly with oxide thickness. favoring formation of uniform oxide layers. In the competing process (sputter-etching) the oxide removal rate is independent of thickness. In the ideal case, these processes can be balanced so that the oxide thickness becomes independent of rf oxidation time and depends only upon the discharge conditions, e.g., oxygen pressure and rf voltage. In practice, such behavior has been achieved for the rf oxidation of Pb films [27] and approached for Pb-In-Au alloy films [28]. The properties of oxides formed on the latter alloy films by rf oxidation are also found to depend on alloy composition, oxide growth kinetics, and backscattering of material sputtered from the surrounding regions of the rf electrode and sample surfaces [4(e), 14]. Nevertheless, the current densities of junctions made with Pb-In-Au base electrodes can be controlled on a fine scale by adjusting the rf discharge parameters. In addition, good-quality Josephson junctions can be made that cover the current density range of interest for logic and memory devices in a manner compatible with the fabrication of integrated circuits.

Tunnel barriers are formed on the Pb-In-Au M, layers by using a combination of thermal and rf oxidation. The thermal oxidation to form an In<sub>2</sub>O<sub>3</sub> layer is carried out before the samples are removed from the M<sub>o</sub> deposition system at 2.7 Pa of O2 for 30 min each at 24° and 75°C [14]. The processing steps required to prepare the I<sub>20</sub> layer defining the area of most of the junctions and the Ma photoresist stencil are carried out next. The tunnel barrier oxide is completed by rf oxidizing regions of the M, surface exposed in the openings in these two layers. For rf oxidation, the substrates are mounted (Ga backing) onto a water-cooled rf electrode coated with Pb-Bi. Before rf oxidation, the vacuum system is exposed to an oxgyen discharge cleaning step with the samples shuttered. The first stage of the rf oxidation is carried out at 125 V (all rf voltages are peak-to-peak) and 10 Pa. This step has been found to remove residues from the preceding photoresist stencil formation step without significantly altering the previously formed In<sub>2</sub>O<sub>3</sub> layer. The second stage of rf oxidation is carried out at 360 V under an oxygen pressure appropriate to complete formation of the tunnel barrier oxide (discussed later). Without breaking vacuum, the Pb-Bi counter-electrode layer is deposited at ≈5 × 10<sup>-5</sup> Pa. The resulting tunnel barrier oxide is composed of In<sub>2</sub>O<sub>3</sub> and several forms of Pb oxide [14].

## Layer patterning

The patterning processes reported here have been practiced primarily on 25-mm-diameter Si wafers that are subsequently sectioned into four  $6.35 \times 6.35$ -mm<sup>2</sup> chips. As already indicated, lift-off stencils are used for patterning

Figure 2 SEMs depicting junction area definition obtained by means of the photoresist stencil lift-off process. (a) A stencil prepared over the  $M_2$  layer and prior to SiO deposition. (b) The stencil after deposition of 275 nm of SiO. (c) The completed SiO opening through which a tunnel barrier is to be formed. Size bars represent 0.5  $\mu$ m.

the Pb-alloy, AuIn<sub>2</sub>, and SiO layers; the Nb and Nb<sub>2</sub>O<sub>5</sub> layers are patterned using photoresist masks and subtractive etching and anodizing, respectively.

Several types of photoresist stencils have been used [29, 30]; that used at present is formed by a single photoresist layer treated by immersion in chlorobenzene [31]. The upper surface of the photoresist is modified such that the development rate for the lower portion is relatively rapid. Using projection exposure, this results in the desired resist edge profile overhang of up to  $\approx 0.5 \mu m$ . A stencil thickness of approximately 800 nm is used for the layers  $\leq 500$  nm thick. For the M<sub>4</sub> and I<sub>4</sub> layers, a stencil about twice as thick is used. Many factors, such as photoresist adhesion, substrate reflectivity, stencil sputtering in the rf discharge, and SiO scattering, influence the effectiveness of the stencil process. For example, to overcome photoresist adhesion problems, hexamethyldisilazane (HMDS) [32] is used prior to photoresist application and a layer of  $TiO_r \approx 1$  nm thick is deposited on underlying SiO surfaces [18]; to ensure stencil lift-off after layer deposition, the stencil profile is formed in a manner adequate for use over the least reflective material (SiO). Also, the stencil overhang is sufficient to withstand the sputtering during rf discharge cleaning prior to deposition of the M<sub>2</sub>, M<sub>4</sub>, C, and R layers. Scattering of SiO beneath the stencil overhang during deposition affects SiO lift-off and junction area definition. The actual junction areas are defined at the interface between the photoresist and the base electrode [30]. Near-normal incidence of the SiO evaporant onto substrates is necessary for well-defined SiO film edges. Figures 2(a-c) show scanning electron micrographs (SEMs) of the junction area definition achieved by means of the photoresist stencil lift-off process.

Usually, a layer-to-layer registration of 2.5  $\mu$ m is used to ensure SiO insulation coverage at metal layer edges and to reduce the possibility of coincident layer edges that might affect pattern definition. However, in some in-

Figure 3 I-V characteristic of a logic interferometer similar to that shown in Fig. 1.

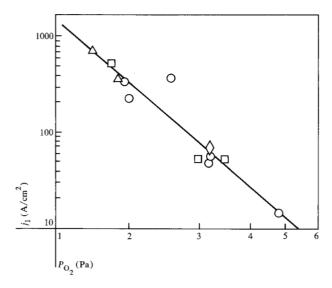

Figure 4 Dependence of junction current density on oxygen pressure used during the second stage of rf oxidation. Different symbols are used to distinguish junctions fabricated with base electrodes from different base-electrode deposition runs.

stances, in order to increase circuit density, a registration of 1.25  $\mu$ m is used [33]. In addition, occasional use is made of layers having coincident edges; the effects of such edges on pattern definition are negligible provided the layers are relatively thin.

## Characterization of circuit layers and circuit elements

The layers and circuit elements for a particular circuit experiment are characterized by using separate samples that are fabricated with the circuit samples and/or by incorporating test sites onto the circuit samples. The metal layers are characterized by measuring their electrical resistivity and (for the superconducting films) by measuring the critical current of a short line segment. The SiO and Nb<sub>2</sub>O<sub>5</sub> insulating layers are evaluated using capacitor structures. For devices, the single-particle-tunneling current-voltage (I-V) characteristics are measured at 4.2 K. The various types of superconducting contacts are characterized by their critical current levels at 4.2 K. Other aspects, such as pattern definition and SiO step coverage by metal layers, are evaluated by test sites designed for electrical measurement and inspected by optical and/or scanning electron microscopy. The superconducting properties of the elements can in some cases be used to advantage in characterizing the behavior of large populations of similar elements, as are needed for circuits. For example, the distribution in Josephson threshold current levels can be obtained from a four-terminal measurement of a seriesconnected string of many devices [4, 34]; the spatial distribution can be obtained by using matrix selection of individual junctions in a large array [34]. The quality of the electrical contacts and of the step coverage by superconducting lines can be judged by comparing the critical currents of lines containing many contacts or steps with those of planar segments of similar lines. (See later discussion.)

## Junctions and gates

A quasistatic I-V characteristic for a typical logic interferometer having four 2.5- $\mu$ m-diameter junctions is shown in Fig. 3. Circuit-design-related parameters, such as the Josephson current  $I_{\mathrm{m}}(0)$ , the current density  $j_1$ , and the energy gap  $\Delta_{\mathrm{M}_2} + \Delta_{\mathrm{M}_3}$ , are determined from the I-V characteristics. The value of  $j_1$  is determined from the relationship  $j_1A = k\delta I$ , where  $\delta I$  is the current jump at  $\Delta_{\mathrm{M}_2} + \Delta_{\mathrm{M}_3}$ , A is the junction area, and k is a constant that depends on the electrode materials ( $\approx 0.7$  for our junctions). The Josephson current  $I_{\mathrm{m}}(0)$  is related to  $j_1$ ; for the interferometer junctions typically used for circuit designs, the Josephson current is uniformly distributed over the junction area and  $I_{\mathrm{m}}(0) = j_1A$ .

Junctions having a desired  $j_1$  are obtained by adjusting the oxygen pressure  $P_{0_2}$  used for the second stage of the rf oxidation portion of the tunnel-barrier formation process. The dependence of  $j_1$  on  $P_{0_2}$  is shown in Fig. 4. Each data point gives the average current density for a group of 19 junctions on the same substrate. Each group was fabricated separately and measured after counter-electrode layer formation. Different symbols are used for junctions

fabricated with base electrodes from different deposition runs. It is evident from Fig. 4 that a wide range of  $j_1$  values are obtainable with good control by an appropriate choice of  $P_{0c}$ .

The  $j_1$  values increase when junctions are annealed. The magnitude of the increase is sensitive to both the oxidation conditions used to form the tunnel barrier and the time and temperature of annealing. An increase in  $j_1$  by a factor of 2-10 can be obtained after  $M_3$  layer formation by annealing at  $70^{\circ}$ C for a period of 90 min. (Such annealing is equivalent to the cumulative heat treatment that the junctions experience during the subsequent fabrication of the  $I_{3b}$ ,  $M_4$ , and  $I_4$  layers). The  $j_1$  changes observed for completed circuits are small at room temperature and can be arrested by using appropriate storage conditions [35].

The following procedure is used to achieve the  $I_{...}(0)$ values desired for circuits. Interferometer test structures are fabricated that are similar to those on the circuits and that have been fabricated with the circuits up to formation of the  $M_a$  stencil. A trial  $I_{2c}$ - $M_3$ - $I_{3a}$  run is then carried out using only the test interferometers. The thermal effects associated with formation of the I<sub>3b</sub>, M<sub>4</sub>, and I<sub>4</sub> layers are then simulated by annealing the interferometers at 70°C for 90 min. Using the  $j_1$  value obtained from the trial run, the  $P_{o_a}$  value to be used for rf oxidation of the circuit samples is adjusted as needed to achieve the desired  $I_m(0)$ value. This procedure reduces the effects of both shortand long-term run-to-run variations that can occur in base-electrode-layer formation, in instrumentation for measuring plasma parameters, in junction area, etc. By using this procedure, the run-to-run variations in j, for completed circuits can be made comparable to those shown for the junction data in Fig. 4.

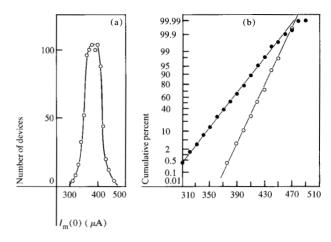

The variation in  $I_m(0)$  values across a chip has been measured [34] for several chips populated with an array of 784 individually measurable three-junction interferometers containing junctions having nominal diameters of 5, 7, and 5  $\mu$ m, respectively. The distribution for a chip is shown in Fig. 5(a). The I<sub>m</sub>(0) distribution is nearly Gaussian [filled circles in Fig. 5(b)]; the data fall on a straight line when plotted using a cumulative normal distribution ordinate. The standard deviation  $\sigma$  is 7%. However,  $I_m(0)$ varies systematically with the position of the junctions on the chip. (This variation is observed to correlate with the position the junctions occupied along the rf electrode radius during rf oxidation and in practice can be reduced by rotating the samples on the rf electrode during tunnelbarrier formation [36].) If this systematic component is removed from the data [open circles in Fig. 5(b)], the adjusted standard deviation  $\sigma'$  is 4%. The contributions to the  $I_m(0)$  distributions of variations in j, and junction area

Figure 5 (a) The distribution of  $I_m(0)$  having  $\sigma = 7\%$  for a chip containing 784 three-junction interferometers. (b) The same distribution of  $I_m(0)$  plotted using a cumulative normal distribution ordinate ( $\bullet$ ). Also included is the distribution after a systematic component has been removed from the data ( $\bigcirc$ ), where  $\sigma' = 4\%$ .

were found from separate experiments to be comparable for 5- $\mu$ m-diameter junctions and consistent with the  $\sigma' = 4\%$  obtained for the data shown in Fig. 5(b).

#### Contact:

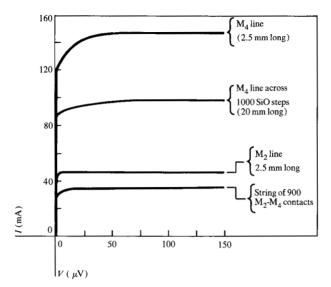

The M<sub>2</sub>, M<sub>4</sub>, and C layers have nominally identical compositions, and interconnections between them are readily made. For example, M2-M4 contacts are used for forming x- and y-line connections, and C-M<sub>4</sub> contacts are used (in conjunction with M,-C contacts) to form ground-plane contacts. These contacts are superconducting with a high critical current in the presence of a thin oxide layer between them, due in part to the presence of In in both electrodes [37]. This oxide layer results from the rf oxygen discharge utilized prior to deposition of the M<sub>2</sub> and M<sub>4</sub> layers for cleaning the surfaces exposed in the stencil used for patterning those layers. The discharge does not cause any significant alteration of the exposed SiO or Nb<sub>0</sub>O<sub>E</sub> insulation layers. The oxide also prevents interdiffusion of the layers at the contacts during the sequential film deposition used to form the M<sub>4</sub> layer. The current level I<sub>c</sub> at which such contacts become nonsuperconducting increases with contact width. For  $2.5 \times 2.5$ - $\mu$ m<sup>2</sup> M<sub>2</sub>-M<sub>4</sub> contacts  $I_c \approx 8$  mA. As indicated previously, the contacts can be characterized using series-connected contact strings; e.g., for a string of 900 M<sub>2</sub>-M<sub>4</sub> contacts, 7  $\times$  7  $\mu$ m<sup>2</sup>,  $I_a \approx 35$  mA, as shown in Fig. 6. For comparison,  $I_c$  values of 7- $\mu$ m-wide, 2.5-mm-long  $M_a$  and  $M_a$ lines are  $\approx$ 45 and 150 mA, respectively; and for a 7- $\mu$ mwide, 20-mm-long M<sub>4</sub> line that crosses 1000 I<sub>3b</sub> steps, it is ≈90 mA.

Figure 6 I-V characteristics of typical lines (7  $\mu$ m wide) and a series-connected string of superconducting contacts.

Figure 7 Edge length per insulator defect *versus* SiO thickness for  $M_2/I_{3b}/M_4$  ( $\bullet$ ) and  $M_3/I_{3a}+I_{3b}/M_4$  ( $\circ$ ) crossings. The dashed line gives the total testable edge length per wafer. The insets show cross sections of structure edges.

Superconducting contacts to the Nb ground plane are made by using an rf Ar plasma to remove surface oxide followed by in situ deposition of the C layer. Sputteretching parameters (360 V at 1.3 Pa of Ar for 15 min) are chosen to minimize photoresist polymerization (which affects stencil lift-off). For the  $\rm M_1\text{-}C$  contacts,  $I_{\rm c}\approx 50$  mA for  $8\times 13\text{-}\mu\text{m}^2$  contacts.

Superconducting contacts to the  $M_3$  layer are formed with the  $M_2$  layer, *i.e.*, by forming Josephson junctions. This procedure allows low-resistance contacts to be formed without incurring interdiffusion of the  $M_2$  and  $M_3$  layers. The area of such "contact junctions" is chosen so that the  $I_{\rm m}(0)$  level is not exceeded in normal circuit operation.

# • Resistors

Resistors of a desired value are obtained by choosing the geometry and sheet resistances at 4.2 K  $R_{so}$  of the AuIn<sub>2</sub> films. Values of  $R_{so}$  in the range of 0.1-4  $\Omega/\Box$  can be obtained conveniently by using an appropriate AuIn<sub>2</sub> film thickness d, since in this range  $R_{so} \approx d^{-1.8}$ . See the accompanying paper by Kircher and Lahiri for details [20]. For circuit fabrication, a procedure has been adopted in which a "trial" resistor deposition is carried out immediately prior to that used for circuit fabrication. On the basis of the  $R_{so}$  obtained for the trial film, d is chosen for the circuit resistor deposition to be subsequently used for circuit samples. The ratios of the actual-to-target  $R_{so}$  values obtained using this procedure for a sequential series of 12 circuit fabrication runs varied from 0.8 to 1.25, with most falling between 0.96 and 1.1. The run-to-run variation of resistor values in circuits was somewhat larger than this, reflecting the added influences of other variables, e.g., geometry, contact resistance, and  $R_{so}$  uniformity.

Contacts to the resistors are achieved with the  $M_2$  or  $M_4$  layers by following the previously described oxygen rf discharge stencil cleaning procedure; the contact resistances are typically  $\approx 0.15~\Omega$  for each  $7\times7-\mu\text{m}^2$  contact. Lahiri has shown that such resistors are sufficiently stable during subsequent storage and annealing [19].

## Lines

The  $I_c$  levels of the superconducting  $M_2$ ,  $M_3$ ,  $M_4$ , and C lines vary linearly with linewidth for lines prepared over a superconducting ground plane. For linewidths of 2.5-40  $\mu$ m,  $I_c \approx 10$  mA/ $\mu$ m for the  $M_2$ ,  $M_3$ , and C lines, and 20 mA/ $\mu$ m for the  $M_4$  lines. A reduction in  $I_c$  can occur for long lengths of line because of line defects and/or inadequate edge coverage where lines cross the edges of underlying layers. For example, a line defect level of  $\approx 1200$  mm per defect was found in one experiment using a group of  $\approx 500$  test sites, each having 72 mm of 3.8- $\mu$ m-wide  $M_4$  lines [17].

## • Insulated crossing

Insulating SiO layers can be prepared with low electrical defect densities. Using a 5-V test, SiO area per defect values typically obtained for unpatterned Pb-alloy films coated with unpatterned SiO films having thicknesses of

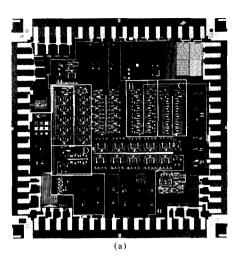

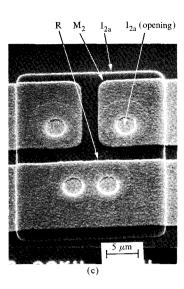

Figure 8 (a) Chip containing experimental current injection logic devices and circuits. Ten-stage chains of four-input AND circuits (A), four-input OR circuits (B), two-input AND circuits (C), and two-input OR circuits (D). (b) SEM of a portion of C showing two interconnected interferometers and a two-junction current injection gate (right, center). (c) SEM of the center portion of one interferometer after formation of its  $I_{2n}$  layer;  $\approx 2.5 - \mu$ m-diameter junction openings.

100-600 nm were >20 mm<sup>2</sup>. The area per defect was smaller when patterned SiO and Pb-alloy films were used; however, these defect densities are adequate for coverage of  $\approx 1 \text{ mm}^2$ , the estimated active SiO area of a 6.35  $\times$  6.35-mm<sup>2</sup> chip.

Insulation of metal edges by SiO is most demanding for x- and y-interconnection line crossings (M<sub>a</sub>/SiO/M<sub>a</sub>) and for device crossings (M<sub>3</sub>/SiO/M<sub>4</sub>). The insulation defect levels at M<sub>2</sub> and M<sub>3</sub> edges in such structures were estimated by comparing the defect levels obtained for two types of capacitor test sites that were interspersed on the same wafer. The test sites had the same active SiO area but had lengths of insulated M, or M, edge that differed by more than a factor of 10<sup>3</sup>. Edge length per insulator defect levels  $E_{\rm p}$  determined in this manner using a 5-V test are shown in Fig. 7. Each data point gives the  $E_{\rm p}$  value obtained for a group of test sites on a single wafer having a total testable edge length of ≈2200 mm per wafer (dashed line). For wafers having one or no edge defects,  $E_{\rm D}$  values are plotted on the dashed line. Typically,  $E_{\rm D} > 500$  mm for both  $M_2$  and  $M_3$  edges at SiO thicknesses  $\geq 400$  nm.

## **Devices and circuits**

A photograph of a chip containing several experimental devices and circuits that were used to investigate the logic delay for current injection logic [38] is shown in Fig. 8(a). The  $6.35 \times 6.35$ -mm<sup>2</sup> chip has 64 peripheral contact pads and includes AND and OR circuit chains of logic interferometers. Illustratively, a ten-stage AND circuit chain

containing about 75 interconnected interferometers is in region A; a ten-stage OR circuit chain containing about 25 interconnected interferometers is in Region B. Two such interconnected interferometers, which form a portion of the AND circuit chain in region C of Fig. 8(a), are shown in Fig. 8(b). The interferometers are identical to the one shown in Fig. 1; they contain four junctions of equal area (≈2.5-µm diameter) with underlying damping resistors (not visible) and overlying  $\approx 2.5 - \mu \text{m}$ -wide control line loops. They are connected to the ground plane at a central M<sub>1</sub>-C-M<sub>4</sub> contact. The region shown in Fig. 8(b) contains a total of about 15 resistors (not visible). The center portion of a partially completed interferometer is shown in Fig. 8(c). The damping resistors, base electrode, and  $I_{22}$ openings that define the junction areas are indicated. Measurements of the average logic delay obtained from the two-input AND and OR chains were 26 and 13 ps, respectively [38].

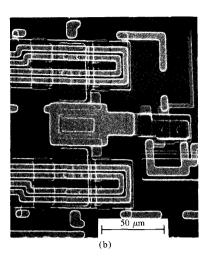

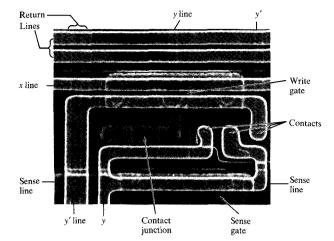

An experimental low-flux-quantum Josephson non-destructive read out (NDRO) memory cell [33] is shown in Fig. 9. The memory cell,  $58 \times 48 \ \mu m^2$  in size, contains a write gate (a three-junction interferometer), a sense gate (a two-junction interferometer), lines ( $M_2$  and  $M_4$ ) for cell interconnections, a contact junction ( $M_2$ - $M_3$ ), contacts ( $M_2$ - $M_4$ ), and a damping resistor (not visible) between the write gate and contact junction. The cell design contains 2.5- $\mu$ m linewidths and line spacings, and a layer-to-layer registration of 1.25  $\mu$ m. Additionally, the design includes coincident edges between some overlying or adjacent lay-

Figure 9 SEM of an experimental low-flux-quantum Josephson NDRO memory cell. The x- and y-interconnection lines are  $\approx 2.5 \ \mu \text{m}$  wide.

ers. Such cells have been fabricated and operated successfully with a stored energy of only  $\approx 6 \times 10^{-2}$  J. They are electrically attractive as the basis for a high-speed cache memory array [33].

# **Concluding remarks**

Additional advances have been made in the previously described process for fabricating experimental Josephson circuits [3]. The process has been extended to the 2.5- $\mu$ m-linewidth and junction-diameter levels. The circuits now utilize interferometers as active elements. Logic and memory circuits containing up to 14 layers and about 100 interferometers have been successfully fabricated [38, 39]. The circuits also contain lines, contacts and transformers, insulated crossings and capacitors, resistors, and power regulators, which are formed in an integrated manner with the interferometers.

Associated circuit performance studies continue to indicate that Josephson circuits have potential for the fabrication of ultrafast computing systems [1, 2]. In order to realize this potential, further development of the process described here will be necessary. Additionally, larger collections of logic and memory circuits having acceptable circuit parameters must be successfully fabricated and must be capable of surviving subsequent packaging and use conditions, including repeated cycling to 4.2 K.

## **Acknowledgments**

Many co-workers were involved in the development and evaluation of the described fabrication process. In particular, we gratefully acknowledge the technical assistance of J. M. Brown, R. E. Drake, M. J. Palmer, W. K. Schug,

P. J. Spadiro, J. F. Stewart, and V. Tom with thin film depositions; A. L. Ginzberg, R. M. Patt, and T. Ross with photolithography; and K. D. Arfman, A. Halperin, J. S. Neely, S. J. Singer, J. F. Smith, and W. G. Thorn with electrical measurements and equipment development.

### References and notes

- 1. J. Matisoo, IBM J. Res. Develop. 24 (1980, this issue).

- 2. W. Anacker, IBM J. Res. Develop. 24 (1980, this issue).

- J. H. Greiner, S. Basavaiah, and I. Ames, J. Vac. Sci. Technol. 11, 81 (1974).

- (a) See for example A. F. Hebard and R. H. Eick, J. Appl. Phys. 49, 339 (1978); (b) R. F. Broom, P. Guéret, W. Kotyczka, Th. O. Mohr, A. Moser, A. Oosenbrug, and P. Wolf, International Solid-State Circuits Conference (ISSC78) Digest 40, 60 (1978); (c) R. H. Havemann, C. A. Hamilton, and R. E. Harris, J. Vac. Sci. Technol. 15, 392 (1978); (d) A. Ishida, K. Kuroda, T. Wahs, and H. Yamada, presented at the Solid State Devices Conference, Tokyo, Japan, August 1978; (e) R. F. Broom, R. Jaggi, Th. O. Mohr, and A. Oosenbrug, IBM J. Res. Develop. 24 (1980, this issue).

- 5. I. Ames, IBM J. Res. Develop. 24 (1980, this issue).

- C. Kircher, K. Grebe, I. Ames, and W. Anacker, IBM Thomas J. Watson Research Center, Yorktown Heights, NY, unpublished work; H. C. Jones, D. J. Herrell, and Y. L. Yao, IEEE Trans. Magnetics MAG-15, 432 (1979); P. Geldermans and C. Y. Ting, IBM Thomas J. Watson Research Center, Yorktown Heights, NY, unpublished results.

- 7. S. Basavaiah and J. H. Greiner, IBM Thomas J. Watson Research Center, Yorktown Heights, NY, unpublished results.

- W. Anacker, K. Grebe, J. H. Greiner, S. K. Lahiri, K. C. Park, and H. Zappe, U.S. Patent 3,733,526, 1973; S. K. Lahiri, U.S. Patent 3,999,203, 1976.

- S. K. Lahiri, J. Vac. Sci. Technol. 13, 148 (1976) and cited references; S. K. Lahiri and S. Basavaiah, J. Appl. Phys. 49, 2880 (1978).

- W. H. Henkels and C. J. Kircher, *IEEE Trans. Magnetics* MAG-13, 637 (1977).

- R. E. Joynson, C. A. Neugebauer, and J. R. Rairden, J. Vac. Sci. Technol. 4, 171 (1967).

- K. Grebe, IBM Thomas J. Watson Research Center, Yorktown Heights, NY, unpublished results.

- J. M. Baker, IBM Thomas J. Watson Research Center, Yorktown Heights, NY, unpublished results.

- 14. J. M. Baker, C. J. Kircher, and J. W. Matthews, *IBM J. Res. Develop.* 24 (1980, this issue).

- S. K. Lahiri, IBM Tech. Disclosure Bull. 21, 3403 (1979);

S. K. Lahiri, S. Basavaiah, and C. Kircher, Appl. Phys. Lett., in press.

- 16. S. K. Lahiri, IBM Tech. Disclosure Bull. 22, 3886 (1980).

- 17. S. Klepner, IBM Thomas J. Watson Research Center, Yorktown Heights, NY, unpublished results.

- E. Yen, IBM General Products Division laboratory, San Jose, CA, unpublished results.

- 19. S. K. Lahiri, *Thin Solid Films* **41**, 209 (1977).

- C. J. Kircher and S. K. Lahiri, IBM J. Res. Develop. 24 (1980, this issue).

- 21. L. M. Geppert, J. H. Greiner, D. J. Herrell, and S. Klepner, *IEEE Trans. Magnetics* MAG-15, 412 (1979).

- 22. S. Basavaiah and C. J. Kircher, IBM Thomas J. Watson Research Center, Yorktown Heights, NY, unpublished results.

- A. E. Hill and G. R. Hoffman, Brit. J. Appl. Phys. 18, 13 (1967);

J. Priest and H. L. Caswell, Transactions of the 8th National Vacuum Symposium, Pergamon Press, Elmsford, NY, 1961, p. 47.

- 24. W. Hammer and C. J. Kircher, IBM Thomas J. Watson Research Center, Yorktown Heights, NY, unpublished results.

- S. I. Raider and R. Flitsch, J. Electrochem. Soc. 123, 1755 (1976).

- S. Basavaiah, J. M. Eldridge, and J. Matisoo, J. Appl. Phys.

45, 457 (1974); also contained in that paper is a review of applicable theoretical studies.

- 27. J. H. Greiner, J. Appl. Phys. 42, 5151 (1971); 45, 32 (1974).

- 28. J. H. Greiner and S. Basavaiah, IBM Thomas J. Watson Research Center, Yorktown Heights, NY, unpublished results.

- K. Grebe, I. Ames, and A. Ginzberg, J. Vac. Sci. Technol. 11, 458 (1974).

- A. Warnecke, R. M. Patt, and C. J. Johnson, Jr., Kodak Microelectronics Seminar Proceedings (INTERFACE '77), Eastman Kodak Company, Rochester, NY, 1978, p. 145.

- B. J. Canavello, M. Hatzakis, and J. M. Shaw, IBM Tech. Disclosure Bull. 19, 4048 (1977); M. Hatzakis, IBM Thomas J. Watson Research Center, Yorktown Heights, NY, unpublished results.

- Purchased from SCM Organic Chemicals Division, SCM Corporation, Gainesville, FL 32602.

- 33. W. H. Henkels and J. H. Greiner, IEEE J. Solid-State Circuits SC-14, 794 (1979).

- 34. S. Basavaiah, J. H. Greiner, H. H. Zappe, and S. J. Singer, J. Appl. Phys., in press.

- S. Basavaiah, K. R. Grebe, J. H. Greiner, S. K. Lahiri, and A. Scott, *IBM Tech. Disclosure Bull.* 17, 3488 (1975); R. F. Broom, R. Jaggi, Th. O. Mohr, and A. Oosenbrug, *IBM Zurich Research Laboratory*, unpublished results.

- P. Brosious, IBM Thomas J. Watson Research Center, Yorktown Heights, NY, unpublished results.

- 37. W. Anacker, J. Greiner, and K. Grebe, IBM Thomas J. Watson Research Center, Yorktown Heights, NY, unpublished work; I. Ames, U.S. Patent 3,852,795, 1974.

- 38. T. R. Gheewala, Appl. Phys. Lett. 33, 781 (1978); 34, 670 (1979).

- 39. W. H. Henkels, J. Appl. Phys. 50 (Dec. 1979).

Received May 17, 1979; revised October 2, 1979

E. T. Yen is located at the IBM General Products Division laboratory, San Jose, California 95150; the other authors are at the IBM Thomas J. Watson Research Center, Yorktown Heights, New York 10598.