# R. Sommerhalder

# Dynamic Performance of Schottky-barrier Field-effect Transistors\*

Abstract: The dynamic performance of Schottky-barrier field-effect transistors is discussed, with the aim of finding in a most simple way the physical parameters on which the dynamic properties of a FET depend, how strong they influence the dynamic qualities of FET's, and what recommendations can be given as to proper choice of material or structure for FET's with good high-frequency performance.

#### **Symbols**

- b gate width

- $C_0$  channel-to-gate capacitance per unit length

- $C_{\rm sg}$  source-gate capacitance

- C<sub>sd</sub> source-drain capacitance

- $C_{\rm dg}$  drain-gate capacitance

- d transistor thickness

- E electric field

- $E_{\rm c}$  critical electric field

- $f_0$  frequency limit

- i channel current

- L gate length

- l channel thickness

- $L_{\rm eff}$  effective length of saturated channel section

- N density of donor centers

- Q charge of free carrier per unit

- R<sub>d</sub> drain resistance

- $R_0$  resistance per unit length

- R<sub>s</sub> source resistance

- v drift velocity

- v<sub>s</sub> saturation drift velocity

- $V_{\rm sd}$  source-drain bias voltage

- $V_{\rm gc}$  gate-channel voltage

- $V_{\rm sg}$  source-gate bias voltage

- $V_{\rm D}$  diffusion voltage

- z impedance

- $z_{\rm sd}$  source-drain impedance

- $z_{\rm sg}$  source-gate impedance

- $z_{\rm gd}$  gate-drain impedance

- z<sub>r</sub> right-end channel impedance

- $\phi$  phase of impedance

- $\tau$  time constant

- μ mobility

#### I. Introduction

The theory presented here is the result of a search conducted with the aim of finding in a most quick and simple manner—at the expense of numerical accuracy—the physical parameters on which the dynamic properties of the field-effect transistor (FET) depend, how strong they influence the dynamic qualities of FET's, and what recommendations can be given as to proper choice of material or structure for FET's with good high-frequency performance.

We shall first derive an equivalent network for a FET which permits approximate calculation of the dynamic response of a field-effect transistor to small, periodically applied gate signals, if the static situation in respect to the operating point is already known. Static solutions on which the dynamics are based will be introduced, with special emphasis placed on the case of a small gate electrode length (i.e., a gate length comparable to the thickness of the transistor), and on the effects due to carrier velocity saturation. Plots of source-to-gate impedance, gate-to-drain impedance, source-to-drain impedance and transconductance are shown for the cases where there was available information on the dc conditions at the operating point.

The main result will be that lumped FET's need not be slow compared to bipolar transistors. Additional high-frequency potentialities may be found if sophisticated devices such as distributed FET's are studied, but this is not done here. Ratios of  $g_m/C$  in the 10 to 30 GHz range may be expected if the transistors are made small enough

The authors are located at the IBM Zurich Research Laboratory, 8803 Rüschlikon-ZH, Switzerland.

<sup>\*</sup> This work has been supported partly by Office of Aerospace Research, U. S. Air Force contract F19628-68-C-0343.

and from a highly doped material with a high value of saturated drift velocity. Typical data may be: (1) carrier concentration  $N \approx 10^{17}/\text{cm}^3$  (or higher, but electric breakdown at the gate will probably soon set an upper limit); (2) saturated drift velocity  $v_s \approx 1$  to  $2 \times 10^7 \text{cm/sec}$ ; and (3) gate length and interspace to source and drain  $\delta \approx 1$  micrometer. In addition, the transistors have to be thin enough (a fraction of one micrometer thick) for reduction of their dc losses to tolerable limits.

# II. Equivalent network of a FET

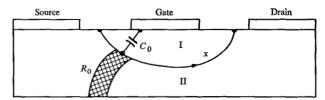

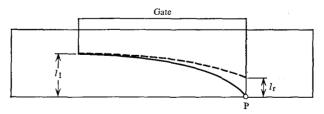

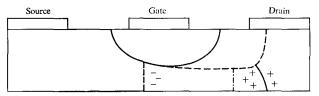

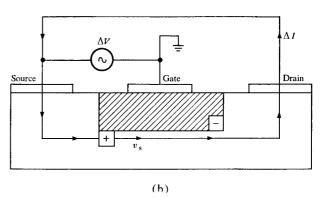

Let us consider a two-dimensional field-effect transistor structure, as shown in Fig. 1, with width b perpendicular to the cross-section.

Let us suppose further that the *static* properties of the FET are known, in particular the resistance per unit length  $R_0$ , of the conducting channel at position x, the capacitance per unit length  $C_0$ , of the conducting channel against the gate electrode at position x, where the coordinate x measures the length of the boundary line separating the depleted and conducting regions, with its origin at the end between source and gate electrodes.

If we now apply a *small and periodic* gate voltage at angular frequency  $\omega$ , a small ac current  $\Delta i(x, \omega)$  will flow through the conducting channel.

The current i is partly due to a change in the number of free carriers per unit length, Q, of the conducting channel, and partly due to a change of their drift velocity, v:

$$\Delta i = \Delta Q \cdot v + Q \cdot \Delta v = \Delta (Qv). \tag{1}$$

In addition,  $\Delta i$  and  $\Delta Q$  are related by the equation of continuity

$$\frac{\partial \Delta i}{\partial x} + \frac{\partial \Delta Q}{\partial t} = 0$$

$$\frac{\partial \Delta i}{\partial x} = -\frac{\partial \Delta Q}{\partial t} = -j\omega \Delta Q.$$

(2)

Combining Eqs. (1) and (2) yields

$$\Delta i = -\frac{v}{i\omega} \frac{\partial \Delta i}{\partial x} + Q \Delta v. \tag{3}$$

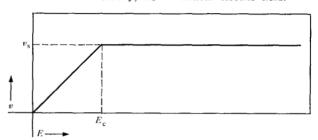

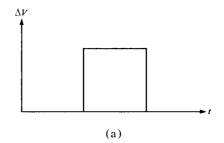

So far, no explicit dependence of the drift velocity, v, of the free carriers on the electric field, E, in the channel has been introduced. It is done now, using the simplified relation shown in Fig. 2, which takes into account the typical low field (constant mobility,  $\mu$ ) and high field (constant drift velocity,  $v_s$ ) ranges properly but assumes a sharp transition at  $E=E_c$  from one to the other region instead of a smeared-out one.

Then, for  $E < E_c$  (for constant mobility there is no space charge in the channel) a change  $\Delta Q$  of free carriers in the conducting channel is associated with a change of the channel-to-gate voltage,  $\Delta V(x, \omega)$ , given by

**Figure 1** Field-effect transistor structure and notations: I = Depleted region; II = Conducting channel region;  $R_0 = Resistance per unit width of conducting channel$ ;  $C_0 = Channel-to-gate capacitance per unit width of conducting channel.$

Figure 2 Drift velocity versus electric-field relationship.  $v_s =$  Saturation drift velocity;  $E_c =$  critical electric field.

$$\Delta V = \frac{1}{C_0} \Delta Q = -\frac{1}{j\omega C_0} \frac{\partial \Delta i}{\partial x}.$$

(4)

In addition, we have

$$\Delta v = \mu \Delta E = -\mu \frac{\partial \Delta V}{\partial x}$$

$$\mu Q = \frac{1}{R_0}$$

(5)

so that we need to find from Eqs. (3), (5) and (4),

$$\Delta i = -\frac{v(x)}{j\omega} \frac{\partial \Delta i}{\partial x} + \frac{1}{R_0(x)} \frac{\partial}{\partial x} \left( \frac{1}{j\omega C_0(x)} \frac{\partial \Delta i}{\partial x} \right). \tag{6}$$

Equation (6) is a differential equation for the ac current. It can be solved provided that v(x),  $C_0(x)$  and  $R_0(x)$  are known.

For  $E > E_c$  we have  $\Delta v = 0$ . Therefore, Eq. (3) simplifies directly into

$$\Delta i = -\frac{v_s}{j\omega} \frac{\partial \Delta i}{\partial x}.$$

(6')

The characteristic channel impedance  $z(x, \omega)$  becomes with Eqs. (4) and (6),

$$\frac{1}{z} = v(x)C_0(x) - \frac{1}{R_0(x)} \frac{C_0(x)}{\frac{\partial \Delta i}{\partial x}} \frac{\partial}{\partial x} \left( \frac{1}{C_0(x)} \frac{\partial \Delta i}{\partial x} \right)$$

(7)

83

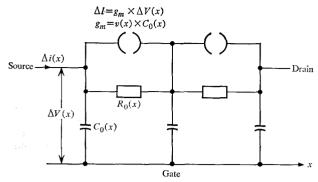

Figure 3 Equivalent electric network of a field-effect transistor.

Figure 4 Depletion region for a FET with a drift-velocity saturated conducting channel (schematic).

for  $E < E_c$ , and reaches, at position  $x = x_0$  for which  $E(x_0) = E_c$ , a value

$$1/z = v_* C_0(x_0). (7')$$

An equivalent electric network corresponding to Eqs. (6) and (6') is a set of FET's forming the transmission line for wave propagation as shown in Fig. 3. For the drift velocity saturated channel section,  $R_0 \to \infty$  because the mobility used here is  $\mu = \partial v/\partial E$  and for  $E > E_c$ ,  $\mu = 0$ . Sections with  $C_0 = 0$  may exist at the source or drain directed ends of the channel; for these sections  $g_m = 0$ , so that nothing more than their total resistance  $R_s$  (source resistance) or  $R_d$  (drain resistance) must be taken into account.

A simple qualitative discussion may convince us that the methods of wave propagation are well suited to get an understanding for the solution of Eqs. (6) and (7).

For  $E > E_c$ , Eq. (6') shows after immediate integration that

$$\Delta i \approx \exp\left(-\frac{j\omega}{v_A}x\right)$$

, (8)

which is an unattenuated current wave propagating through the channel with saturation drift velocity  $v_{\rm s}$ . A very similar delay-line type solution

$$\left(\Delta i \approx \exp -\int \frac{j\omega}{v(x)} dx\right) \tag{9}$$

also exists in the case  $E < E_{\rm e}$ , provided that the second term on the right-hand side of Eq. (6) is negligibly small compared to the first one. If, on the other hand, the second right-hand term of Eq. (6) predominates over the first, we are merely left with the differential equation for an RC-transmission line.

Note that the delay-line solutions are unidirectional (source  $\rightarrow$  drain) waves, while the *RC*-line solutions are two-directional (source  $\rightleftharpoons$  drain) current waves.

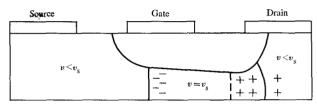

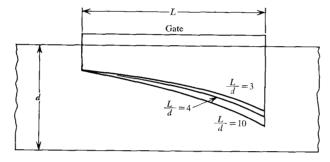

# III. Some remarks on static performance, mainly transconductance

Unfortunately there is not ample theoretical information available on such static data as requested by Eq. (6). Shockley's well-known gradual-case theory applies only to the case of a very-long-gate electrode (gate length >>> transistor thickness) and, further, neglects drift velocity saturation of the carriers running through the conducting channel. The authors<sup>2</sup> handled, by means of an analog model, the case of FET's with a gate electrode length as small as the thickness of the transistor, but likewise ignored drift-velocity saturation in the conducting channel. Inclusion of these latter effects seems to call for a sophisticated numerical analysis, but sufficient results are not yet available to us. In this paper we suggest that for an operating point in the saturation region of the draincurrent versus drain-voltage characteristics, a drift-velocity saturated channel section exists, as indicated schematically in Fig. 4, whose length increases with increasing drain voltage and may become predominating over the unsaturated section. The accumulation of charges is treated by Kennedy. 5 Before going into Eq. (6), we discuss with this diagram some static aspects involved with respect to the transconductance,  $g_m$ . If  $g_m$  is mainly limited by the drift velocity saturation, we can identify the transconductance of the transistor with that of the saturated channel part of Fig. 4. In order to calculate the latter expression, we distinguish by subscripts I and r, values referring to the left- and right-hand ends of the saturated channel, respectively, and find with Eqs. (7) and (4) in a straightforward manner that the transconductance is equal to the reciprocal left-hand end channel impedance:

$$g_m = \frac{\Delta i_r}{\Delta V_1} = \frac{\Delta i_1}{\Delta V_1} = \frac{1}{z_1} = v_s \cdot C_{01}.$$

(10)

The result expressed by Eq. (10) differs remarkably from the well-known formula:

$$g_m = \frac{\sigma b d}{L} \tag{11}$$

of the Shockley theory, where  $\sigma = \text{conductivity}$ , b = device width, d = device thickness and L = gate length. This difference is not surprising, because Eq. (11) was

derived for a different geometry (a large gate electrode length, L, compared to the transistor thickness, d) and because drift velocity saturation was ignored. Either the difference in geometry or the neglectance of drift-velocity saturation might account for the discrepancy in the results obtained for  $g_m$ . In order to analyze this question further, we now consider a transistor with a long gate electrode  $(L \gg d)$ , but take drift-velocity saturation into account.

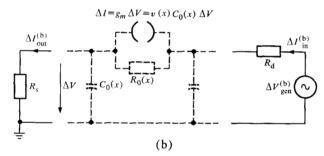

In this case, we have made the assumption that the drift velocity saturation is confined to an extremely thin region at the right-hand end of the conducting channel. This assumption is based on the fact that the output conductance is low for higher drain voltages, and therefore the drain current is almost independent of drain voltage. If the drain current is almost constant, this means that the geometry of the unsaturated part of the depletion-layer will change very little when drain voltage is varied. We assume, then, constant mobility in the whole channel. Thus it is only the boundary condition at the right-hand end of the channel which becomes different, according to whether or not drift-velocity saturation is taken into account. Shockley assumed  $v_r \to \infty$ , which corresponds to a rightend channel impedance  $z_r = 0$  (instead of  $z_r = 1/v_s C_{0r}$ ), and as a consequence of this he obtained drain-current saturation for complete pinch-off instead of for a finite width,  $l_r$ , of the conducting channel (see Fig. 5).

In order to derive the formal expression for the transconductance, we have to combine the Shockley equation<sup>3</sup>†

$$I_{\rm sd} = \frac{\sigma b d}{L} \left[ \left( 1 - \frac{2}{3} \sqrt{\frac{V_{\rm r}}{Ned^2}} \right) V_{\rm r} + \left( 1 - \frac{2}{3} \sqrt{\frac{V_{\rm sg}}{Ned^2}} \right) V_{\rm sg} \right]$$

$$(12)$$

where ( $\sigma$  = conductivity, N = free carrier concentration,  $\epsilon$  = dielectric constant, b = width of the transistor, L = gate electrode length, d = thickness of the transistor) relating the drain current,  $I_{\rm sd}$ , to the left- and right-hand end channel-to-gate voltages  $V_{\rm sg}$  (source-to-gate voltage) and  $V_{\rm r}$ , respectively, with the expression for the saturated current

$$I_r = (Ne \, v_s)b \, I_r = I_{\rm sd}, \tag{13}$$

$(v_{\bullet} = \text{saturation-drift velocity})$  where according to the Shockley theory the width of the channel is

$$l_{\rm r} = d \left[ 1 - \sqrt{\frac{V_{\rm r}}{Ned^2}} \right], \tag{14}$$

and then find by straightforward calculation for small changes of current,  $\Delta I_{sd}$ , and voltage,  $\Delta V_{sg}$ ,

Figure 5 Schematic plots of depletion layer according to Shockley's theory (-), and modified owing to drift-velocity saturation (--). G = Gate electrode; P = Pinch-off point;  $l_1$ ,  $l_r = Left$  and right-hand widths of conducting channel.

$$g_{m} = \frac{\Delta I_{\text{sd}}}{\Delta V_{\text{sg}}} = \frac{g_{m(\text{Shockley theory})}}{1 + \left(\frac{1}{v_{\text{s}} \cdot C_{0r}}\right) \cdot \frac{l_{r}}{l_{l}} \cdot g_{m(\text{Shockley theory})}}, \quad (15)$$

where

$$g_{m(\text{Shockley theory})} = \frac{\sigma b d}{L} \left[ 1 - \sqrt{\frac{V_{sg}}{Ned^2}} \right],$$

(16)

$$C_{0r} = \varepsilon \varepsilon_0 b/(d-l_r)$$

and (17)

$$l_1 = d \left[ 1 - \sqrt{\frac{V_{\text{sg}}}{Ned^2}} \right]$$

(18)

Since in this calculation we have not explicitly made use of the right-hand end channel impedance, it is instructive to verify Eq. (10) for this special case. Indeed we easily find from Eqs. (13) and (14):

$$z_{\rm r} = \frac{\Delta V_{\rm r}}{\Delta I_{\rm sd}} = \frac{1}{C_{0_{\rm r}} \cdot v_{\rm s}}$$

(19)

Figure 6 shows an example of  $g_m$ ,  $g_m$  (Shockley theory) and  $1/v_s$   $C_{0r}$  versus free carrier concentration, N, for the data b=1 mm,  $L=4\mu$ ,  $d=1\mu$ ,  $\mu=2500$  cm<sup>2</sup>/V·sec,  $V_{sg}=0$  volt. The essence of the plots is that the Shockley theory formula is essentially correct as long as  $g_m$  (Shockley theory)  $\ll C_{0r} \cdot v_s$ , but fails for  $g_m$  (Shockley theory)  $\gg C_{0r} \cdot v_s$ . If the last-mentioned condition holds,  $g_m$  is rather close to  $C_{0r} \cdot v_s$ , although, in principle, a larger transconductance than this can be achieved. Equation (10) is valid for the saturated part of the channel with either a long  $(L \gg d)$  or short (L=d) gate electrode, and  $C_{0r} \cdot v_s$  is a "figure of merit" for the largest transconductance achievable.

Although the purpose of this paper is to discuss the performance of a lumped device, it is appropriate to make some remarks with regard to a distributed FET. By this we mean an FET with a width b so large that source, gate and drain electrodes have to be considered as transmission lines for wave propagation. The lumped device may be considered as a cross-section of the distributed device.

Let us first see what transconductance values are required in order to obtain voltage, current or power amplifi-

<sup>†</sup>  $I_A \rightarrow I_{rd}/2$ ,  $a \rightarrow d$ ,  $(U_A - U_c) \rightarrow V_r$  have to be substituted to adopt the notations, and correct for a slightly different geometry.

**Figure 6** Gradual case transconductance  $g_m$  as a function of free carrier concentration, N. Values of  $g_{m(Shockley Theory)}$  and  $(C_{0r} \cdot v_s)$  are plotted for comparison.  $L = 4\mu$ ,  $d = 1 \mu$ , b = 1 mm,  $\mu = 2500 \text{ cm}^2/\text{V} \cdot \text{sec}$ ,  $V_{sg} = 0$ .

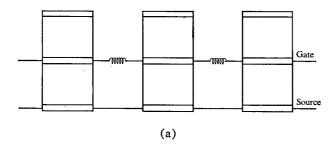

Figure 7 Distributed FET. Schematic plot of source-to-gate and source-to-drain transmission lines.

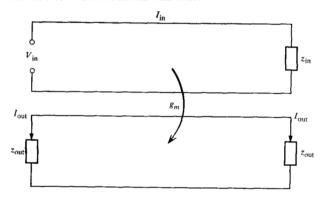

cation in a distributed FET. Figure 7 shows a simplified schematic plot of the distributed device. Source-to-gate and source-to-drain lines are supposed to have no losses. The source-to-gate line is terminated by an impedance  $z_{\rm in}$  and carries a current  $I_{\rm in} = V_{\rm in}/z_{\rm in}$ , if  $V_{\rm in}$  stands for the applied voltage. The source-to-drain line is terminated at both ends by an impedance  $z_{\rm out}$  and carries a current  $I_{\rm out} = g_{\rm m} \cdot V_{\rm in}$ .

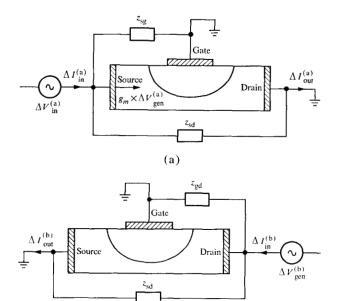

Figure 8 Equivalent network relating  $\Delta \mid _{in}^{(a,b)}$  and  $\Delta \mid _{out}^{(a,b)}$  to  $\Delta V_{gen}^{(a,b)}$ .

The conditions for current, voltage and power amplification, respectively, read:

$$\frac{I_{\text{out}}}{I_{\text{in}}} = \frac{g_{m}z_{\text{in}}}{2} > 1, \tag{20}$$

$$\frac{V_{\text{out}}}{V_{\text{in}}} = \frac{g_m z_{\text{out}}}{2} > 1, \tag{21}$$

$$\frac{(IV)_{\text{out}}}{(IV)_{\text{in}}} = \frac{g_m^2 z_{\text{in}} z_{\text{out}}}{4} > 1.$$

(22)

If for further simplicity  $z_{\rm in}=z_{\rm out}=z$ , Eqs. (20), (21) and (22) read simultaneously:

$$g_m > 2/z. (23)$$

Thus for  $z = 50\Omega$  we need a transconductance larger than  $g_m = 40 \text{ mA/V}$ .

Such high transconductance values may be achieved by means of a large capacity per unit length,  $C_0$ , which implies that the depleted layer has to be thin or that the transistor has to be wide enough. Unfortunately the width of the transistor is limited because the metal contacts, which are the conductors of the transmission line, are very thin, and the resistance of these conductors gives rise to attenuation. As a consequence, considerable dc losses occur in the transistor unless a sufficiently thin wafer plate has been chosen.

To be specific, we apply the gradual-case theory to the following data:  $L = 1\mu$ ,  $d = \frac{1}{3}\mu$ , b = 1 mm,  $N = 5 \times 1$

**Figure 9** "Vierpol parameter" of the field-effect transistor.  $g_m =$  transconductance;  $z_{sd} =$  source-to-drain impedance;  $z_{sg} =$  source-to-gate impedance;  $z_{gd} =$  gate-to-drain impedance.

(b)

$10^{16}/\mathrm{cm}^3$ ,  $\mu=500~\mathrm{cm}^2/\mathrm{Volt\cdot sec}^\dagger$ ,  $v_s=10^7~\mathrm{cm/sec}$ ,  $\epsilon\epsilon_0=10^{-12}~\mathrm{Coulomb/Volt\cdot cm}$ ,  $V_{sg}=0$ ,  $V_{sd}=1.4~\mathrm{Volt}$ . We then need to find a drain current  $I_{sd}=120~\mathrm{mA}$ , thus a dc power of  $P=170~\mathrm{mW}$ , and a transconductance  $g_m=64~\mathrm{mA/V}$ . The thickness of the depletion layer is zero at the source-directed end of the gate electrode, and  $1870~\mathrm{Å}$  at the drain-directed end of the gate, if we assume that no carrier accumulation takes place in the channel under the gate.

If, however, such thin depleted layers are required in order to achieve the transconductance value needed for distribution, one may question whether the assumption of a completely depleted barrier region is good enough. Although little experimental information referring to this aspect is available, it is encouraging. Silicon transistors have been prepared on layers as thin as 0.2 micrometer. The measured dc transconductance was comparable with that calculated for a completely depleted barrier region.

#### IV. Dynamics of FET's: transconductance, impedances between electrodes and their frequency dependence

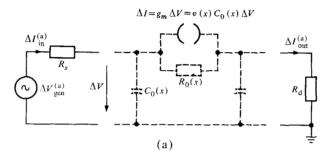

Let us apply a generating voltage  $\Delta V_{\rm gen}$  to either the source or drain electrode, while the other two electrodes (gate and either drain or source electrode) are kept at an ac "ground

potential."  $\Delta V_{\rm gen}$  will produce an input (either source or drain) current  $\Delta I_{\rm in}$  and an output (either drain or source) current  $\Delta I_{\rm out}$ , which can be calculated according to Figs. 8a and 8b, where currents and voltages corresponding to the two different cases are distinguished by an appropriate index letter "a" or "b". The reason for doing this calculation is that the FET's source-to-gate impedance,  $z_{\rm sg}$ , gate-to-drain impedance,  $z_{\rm gd}$ , source-to-drain impedance,  $z_{\rm sd}$ , and transconductance,  $g_{\rm m}$ , have a simple representation in terms of

$$\frac{\Delta I_{\text{in}}^{(a)}}{\Delta V_{\text{gen}}^{(a)}}, \frac{\Delta I_{\text{out}}^{(a)}}{\Delta V_{\text{gen}}^{(a)}}, \frac{\Delta I_{\text{in}}^{(b)}}{\Delta V_{\text{gen}}^{(b)}}, \frac{\Delta I_{\text{out}}^{(b)}}{\Delta V_{\text{gen}}^{(b)}}$$

In fact we may easily verify by means of Figs. 9a and 9b that:

$$\frac{\Delta I_{ia}^{(a)}}{\Delta V_{gen}^{(a)}} = g_m + \frac{1}{z_{sd}} + \frac{1}{z_{sg}}$$

$$\frac{\Delta I_{out}^{(a)}}{\Delta V_{gen}^{(a)}} = g_m + \frac{1}{z_{sd}}$$

(24)

$$\frac{\Delta I_{\text{in}}^{(b)}}{\Delta V_{\text{gen}}^{(b)}} = \frac{1}{z_{\text{sd}}}$$

$$\frac{\Delta I_{\text{out}}^{(b)}}{\Delta V_{\text{gen}}^{(b)}} = \frac{1}{z_{\text{sd}}} + \frac{1}{z_{\text{gd}}}.$$

(25)

We have numerically calculated  $z_{\rm sd}$ ,  $z_{\rm gd}$ ,  $z_{\rm sd}$  and  $g_m$  as a function of frequency, f, for Examples 2 and 3 listed in Table 1.

### • Example 1

The static information was obtained from the gradual case theory developed in Section III, which takes drift velocity saturation into account. The source-to-drain voltages  $V_{\rm sd}$  listed in Table 1 are the smallest required to achieve drain-current saturation with the prescribed source-to-gate voltage  $V_{\rm sg} = -1$  V. Note that these drain voltages depend on the ratio of gate electrode length to transistor thickness, which would not be true for the Shockley theory. The dynamic performance would not have been different, if a larger drain-voltage had been chosen.

Figure 10 shows the shape of the depleted regions. We recall that drift-velocity saturation is reached at the drain-directed end of the channel only, and that there is no "pinch-off" as would be according to the Shockley theory.

The 3-dB-point frequencies,  $f_{3 \text{ dB}}$ , with corresponding phase shifts,  $\phi_{3\text{dB}}$ , for  $g_{\text{vs}}$  are listed in Table 2. We have also listed for comparison the respective values appropriate to  $v_s \to \infty$  (Shockley theory) and  $V_{\text{sd}} \geq 3V$ , without going into details of the calculation.

Since an algebraic expression for the input data of the dynamic equation was used here, there should be no difference between the dynamically calculated low-

<sup>†</sup> This order of magnitude for N and  $\mu$  was measured by Th. Mohr of this laboratory in epitaxially grown Si layers as thin as 0.2 micrometer. Further, these numbers are compatible with data collected by Motorola.<sup>4</sup>

Table 1 Calculations for Examples 1, 2 and 3.

|                | Transistor geometry device width = $10^{-1}$ cm                                            |                               | Static operation point         |                            | Material data $\varepsilon \varepsilon_0 = 10^{-12} \frac{C}{V \cdot cm}$                                                                                                                       |                                                                                                              |  |

|----------------|--------------------------------------------------------------------------------------------|-------------------------------|--------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|

| Example<br>no. | Gate<br>length,<br>L                                                                       | Transistor<br>thickness,<br>d | $Drain \ voltage, \ V_{ m sd}$ | Gate voltage, $V_{\rm sg}$ | Free carrier conc. N = 5 × 10 <sup>15</sup> /cm <sup>3</sup> Drift velocity v Mobility μ                                                                                                        | Method for obtaining dc-information                                                                          |  |

| 1              | $3 \times 10^{-4} \text{ cm}$ $4 \times 10^{-4} \text{ cm}$ $10 \times 10^{-4} \text{ cm}$ | 10 <sup>-4</sup> cm           | 1.37 V<br>1.63 V<br>2.24 V     |                            | $\mu = 1250 \frac{\text{cm}}{\text{V} \cdot \text{sec}};$ $v_s = 9 \times 10^8 \text{ cm/sec}$ $v = \mu E \text{ for } v < v_s$ $v = v_s \text{ for } E \ge 7 \times 10^3 \text{ V/cm}$         | Gradual Case Theory<br>according to Sect. II<br>(incomplete pinch-off)                                       |  |

| 2              | 10-4 cm                                                                                    | 10 <sup>-4</sup> cm           | 1.8 V                          | -2 V                       | $\mu = 1250 \frac{\text{cm}^2}{\text{V} \cdot \text{sec}};$ $v_s = 9 \times 10^6 \text{ cm/sec}$ $v = \mu \cdot E \text{ for } v < v_s$ $v = v_s \text{ for } E \ge 7 \times 10^3 \text{ V/cm}$ | Analog model                                                                                                 |  |

| 3              | 10 <sup>-4</sup> cm                                                                        | 10 <sup>-4</sup> cm           | 13 V                           | -2 V                       | $\mu = 1250 \frac{\text{cm}^2}{\text{V} \cdot \text{sec}};$ $v_s = 9 \times 10^6 \text{ cm/sec}$ $v = \mu E \text{ for } v < v_s$ $v = v_s \text{ for } E \ge 7 \times 10^3 \text{ V/cm}$       | Analog model for un-<br>saturated channel<br>sections. Drift saturated<br>section treated as a<br>delay line |  |

Figure 10 Depleted regions for Example 1.

Table 2 Three-dB point frequencies, with phase shifts.

| L/d | f <sub>3</sub> dB<br>GHz  | φ₃ dB<br>Degrees | f <sub>3</sub> dB φ <sub>3</sub> dB<br>GHz Degrees |            |  |

|-----|---------------------------|------------------|----------------------------------------------------|------------|--|

|     | Drift velocity<br>limited |                  | Drift velocity<br>not limited                      |            |  |

| 3 4 | 18.0<br>11.5              |                  |                                                    | -80<br>-80 |  |

| 10  | 2.5                       | <b>–77</b>       | 19.0                                               | -80        |  |

frequency transconductance and the static value according to Eq. (15). This in fact is true, and is put into evidence in Table 3

For frequencies up to the 3-dB point,  $g_m$  may be presented by

$$\frac{g_{m(f)}}{g_{\pi(0)}} = \frac{e^{-j2\pi\nu\tau_1}}{1+j2\pi\nu\tau_0},$$

(26)

where the time constants  $\tau_1$  and  $\tau_2$  are to be taken from Table 4.

The frequencies  $f_{45}$  corresponding to a phase shift of 45° for  $z_{sg}$  are listed in Table 5 together, for comparison, with

the respective values appropriate to  $v_{\rm s} \to \infty$  (Shockley theory) and  $V_{\rm sd} \ge 3 {\rm V}$  (drain current saturation).

At low frequencies,  $z_{sg}$  is roughly

$$z_{sg(f)} = \frac{1}{2\pi t C} \tag{27}$$

where

$$C = \frac{\varepsilon \varepsilon_0 b}{d} \int_0^L \frac{dx}{1 - l(x)}$$

(28)

is the capacity of the depletion layer. In principle, it is not quite correct to calculate C as if no drain current were

Table 3 Calculations of low-frequency transconductance.

|                                                    |      | L/d  |      |  |

|----------------------------------------------------|------|------|------|--|

| $g_m$ according to:                                | 3    | 4    | 10   |  |

|                                                    | mA/V | mA/V | mA/V |  |

| Static Eq. (16) Dynamic equation $f \rightarrow 0$ | 10.0 | 8.8  | 4.5  |  |

|                                                    | 10.1 | 8.8  | 4.6  |  |

Table 4 Time constant.

| L/d | $	au_1$ in psec | $	au_2$ in psec | $	au_3$ in psec |

|-----|-----------------|-----------------|-----------------|

| 3   | 3.4             | 8.8             | 3.1             |

| 4   | 6.0             | 14.0            | 5.3             |

| 10  | 3.6             | 64.0            | 27.0            |

Table 5 Frequencies corresponding to 45° phase shift.

| L/d | f40                    | ° GHz                      |

|-----|------------------------|----------------------------|

|     | Drift velocity limited | Drift velocity not limited |

| 3   | 52.0                   | 60.0                       |

| 4   | 30.0                   | 34.0                       |

| 10  | 5.8                    | 5.3                        |

flowing, and therefore we need to find some discrepancy, which is put into evidence in Table 6.

For frequencies corresponding to phase shifts up to 45°,  $z_{\rm sg}$  may be approximated by

$$z_{ag(\nu)} = \frac{1}{2\pi f C} \frac{1}{1 + j \cdot 2\pi f \tau_3}, \qquad (29)$$

where the time constant  $\tau_3$  has to be taken from Table 4. The gain-bandwidth product  $f_0 = (1/2\pi)(g_m/C)$  is listed in Table 7, together for comparison with the corresponding values given by the Shockley theory. The data listed demonstrate the increasing importance of taking drift velocity saturation into account with decreasing L/d.

So far, the source resistance,  $R_s$ , was supposed to be zero.  $R_s$  has mainly the effect of increasing  $\tau_3$ .

We conclude by recalling that for all Examples 1, no longitudinal electric fields have been taken into account in the depletion layer. Although this gradual case approxi-

Table 6 Calculations for C allowing for drain current flow.

| L/d | $\left(\frac{1}{2\pi f z_{\rm sg}}\right)_{f\to 0}$ in pF | C in pF |  |

|-----|-----------------------------------------------------------|---------|--|

| 3   | 0.45                                                      | 0.49    |  |

| 4   | 0.57                                                      | 0.64    |  |

| 10  | 1.20                                                      | 1.50    |  |

**Table 7** Gain-bandwidth products compared with those from Shockley theory.

| L/d | fo                     | in GHz                     |

|-----|------------------------|----------------------------|

|     | Drift velocity limited | Drift velocity not limited |

| 3   | 3.2                    | 7.8                        |

| 4   | 2.2                    | 4.4                        |

| 10  | 0.5                    | 0.7                        |

Figure 11 Depletion layers for Examples 2 (—) and 3 (---). The drift-velocity saturated section is put into evidence by its space charge. ---- marks the neutral cross-section.

mation procedure is generally used, it might not be justified, even for  $L\gg d$ , in the neighborhood of the drain-directed end of the gate electrode. Therefore, emphasis will be placed on the succeeding examples to use a better static background in this region, and to point out the consequences on the dynamic performance of field-effect transistors.

#### • Examples 2 and 3

Examples 2 and 3 have been chosen so as to demonstrate the delay effects involved with an extended channel section where drift-velocity saturation is established. The static pictures for 2 and the assumed picture for 3 are plotted in Fig. 11. In Example 2, the source-to-drain voltage is so small that the carrier drift-velocity is everywhere below its saturation value except for the most narrow cross-section of the conducting channel; in Example 3 the drain voltage is so large that drift-velocity saturation is reached

Figure 12 Absolute value  $|z_{sg}|$  and phase  $\phi_{gd}$  of source-to-gate impedance for Examples 2 (—) and 3 (---).

in an appreciable section of the channel. The saturated part of the channel contains negative space charge at the source-directed end and positive charge at the drain-directed end. The positive charge extends into the region where  $v < v_{\rm s}$ . In our treatment, however, the space charge outside the drift-velocity saturated section was ignored.

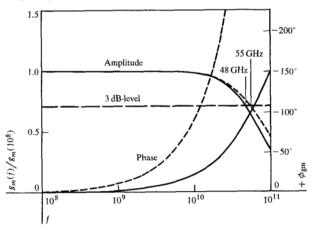

The frequency dependence of  $z_{sg}$ ,  $z_{gd}$  and  $g_m$  is plotted in Figs. 12, 13, and 14,  $(z_{sd} \rightarrow \infty)$  and the values of  $R_{sd}$ ,  $C_{sg}$ ,  $C_{gd}$  and  $g_m$  as determined from the respective zero-frequency impedances are listed in Table 8. The  $g_m$  values listed above compare well with those predicted earlier by the authors from a less-detailed discussion of drift-velocity saturation effects (Fig. 7 of Ref. 2).

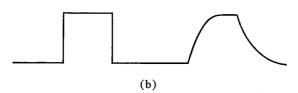

A striking result evident from Fig. 12 is that oscillations of  $z_{\rm sg}$  appear at frequency intervals of roughly  $f=5\times 10^{10}$  Hz for Example 3. The origin of these can be understood. Suppose that a voltage pulse (Fig. 15a) has been applied to the gate electrode. It will produce at the left end of the drift-velocity saturated channel (see Fig. 15b for a schematic plot) a charge pulse which propagates with velocity  $v_{\rm s}$ . After a time  $\tau=L_{\rm eff}/v_{\rm s}$  ( $L_{\rm eff}=$  effective length of saturated channel section) it will leave the channel at its right end. We may suggest that thereby a charge pulse of opposite sign is produced in order to bring the channel back to its originally neutral state. If we produce a new pulse at this moment and continue to do so at a rate of  $t=1/\tau$ , we ensure that no gate current is set up

Figure 13 Absolute value  $|z_{\rm gd}|$  and phase  $\phi_{\rm gd}$  of gate-to-drain impedance for Examples 2 (—) and 3 (---) versus frequency, f.

Figure 14 Absolute value  $|g_m|$  and phase  $\phi_{g_m}$  of transconductance for Examples 2 (—) and 3 (---) versus frequency.

**Table 8** Values of  $R_{\rm sd}$ ,  $C_{\rm sg}$ ,  $C_{\rm gd}$  and  $g_m$  determined from zero-frequency impedances.

| Example | $R_{ m sd}$ | $C_{ m sg}$ | $C_{ m gd}$ | $g_m$     |

|---------|-------------|-------------|-------------|-----------|

| 2       | 8           | 0.25 pF     |             | 11.5 mA/V |

| 3       | 80          | 0.49 pF     | 0.03 pr     | 12 mA/V   |

in the transistor, which means that the input impedance is infinitely large (losses have been neglected). Appropriate data are roughly  $L_{\rm eff}=2\times10^{-4}$  cm and  $v_{\rm s}=10^{7}$  cm/sec, which yield  $v_{\rm 0}=5\times10^{10}$  Hz, thus the right order of magnitude. In the frequency range below that for oscillator effects,  $z_{\rm sg}$  may be represented by

$$z_{sg(r)} = \frac{1}{2\pi f C_{sg}} \frac{1}{1 + j2\pi f \tau_3}.$$

(30)

The appropriate time constants  $\tau_3$  are listed in Table 9. Evidently there is a pronounced difference in favor of Example 2, on which we should like to comment.

The source-to-gate capacitance is larger for Example 3 than for Example 2 (Table 8). If the difference  $\Delta C_{\rm sg}$  is due to the capacitance associated with the saturated channel section of Example 3, it should be roughly  $\Delta C_{\rm sg} = C_{\rm 0r} \cdot L_{\rm eff}$ . Since we have  $C_{\rm 0r} = 10^{-9}$  F/cm and  $L_{\rm eff} = 2 \times 10^{-4}$  cm we need to find  $\Delta C_{\rm sg} = 0.2$  pF, which is the right order of magnitude. An increase in source-to-gate capacitance is unfavorable, because it gives rise, in connection with the source resistance  $R_{\rm s}$ , to additional phase shift between input voltage and current, and additional damping. This effect may be minimized either by reducing  $R_{\rm s}$  by means of technological tricks, or by choosing the smallest possible source-to-drain voltage required (for a given source-to-gate voltage) to achieve drift-current saturation.

The situation is just the reverse with respect to the gate-to-drain impedance  $z_{\rm gd}$  (see Table 8 and Fig. 13). The Miller capacitance  $C_{\rm gd}$  is smaller for Example 3 than for Example 2. The gate-to-drain impedance may be represented by

$$z_{\text{gd}(f)} = \frac{1}{2\pi f C_{\text{gd}}} \frac{1}{1 + j2\pi f \tau_4}$$

(31)

with time constant  $\tau_4$  as listed in Table 9. Thus Example 3 is dynamically more favorable than Example 2.

The transconductance,  $g_m$ , is represented below its 3 dB level by

$$\frac{g_{m(f)}}{g_{m(0)}} = \frac{e^{-i2\pi f \tau_1}}{1 + j2\pi f \tau_2},\tag{32}$$

where the relaxation times  $\tau_1$  and  $\tau_2$  are contained in Table 9. We see from Fig. 14, that for Example 2 the 3 dB point is located at 48 GHz with a corresponding phase shift of  $\approx 85^{\circ}$ ; for Example 3 corresponding data are 55 GHz and  $\approx 450^{\circ}$ . The difference in phase shifts must roughly be equal to the delay  $fL_{\rm eff}/v_s \times 360^{\circ}$  [see Eq. (8)] associated with the waves propagating along the saturated channel section in Example 3, and in fact we find good agreement for f=55 GHz,  $L_{\rm eff}=2\times 10^{-4}$  cm and  $v_s=10^{7}$  cm/sec. Pronounced delay effects may cause serious instability problems in a distributed device; therefore the cross-sectional elements in a distributed device

Figure 15 Applied source-to-gate voltage pulse a) and schematic plot of current pulse product b). Hatched area is the depleted region.

Table 9 Time constants for Examples 2 and 3, in psec.

| Example | $	au_1$ | $	au_2$ | $	au_3$ | τ4       |

|---------|---------|---------|---------|----------|

| 2       | 2.3     | 3.3     | 2.8     | 2.0      |

| 3       | 20.0    | 3.3 2.9 | 10.0    | 0.0      |

|         | 1       | l       |         | <u> </u> |

should be operated with the smallest possible source-todrain voltage required for a given source-to-gate voltage to obtain drift-current saturation.

If we remember that a saturated channel permits current propagation without attenuation, we may also understand why the 3-dB point of the transconductance is located at a higher frequency for Example 3 than for Example 2.

The gain bandwidth product  $f_0$  for amplification is not very much different for Examples 2 and 3; the average value becomes

$$f_0 = \frac{1}{2\pi} \frac{g_m}{C_{\rm sg} + C_{\rm gd}} \approx 4 \text{ GHz}.$$

(33)

This is a drastically smaller value than the 15 GHz attained with neglection of drift-velocity saturation.

The result for  $f_0$  obtained here completes Table 7 for the geometry L/d = 1. We recognize that  $f_0$  increases with decreasing L/d and saturates around  $L/d \approx 3$ .

91

Figure 16 a) Source-to-date channel of distributed FET, b) input signal and distortion of transmitted signal.

Figure 17 Gain-bandwidth product.

Figure 18 Saturated drain current.

Table 10 Relation between mobility and doping level.

| $\mu$ , $\frac{\text{cm}^2}{\text{V} \cdot \text{sec}}$ | 640                  | 520  | 350                | 290  | 160                  |

|---------------------------------------------------------|----------------------|------|--------------------|------|----------------------|

| N, cm <sup>-3</sup>                                     | 5 × 10 <sup>16</sup> | 1017 | $5 \times 10^{17}$ | 1018 | 5 × 10 <sup>18</sup> |

The  $g_m/C$  ratio is certainly a "figure of merit" for the lumped device. We want to point out that, in addition, it also becomes figure of merit for the distributed device, provided that the cross-sectional element has a conducting channel which consists predominantly of the drift-velocity saturated section, so that:

$$g_m \approx C_{0_{\rm r}} \cdot v_{\rm s}$$

(34)

and

$$C_{\rm sg} \approx C \approx C_{\rm 0r} L.$$

(35)

In order to develop the argument, let us recall that the basic idea of distribution is to get rid of the frequency-limiting effects due to capacitance in a lumped device by connecting a large number of lumped devices in parallel, with inductive coupling elements in between (Fig. 16b). The parameter  $C_*$  then becomes a cross-sectional element in an LC-transmission line (the source-to-gate channel), on which signals can be transmitted without distortion up to the highest frequencies, if losses are neglected.

An implicit assumption made in this argument is that a cross-sectional element has a source-to-gate impedance which is a capacitance up to the highest frequencies used for transmission. But it is clear that at frequencies  $f\gg 1/2\pi\tau$ , where  $\tau$  stands for the flight-time of the free carriers along the gate, this is no longer the case: at these frequencies, the time needed to charge or discharge the depleted region becomes so large that signals propagating along the source-to-gate channel become distorted (Fig. 16a), so that distribution no longer presents the expected advantage. If we calculate  $f_0$  by means of Eqs. (34) and (35), it turns out that the upper frequency limit for undistorted transmission on the source-to-gate channel of a distributed device is equal to the frequency limit for amplification with subsequent stages of a lumped device:

$$f_0 = \frac{1}{2\pi} = \frac{g_m}{C} = \frac{1}{2\pi} \frac{L}{v_s} = \frac{1}{2\pi\tau}.$$

(36)

In this consideration the parasitic capacitances and the capacitances at both edges of the gate have not been taken into account. These capacitances can be compensated for, and therefore the upper limit for undistorted transmission will be higher than the gain bandwidth product  $f_0$ .

Figure 19 Minimum drain voltage for current saturation.

Figure 21 Highest gate-to-channel voltage.

Figure 22 Transconductance.

#### V. Discussion of results

The frequency limit for a given FET in a circuit depends on the way in which the transistor is being used. In wideband lumped devices the gain-bandwidth product

$$f_0 = \frac{g_m}{2\pi C}$$

is certainly a "figure of merit." We find within the framework of the present study that  $f_0 \approx 10$  GHz can be obtained with Si Schottky-barrier FET's. The transistors have to be made from highly doped material (free carrier concentration  $N \approx 10^{17}/\mathrm{cm}^3$  or higher, until electric breakdown at the gate junction sets an upper limit) with a gate length of 1  $\mu$ m (and equal distances to source and drain). In addition they have to be thin, no thicker than a few tenths of a  $\mu$ m, in order to keep the dc losses within tolerable limits.  $f_0$  should rise to the 30 GHz range if GaAs is used instead of Si, due to the larger saturation drift velocity in the former material, if not, instabilities cause disturbing effects.

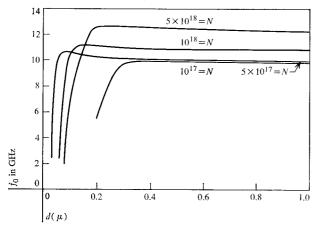

The value  $f_0$  for silicon FET's is displayed in Fig. 17 as a function of transistor thickness, d, and for various carrier concentrations, N. The plots refer to b=1 mm, L=1  $\mu$ m (distances to source and drain are equal),  $V_{sg}=-2V$ ,  $R_{sg}=0$  and a mobility versus doping level relationship as listed in Table 10.

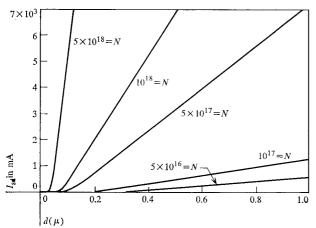

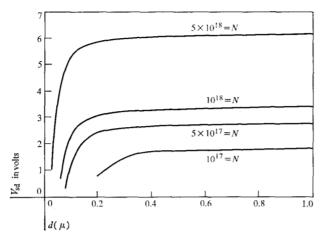

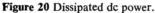

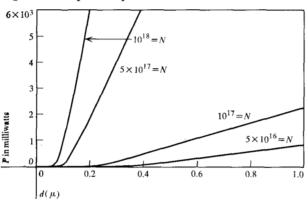

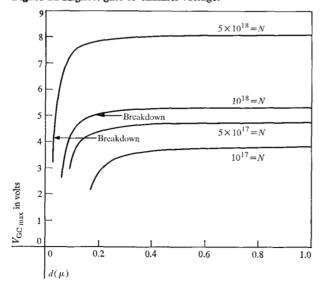

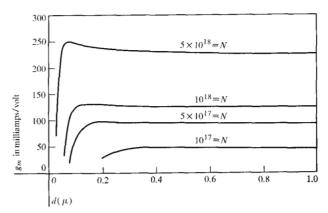

Some additional data: the saturated drain current,  $I_{\rm sd}$ , and the smallest source-to-drain voltage,  $V_{\rm sd}$ , needed for current saturation are depicted in Figs. 18 and 19. For the so-defined operating points we then plotted the dissipated dc power, P (Fig. 20), the highest gate-to-channel voltage,  $V_{\rm gemax}$  (Fig. 21), and the transconductance  $g_m$  (Fig. 22).

$$f_{\text{max}} = \frac{f_0}{2} \sqrt{\frac{R_{\text{sd}}}{R_{\text{eg}}}},$$

(37)

which is the highest frequency for power gain with matched input and output, is the appropriate "figure of merit." Here  $R_{\rm sd}$  and  $R_{\rm sg}$  stand for source-to-drain resistance and source-to-gate resistance (including the resistance along the gate contact), respectively.

<sup>†</sup> If FET's are used in a distributed device, such as for example, in a chain amplifier, then

Figure 23 Optimized transconductance as a function of gate width.

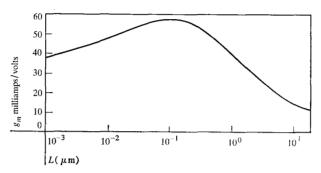

Figure 23 shows finally how the highest achievable transconductance (optimized by choosing the transistor thickness appropriately at a constant doping level  $N=0.8\times 10^{17}/\mathrm{cm}^3$  and a gate voltage  $V_{\mathrm{sg}}=I_{\mathrm{sd}}\cdot R_{\mathrm{sg}}+V_{\mathrm{d}}$ , where  $V_{\mathrm{d}}$  denotes a diffusion voltage  $V_{\mathrm{d}}=0.5$  V) depends on the size of the transistor structure. The transconductance would admit a maximum value for a gate length

equal to some tenths of a micrometer, which cannot be realized for technological reasons at present. However, since the maximum is flat, a one-micrometer structure comes quite close to the best conditions.

# VI. Acknowledgments

The programming and computing work was carried out by H. Keller. His contribution is gratefully acknowledged. We should also like to thank Prof. G. Kohn, who first initiated the idea of a Schottky-barrier FET in our laboratory.

#### References

- 1. W. Shockley, Proc. IRE 40, 1365 (1952).

- K. E. Drangeid and R. Sommerhalder, Helv. Phys. Acta 41, 766 (1968).

- H. Salow et al., Der Transistor, Springer-Verlag, 1963, p. 395.

- 4. Motorola, Integrated Circuit Design, 1964.

- D. P. Kennedy and R. R. O'Brien, IBM J. Res. Develop., 14, 95 (1970, this issue).

Received September 25, 1969