# Assembler POS-III

### Reference Manual

# Assembler For HP 2000 Computers

Reference Manual

HEWLETT-PACKARD COMPANY

11000 WOLFE ROAD, CUPERTINO, CALIFORNIA, 95014

# LIST OF EFFECTIVE PAGES

| Pages       | Effective Date |

|-------------|----------------|

| Title       | July 1974      |

| ii to v     | July 1974      |

| 1-1 to 1-3  | July 1974      |

| 2-1 to 2-7  | July 1974      |

| 3-1 to 3-10 | July 1974      |

| 4-1 to 4-18 | July 1974      |

| A-1 to A-3  | -              |

| B-1 to B-8  | July 1974      |

| C-1 to C-2  | •              |

| D-1 to D-3  | July 1974      |

| E-1 to E-2  | July 1974      |

| I-1 to I-3  | •              |

This manual describes the Assembler which is designed to operate under control of the HP 24307B DOS-III Disc Operating System. The Assembler permits the programmer to use all supported machine instructions for the HP 21MX Computer.

It is assumed that object programs produced by the Assembler will be executed on an HP 21MX Computer. However, the object program may be executed on other HP 2100-Series computers (2114, 2115, 2116, or 2100) if the following machine and pseudo instructions are not used:

- Word Processing (described in paragraph 3-5)

- Byte Processing (paragraph 3-6)

- Bit Processing (paragraph 3-7)

- Index Register Group (paragraph 3-11)

- DBL and DBR: Define Left Byte and Define Right Byte (paragraph 4-3)

- BYT: Define Octal Byte Constants (paragraph 4-4)

- MIC: Define User Instruction (paragraphs 4-8 through 4-14)

It is assumed that object programs produced by the Assembler will be loaded and executed under control of the HP 24307B DOS-III Disc Operating System. However, the object program may be loaded and executed under control of some other operating system with the following restrictions:

- ENT pseudo instructions with absolute or common symbols as operands must not be used.

- I/O select codes must not be defined via the ENT pseudo instruction.

- The DBL (Define Left Byte) and DBR (Define Right Byte) pseudo instructions must not be used.

When assembling programs to be run under control of the Basic Control System (BCS), the following restrictions also apply:

- Absolute operands greater than 77<sub>8</sub> are illegal in relocatable programs. However, such usage will not be diagnosed as errors by the loader; it will instead result in errors during execution of the object program.

- The ORB (Reset Base Page Origin) pseudo instruction is not available.

This manual is arranged in four sections with six appendices. Section I discusses the assembly process in general, program relocation, assembly options, and assembler input and output. Section II describes the source statement format. Section III describes all of the available machine instructions. Section IV describes all of the available assembler pseudo instructions. Appendix A describes the Hewlett-Packard character set. Appendix B summarizes all of the available machine and pseudo instructions (including instruction formats), arranged by instruction type. Appendix C presents a one-sentence definition of all available machine and pseudo instructions, arranged alphabetically by mnemonic. Appendix D presents a tabular summary of the binary format of all available machine instructions. Appendix E describes how to run an assembly under DOS-III. Appendix F describes all of the assembler error messages. For the programmer's convenience, a table of the powers of two is contained on the inside back cover.

### **CONTENTS**

| Section I Pag INTRODUCING THE ASSEMBLER   | ge Section IV Page PSEUDO INSTRUCTIONS |

|-------------------------------------------|----------------------------------------|

| Assembly Processing                       |                                        |

| Symbolic Addressing                       |                                        |

| Program Relocation                        |                                        |

| Program Location Counter                  |                                        |

| Assembly Options                          |                                        |

| Source Program                            |                                        |

| Binary Output                             |                                        |

| List Output                               |                                        |

| List Output                               | "Jump to Microprogram"4-17             |

|                                           | Example 4-17                           |

| Section II Pag                            |                                        |

| Section II Pag<br>SOURCE STATEMENT FORMAT | Example4-17                            |

| Statement Characteristics                 |                                        |

|                                           |                                        |

| Field Delimiters                          | <del>-</del>                           |

| Character Set                             |                                        |

| Statement Length                          |                                        |

| Label Field                               |                                        |

| Label Symbol                              |                                        |

| Asterisk                                  |                                        |

| Opcode Field                              |                                        |

| Operand Field                             |                                        |

| Symbolic Terms                            | 11ppchaix 11                           |

| Numeric Terms                             |                                        |

| Asterisk2                                 |                                        |

| Expression Operators                      |                                        |

| Evaluation of Expressions2                | -5                                     |

| Expression Terms                          |                                        |

| Absolute and Relocatable Expressions 2    |                                        |

| Absolute Expressions2                     | 5 SUMMARY OF INSTRUCTIONS              |

| Relocatable Expressions                   |                                        |

| Literals                                  | -6 Memory Reference                    |

| Indirect Addressing                       | -6 Jump and Increment-Skip             |

| Clear Flag Indicator2                     | -7 Add. Load, and Store                |

| Comments Field2                           | -7 LogicalB-2                          |

|                                           | Word ProcessingB-2                     |

|                                           | Byte ProcessingB-3                     |

| Section III Pag                           |                                        |

| MACHINE INSTRUCTIONS                      | Register ReferenceB-3                  |

| Memory Reference                          |                                        |

| Jump and Increment-Skip                   |                                        |

| Add, Load, and Store                      |                                        |

| Logical Operations                        |                                        |

| Word Processing (21MX only)               |                                        |

| Byte Processing (21MX only)               |                                        |

| Bit Processing (21MX only)                |                                        |

| Register Reference                        |                                        |

| Shift-Rotate Group                        |                                        |

| Alter-Skip Group                          |                                        |

| Index Register Group (21MX only)          |                                        |

| No-Operation Instruction                  |                                        |

| Input/Output, Overflow, and Halt          |                                        |

| Input/Output                              |                                        |

| Overflow                                  |                                        |

| Halt3                                     |                                        |

| Extended Arithmetic Unit (EAU)            |                                        |

| Floating Point 3-                         |                                        |

| 1 Manuel Mill                             | Dellie Obel Indu ucuvii                |

# **CONTENTS** (continued)

| Appendix C ALPHABETIC LIST OF INSTRUCTIONS | Page       | Appendix E RUNNING ASSEMBLIES UNDER DOS-III | Page |

|--------------------------------------------|------------|---------------------------------------------|------|

|                                            |            | Assembler I/O                               |      |

|                                            |            | Assembler Operation                         |      |

|                                            |            |                                             |      |

| Appendix D                                 | Page       | Appendix F                                  | Page |

| CONSOLIDATED CODING SHEETS                 | <b>D-1</b> | ASSSEMBLER ERROR MESSAGES                   | F-1  |

## **ILLUSTRATIONS**

| Title Pag                                   | ge  | Title                                     | Page |

|---------------------------------------------|-----|-------------------------------------------|------|

| Sample Labels                               | 2-2 | Example of Correct Address Modification   | 4-8  |

| Label Usage Examples                        |     | Loader-Assigned Locations for Figure 4-10 | 4-8  |

| Symbolic Term Examples                      |     | ABS Examples                              |      |

| Expression Operator Examples                |     | EQU Example                               |      |

| Indirect Addressing Example                 |     | EQU Examples                              |      |

| Clear Flag Examples                         |     | ASC Example                               |      |

| ORR Example (with Single ORG)4              |     | DEC Examples (Integer)                    |      |

| ORR Example (with Multiple ORGs)4           |     | DEC Examples (Floating Point)             |      |

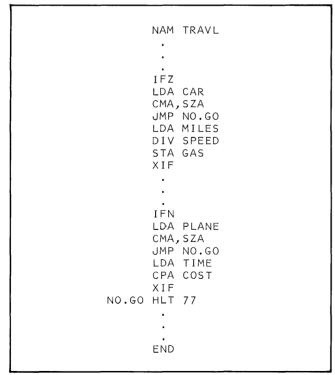

| IFN/XIF and IFZ/XIF Example                 |     | DEC Examples (Floating Point)             |      |

| IFZ/XIF Example4                            |     | DEX Memory Format                         |      |

| COM Examples                                |     | DEX Examples                              |      |

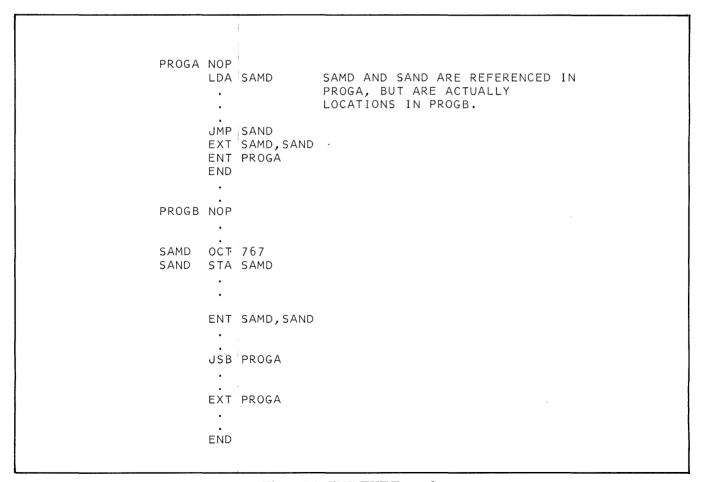

| ENT/EXT Examples4                           |     | OCT Examples                              |      |

| DEF Examples4                               |     | BYT Examples                              |      |

| Example of Incorrect Address Modification 4 |     | ASCII Characters and Binary Codes         |      |

| Loader-Assigned Locations for Figure 4-8    |     |                                           |      |

### **TABLES**

| Title                         | Page         | Title                                      | Page |

|-------------------------------|--------------|--------------------------------------------|------|

| Control Statement Parameters  | . 1-3        | Base Set Instruction Codes in Binary       |      |

| Legend for Figure A-1         | . <b>A-2</b> | Extended Instruction Group Codes in Binary | D-3  |

| HP 7970R RCD-ASCII Conversion | Δ-3          |                                            |      |

INTRODUCING THE ASSEMBLER

The Assembler translates symbolic source language instructions into an object program for execution on the computer. The source language provides mnemonic machine operation codes, assembler-directing pseudo instructions, and symbolic addressing. The assembled program may be absolute or relocatable.

The source program may be assembled as a complete entity or it may be subdivided into several relocatable subprograms (or a main program and several subroutines), each of which may be assembled separately. When relocatable object programs and subprograms are subsequently executed, they are loaded and linked to one another by the relocating loader; absolute object programs are loaded by the Basic Binary Loader or the Basic Binary Disc Loader.

The Assembler can read the source input from paper tape, punched cards, magnetic tape, or from a DOS-III file (or files) in the User Area of the disc. The Assembler outputs the resultant object program on the standard punch output device and/or to the Job Binary Area of the disc in a format acceptable to the DOS-III Relocating Loader.

#### 1-1. ASSEMBLY PROCESSING

The Assembler is a two pass system. A pass is defined as a processing cycle of the source program input.

In the first pass, the Assembler creates a symbol table from the names used in the source statements and (if requested) prints a symbol table listing on the standard list output device. It also checks for certain possible error conditions and prints error messages on the console device if necessary.

During pass two, the Assembler again examines each statement in the source program along with the symbol table and produces the binary object program. It outputs the object program to the standard punch output device and/or to the Job Binary Area of the disc. If requested, the Assembler also prints the object program listing on the standard list output device. Additional error messages may also be printed on the console device.

Note: If only one output device is available, and if both the punch output and list output are requested, the listing function is deferred and performed as a third pass.

If the source input is being read from a non-disc device, it is written on the disc at the start of pass 1; for pass 2, the source is then read from the disc. However, if there is not sufficient space available on the disc to do this, the source input will have to be read through the non-disc device at the start of pass 2. In such a case, the Assembler prints \$END ASMB PASS on the console device at the end of pass 1. The operator responds by reloading the source input into the non-disc device and then entering :GO through the console device.

#### 1-2. SYMBOLIC ADDRESSING

Symbols may be used for referring to machine instructions, data, constants, and certain other pseudo operations. A symbol represents the address for a computer word in memory. A symbol is defined when it is used as a label for a location in the program, a name of a common storage segment, the label of a data storage area or constant, the label of an absolute or relocatable value, or a location external to the program.

Through use of simple arithmetic operators, symbols may be combined with other symbols or numbers to form an expression which may identify a location other than that specifically named by a symbol. Symbols appearing in operand expressions, but not specifically defined, and symbols that are defined more than once are considered to be in error by the Assembler.

#### 1-3. PROGRAM RELOCATION

Relocatable programs are relocated in core by the relocating loader; the location of the program origin and all subsequent instructions is determined at the time the program is loaded.

A relocatable program is assembled assuming a starting location of zero. All other instructions and data areas are assembled relative to this zero base. When the program is loaded, the relocatable operands are adjusted to correspond with the actual locations assigned by the loader.

The starting location of the common storage area is always established by the loader. References to the common area are common relocatable. If a program refers to the common area, the program must be relocatable.

If a program is to be relocatable, all subprograms comprising the program must be relocatable; all memory reference operands must be relocatable expressions or literals, or have an absolute value of less than  $2000_8$ .

#### PROGRAM LOCATION 1-4. **COUNTER**

The Assembler maintains a counter, called the program location conter, that assigns consecutive memory addresses to source statements.

The initial value of the program location counter is established according to the use of either the NAM or ORG pseudo operation at the start of the program. The NAM operation causes the program location counter to be set to zero for a relocatable program; the ORG operation specifies the absolute starting location for an absolute program.

#### 1-5. ASSEMBLY OPTIONS

The control statement must be the first statement in the source program and it specifies the desired assembly options:

$$ASMB, p_1, p_2, \dots, p_n$$

"ASMB," is in positions 1-5 of the statement. Following the comma are one or more parameters, in any order. The parameters are shown in Table 1-1. If output to the Job Binary Area is specified in the :PROG, ASMB directive (:PROG,ASMB, . . . ,99), the control statement may contain no parameters. This is the only instance in which the control statement may contain no parameters.

Since they contradict one another, F and X must never appear in the control statement for the same source program. If neither A nor R is specified, R is assumed. If T is omitted, the symbol table listing will not be printed. If B is omitted, the object program will not be outputted to the standard punch output device (it may, however, be outputted to the Job Binary Area of the disc if so specified in the :PROG,ASMB DOS-III directive).

The control statement can be altered at assembly time through the system console device. To do so, add 10010 to the input logical unit number in the :PROG,ASMB directive. In such a case, the Assembler responds by printing the following on the system console device:

#### ENTER NEW CONTROL STATEMENT

The user then enters the desired control statement through the system console device. The new control statement overrides the one contained in the source input. During Pass 1, the Assembler prints "CONSOLE!" followed by the new control statement on the list device. The change does not appear in the source program listing.

#### 1-6. **SOURCE PROGRAM**

Following the control statement, the first statement of the program (other than remarks or a HED statement) must be a NAM statement for a relocatable program or an ORG statement for indicating the origin of an absolute program. The last statement must be an END statement and may contain a transfer address for the start of a relocatable program. Each statement is terminated by an end-ofstatement or end-of-record mark if not on cards.

#### 1-7. **BINARY OUTPUT**

The binary output is defined by the ASMB control statement. The binary output includes the instructions translated from the source program. It does not include system subroutines referenced within the source program (arithmetic subroutine calls, .IOC., .DIO., .ENTR, etc.)

#### 1-8. LIST OUTPUT

Fields of the object program are listed in the following print columns:

| Columns | Content                                                     |

|---------|-------------------------------------------------------------|

| 1-4     | Source statement sequence number generated by the Assembler |

| 5-6     | Blank                                                       |

| 7-11    | Location (octal)                                            |

| 12      | Blank                                                       |

| 13-18   | Object code word in octal                                   |

| 19      | Relocation or external symbol indicator                     |

| 20      | Blank                                                       |

| 21-72   | First 52 characters of source statement                     |

|         |                                                             |

Lines consisting entirely of comments (i.e., \* in column 1) are printed as follows:

| Columns | Content                          |  |  |

|---------|----------------------------------|--|--|

| 1-4     | Source statement sequence number |  |  |

| 5-72    | Up to 68 characters of comments  |  |  |

The Symbol Table listing at the end of Pass 1 has the following format:

| Columns | Content                                 |  |

|---------|-----------------------------------------|--|

| 1-5     | Symbol                                  |  |

| 6       | Blank                                   |  |

| 7       | Relocation of external symbol indicator |  |

| 8       | Blank                                   |  |

| 9-14    | Value of the symbol                     |  |

Table 1-1. Control Statement Parameters

| PARAMETER | MEANING                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| А         | Absolute assembly. The addresses generated by the Assembler are to be interpreted as absolute locations in memory. The program is a complete entity; external symbols, common storage references, and entry points are not permitted. Note that an absolute object program cannot be executed under DOS-III.                                                                                                                                    |  |

| R         | Relocatable assembly. The object program may be loaded anywhere in memory. All operands which refer to memory locations are automatically adjusted as the program is loaded. Operands referring to memory locations greater than 17778 must be relocatable expressions. Programs may contain external symbols and entry points, and may refer to common storage.                                                                                |  |

| В         | Binary output. An absolute or relocatable object program is to be outputted to the standard punch device.                                                                                                                                                                                                                                                                                                                                       |  |

| L         | List output. A program listing is to be printed on the standard list device.                                                                                                                                                                                                                                                                                                                                                                    |  |

| Т         | Symbol table print. A listing of the symbol table is to be printed on the standard list output device.                                                                                                                                                                                                                                                                                                                                          |  |

| N,Z       | Selective assembly. Sections of the program are to be included or excluded at assembly time depending upon the option specified. See the descriptions of the IFN and IFZ pseudo instructions in Section IV of this manual.                                                                                                                                                                                                                      |  |

| С         | Cross reference table print. All references to statement labels, external symbols, and user-defined opcodes are to be listed on the standard list output device after the end of the assembly.                                                                                                                                                                                                                                                  |  |

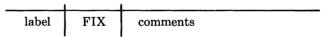

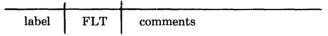

| F         | Floating point instructions. The floating point machine instructions are to be used instead of the software simulation routines for the following floating point operations: FIX, FLT, FDV, FMP, FAD, and FSB.                                                                                                                                                                                                                                  |  |

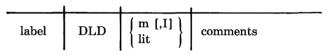

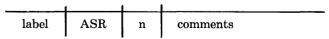

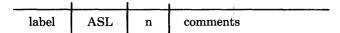

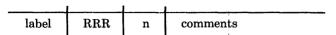

| Χ .       | No EAU hardware. Signifies that the object program will be executed on a machine which does <b>not</b> have the Extended Arithmetic Unit (EAU) hardware. This parameter prevents the use of the following EAU instructions: ASR, ASL, RRR, RRL, LSR, LSL, and SWP. In addition, it causes all occurrences of the MPY, DIV, DLD, and DST instructions to be substituted with a call to the appropriate subroutine in the floating point library. |  |

The characters that designate an external symbol or type of relocation for the Operand field or the symbol are as follows:

| Relocation Base     |

|---------------------|

| Absolute            |

| Program relocatable |

| Common relocatable  |

| External symbol     |

|                     |

At the end of each pass, the following is printed on both the console and list device:

The value nnnn indicates the number of errors.

If there are errors, the message PG xxx is printed on the list device immediately preceding the \*\*nnnn ERRORS\* message, where xxx is the page number where the final error was detected. The same message appears in the listing following each error and it points to the page number where the previous error was detected. The backwards pointer following the first error in the program is PG 000.

A source language statement consists of a label, an operation code, an operand (or operands) and comments. The label is used when needed as a reference by other statements. The operation code may be a mnemonic machine operation or an assembly directing pseudo code. An operand may be an expression consisting of an alphanumeric symbol, a number, a special character, or any of these combined by arithmetic operators. An operand may also be a literal. Indicators may be appended to an operand to specify certain functions such as indirect addressing. The comments portion of the statement is optional.

#### 2-1. STATEMENT CHARACTERISTICS

The fields of the source statement appear in the following order:

- 1. Label

- 2. Opcode

- 3. Operands

- 4. Comments

#### 2-2. FIELD DELIMITERS

One or more spaces separate the fields of a statement. An end-of-statement or end-of-record mark terminates the statement. On paper tape this mark is a return, CR, and line feed, LF.† A single space as the first character of a source statement is the null indicator for the label field.

#### 2-3. CHARACTER SET

The characters that may appear in a statement are as follows:

- A through Z

- 0 through 9

- . (period)

- \* (asterisk)

- + (plus)

- (minus)

- , (comma)

- = (equals)

- () (parentheses) (space)

Any other ASCII characters may appear in the Comments field. (See Appendix A.)

The letters A through Z, the numbers 0 through 9, and the period may be used in an alphanumeric symbol. In the first position in the Label field, an asterisk indicates a comment; in the Operand field, it represents the value of the program location counter for the current instruction. The plus and minus are used as operators in arithmetic address expressions. The comma separates several operation codes, or an expression and an indicator in the Operand field. An equals sign indicates a literal value. The parentheses are used only in the COM pseudo instruction.

Spaces separate fields of a statement and operands in a multi-operand field. They may also be used to enhance the appearance of the listing. Within a field they may be used freely when following +, -,  $\cdot$ , or (.

#### 2-4. STATEMENT LENGTH

A statement may contain up to 80 characters including blanks, but excluding the end-of-statement mark. Fields beginning in columns 73—80 are not processed by the Assembler.

#### 2-5. LABEL FIELD

The Label field identifies the statement and may be used as a reference point by other statements in the program.

The field starts in position one of the statement. It is terminated by space. A space in position one is the null field indicator for the label field; the statement is unlabeled.

#### 2-6. LABEL SYMBOL

A label may have one to five characters consisting of A through Z, 0 through 9, and the period.

Note: The Assembler allows the use of certain other characters in the Label field. However, they are reserved for use in Hewlett-Packard programs.

| LDA    | NO LABEL                         |

|--------|----------------------------------|

| .ABCD  | VALID LABEL                      |

| .1234  | VALID LABEL                      |

| A.123  | VALID LABEL                      |

|        | VALID LABEL                      |

| 1.AB   | ILLEGAL LABEL - FIRST CHARACTER  |

|        | NUMERIC.                         |

| ABC123 | ILLEGAL LABEL - TRUNCATED TO     |

|        | ABC12.                           |

| A*BC   | ILLEGAL LABEL - ASTERISK NOT     |

|        | ALLOWED IN LABEL.                |

| ABC    | NO LABEL -THE ASSEMBLER ATTEMPTS |

|        | TO INTERPRET ABC AS AN OPERATION |

|        | CODE.                            |

|        |                                  |

|        |                                  |

|        | <b>!</b>                         |

Figure 2-1. Sample Labels

```

COM ACOM(20), BC(30), ABC

EQU 160

VALID LABEL

LB

ENT ABC

EXT XL1,XL2

START LDA LB

VALID LABEL

VALID LABEL

N25

XL2

ILLEGAL LABEL - USED IN EXT.

ВС

ILLEGAL LABEL - USED IN COM.

N25

ILLEGAL LABEL - PREVIOUSLY

DEFINED.

ABC

VALID LABEL

```

Figure 2-2. Label Usage Examples

| LDA A1234  | VALID IF DEFINED                           |

|------------|--------------------------------------------|

| ADA B.1    | VALID IF DEFINED                           |

| JMP ENTRY  | VALID IF DEFINED                           |

| STA 1ABC   | ILLEGAL OPERAND FIRST CHARACTER NUMERIC.   |

| STB ABCDEF | ILLEGAL OPERAND MORE THAN FIVE CHARACTERS. |

|            |                                            |

Figure 2-3. Symbolic Term Examples

The first character must be alphabetic or a period. A label of more than five characters could be entered on the source statement, but the Assembler flags this condition as an error and truncates the label from the right to five characters. Some examples are shown in Figure 2-1.

Each label must be unique within the program; two or more statements may not have the same symbolic name. Names which appear in the Operand field of an EXT or COM pseudo instruction may not also be used as statement labels in the same subprogram. However, names appearing in a COM pseudo instruction may be defined as entry points in an ENT pseudo instruction. Some examples are shown in Figure 2-2.

#### 2-7. ASTERISK

An asterisk in position one indicates that the entire statement is a comment. Positions 2 through 80 are available; however, positions 1 through 68 only are printed as part of the assembly listing. An asterisk within a label is illegal in any position.

#### 2-8. OPCODE FIELD

The operation code defines an operation to be performed by the computer or the Assembler. The Opcode field follows the Label field and is separated from it by at least one space. If there is no label, the operation code may begin anywhere after position one. The Opcode field is terminated by a space immediately following an operation code. Operation codes are organized in the following categories:

Machine operation codes:

- Memory Reference

- Register Reference

- Input/Output, Overflow, and Halt

- Extended Arithmetic Unit

Pseudo operation codes:

- Assembler control

- Object program linkage

- Address and symbol definition

- Constant definition

- Storage allocation

- Arithmetic subroutine calls

- Assembly Listing Control

- Define User Opcodes

Operation codes are discussed in detail in Sections III and IV.

#### 2-9. OPERAND FIELD

The meaning and format of the Operand field depend on the type of operation code used in the source statement. The field follows the Opcode field and is separated from it by at least one space. It is terminated by a space except when the space follows , +-( or, if there are no comments, by an end-of-statement mark. If more than one operand is required, they are separated from one another by at least one space.

The Operand field may contain an expression consisting of one of the following:

- Single symbolic term

- Single numeric term

- Asterisk

- Combination of symbolic terms, numeric terms, and the asterisk joined by the arithmetic operators + and -.

An expression may be followed by a comma and an indicator.

Programs may also contain a literal value in the Operand field.

#### 2-10. SYMBOLIC TERMS

A symbolic term may be one to five characters consisting of A through Z, 0 through 9, and the period. The first character must be alphabetic or a period. Some examples are shown in Figure 2-3.

A symbol used in the Operand field must be a symbol that is defined elsewhere in the program in one of the following ways:

- As a label in the Label field of a machine operation or a user-defined instruction

- As a label in the Label field of a BSS, ASC, DEC, DEX, OCT, DEF, BYT, ABS, EQU, DBL, DBR or REP pseudo operation

- As a name in the Operand field of a COM or EXT pseudo operation

- As a label in the Label field of an arithmetic subroutine pseudo operation

The value of a symbol is absolute or relocatable depending on the assembly option selected by the user. The Assembler assigns a value to a symbol as it appears in one of the above fields of a statement. If a program is to be loaded in absolute form, the values assigned by the Assembler remain fixed. If the program is to be relocated, the actual value of a symbol is established on loading. A symbol may be assigned an absolute value through use of the EQU pseudo instruction.

A symbolic term may be preceded by a plus or minus sign. If preceded by a plus or no sign, the symbol refers to its associated value. If preceded by a minus sign, the symbol refers to the two's complement of its associated value. A single negative symbolic operand may be used only with the ABS pseudo operation.

#### 2-11. NUMERIC TERMS

A numeric term may be decimal or octal. A decimal number is represented by one to five digits within the range 0 to 32767. An octal number is represented by one to six octal digits followed by the letter B; (0 to 177777B).

If a numeric term is preceded by a plus or no sign, the binary equivalent of the number is used in the object code. If preceded by a minus sign, the two's complement of the binary equivalent is used. A negative numeric operand may be used only with the DEX, DEC, OCT, BYT and ABS pseudo operations.

In an absolute program, the maximum value of a numeric operand depends on the type of machine or pseudo instruction. In a relocatable program, the value of a numeric operand may not exceed 1777<sub>8</sub>. Numeric operands are absolute. Their value is not altered by the assembler or the loader.

#### 2-12. ASTERISK

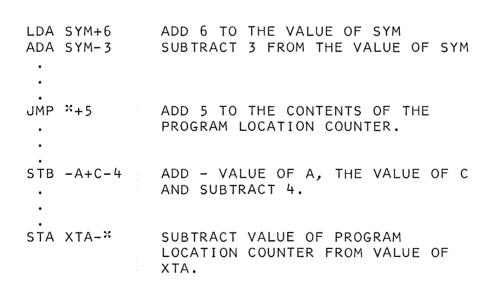

An asterisk in the Operand field refers to the value in the program location counter at the time the source program statement is encountered. The asterisk is considered a relocatable term in a relocatable program.

#### 2-13. EXPRESSION OPERATORS

The asterisk, symbols, and numbers may be joined by the arithmetic operators + and - to form arithmetic address expressions. The Assembler evaluates an expression and produces an absolute or relocatable value in the object code. Some examples are shown in Figure 2-4.

Figure 2-4. Expression Operator Examples

#### 2-14. EVALUATION OF EXPRESSIONS

An expression consisting of a single operand has the value of that operand. An expression consisting of more than one operand is reduced to a single value. In expressions containing more than one operator, evaluation of the expression proceeds from left to right. The algebraic expression A-(B-C+5) must be represented in the Operand field as A-B+C-5. Parentheses are not permitted in operand expressions.

The range of values that may result from an operand expression depends on the type of operation. The Assembler evaluates expressions as follows:†

Pseudo Operations: modulo 2<sup>15</sup>·1

Memory Reference: modulo 2<sup>10</sup>·1

Input/Output: 2<sup>6</sup> · 1 (maximum value)

#### 2-15. EXPRESSION TERMS

The terms of an expression are the numbers and the symbols appearing in it. Decimal and octal integers, and symbols defined as being absolute in an EQU pseudo operation are absolute terms. The asterisk and all symbols that are defined in the program are relocatable or absolute depending on the type of assembly. Symbols that are defined as external may appear only as single term expressions and may not be indirect.

Within a relocatable program, terms may be program relocatable or common relocatable. A symbol that names an area of common storage is a common relocatable term. A symbol that is defined in any statement other than COM or EQU is a relocatable term. Within one expression all relocatable terms must be program relocatable or common relocatable; the two types may not be mixed.

### 2-16. ABSOLUTE AND RELOCATABLE EXPRESSIONS

An expression is absolute if its value is unaffected by program relocation. An expression is relocatable if its value changes according to the location into which the program is loaded. In an absolute program, all expressions are absolute. In a relocatable program, an expression may be program relocatable, common relocatable, or absolute (if less than 2000<sub>8</sub>) depending on the definition of the terms composing it.

2-17. ABSOLUTE EXPRESSIONS. An absolute expression may be any arithmetic combination of absolute terms. It may contain relocatable terms alone, or in combination with absolute terms. If relocatable terms appear, there must be an even number of them; they must be of the same type; and they must be paired by sign (a negative term for each positive term). The paired terms do not have to be contiguous in the expression. The pairing of terms by type cancels the effect of relocation; the value represented by a pair remains constant.

An absolute expression reduces to a single absolute value. The value of an absolute multi-term expression may be negative only for ABS pseudo operations. A single numeric term also may be negative in an OCT, DEX, BYT, or DEC pseudo instruction. In a relocatable program the value of an absolute expression must be less than  $2000_8$  for instructions that reference memory locations (Memory Reference, DEF, Arithmetic subroutine calls, etc.).

If  $P_1$  and  $P_2$  are program relocatable terms;  $C_1$  and  $C_2$ , common relocatable; and A, an absolute term; then the following are absolute terms:

$$A = C_1 + C_2$$

$A = P_1 + P_2$   $C_1 = C_2 + A$

$A + A$   $P_1 = P_2$   $-C_1 + C_2 + A$

\*  $-P_1$   $-P_1 + P_2$   $-A - P_1 + P_2$

The asterisk is program relocatable.

2-18. **RELOCATABLE EXPRESSIONS**. A relocatable expression is one whose value is changed by the loader. All relocatable expressions must have a positive value.

A relocatable expression may contain an odd number of relocatable terms, alone, or in combination with absolute terms. All relocatable terms must be of the same type. Terms must be paired by sign with the odd term being positive.

A relocatable expression reduces to a single positive relocatable term, adjusted by the values represented by the absolute terms and paired relocatable terms associated with it.

<sup>†</sup>The evaluation of expressions by the Assembler is compatible with the addressing capability of the hardware instructions (e.g., up to 32K words through Indirect Addressing). The user must take care not to create addresses which exceed the memory size of the particular configuration.

If  $P_1$ ,  $P_2$ , and  $P_3$  are program relocatable terms;  $C_1$ ,  $C_2$  and  $C_3$ , common relocatable; and A, an absolute term; then the following are relocatable terms:

#### 2-19. LITERALS

Literal values may be specified as operands in relocatable programs. The Assembler converts the literal to its binary value, assigns an address to it, and substitutes this address as the operand. Locations assigned to literals are those immediately following the last location used by the program.

A literal is specified by using an equal sign and a one-character identifier defining the type of literal. The actual literal value is specified immediately following this identifier; no spaces may intervene.

#### The identifiers are:

- =D a decimal integer, in the range -32767 to 32767, including zero.†

- =F a floating point number; any positive or negative real number in the range 10<sup>-38</sup> to 10<sup>38</sup>, including zero.†

- =B an octal integer, one to six digits,  $b_1b_2b_3b_4b_5b_6$ , where  $b_1$  may be 0 or 1, and  $b_2$ - $b_7$  may be 0 to 7.†

- =A two ASCII characters.†

- =L an expression which, when evaluated, will result in an absolute value. All symbols appearing in the expression must be previously defined.

If the same literal is used in more than one instruction or if different literals have the same value (e.g., =B100 and =D64), only one value is generated, and all instructions using these literals refer to the same location.

Literals may be specified only in the following memory reference, register reference, EAU, and pseudo instructions:

|     | tu - #H1496. | 医多数乳动剂剂   |                                                    |

|-----|--------------|-----------|----------------------------------------------------|

| ADA | CPA          | MBT       |                                                    |

| ADB | CPB          | MDB       |                                                    |

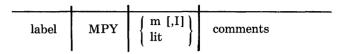

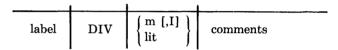

| ADX | DIV          | MPY       |                                                    |

| ADY | IOR          | MVW       | mav use =D, =B, =A, =L                             |

| AND | LDA          | SBS       | $\left.\right\}$ may use $-D$ , $-B$ , $-A$ , $-D$ |

| CBS | LDB          | TBS       |                                                    |

| CBT | LDX          | XOR       |                                                    |

| CMW | LDY          |           |                                                    |

|     |              |           |                                                    |

|     |              | 7 194 104 |                                                    |

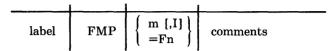

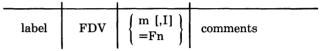

| DLD | FDV          | FSB       | may use =F                                         |

| FMP | FAD          |           | may use                                            |

|     |              |           | 不多以后,但这些处理的特别。                                     |

Examples are as follows:

| LDA | =D7980         | A-Register is loaded with the binary equivalent of $7980_{10}$ .                      |

|-----|----------------|---------------------------------------------------------------------------------------|

| IOR | =B777          | Inclusive OR is performed with contents of A-Register and $777_8$ .                   |

| LDA | =ANO           | A-Register is loaded with binary representation of ASCII characters NO.               |

| LDB | =LZETZ-ZOOM+68 | B-Register is loaded with<br>the absolute value resulting<br>from the expression.     |

| FMP | =F39.75        | Contents of A- and B-<br>Registers multiplied by<br>floating point constant<br>39.75. |

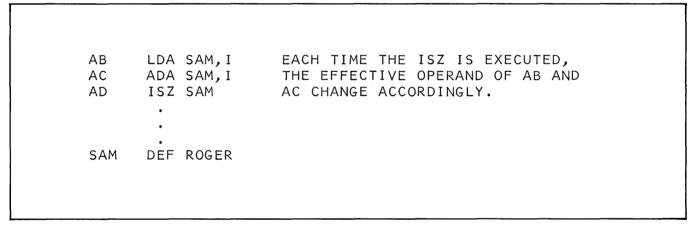

#### 2-20. INDIRECT ADDRESSING

The HP computers provide an indirect addressing capability for memory reference instructions. The operand portion of an indirect instruction contains the address of another location. The secondary location may be the operand or it may be indirect also and give yet another location, and so forth. The chaining ceases when a location is encountered that does not contain an indirect address. Indirect addressing provides a simplified method of address modifications as well as allowing access to any location in core.

The Assembler allows specification of indirect addressing by appending a comma and the letter I to any memory reference operand other than one referring to an external symbol. The actual address of the instruction may be given in a DEF pseudo operation; this pseudo operation may also be used to indicate further levels of indirect addressing. An example is shown in Figure 2-5. A relocatable assembly language program, however, may be designed without concern for the pages in which it will be stored; indirect addressing is not required in the source language. When the program is being loaded, the loader provides indirect addressing whenever it detects an operand which does not fall in the current page or the base page. The loader substitutes a reference to a program link location (established by the loader in either the base page or the current page\*) and then stores an indirect address in the particular program link location. If the program link location is in the base page, all references to the same operand from other pages will be via the same link location.

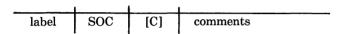

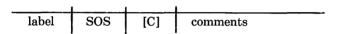

#### 2-21. CLEAR FLAG INDICATOR

The majority of the input/output instructions can alter the status of the input/output interrupt flag after execution or after the particular test is performed. In source language, this function is selected by appending a comma and a letter C to the Operand field. Some examples are shown in Figure 2-6.

#### 2-22. COMMENTS FIELD

The Comments field allows the user to transcribe notes on the program that will be listed with source language coding on the output produced by the Assembler. The field follows the Operand field and is separated from it by at least one space. The end-of-record mark, the end-of-statement mark, CR LF, or the 80th character of a statement terminates the field. The statement length should not exceed 52 characters, the width of the source language portion of the listing. However, statements consisting solely of comments may contain up to 68 characters including the asterisk in the first position. On the list output, statements consisting entirely of comments begin in position 5 rather than 21 as with other source statements. Any characters beyond the above limits will not appear on the listing.

If there is no operand present, the Comments field should be omitted in the NAM and END pseudo operations and in the input/output statements, SOC, SOS, and HLT. If a comment is used, the Assembler attempts to interpret it as an operand. This limitation applies also to multi-operand instructions.

Figure 2-5. Indirect Addressing Example

STC 107,C CLEAR FLAG 107 AFTER CONTROL BIT IS SET OTB 105,C CLEAR FLAG 105 AFTER MOVE

Figure 2-6. Clear Flag Examples

<sup>\*</sup>Refer to the description of the :PROG,LOADR directive in HP 24307B DOS-III Disc Operating System (24307-90006).

### **MACHINE INSTRUCTIONS**

SECTION

Ш

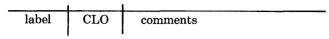

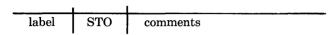

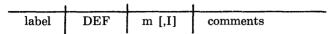

The Assembler language machine instruction codes take the form of three-letter mnemonics. Each source statement corresponds to a machine operation in the object program produced by the Assembler.

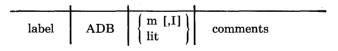

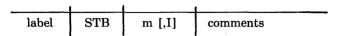

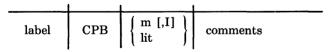

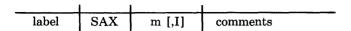

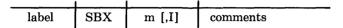

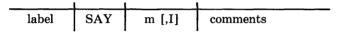

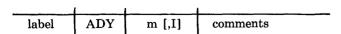

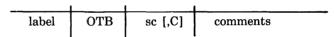

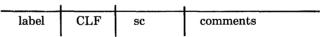

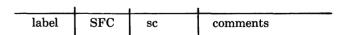

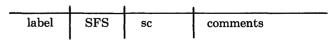

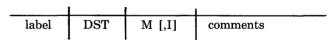

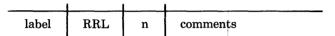

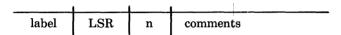

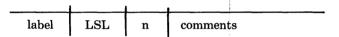

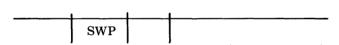

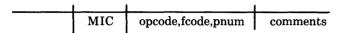

Notation used in representing source language instruction is as follows:

| label    | Optional statement label                                         |

|----------|------------------------------------------------------------------|

| m        | Memory location — an expression                                  |

| I        | Indirect addressing indicator                                    |

| sc       | Select code — an expression                                      |

| C        | Clear interrupt flag indicator                                   |

| comments | Optional comments                                                |

| []       | Brackets defining a field or portion of a field that is optional |

| { }      | Brackets indicating that one of the set may be selected.         |

| lit      | literal                                                          |

|       | L   |        | l        |

|-------|-----|--------|----------|

| label | JMP | m [,I] | comments |

Jump to m. Jump indirect inhibits interrupt until the transfer of control is complete.

|       | L   |        |          |

|-------|-----|--------|----------|

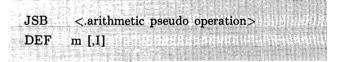

| label | JSB | m [,I] | comments |

Jump to subroutine. The address for label+1 is placed into the location represented by m and control transfers to m+1. On completion of the subroutine, control may be returned to the normal sequence by performing a JMP m, I.

| label | ISZ | m [,I] | comments |

|-------|-----|--------|----------|

Increment, then skip if zero. ISZ adds 1 to the contents of m. If m then equals zero, the next instruction in memory is skipped.

#### 3-1. MEMORY REFERENCE

The memory reference instructions perform arithmetic, logical, jump, word manipulation, byte manipulation, and bit manipulation operations on the contents of memory locations and the registers. An instruction may directly address the  $2048_{10}$  words of the current and base pages. If required, indirect addressing may be used to refer to all  $32,768_{10}$  words of memory. Expressions in the Operand field are evaluated modulo  $2^{10}$ .

If the program is to be assembled in relocatable form, the Operand field may contain relocatable or absolute expressions; however, absolute expressions must be less than 2000<sub>8</sub> in value. If the program is to be assembled in absolute form, the Operand field may contain any expression which is consistent with the location of the program. Literals may not be used in absolute programs. Absolute programs must be complete entities; they may not refer to external subroutines or to common storage.

#### 3-2. JUMP AND INCREMENT-SKIP

Jump and Increment-Skip instructions may alter the normal sequence of program execution.

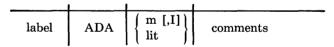

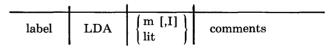

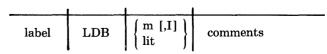

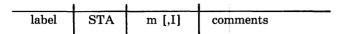

#### 3-3. ADD, LOAD AND STORE

Add, Load, and Store instructions transmit and alter the contents of memory and of the A- and B-Registers. A literal, indicated by "lit", may be either =D, =B, =A, or =L type.

Add the contents of m to A.

Add the contents of m to B.

Load A with the contents of m.

Load B with the contents of m.

Store contents of A in m.

Store contents of B in m.

In each instruction, the contents of the sending location is unchanged after execution.

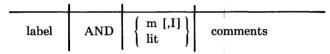

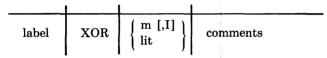

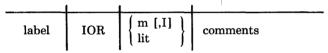

#### 3-4. LOGICAL OPERATIONS

The logical instructions allow bit manipulation and the comparison of two computer words.

The logical product ("AND") of the contents of m and the contents of A are placed in A.

The modulo-two sum (exclusive "or") of the bits in m and the bits in A is placed in A.

The logical sum (inclusive "or") of the bits in m and the bits in A is placed in A.

| label | CPA | $\left\{\begin{array}{l} m \ [,I] \\ lit \end{array}\right\}$ | comments |

|-------|-----|---------------------------------------------------------------|----------|

Compare the contents of m with the contents of A. If they differ, skip the next instruction; otherwise, continue.

Compare the contents of m with the contents of B. If they differ, skip the next instruction; otherwise, continue.

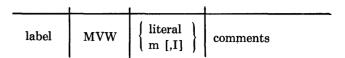

#### 3-5. WORD PROCESSING (21MX ONLY)

The word processing instructions allow the user to move a series of data words from one array in memory to another or to compare (word-by-word) the contents of two arrays in memory.

Move words. The A-register contains the starting (lowest) word address of the source array. The B-register contains the starting (lowest) word address of the destination array. The number of words to be moved is specified by literal or by the value contained in m [,I]. The specified number of words are moved from the source array into the destination array. As each word is moved, the A- and B-registers are incremented by one. The source array is not altered.

Compare words. The A-register contains the starting (lowest) word address of array #1. The B-register contains the starting (lowest) word address of array #2. The number of word comparisons to be performed is specified by literal or by the value contained in m [,I]. The two arrays are compared word-by-word beginning at the specified addresses. The operation is finished when an inequality is detected or when the specified number of word comparisons have been performed. When the operation is finished, the A-register contains the word address of the last word in array #1 which was compared; the B-register contains the starting address of array #2 incremented by the "count" parameter (literal or the value in m [,I]). If the two arrays are equal, execution proceeds at the next sequential source language instruction (P+3). If array #1 is "less than" array #2, execution proceeds at instruction P+4. If array #1 is "greater than" array #2, execution proceeds at instruction P+5. The two arrays are not altered.

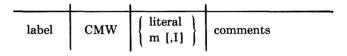

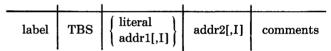

#### 3-6. BYTE PROCESSING (21MX ONLY)

The byte processing instructions allow the user to copy a data byte from memory into the A- or B-register, copy a data byte from the A- or B-register into memory, copy a series of data bytes from one array in memory to another, compare (byte-by-byte) the contents of two arrays in memory, or scan an array in memory for particular data bytes.

A byte address is defined as two times the word address of the memory location containing the particular data byte. If the byte location is the low order half of the memory location (bits 0-7), bit 0 of the byte address is set; if the byte location is the high order half of the memory location (bits 8-15), bit 0 of the byte address is clear.

Load byte. The B-register contains the byte address of the byte to be loaded. The specified byte is copied from memory into bits 0-7 of the A-register (bits 8-15 of the A-register are set to zeros). The B-register is then incremented by one. The memory location is not altered.

Store byte. The B-register contains the byte address into which the byte is to be stored. Bits 0-7 of the A-register are copied into the specified memory byte location (bits 8-15 of the A-register are ignored). The B-register is then incremented by one. The A-register is not altered.

Move bytes. The A-register contains the starting (lowest) byte address of the source array. The B-register contains the starting (lowest) byte address of the destination array. The number of bytes to be moved is specified by literal or by the value contained in m [,I]. The specified number of bytes are moved from the source array into the destination array. As each byte is moved, the A- and B-registers are incremented by one. The source array is not altered.

Compare bytes. The A-register contains the starting (lowest) byte address of array #1. The B-register contains the starting (lowest) byte address of array #2. The number of byte comparisons to be performed is specified by literal or by the value contained in m [,I]. The two arrays are compared byte-by-byte beginning at the specified addresses. The operation is finished when an inequality is detected or when the specified number of byte comparisons have been performed. When the operation is finished, the A-register contains the byte address of the last byte in array #1 which was compared; the B-register contains the starting byte address of array #2 incremented by the "count" parameter (literal or the value in m [,I]). If the two arrays are equal, execution proceeds at the next sequential source language instruction (P+3). If array #1 is "less than" array #2, execution proceeds at instruction P+4. If array #1 is "greater than" array #2, execution proceeds at instruction P+5. The two arrays are not altered.

Scan for byte. The A-register contains a test byte in bits 0-7 and a termination byte in bits 8-15. The B-register

contains the starting (lowest) byte address of the array to be scanned. The array is compared byte-by-byte against both the test and termination bytes starting at the specified address. The operation is finished when a positive comparison is detected or when the end of memory is reached. If the test byte is detected, execution proceeds at the next sequential source language instruction (P+1) and the B-register contains the address of the test byte in the array. If the termination byte is detected, execution proceeds at instruction P+2 and the B-register contains the address plus one of the termination byte in the array. If the end of memory is detected, execution proceeds at instruction P+2 and the B-register contains all zeros. The A-register and the array are not altered.

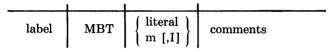

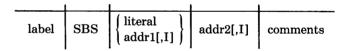

#### 3-7. BIT PROCESSING (21MX ONLY)

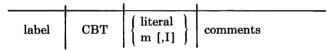

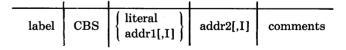

The bit processing instructions allow the user to selectively test, set, or clear bits in a memory location according to the contents of a mask. In the descriptions below, addr1 and addr2 may be operand expressions.

Test bits. literal is a test mask, addr1[,I] is the address of a memory location containing a test mask, and addr2[,I] is the address of a memory location containing the bits to be tested. The bits in addr2[,I] which correspond to the "1" bits in the mask are tested. All other bits in addr2[,I] are ignored. If all the applicable bits in addr2[,I] are set, execution proceeds at the next sequential source language instruction (P+3). If any of the applicable bits in addr2[,I] are clear, execution proceeds at instruction P+4.

Set bits. literal is a mask, addr1[,I] is the address of a memory location containing a mask, and addr2[,I] is the address of a memory location containing the bits to be set. The bits in addr2[,I] which correspond to the "1" bits in the mask are set. All other bits in addr2[,I] are not affected. Functionally, the SBS instruction is a "logical OR" operation.

Clear bits. literal is a mask, addr1[,I] is the address of a memory location containing a mask, and addr2[,I] is the address of a memory location containing the bits to be cleared. The bits in addr2[,I] which correspond to the "1" bits in the mask are cleared. All other bits in addr2[,I] are not affected.

#### 3-8. REGISTER REFERENCE

The register reference instructions include a shift-rotate group, an alter-skip group, an index register group, and NOP (no operation). For the shift-rotate and alter-skip groups, the instruction mnemonics within each group may be combined into a single source statement to cause multiple operations to be executed during one memory cycle. In such cases, successive mnemonics within a single source statement are separated from one another by a comma.

These instructions may be combined as follows:

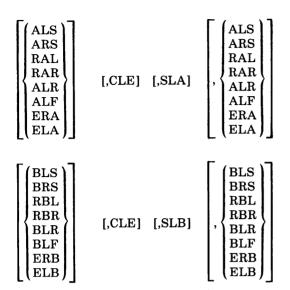

$$\begin{bmatrix} \left\{ \begin{array}{c} ALS \\ ARS \\ RAL \\ RAR \\ ALR \\ ALF \\ ERA \\ ELA \\ \end{array} \right\} \begin{bmatrix} (CLE] \ [,SLA] \\ (SLA] \\ (SLA) \\ (S$$

$$[abel] \left\{ \begin{bmatrix} BLS \\ BRS \\ RBL \\ RBR \\ BLR \\ BLF \\ ERB \\ ELB \end{bmatrix} [,CLE] [,SLB] \left\{ \begin{bmatrix} BLS \\ BRS \\ RBL \\ RBR \\ BLR \\ BLR \\ BLF \\ ERB \\ ELB \end{bmatrix} \right\} comments$$

#### 3-9. SHIFT-ROTATE GROUP

This group contains 19 basic instructions that can be combined to produce more than 500 different single cycle operations.

- CLE Clear E to zero

- ALS Shift A left one bit, zero to least significant bit. Sign unaltered

- BLS Shift B left one bit, zero to least significant bit. Sign unaltered

- ARS Shift A right one bit, extend sign; sign unaltered

- BRS Shift B right one bit, extend sign; sign unaltered

- RAL Rotate A left one bit

- RBL Rotate B left one bit

- RAR Rotate A right one bit

- RBR Rotate B right one bit

- ALR Shift A left one bit, clear sign, zero to least significant bit

- BLR Shift B left one bit, clear sign, zero to least significant bit

- ERA Rotate E and A right one bit

- ERB Rotate E and B right one bit

- ELA Rotate E and A left one bit

- ELB Rotate E and B left one bit

- ALF Rotate A left four bits

- BLF Rotate B left four bits

- SLA Skip next instruction if least significant bit in A

- SLB Skip next instruction if least significant bit in B is zero

CLE, SLA, or SLB appearing alone or in any valid combination with each other are assumed to be a shift-rotate machine instruction.

The shift-rotate instructions must be given in the order shown. At least one and up to four are included in one statement. Instructions referring to the A-register may not be combined in the same statement with those referring to the B-register.

#### 3-10. ALTER-SKIP GROUP

The alter-skip group contains 19 basic instructions that can be combined to produce more than 700 different single cycle operations.

- CLA Clear the A-Register

CLB Clear the B-Register

- CMA Complement the A-Register

- CMB Complement the B-Register

CCA Clear, then complement the A-Register (set to

- ones)

- CCB Clear, then complement the B-Register (set to ones)

- CLE Clear the E-Register

- CME Complement the E-Register

- CCE Clear, then complement the E-Register

- SEZ Skip next instruction if E is zero

- SSA Skip if sign of A is positive (0)

- SSB Skip if sign of B is positive (0)

| INA | Increment A by one                                                                                                            |

|-----|-------------------------------------------------------------------------------------------------------------------------------|

| INB | Increment B by one                                                                                                            |

| SZA | Skip if contents of A equals zero                                                                                             |

| SZB | Skip if contents of B equals zero                                                                                             |

| SLA | Skip if least significant bit of A is zero                                                                                    |

| SLB | Skip if least significant bit of B is zero                                                                                    |

| RSS | Reverse the sense of the skip instructions. If no<br>skip instructions precede in the statement, skip<br>the next instruction |

These instructions may be combined as follows:

| label | $ \begin{bmatrix} \begin{pmatrix} \text{CLA} \\ \text{CMA} \\ \text{CCA} \end{bmatrix} \end{bmatrix} [,\text{SEZ}] \begin{bmatrix} \begin{pmatrix} \text{CLE} \\ \text{CME} \\ \text{CCE} \end{pmatrix} \end{bmatrix} [ $          | [.RSS.] [.SLA] [.NA], [.RSS.] [.RSS.] | comments |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------|

| label | $\left[ \left\{ \begin{array}{c} \text{CLB} \\ \text{CMB} \\ \text{CCB} \end{array} \right\} \right] \text{ [,SEZ]} \left[ \left\{ \begin{array}{c} \text{CLE} \\ \text{CME} \\ \text{CCE} \end{array} \right\} \right] \text{ [}$ | .SSB] [,SLB] [,INB] [,SZB] [,RSS]     | comments |

The alter-skip instructions must be given in order shown. At least one and up to eight are included in one statement. Instructions referring to the A-register may not be combined in the same statement with those referring to the B-register. When two or more skip functions are combined in a single operation, a skip occurs if any one of the conditions exists. If a word with RSS also includes both SSA and SLA (or SSB and SLB), a skip occurs only when sign and least significant bit are both set (1).

#### 3-11. INDEX REGISTER GROUP (21MX ONLY)

This group contains 32 instructions which perform various operations involving the use of index registers X and Y. An instruction may directly address the  $2048_{10}$  words of the current and base pages. If required, indirect addressing may be used (except where noted otherwise) to refer to all  $32,768_{10}$  words of memory. Expressions in the Operand field are evaluated modulo  $2^{10}$ .

| label | CAX | comments |

|-------|-----|----------|

Copy A to X. The contents of the A-register are copied into the X-register. The A-register is not altered.

|       |     | <u></u>  |

|-------|-----|----------|

| label | CBX | comments |

Copy B to X. The contents of the B-register are copied into the X-register. The B-register is not altered.

|       | L   |          |

|-------|-----|----------|

| label | CAY | comments |

Copy A to Y. The contents of the A-register are copied into the Y-register. The A-register is not altered.

| label | CBY | comments |

|-------|-----|----------|

Copy B to Y. The contents of the B-register are copied into the Y-register. The B-register is not altered.

|       |     | <u> </u> |

|-------|-----|----------|

| label | CXA | comments |

Copy X to A. The contents of the X-register are copied into the A-register. The X-register is not altered.

| label | CXB | comments |  |

|-------|-----|----------|--|

Copy X to B. The contents of the X-register are copied into the B-register. The X-register is not altered.

|       | l   | L        |

|-------|-----|----------|

| label | CYA | comments |

Copy Y to A. The contents of the Y-register are copied into the A-register. The Y-register is not altered.

|       | L   | <u>                                     </u> |

|-------|-----|----------------------------------------------|

| label | CYB | comments                                     |

Copy Y to B. The contents of the Y-register are copied into the B-register. The Y-register is not altered.

| label | XAX | comments |

|-------|-----|----------|

Exchange A and X. The contents of the A-register are copied into the X-register and the contents of the X-register are copied into the A-register.

|       |     | L        |

|-------|-----|----------|

| label | XBX | comments |

Exchange B and X. The contents of the B-register are copied into the X-register and the contents of the X-register are copied into the B-register.

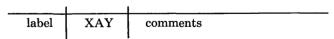

Exchange A and Y. The contents of the A-register are copied into the Y-register and the contents of the Y-register are copied into the A-register.

Exchange B and Y. The contents of the B-register are copied into the Y-register and the contents of the Y-register are copied into the B-register.

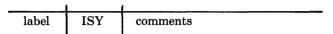

Increment X and skip if zero. The contents of the X-register are incremented by one and then tested. If the new value in X is zero, the next sequential instruction (P+1) is skipped and execution proceeds at instruction P+2; if the new value in X is non-zero, execution proceeds at instruction P+1.

Increment Y and skip if zero. The contents of the Y-register are incremented by one and then tested. If the new value in Y is zero, the next sequential instruction (P+1) is skipped and execution proceeds at instruction P+2; if the new value in Y is non-zero, execution proceeds at instruction P+1.

| label | DSX | comments |

|-------|-----|----------|

Decrement X and skip if zero. The contents of the X-register are decremented by one and then tested. If the new value in X is zero, the next sequential instruction (P+1) is skipped and execution proceeds at instruction P+2; if the new value in X is non-zero, execution proceeds at instruction P+1.

| label | DSY | comments |

|-------|-----|----------|

Decrement Y and skip if zero. The contents of the Y-register are decremented by one and then tested. If the new value in Y is zero, the next sequential instruction (P+1) is skipped and execution proceeds at instruction P+2; if the new value in Y is non-zero, execution proceeds at instruction P+1.

| label | LDX | $\left\{\begin{array}{c} m \ [,I] \\ literal \end{array}\right\}$ | comments |

|-------|-----|-------------------------------------------------------------------|----------|

Load X from memory. The contents of the specified memory location are copied into the X-register. Indirect addressing may be used. The memory location is not altered.

| label | LDY | $\left\{\begin{array}{l} m \ [,I] \\ literal \end{array}\right\}$ | comments |

|-------|-----|-------------------------------------------------------------------|----------|

Load Y from memory. The contents of the specified memory location are copied into the Y-register. Indirect addressing may be used. The memory location is not altered.

| label | STX | m [,I] | comments |

|-------|-----|--------|----------|

Store X into memory. The contents of the X-register are copied into the specified memory location. Indirect addressing may be used. The X-register is not altered.

|       |     |        | <u> </u> |

|-------|-----|--------|----------|

| label | STY | m [,I] | comments |

Store Y into memory. The contents of the Y-register are copied into the specified memory location. Indirect addressing may be used. The Y-register is not altered.

| 1     |     |        |          |

|-------|-----|--------|----------|

| label | LAX | m [,I] | comments |

Load A from memory indexed by X. The contents of the specified memory location are copied into the A-register. Indirect addressing may be used. The address of the memory location is computed by adding the contents of the X-register to **m** or to **m**,I. Note that indirect addressing (if specified) is performed first and then the address is indexed. The X-register and the memory location are not altered.

| label | LBX | m [,I] | comments |

|-------|-----|--------|----------|

Load B from memory indexed by X. The contents of the specified memory location are copied into the B-register. Indirect addressing may be used. The address of the memory location is computed by adding the contents of the X-register to m or to m,I. Note that indirect addressing (if specified) is performed first and then the address is indexed. The X-register and the memory location are not altered.

Load A from memory indexed by Y. The contents of the specified memory location are copied into the A-register. Indirect addressing may be used. The address of the memory location is computed by adding the contents of the Y-register to m or to m,I. Note that indirect addressing (if specified) is performed first and then the address is indexed. The Y-register and the memory location are not altered.

|       |     |        | <u> </u> |

|-------|-----|--------|----------|

| label | LBY | m [,I] | comments |

Load B from memory indexed by Y. The contents of the specified memory location are copied into the B-register. Indirect addressing may be used. The address of the memory location is computed by adding the contents of of the Y-register to m or to m,I. Note that indirect addressing (if specified) is performed first and then the address is indexed. The Y-register and the memory location are not altered.

Store A into memory indexed by X. The contents of the A-register are copied into the specified memory location. Indirect addressing may be used. The address of the memory location is computed by adding the contents of the X-register to **m** or to **m**,I. Note that indirect addressing (if specified) is performed first and then the address is indexed. The A-register and the X-register are not altered.

Store B into memory indexed by X. The contents of the B-register are copied into the specified memory location. Indirect addressing may be used. The address of the memory location is computed by adding the contents of the X-register to m or to m,I. Note that indirect addressing (if specified) is performed first and then the address is indexed. The B-register and the X-register are not altered.

Store A into memory indexed by Y. The contents of the A-register are copied into the specified memory location. Indirect addressing may be used. The address of the memory location is computed by adding the contents of the Y-register to m or to m,I. Note that indirect addressing (if specified) is performed first and then the address is indexed. The A-register and the Y-register are not altered.

Store B into memory indexed by Y. The contents of the B-register are copied into the specified memory location. Indirect addressing may be used. The address of the memory location is computed by adding the contents of the Y-register to m or to m,I. Note that indirect addressing (if specified) is performed first and then the address is indexed. The B-register and the Y-register are not altered.

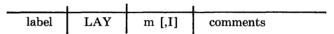

Add memory to X. The contents of the specified memory location are algebraically added to the contents of the X-register. Indirect addressing may be used. The memory location is not altered.

Add memory to Y. The contents of the specified memory location are algebraically added to the contents of the Y-register. Indirect addressing may be used. The memory location is not altered.

|       | L   | L      |          |

|-------|-----|--------|----------|

| label | JLY | m [,I] | comments |

Jump and load Y. Control transfers unconditionally to the specified memory location and the address P+2 is loaded into the Y-register. Indirect addressing may be used. This instruction is used for calling subroutines. The subroutines use the Y-register to access parameters and to return control (by way of the JPY instruction) to the calling program.

| label | JPY | m | comments |

|-------|-----|---|----------|

Jump indexed by Y. Control transfers unconditionally to the specified memory location. Indirect addressing may not be used. The address of the memory location is computed by adding the contents of the Y-register to m. This instruction is used for returning control from subroutines to the calling program (assuming that they were entered by way of JLY instructions).

#### 3-12. NO-OPERATION INSTRUCTION

When a no-operation is encountered in a program, no action takes place; the computer goes on to the next instruction. A full memory cycle is used in executing a no-operation instruction.

| label | NOP | comments |

|-------|-----|----------|

A subroutine to be entered by a JSB instruction should have a NOP as the first statement. The return address can be stored in the location occupied by the NOP during execution of the program. A NOP statement causes the Assembler to generate a word of zero.

### 3-13. INPUT/OUTPUT, OVERFLOW, AND HALT

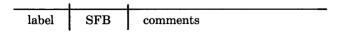

The input/output instructions allow the user to transfer to and from an external device via a buffer, to enable or disable external interrupt, or to check the status of I/O devices and operations. A subset of these instructions permits checking for an arithmetic overflow condition.

Input/output instructions require the designation of a select code, sc, which indicates one of  $64_{10}$  input/output channels or functions. Each channel consists of a connect/disconnect control bit, a flag bit, and a buffer of up to 16 bits. The setting of the control bit indicates that a

device associated with the channel is operable. The flag bit is set automatically when transmission between the device and the buffer is completed. Instructions are also available to test or clear the flag bit for the particular channel. If the interrupt system is enabled, setting of the flag causes program interrupt to occur; control transfers to the interrupt location related to the channel.

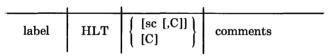

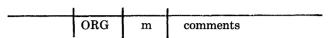

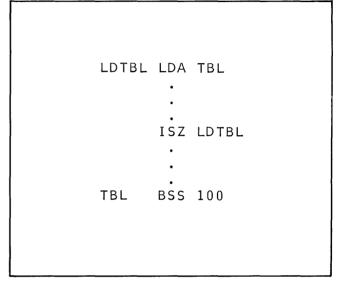

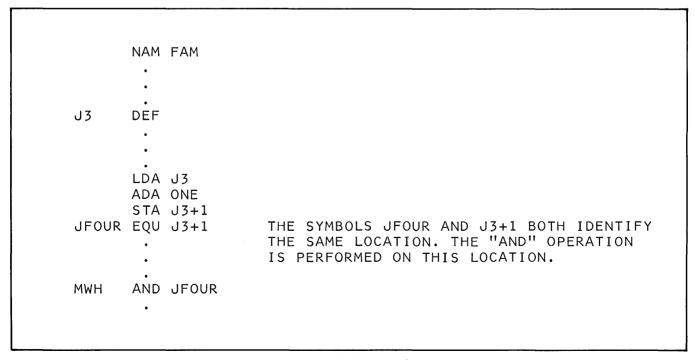

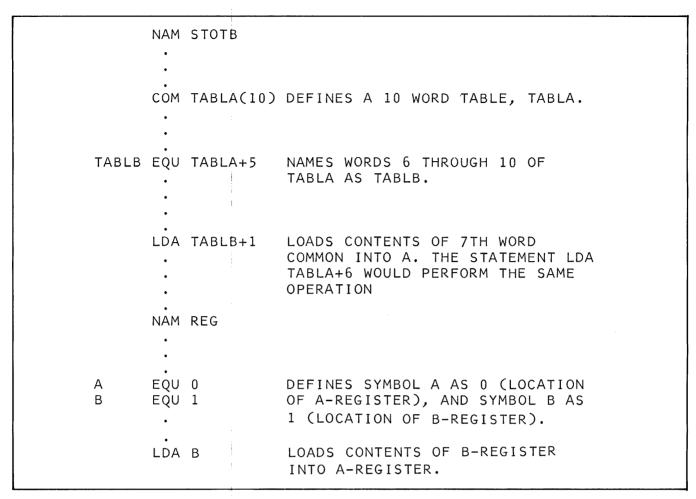

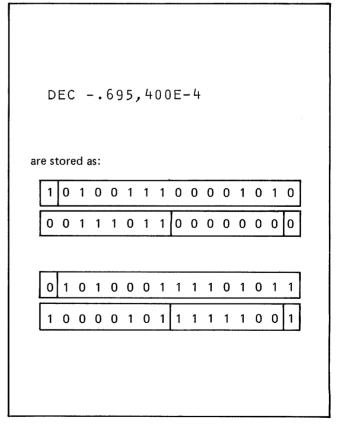

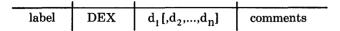

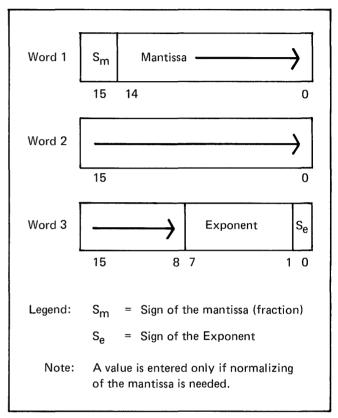

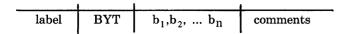

Note: When Memory Protect is enabled, execution of all I/O instructions except those which reference the switch register (select code 01) or the overflow bit is prohibited.