## DEMFA HARDWARE FUNCTIONAL SPECIFICA-TION

Order Number: XXX

This document specifies the functionality of the DEMFA, the XMI to FDDI adapter.

Revision

1.3

ONLY

DIGITAL INTERNAL USE ONLY

Written by: The DEMFA Group

Edited by: Ron Edgar Santosh Hasani Lea Walton

VAX PRODUCTS AND OPTIONS 14-March-1991

**Digital Equipment Corporation**

### **REVISION HISTORY**

| Date    | Revision | Summary of Changes                                                                              |  |

|---------|----------|-------------------------------------------------------------------------------------------------|--|

| 1/13/89 | X00      | First cut                                                                                       |  |

| 1/20/89 | X01      | First 'complete' edition                                                                        |  |

| 3/7/89  | X02      | Expanded and corrected                                                                          |  |

| 5/5/89  | X03      | Further expanded and corrected - for group internal review                                      |  |

| 5/19/89 | X04      | Expanded and corrected as the result of group internal review. This edition for external review |  |

| 2/7/90  | X05      | Registers updated                                                                               |  |

| 6/30/90 | X06      | LED table included, More complete Environment conditions mentioned,<br>Some other overhauling   |  |

| 7/20/90 | 1.0      | Major update of All Chapters                                                                    |  |

| 1/8/91  | 1.1      | Further updates from DEMFA notesfiles, design reviews, and PMC2.                                |  |

| 3/1/91  | 1.2      | Change to PMC Register CSR03; protocol errors 24 and 25 are reversed.                           |  |

| 3/14/91 | 1.3      | Included DEMFA MTBF figures.                                                                    |  |

### Copyright ©1988,1989 by Digital Equipment Corporation

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may occur in this document.

This specification does not describe any program or product which is currently available from Digital Equipment Corporation. Nor does Digital Equipment Corporation commit to implement this specification in any product or program. Digital Equipment Corporation makes no commitment that this document accurately describes any product it might ever make.

### **CONTENTS**

| Gr | napter 1 DEMFA INTRODUCTION                                                                                                                                                                                          | 1                                      |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|    | 1.1 INTENDED AUDIENCE                                                                                                                                                                                                | 1                                      |

|    | 1.2 GOALS AND NON-GOALS                                                                                                                                                                                              | 1                                      |

|    | 1.3 ASSOCIATED DOCUMENTS                                                                                                                                                                                             | 2                                      |

|    | 1.4 TERMINOLOGY                                                                                                                                                                                                      | 3                                      |

|    | 1.5 FDDI/802.2 Frame Format                                                                                                                                                                                          | 4                                      |

| Cr | napter 2 DEMFA EXECUTIVE SUMMARY                                                                                                                                                                                     | 5                                      |

|    | 2.1 DEMFA CONTEXT                                                                                                                                                                                                    | 5                                      |

|    | 2.2 DEMFA OVERVIEW 2.2.1 HOST INTERFACE 2.2.2 THE ADAPTER MANAGER SUBSYSTEM 2.2.3 THE PACKET BUFFER MEMORY SUBSYSTEM 2.2.4 THE FDDI CHIPSET AND THE PARSER                                                           | 6<br>7<br>7<br>7<br>8                  |

|    | 2.3 PACKET RECEPTION                                                                                                                                                                                                 | 11                                     |

|    | 2.4 PACKET TRANSMISSION                                                                                                                                                                                              | 11                                     |

|    | 2.5 PERFORMANCE                                                                                                                                                                                                      | 12                                     |

| Ch | napter 3 DEMFA FUNCTIONAL DESCRIPTION                                                                                                                                                                                | 15                                     |

|    | 3.1 HOST INTERFACE 3.1.1 THE XMI CORNER 3.1.2 DEMFA SUPPORTED XMI TRANSACTIONS 3.1.3 XMI INTERFACE 3.1.3.1 THE XCI BUS 3.1.3.2 THE PBI BUS 3.1.3.2.1 PBI BUS PROTOCOL 3.1.3.3 THE ESP BUS 3.1.4 THE ESP GATE ARRAY   | 15<br>15<br>17<br>17<br>18<br>18<br>19 |

|    | 3.2 ADAPTER MANAGER SUBSYSTEM 3.2.1 OVERVIEW 3.2.2 AMI INTERFACES 3.2.2.1 THE ESP BUS 3.2.3 MICROPROCESSOR 3.2.4 AMI GATE ARRAY 3.2.4.1 FUNCTIONAL UNITS 3.2.5 68020 MEMORY SUBSYSTEM 3.2.6 SUBSYSTEM DATA INTEGRITY | 22<br>23<br>24<br>25<br>26<br>27<br>29 |

|    | 3.2.7 POWER UP & SELF TEST                           | 30 |

|----|------------------------------------------------------|----|

|    | 3.3 PMC GATE ARRAY                                   | 30 |

|    | 3.3.1 OVERVIEW                                       | 30 |

|    | 3.3.2 INTERFACES                                     | 32 |

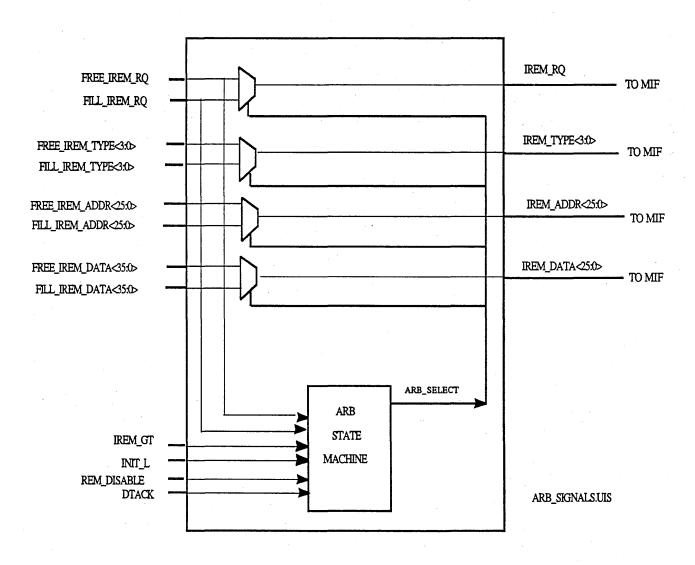

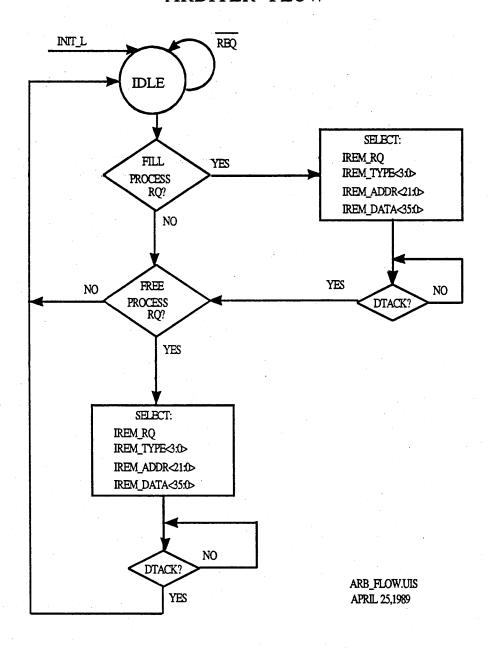

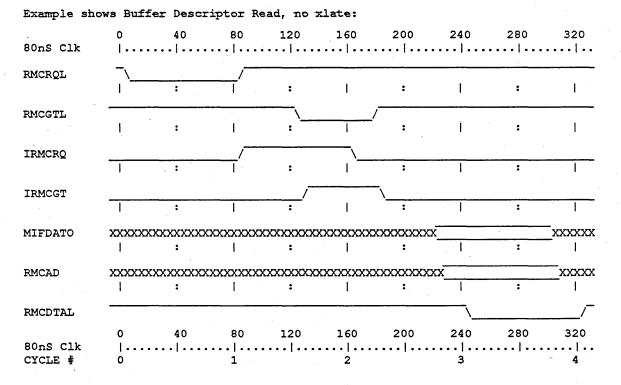

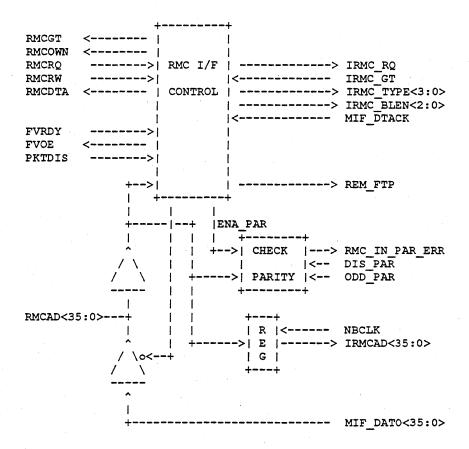

|    | 3.3.2.1 RMC INTERFACE                                | 32 |

|    | 3.3.2.2 ESP INTERFACE                                | 32 |

|    | 3.3.3 FUNCTIONAL BLOCK DESCRIPTIONS                  | 32 |

|    | 3.3.3.1 PACKET BUFFER MEMORY                         | 32 |

|    | 3.3.3.2 PAGE TABLE AND BUFFER DESCRIPTOR MEMORY      | 32 |

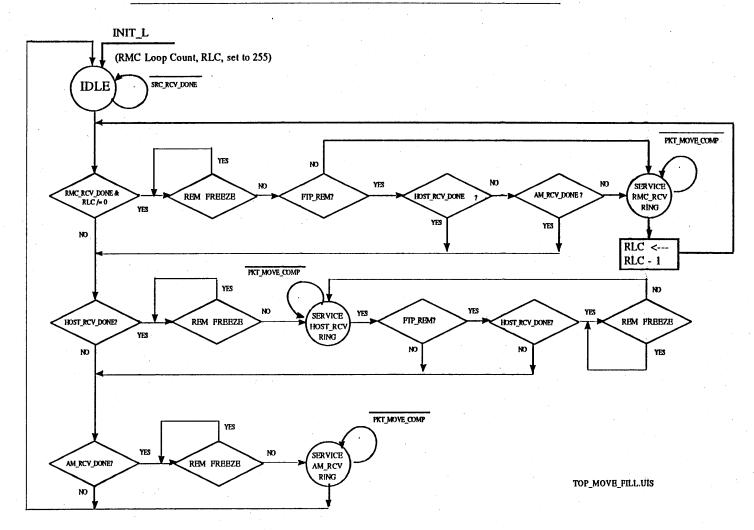

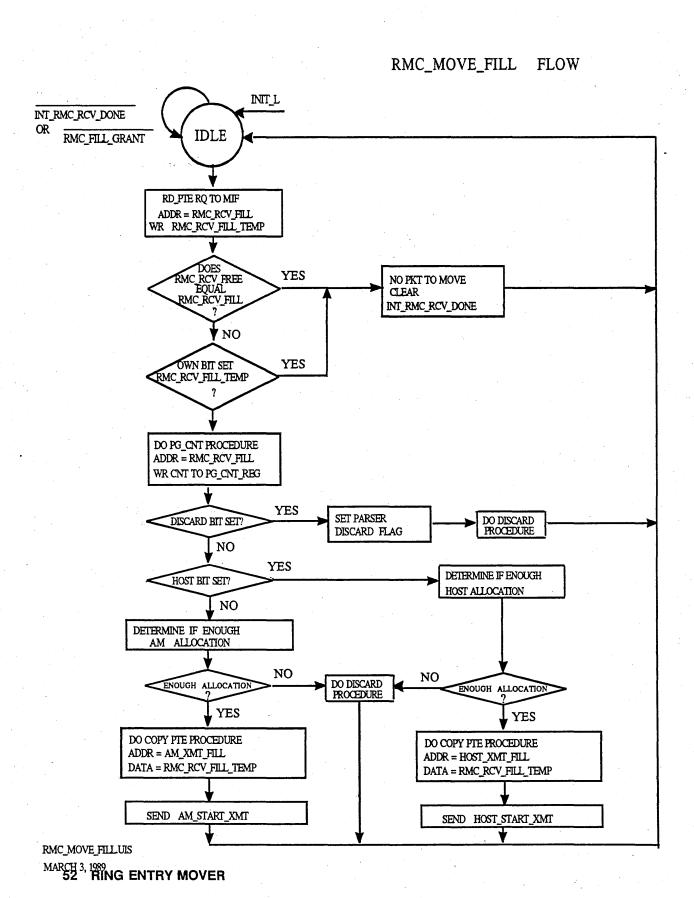

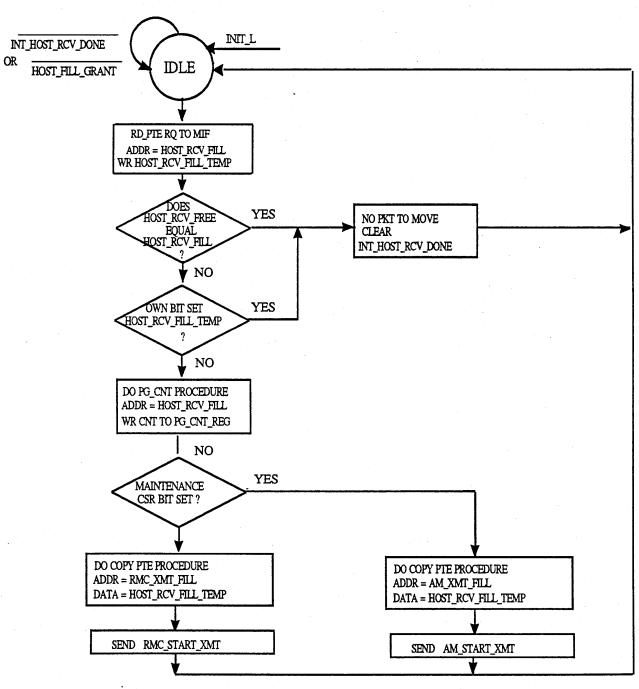

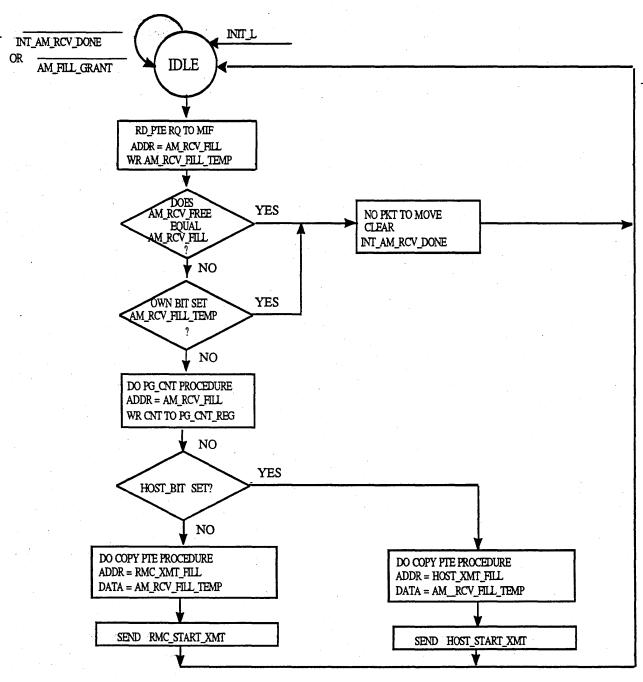

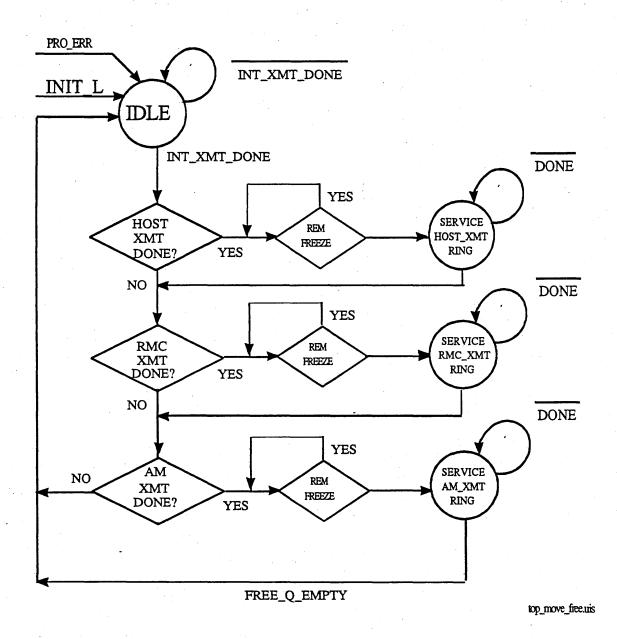

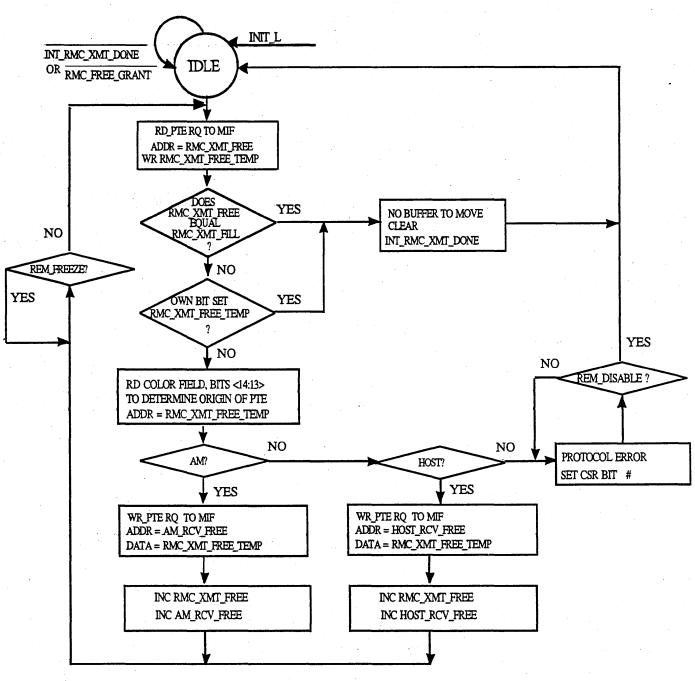

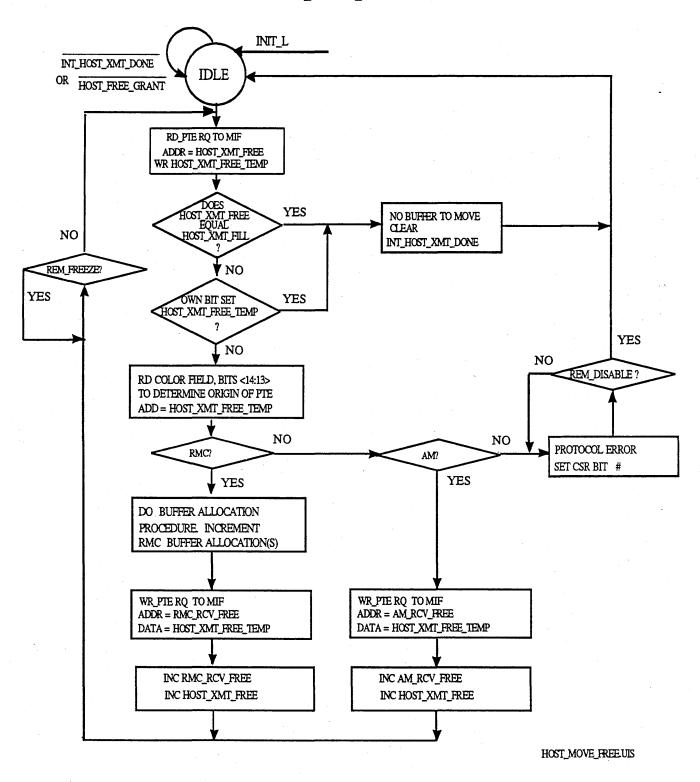

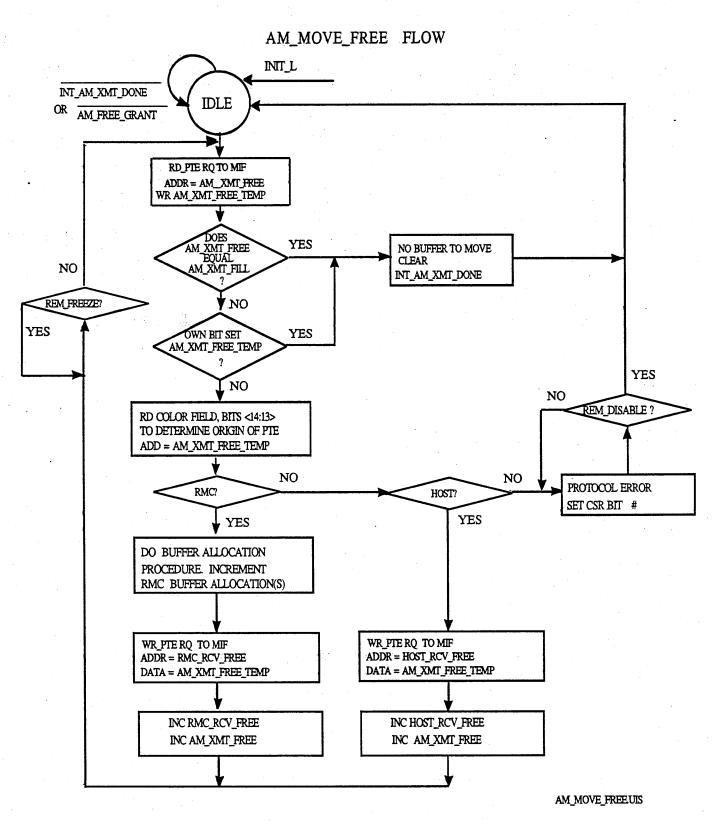

|    | 3.3.3.3 RING ENTRY MOVER                             | 33 |

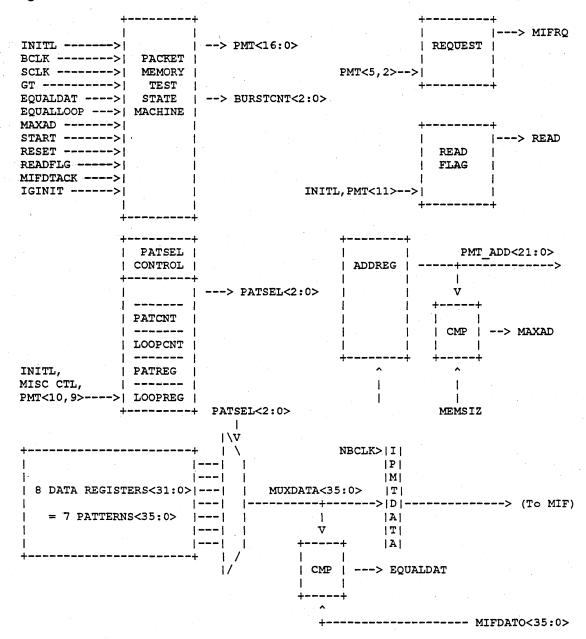

|    | 3.3.3.4 PMT - Packet Memory Test                     | 34 |

|    |                                                      | 34 |

|    | 3.3.3.5 MIF - MEMORY CONTROLLER                      |    |

|    | 3.3.3.6 RMC I/F                                      | 34 |

|    | 3.3.3.7 ESP I/F                                      | 34 |

|    | 3.3.4 TRANSMIT/RECEIVE DATA STREAM PRIORITY          | 35 |

|    | 3.3.5 ADDITIONAL FEATURES                            | 35 |

|    | 3.4 THE FDDI CHIP SET                                | 35 |

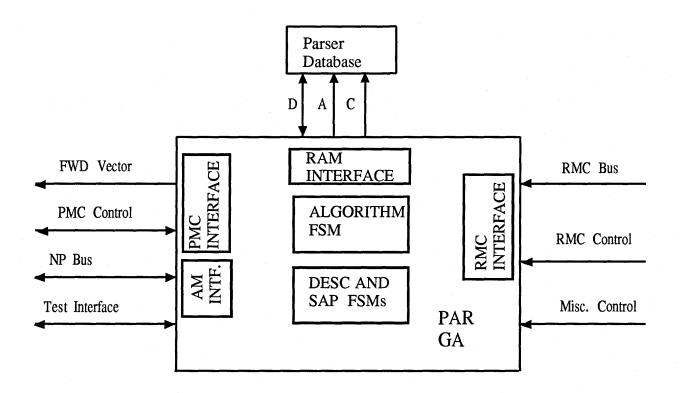

|    | 3.5 PARSER SUBSYSTEM                                 | 37 |

|    | 3.5.1 OVERVIEW                                       | 37 |

|    | 3.5.2 THE PARSER GA                                  | 42 |

|    | 3.5.2.1 RMC INTERFACE                                | 42 |

|    | 3.5.2.2 ADAPTER MANAGER INTERFACE                    | 42 |

|    | 3.5.2.3 RAM INTERFACE                                | 42 |

|    | 3.5.2.4 PACKET MEMORY CONTROLLER INTERFACE           | 42 |

|    | 3.5.2.5 ALGORITHM STATE MACHINE                      | 42 |

|    | 3.5.2.6 BUFFER DESCRIPTOR DECODE STATE MACHINE       | 42 |

|    | 3.5.2.7 SAP DECODE STATE MACHINE                     | 42 |

|    |                                                      |    |

|    | 3.5.2.8 TEST INTERFACE                               | 43 |

|    | 3.5.3 THE PARSER DATABASE                            | 43 |

|    | 3.6 EXPLANATION OF REGISTER DESCRIPTIONS             | 45 |

|    |                                                      |    |

| Jh | apter 4 ESP REGISTERS                                | 47 |

|    | 4.1 XMI REQUIRED REGISTERS                           | 47 |

|    | 4.1.1 DEVICE REGISTER (XDEV)                         | 47 |

|    | 4.1.2 XMI BUS ERROR REGISTER (XBER)                  | 48 |

|    | 4.1.3 XMI FAILING ADDRESS REGISTER (XFADR)           | 52 |

|    | 4.1.4 XMI FAILING ADDRESS EXTENTION REGISTER (XFAER) | 52 |

|    |                                                      |    |

|    | 4.2 DEMFA PORT REGISTERS                             | 53 |

|    | 4.2.1 PORT DATA REGISTER 1 (XPD1)                    | 53 |

|    | 4.2.2 PORT DATA REGISTER 2 (XPD2)                    | 54 |

|    | 4.2.3 PORT STATUS REGISTER (XPST)                    | 54 |

|    | 4.2.4 POWER UP DIAGNOSTIC REGISTER (XPUD)            | 56 |

|    | 4.2.5 PORT CONTROL INITIALIZE REGISTER (XPCI)        | 56 |

|    | 4.2.6 PORT CONTROL SHUTDOWN REGISTER (XPCS)          | 56 |

|    |                                                      |    |

|    | 4.2.7 TRANSMIT CONTROL REGISTER (XTFL)                                                                                    | 57         |

|----|---------------------------------------------------------------------------------------------------------------------------|------------|

|    | 4.2.8 RECEIVE CONTROL REGISTER (XRFL)                                                                                     | 58         |

|    | 4.2.9 COMMAND CONTROL REGISTER (XCFL)                                                                                     | 58         |

|    | 4.2.10 UNSOLICITED CONTROL REGISTER (XUFL)                                                                                | 59         |

|    | 4.2.11 TRANSMIT HOST HIBERNATION LOW REGISTER (THIBL)                                                                     | 59         |

|    | 4.2.12 TRANSMIT HOST HIBERNATION HIGH REGISTER (THIBH)                                                                    | 60         |

|    | 4.2.13 RECEIVE HOST HIBERNATION LOW REGISTER (RHIBL)                                                                      | 60         |

|    | 4.2.14 RECEIVE HOST HIBERNATION HIGH REGISTER (RHIBH)                                                                     | 60         |

|    | 4.2.15 EEPROM UPDATE REGISTER (EEUP)                                                                                      | 61         |

|    | 4.2.16 INTERRUPT VECTOR REGISTER (ITVR)                                                                                   | 61         |

|    | 4.2.17 INTERRUPT DESTINATION VECTOR REGISTER (IDVR)                                                                       | 62         |

|    | 4.3 ESP CONTROL AND STATUS REGISTERS                                                                                      | 62         |

|    | 4.3.1 ESP ERROR REGISTER (ESPERR)                                                                                         | 63         |

|    | 4.3.2 ADAPTER MANAGER INTERRUPT REGISTER (AMIR)                                                                           | 64         |

|    | 4.3.3 ESP MISCELLANEOUS REGISTER (ESPMR)                                                                                  | 65         |

|    | 4.3.4 HOST TRANSMIT RING BASE LOW ADDRESS REGISTER (HTRBLAR)                                                              | 68         |

|    | 4.3.4 HOST TRANSMIT RING BASE LOW ADDRESS REGISTER (HTRBLAR) 4.3.5 HOST TRANSMIT RING BASE HIGH ADDRESS AND SIZE REGISTER | UC         |

|    | (HTRBHARSR)                                                                                                               | 69         |

|    | 4.3.6 HOST RECEIVE RING BASE LOW ADDRESS REGISTER (HRRBLAR)                                                               | 69         |

|    | 4.3.7 HOST RECEIVE RING BASE HIGH ADDRESS AND SIZE REGISTER                                                               | 00         |

|    | (HRRBHARSR)                                                                                                               | 70         |

|    | 4.3.8 PMC TRANSMIT RING BASE ADDRESS REGISTER (PMCTRBAR)                                                                  | 70         |

|    | 4.3.9 PMC RECEIVE RING BASE ADDRESS REGISTER (PMCRRBAR)                                                                   | 71         |

|    | 4.3.10 ADAPTER MANAGER PACKET BUFFER ADDRESS REGISTER (AMPBAR)                                                            | 71         |

|    | 4.3.11 ADAPTER MANAGER PACKET BUFFER DATA 0 REGISTER (AMPBDOR)                                                            | 73         |

|    | 4.3.12 ADAPTER MANAGER PACKET BUFFER DATA 1 REGISTER (AMPBD1R)                                                            | 73         |

|    | 4.3.13 ADAPTER MANAGER PACKET BUFFER DATA 2 REGISTER (AMPBD2R)                                                            | 73         |

|    | 4.3.14 ADAPTER MANAGER PACKET BUFFER DATA 3 REGISTER (AMPBD3R)                                                            | 74         |

|    | 4.3.15 ADAPTER MANAGER XMI LOW ADDRESS REGISTER (AMXMIL)                                                                  | 74         |

|    | 4.3.16 ADAPTER MANAGER XMI HIGH ADDRESS REGISTER (AMXMIH)                                                                 | <b>7</b> 5 |

|    | 4.3.17 ADAPTER MANAGER XMI DATA 0 REGISTER (AMXMIDOR)                                                                     | 75         |

|    | 4.3.18 ADAPTER MANAGER XMI DATA 1 REGISTER (AMXMID1R)                                                                     | 76         |

|    | 4.3.19 ADAPTER MANAGER XMI DATA 2 REGISTER (AMXMID2R)                                                                     | 76         |

|    | 4.3.20 ADAPTER MANAGER XMI DATA 3 REGISTER (AMXMID3R)                                                                     | 77         |

|    |                                                                                                                           | • •        |

| Ch | apter 5 AMI REGISTERS                                                                                                     | <b>7</b> 9 |

|    |                                                                                                                           |            |

|    | 5.1 ESP INTERFACE STATUS REGISTER (ESPIFSR)                                                                               | 81         |

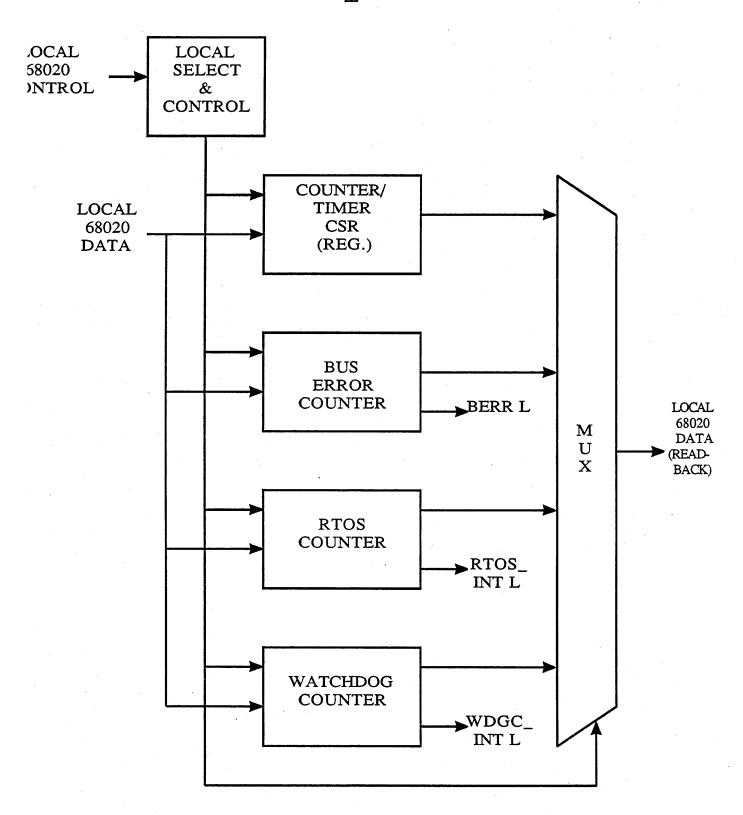

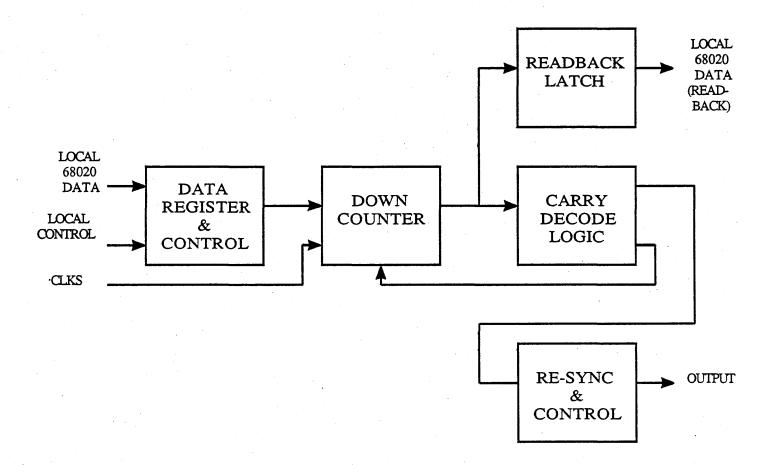

|    | 5.2 TIMERS AND COUNTERS                                                                                                   | 82         |

|    | 5.2.1 AMI WATCHDOG TIMER (WDTIMR)                                                                                         | 82         |

|    | 5.2.2 AMI RTOS TIMER (RTOSTIMR)                                                                                           | 82         |

|    | 5.2.3 COUNTER/TIMER CSR (CTCSR)                                                                                           | 83         |

|    | 5.2.4 BUS ERROR TIMER (BET)                                                                                               | 84         |

|    | 5.3 AMI GENERAL PURPOSE CSR (GPCSR)                                                                                       | 85         |

|    | 5.4 AMI EVENT STROBES                                                                                                     |            |

|    | 0.4 AIVII E VENT STRUDES                                                                                                  | 88         |

| 5.4.1 ADAPTER MANAGER TRANSMIT DONE STROBE (AMTDS) 5.4.2 ADAPTER MANAGER RECEIVE DONE STROBE (AMRDS) 5.4.3 SMT PRIORITY STROBE (SMTPS) 5.4.4 RTOS EVENT STROBE (RTOSES) 5.4.5 WATCHDOG TIMER CLEAR STROBE (WDTCLR)                                                                                                                                                         | . 89<br>. 89<br>. 90             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 5.5 AMI MISCELANEOUS REGISTERS                                                                                                                                                                                                                                                                                                                                             |                                  |

| 5.6 INTERRUPT AND INTERRUPT VECTOR REGISTERS 5.6.1 INTERRUPT CSR 1 (INTCSR1) 5.6.2 INTERRUPT CSR 2 (INTCSR2) 5.6.3 SOURCE INTERRUPT MASK REGISTER (SIMR) 5.6.4 IPL INTERRUPT MASK REGISTER (IPLIMR) 5.6.5 SOURCE INTERRUPT ENABLE REGISTER (SIER) 5.6.6 IPL INTERRUPT ENABLE REGISTER (IPLIER) 5.6.7 INTERRUPT SELF TEST REGISTER (INTST) 5.6.8 VECTOR REGISTERS (VECREGS) | 92<br>93<br>95<br>96<br>98<br>99 |

| Chapter 6 PMC REGISTERS                                                                                                                                                                                                                                                                                                                                                    | . 111                            |

| 6.1 PMC REGISTER SUMMARY                                                                                                                                                                                                                                                                                                                                                   | . 111                            |

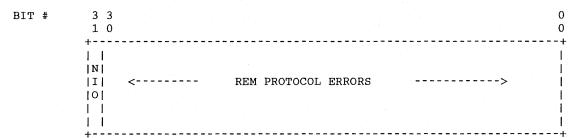

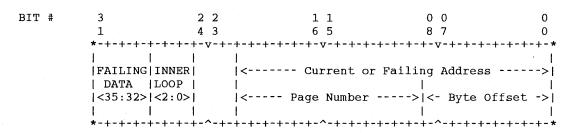

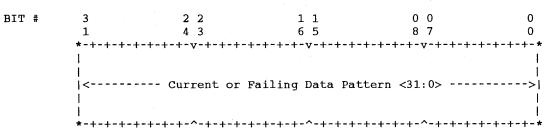

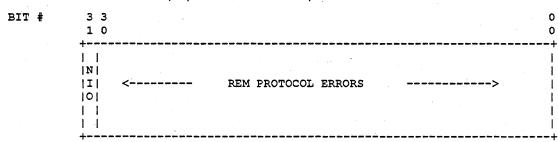

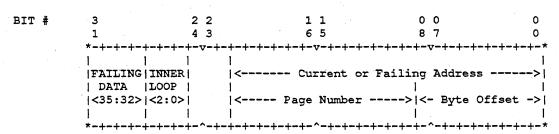

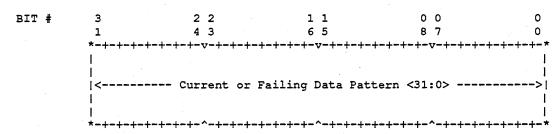

| 6.2 PMC REGISTER DEFINITIONS 6.2.1 PMC CONTROL AND STATUS REGISTER (CSR00) 6.2.2 PMC RAM PARITY ERROR REGISTER (CSR01) 6.2.3 PMC MASK AND INTERRUPT REGISTER (CSR02) 6.2.4 PMC PROTOCOL ERROR REGISTER (CSR03) 6.2.5 PMC PMT FAILING ADDRESS REGISTER (CSR07) 6.2.6 PMC PMT FAILING DATA REGISTER (CSR0B) 6.2.7 PMC PMT CONTROL AND STATUS REGISTER (CSR0F)                | 117<br>119<br>120<br>121<br>123  |

| Chapter 7 PARSER REGISTERS AND DATABASE                                                                                                                                                                                                                                                                                                                                    | 127                              |

| 7.1 CSR REGISTERS  7.1.1 CONTROL REGISTER 0 (CR0)  7.1.2 CONTROL REGISTER 1 (CR1)  7.1.3 STATUS REGISTERS  7.1.3.1 INTERRUPT CAUSE REGISTER (ICR)  7.1.3.2 INTERRUPT MASK REGISTER (IMR)  7.1.4 DATABASE UPDATE REGISTER(S)                                                                                                                                                | 127<br>129<br>130<br>130         |

| 7.2 PARSER DATABASE 7.2.1 FRAME CONTROL 7.2.2 DESTINATION ADDRESSES 7.2.3 FILTERING DATA FOR FC AND DA ONLY FILTERING 7.2.4 DESTINATION SERVICE ACCESS POINT (DSAPs) 7.2.5 PROTOCOL IDENTIFICATIONS (PIDS) 7.2.6 FILTERING DATA FOR FC DA AND LLC FILTERING                                                                                                                | 135<br>136<br>136<br>137<br>138  |

| 1.2.0 FIDIEGING DATA FUR FUNDA AND DIO FIDIEGING                                                                                                                                                                                                                                                                                                                           | . 158                            |

| 7    | 2.7 FILTERING DATA FOR A PARTICULAR USER FOR FC,DA AND LLC FILTERING |

|------|----------------------------------------------------------------------|

| 7    | 2.8 FILTERING DATA FOR PROMISCUOUS USER(S)                           |

| Chap | er 8 FDDI REGISTERS                                                  |

| Спар | i o FDDI REGISTERS                                                   |

| Chap | er 9 DEMFA MISCELLANEOUS FEATURES                                    |

| 9.   | DEMFA MODULE DATA INTEGRITY                                          |

| 9.   | FDDI MAINTENANCE SERVICES                                            |

| 9.   | INTERLOCKED OPERATION                                                |

| 9.4  | SELF TEST PROCEDURE                                                  |

| 9.   | STATUS LEDS                                                          |

|      |                                                                      |

| Chap |                                                                      |

|      | DEMFA MODULE SPECIFICATION                                           |

|      | 1.1.1 OVERVIEW                                                       |

|      | 10.1.2.1 DEMFA XMI MODULE                                            |

|      | 0.1.2.2 DEMFA ACTIVE BULKHEAD MODULE                                 |

| . 1  | .1.3 DEMFA CLOCK                                                     |

| 1    | .1.4 MECHANICAL DIMENSIONS                                           |

|      | 0.1.4.1 DEMFA XMI MODULE                                             |

| -    | .0.1.4.2 DEMFA ACTIVE BULKHEAD                                       |

|      | .1.6 NON-OPERATING ENVIRONMENT                                       |

|      | .1.7 MEANTIME BETWEEN FAILURES                                       |

|      |                                                                      |

| • •  | dix A DEMFA MODULE I/O PINNING                                       |

| A.   | XMI INTERFACE SIGNALS                                                |

| A.   | DEMFA ACTIVE BULKHEAD INTERFACE SIGNALS                              |

| Appe | dix B GATE ARRAY PINNING                                             |

|      | ESP GATE ARRAY PINNING                                               |

|      | PMC GATE ARRAY PINNING                                               |

|      | AMI GATE ARRAY PINNING                                               |

|      |                                                                      |

| В.   | PAR GATE ARRAY PINNING                                               |

| Appe | dix C ACTIVE BULKHEAD                                                |

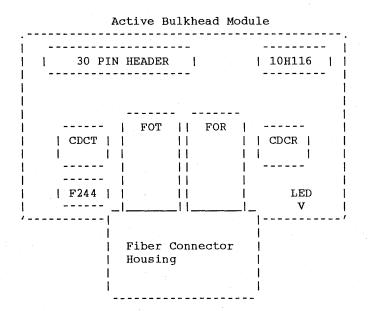

| C.   | INTRODUCTION                                                         |

| C    | RELATED DOCUMENTS                                                    |

| C.3.1 PARTSLIST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 168                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| O.S.I IMITODISI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 169                                                        |

| C.3.2 FEATURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 170                                                        |

| C.3.3 COMPONENT LOCATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 170                                                        |

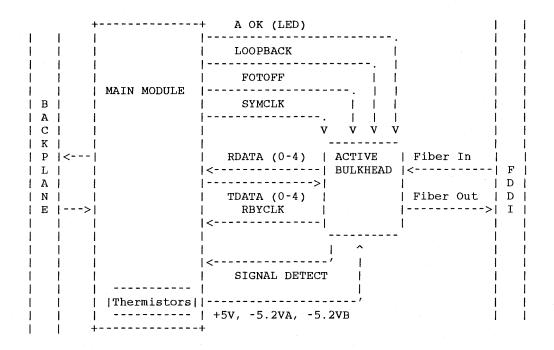

| C.3.4 DEMFA BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 171                                                        |

| C.3.5 SIGNAL DEFINITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 171                                                        |

| C.3.6 TESTABILITY FEATURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 172                                                        |

| C.3.7 OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 172                                                        |

| C.4 RECOMMENDED OPERATING CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 172                                                        |

| C.4.1 ENVIRONMENTAL CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                            |

| C.4.2 DC CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                            |

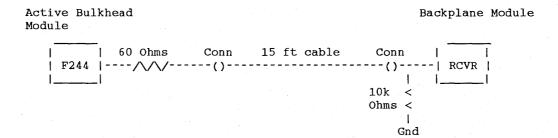

| C.4.3 TERMINATION REQUIREMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                            |

| C.5 DEVICE PINOUTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                            |

| C.5.1 CONNECTOR PINOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                            |

| C.5.2 CDCR PINOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                            |

| C.5.3 CDCT PINOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                            |

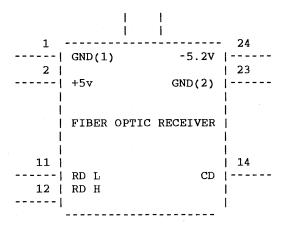

| C.5.4 FIBER OPTIC RCVR PINOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                            |

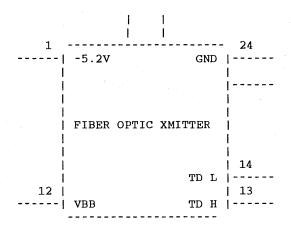

| C.5.5 FIBER OPTIC XMITTER PINOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                            |

| C.6 T2027 MODULE REQUIREMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 177                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                            |

| C.6 T2027 MODULE REQUIREMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                            |

| C.7 ISSUES/MISCELLANEOUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 178                                                        |

| C.7 ISSUES/MISCELLANEOUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 178                                                        |

| C.7 ISSUES/MISCELLANEOUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 178                                                        |

| C.7 ISSUES/MISCELLANEOUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 178<br>179                                                 |

| C.7 ISSUES/MISCELLANEOUS  Appendix D PARSER ALGORITHM  FIGURES  1 FDDI CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                            | 178<br>179                                                 |

| C.7 ISSUES/MISCELLANEOUS  Appendix D PARSER ALGORITHM  FIGURES  1 FDDI CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                            | 178 179 6                                                  |

| C.7 ISSUES/MISCELLANEOUS  Appendix D PARSER ALGORITHM  FIGURES  1 FDDI CONFIGURATION 2 XMI - FDDI ADAPTER BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                         | 178 179 6 10 14                                            |

| C.7 ISSUES/MISCELLANEOUS  Appendix D PARSER ALGORITHM  FIGURES  1 FDDI CONFIGURATION 2 XMI - FDDI ADAPTER BLOCK DIAGRAM 3 DEMFA PERFORMANCE 4 DEMFA RESPONSE TO XMI COMMANDS                                                                                                                                                                                                                                                                                                                                                    | 178 179 6 10 14 16                                         |

| C.7 ISSUES/MISCELLANEOUS  Appendix D PARSER ALGORITHM  FIGURES  1 FDDI CONFIGURATION 2 XMI - FDDI ADAPTER BLOCK DIAGRAM 3 DEMFA PERFORMANCE 4 DEMFA RESPONSE TO XMI COMMANDS                                                                                                                                                                                                                                                                                                                                                    | 178 179 6 10 14 16                                         |

| C.7 ISSUES/MISCELLANEOUS  Appendix D PARSER ALGORITHM  FIGURES  1 FDDI CONFIGURATION 2 XMI - FDDI ADAPTER BLOCK DIAGRAM 3 DEMFA PERFORMANCE 4 DEMFA RESPONSE TO XMI COMMANDS 5 DEMFA INITIATED XMI COMMANDS                                                                                                                                                                                                                                                                                                                     | 178 179 6 10 14 16 17                                      |

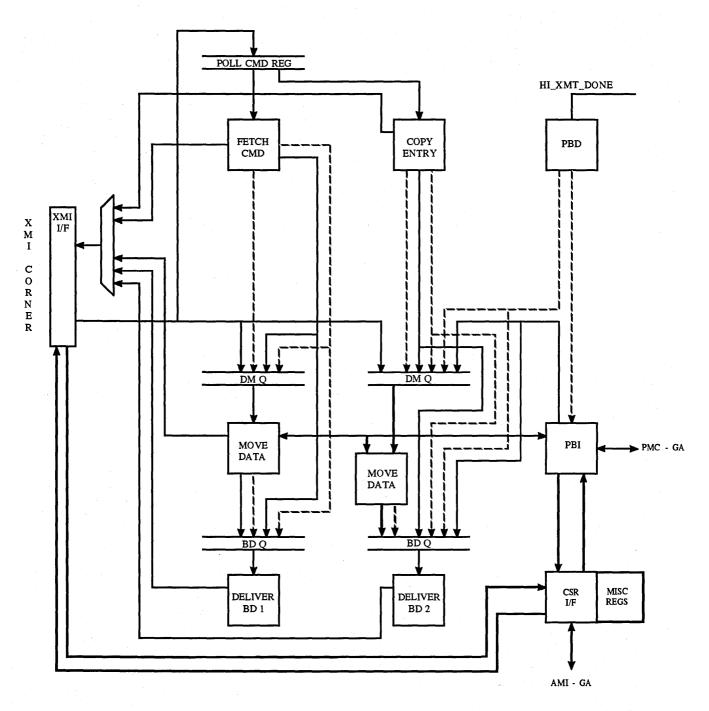

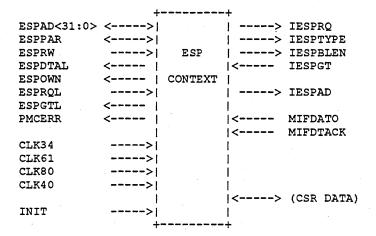

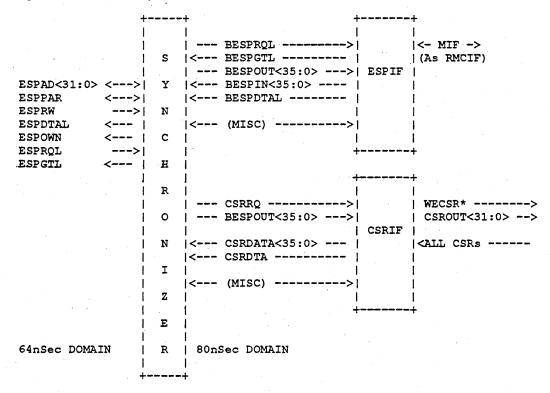

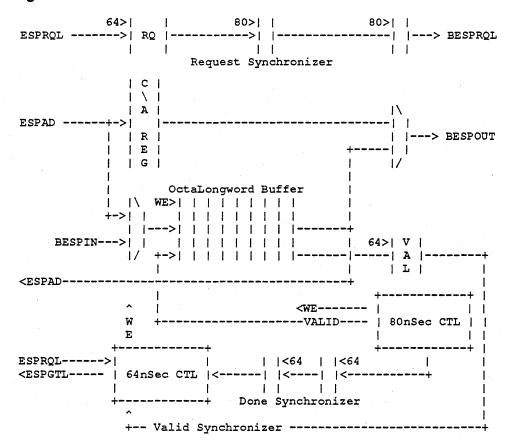

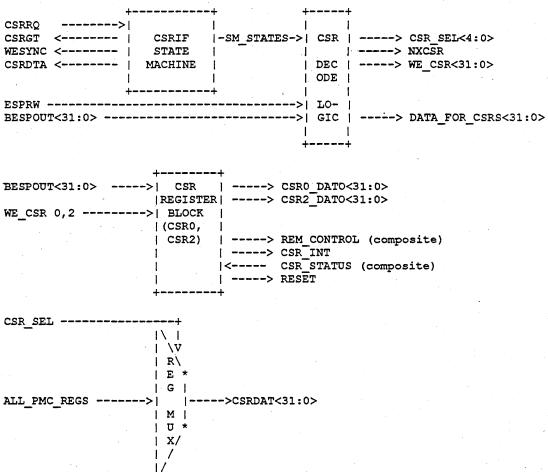

| C.7 ISSUES/MISCELLANEOUS  Appendix D PARSER ALGORITHM  FIGURES  1 FDDI CONFIGURATION 2 XMI - FDDI ADAPTER BLOCK DIAGRAM 3 DEMFA PERFORMANCE 4 DEMFA RESPONSE TO XMI COMMANDS 5 DEMFA INITIATED XMI COMMANDS 6 ESP FUNCTIONAL BLOCK DIAGRAM                                                                                                                                                                                                                                                                                      | 178 179 6 10 14 16 17 21                                   |

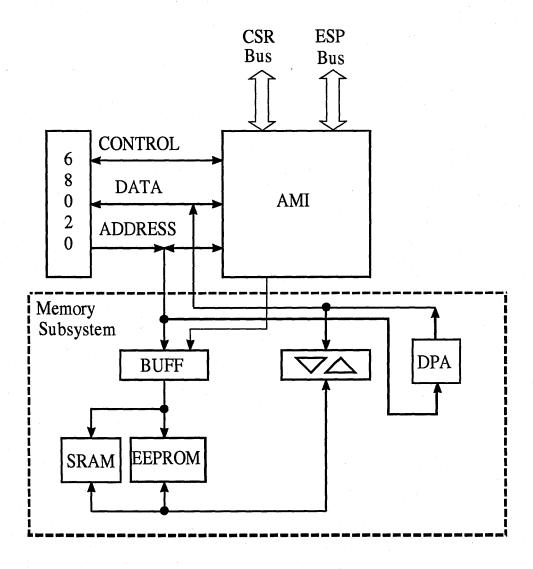

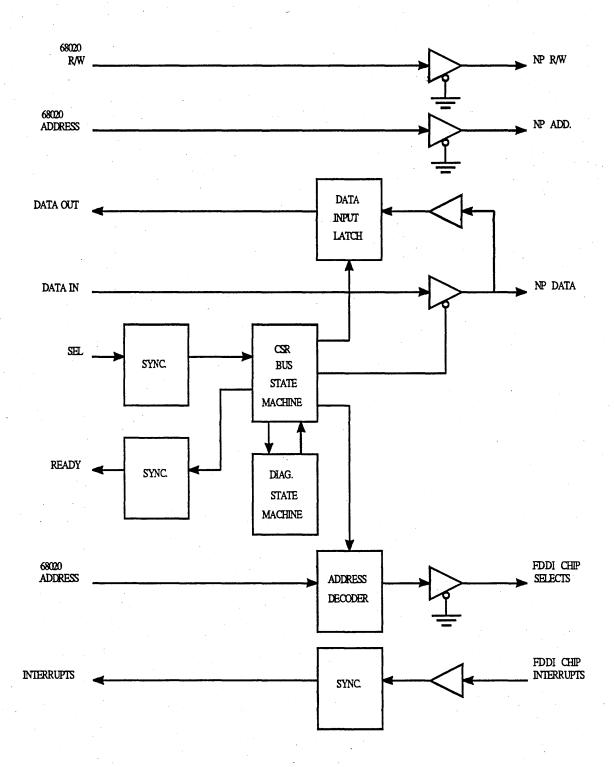

| C.7 ISSUES/MISCELLANEOUS  Appendix D PARSER ALGORITHM  FIGURES  1 FDDI CONFIGURATION 2 XMI - FDDI ADAPTER BLOCK DIAGRAM 3 DEMFA PERFORMANCE 4 DEMFA RESPONSE TO XMI COMMANDS 5 DEMFA INITIATED XMI COMMANDS 6 ESP FUNCTIONAL BLOCK DIAGRAM 7 68020 SUBSYSTEM - BLOCK DIAGRAM                                                                                                                                                                                                                                                    | 178 179 6 10 14 16 17 21 23 24                             |

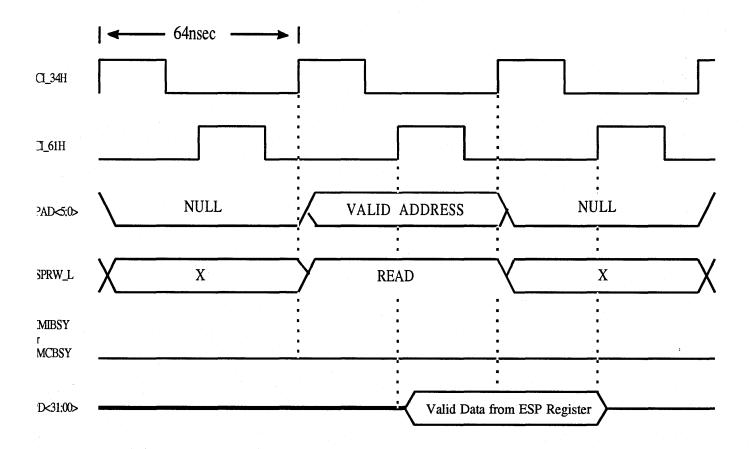

| C.7 ISSUES/MISCELLANEOUS  Appendix D PARSER ALGORITHM  FIGURES  1 FDDI CONFIGURATION 2 XMI - FDDI ADAPTER BLOCK DIAGRAM 3 DEMFA PERFORMANCE 4 DEMFA RESPONSE TO XMI COMMANDS 5 DEMFA INITIATED XMI COMMANDS 6 ESP FUNCTIONAL BLOCK DIAGRAM 7 68020 SUBSYSTEM - BLOCK DIAGRAM 8 ESP BUS READ                                                                                                                                                                                                                                     | 178 179 6 10 14 16 17 21 23 24 25                          |

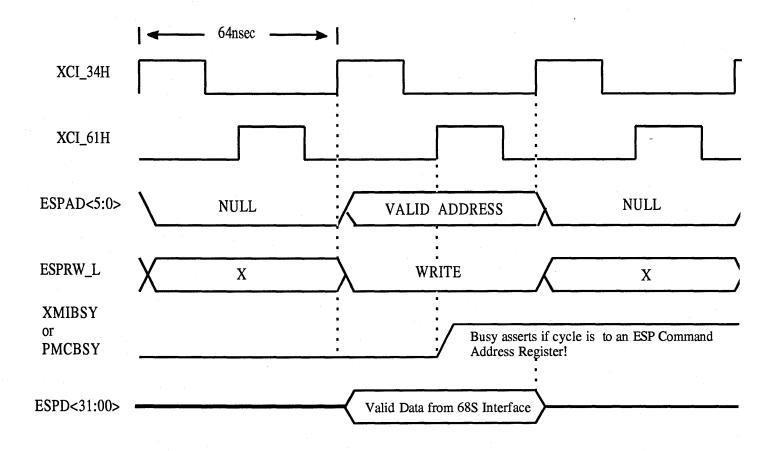

| C.7 ISSUES/MISCELLANEOUS  Appendix D PARSER ALGORITHM  FIGURES  1 FDDI CONFIGURATION 2 XMI - FDDI ADAPTER BLOCK DIAGRAM 3 DEMFA PERFORMANCE 4 DEMFA RESPONSE TO XMI COMMANDS 5 DEMFA INITIATED XMI COMMANDS 6 ESP FUNCTIONAL BLOCK DIAGRAM 7 68020 SUBSYSTEM - BLOCK DIAGRAM 8 ESP BUS READ 9 ESP BUS WRITE                                                                                                                                                                                                                     | 178 179 6 10 14 16 17 21 23 24 25                          |

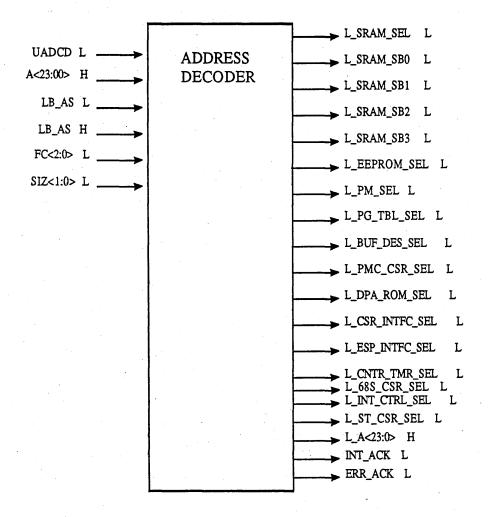

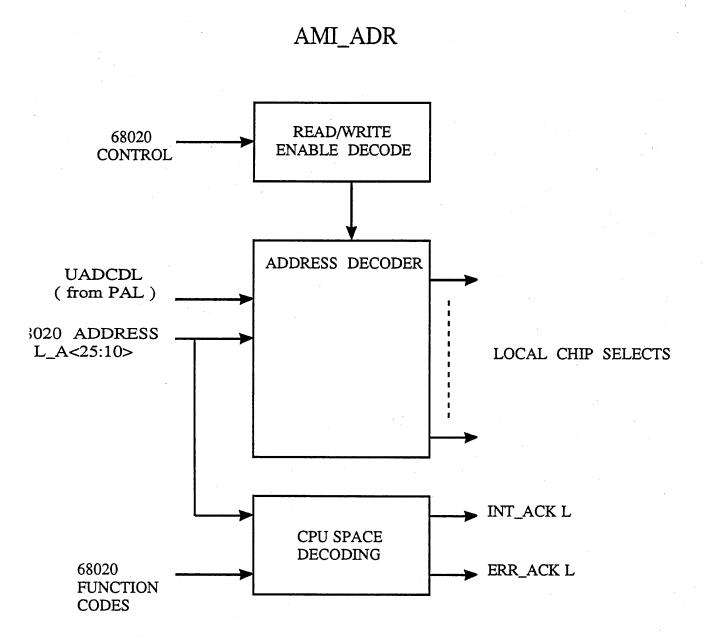

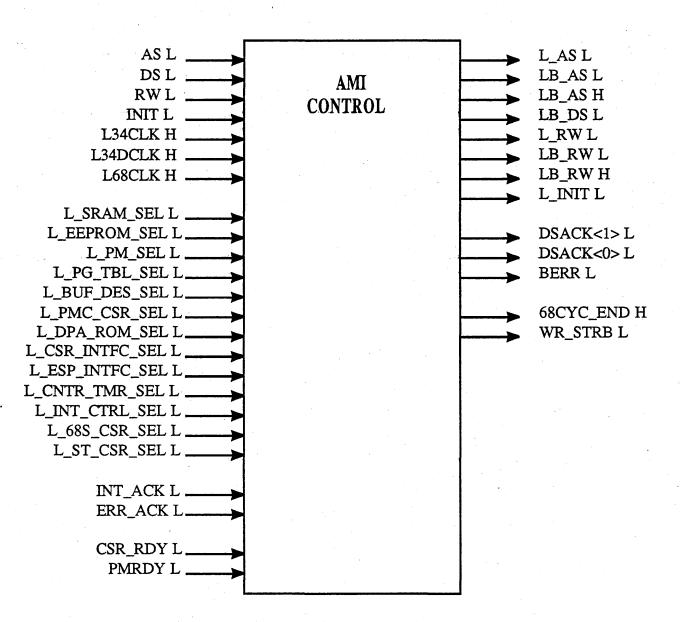

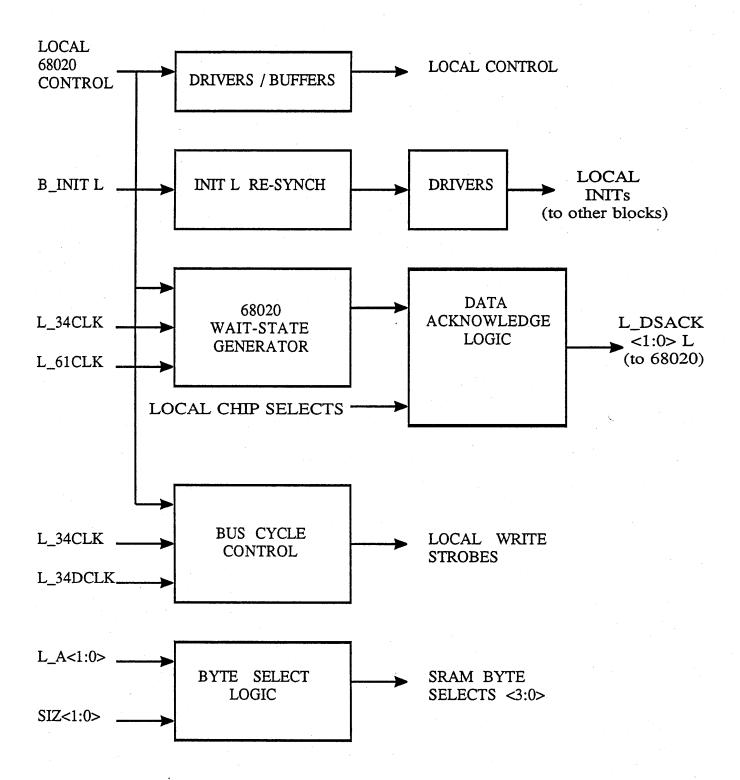

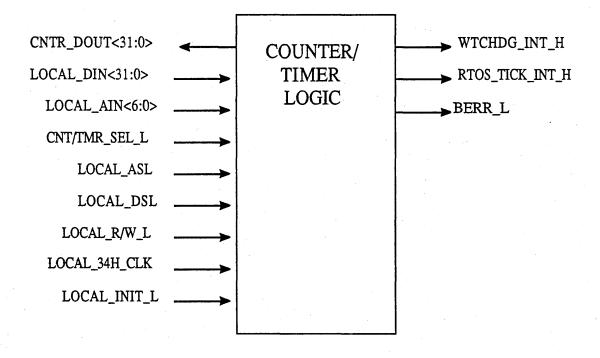

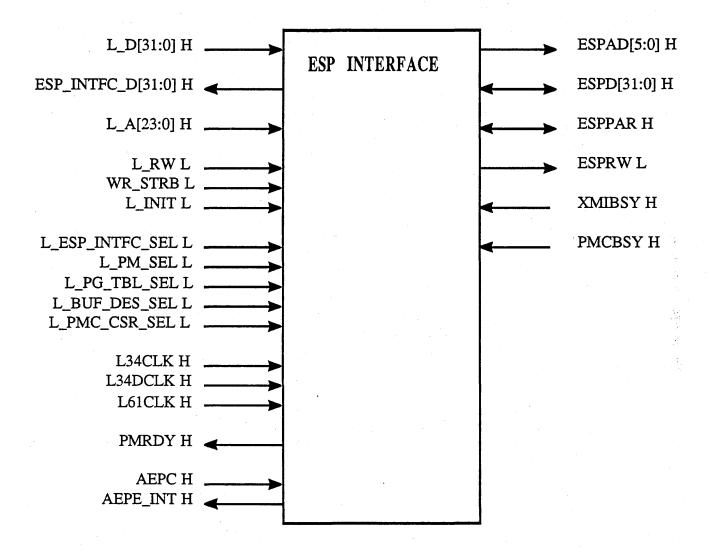

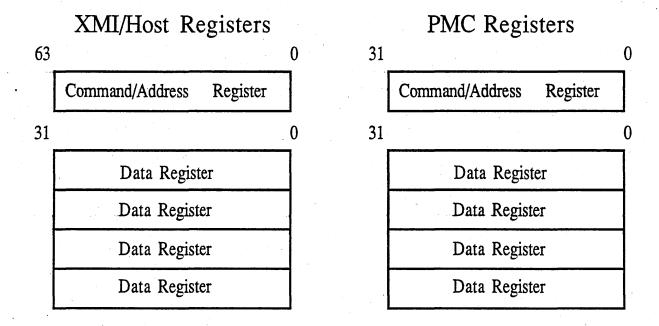

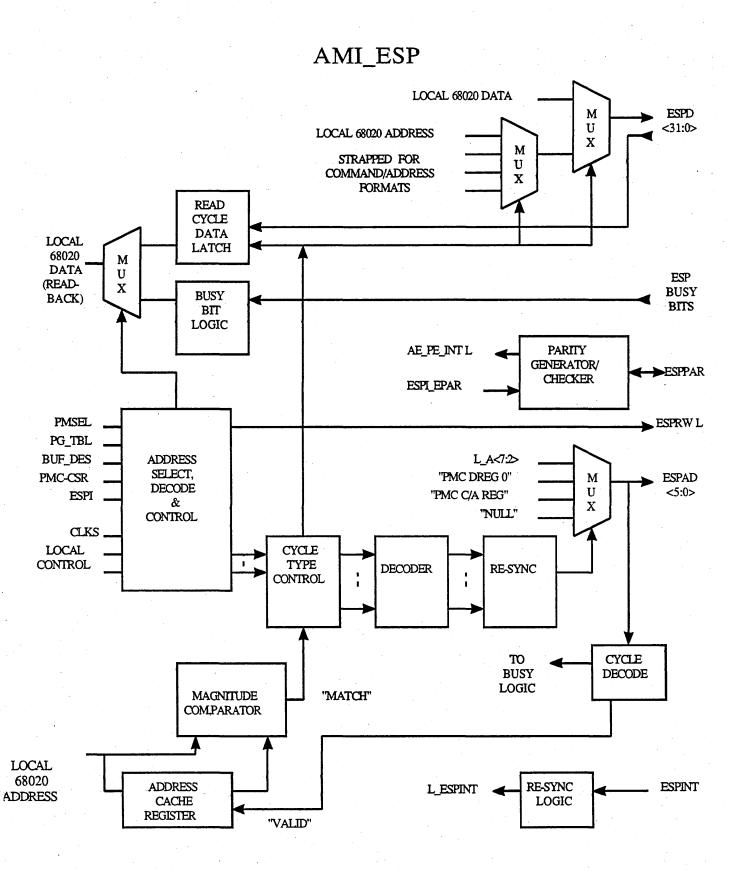

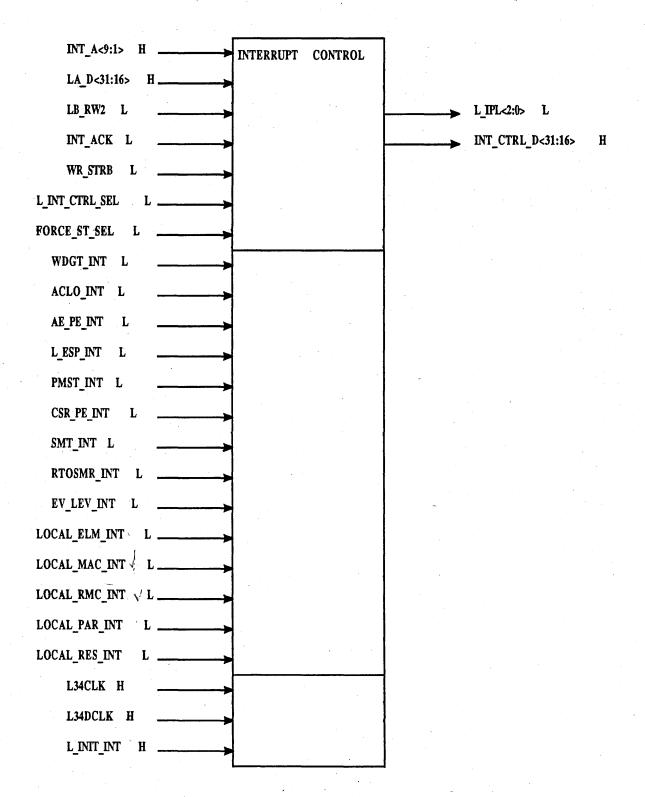

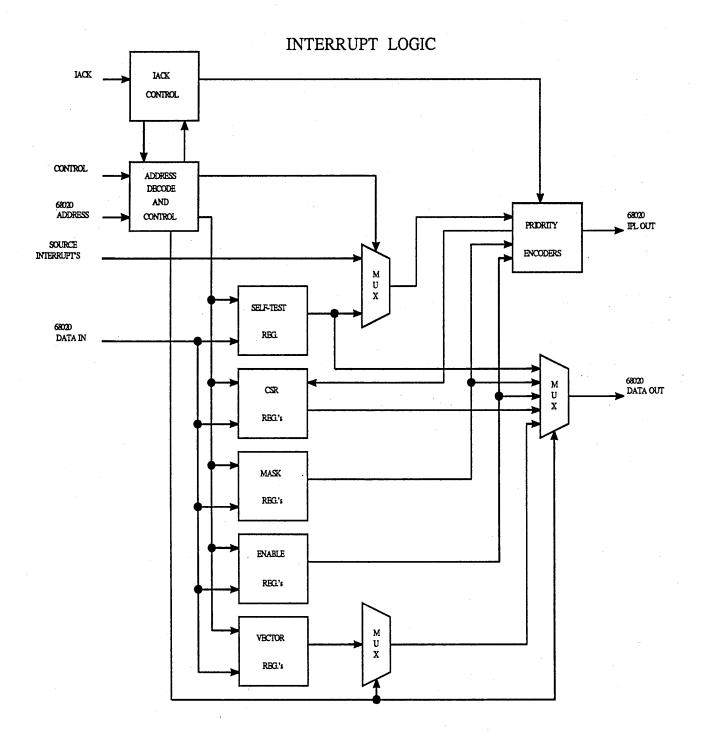

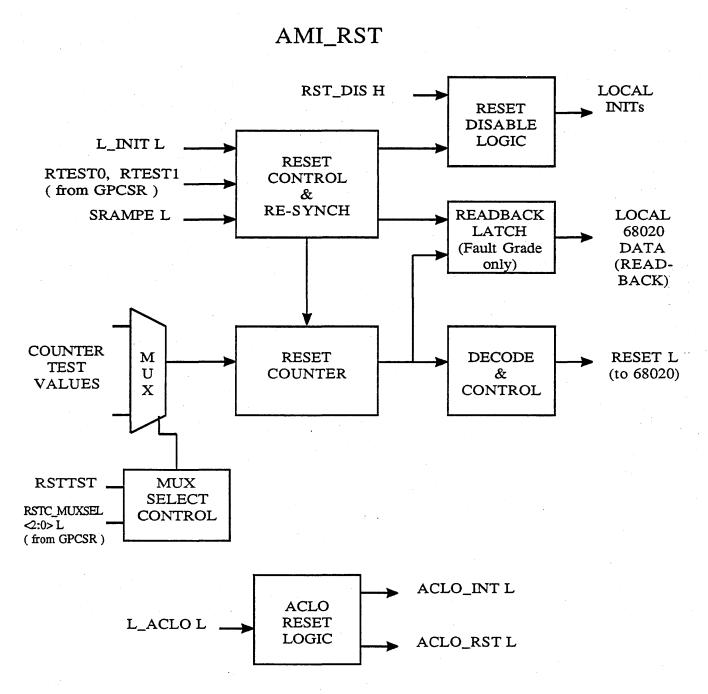

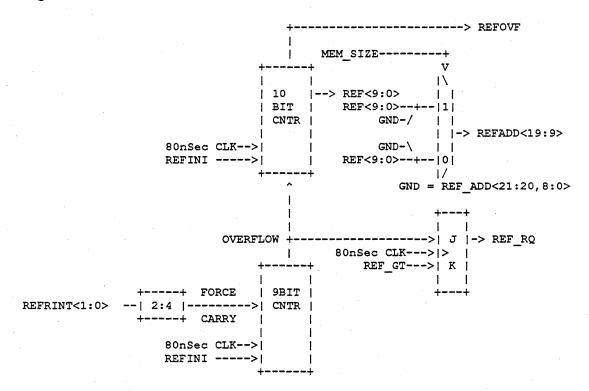

| C.7 ISSUES/MISCELLANEOUS  Appendix D PARSER ALGORITHM  FIGURES  1 FDDI CONFIGURATION 2 XMI - FDDI ADAPTER BLOCK DIAGRAM 3 DEMFA PERFORMANCE 4 DEMFA RESPONSE TO XMI COMMANDS 5 DEMFA INITIATED XMI COMMANDS 6 ESP FUNCTIONAL BLOCK DIAGRAM 7 68020 SUBSYSTEM - BLOCK DIAGRAM 8 ESP BUS READ 9 ESP BUS WRITE 10 AMI BLOCK DIAGRAM                                                                                                                                                                                                | 178 179 6 10 14 16 17 21 23 24 25 26 31                    |

| C.7 ISSUES/MISCELLANEOUS  Appendix D PARSER ALGORITHM  FIGURES  1 FDDI CONFIGURATION 2 XMI - FDDI ADAPTER BLOCK DIAGRAM 3 DEMFA PERFORMANCE 4 DEMFA RESPONSE TO XMI COMMANDS 5 DEMFA INITIATED XMI COMMANDS 6 ESP FUNCTIONAL BLOCK DIAGRAM 7 68020 SUBSYSTEM - BLOCK DIAGRAM 8 ESP BUS READ 9 ESP BUS WRITE 10 AMI BLOCK DIAGRAM 11 PACKET MEMORY CONTROLLER - FUNCTIONAL BLOCK DIAGRAM                                                                                                                                         | 178 179 6 10 14 16 21 23 24 25 26 31 33                    |

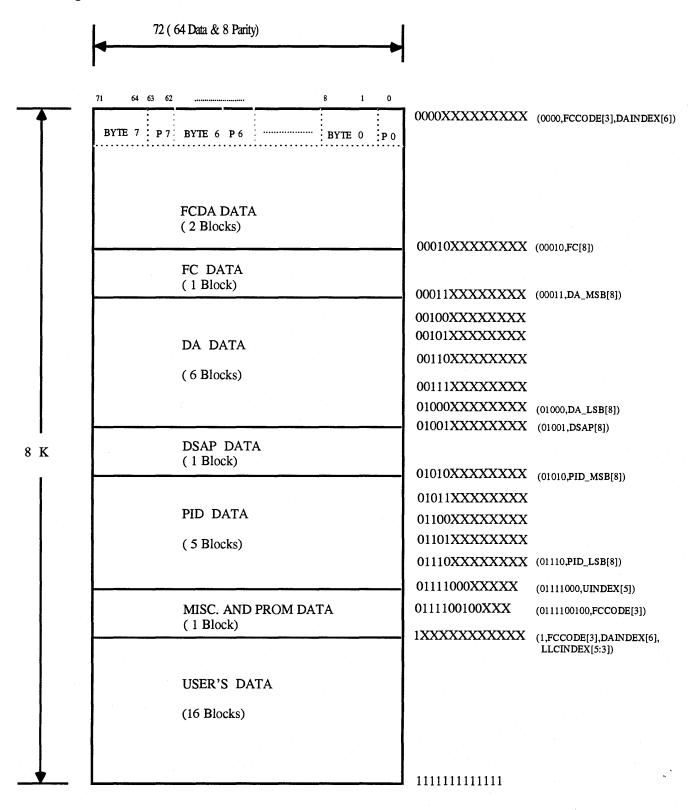

| C.7 ISSUES/MISCELLANEOUS  Appendix D PARSER ALGORITHM  FIGURES  1 FDDI CONFIGURATION 2 XMI - FDDI ADAPTER BLOCK DIAGRAM 3 DEMFA PERFORMANCE 4 DEMFA RESPONSE TO XMI COMMANDS 5 DEMFA INITIATED XMI COMMANDS 6 ESP FUNCTIONAL BLOCK DIAGRAM 7 68020 SUBSYSTEM - BLOCK DIAGRAM 8 ESP BUS READ 9 ESP BUS WRITE 10 AMI BLOCK DIAGRAM 11 PACKET MEMORY CONTROLLER - FUNCTIONAL BLOCK DIAGRAM 12 MEMORY ALLOCATION                                                                                                                    | 178 179 6 10 14 16 17 21 23 24 25 26 31 33                 |

| C.7 ISSUES/MISCELLANEOUS  Appendix D PARSER ALGORITHM  FIGURES  1 FDDI CONFIGURATION 2 XMI - FDDI ADAPTER BLOCK DIAGRAM 3 DEMFA PERFORMANCE 4 DEMFA RESPONSE TO XMI COMMANDS 5 DEMFA INITIATED XMI COMMANDS 6 ESP FUNCTIONAL BLOCK DIAGRAM 7 68020 SUBSYSTEM - BLOCK DIAGRAM 8 ESP BUS READ 9 ESP BUS WRITE 10 AMI BLOCK DIAGRAM 11 PACKET MEMORY CONTROLLER - FUNCTIONAL BLOCK DIAGRAM 12 MEMORY ALLOCATION 13 FDDI CHIP SET                                                                                                   | 178 179 6 10 14 16 17 21 23 24 25 26 31 33 36 40           |

| C.7 ISSUES/MISCELLANEOUS  Appendix D PARSER ALGORITHM  FIGURES  1 FDDI CONFIGURATION 2 XMI - FDDI ADAPTER BLOCK DIAGRAM 3 DEMFA PERFORMANCE. 4 DEMFA RESPONSE TO XMI COMMANDS. 5 DEMFA INITIATED XMI COMMANDS. 6 ESP FUNCTIONAL BLOCK DIAGRAM. 7 68020 SUBSYSTEM - BLOCK DIAGRAM. 8 ESP BUS READ. 9 ESP BUS WRITE. 10 AMI BLOCK DIAGRAM. 11 PACKET MEMORY CONTROLLER - FUNCTIONAL BLOCK DIAGRAM. 12 MEMORY ALLOCATION. 13 FDDI CHIP SET. 14 PARSER SUBSYSTEM IN DEMFA.                                                          | 178 179 6 10 14 16 21 23 24 25 26 31 33 36 40 41           |

| Appendix D PARSER ALGORITHM  FIGURES  1 FDDI CONFIGURATION 2 XMI - FDDI ADAPTER BLOCK DIAGRAM 3 DEMFA PERFORMANCE 4 DEMFA RESPONSE TO XMI COMMANDS 5 DEMFA INITIATED XMI COMMANDS 6 ESP FUNCTIONAL BLOCK DIAGRAM 7 68020 SUBSYSTEM - BLOCK DIAGRAM 8 ESP BUS READ 9 ESP BUS WRITE 10 AMI BLOCK DIAGRAM 11 PACKET MEMORY CONTROLLER - FUNCTIONAL BLOCK DIAGRAM 12 MEMORY ALLOCATION 13 FDDI CHIP SET 14 PARSER SUBSYSTEM IN DEMFA 15 FORWARDING VECTOR                                                                           | 178 179 6 10 14 16 17 21 23 24 25 26 31 33 36 40 41        |

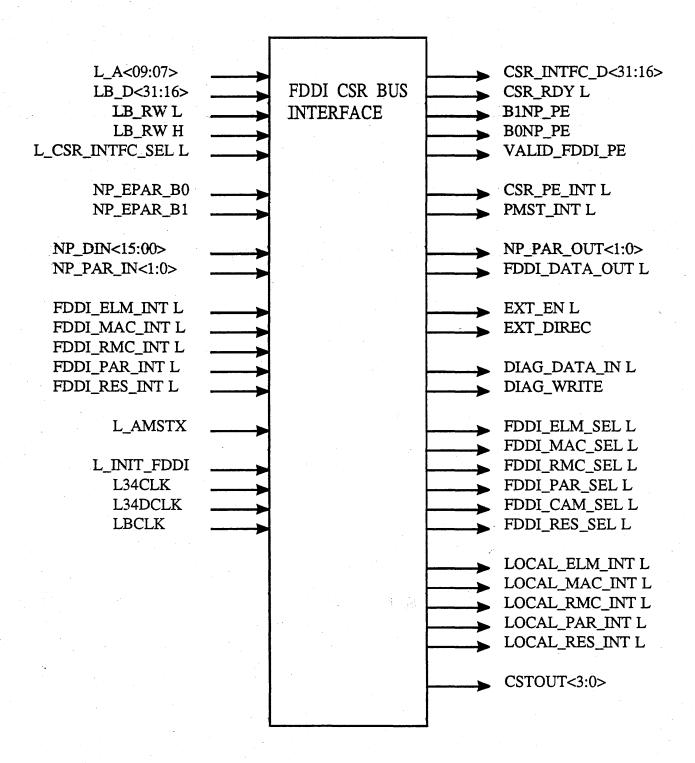

| Appendix D PARSER ALGORITHM  FIGURES  1 FDDI CONFIGURATION 2 XMI - FDDI ADAPTER BLOCK DIAGRAM 3 DEMFA PERFORMANCE 4 DEMFA RESPONSE TO XMI COMMANDS 5 DEMFA INITIATED XMI COMMANDS 6 ESP FUNCTIONAL BLOCK DIAGRAM 7 68020 SUBSYSTEM - BLOCK DIAGRAM 8 ESP BUS READ 9 ESP BUS WRITE 10 AMI BLOCK DIAGRAM 11 PACKET MEMORY CONTROLLER - FUNCTIONAL BLOCK DIAGRAM 12 MEMORY ALLOCATION 13 FDDI CHIP SET 14 PARSER SUBSYSTEM IN DEMFA 15 FORWARDING VECTOR 16 PARSER SUBSYSTEM BLOCK DIAGRAM                                         | 178 179 6 10 14 16 23 24 25 26 31 33 36 40 41 80           |

| C.7 ISSUES/MISCELLANEOUS  Appendix D PARSER ALGORITHM  FIGURES  1 FDDI CONFIGURATION 2 XMI - FDDI ADAPTER BLOCK DIAGRAM 3 DEMFA PERFORMANCE 4 DEMFA RESPONSE TO XMI COMMANDS 5 DEMFA INITIATED XMI COMMANDS 6 ESP FUNCTIONAL BLOCK DIAGRAM 7 68020 SUBSYSTEM - BLOCK DIAGRAM 8 ESP BUS READ 9 ESP BUS WRITE 10 AMI BLOCK DIAGRAM 11 PACKET MEMORY CONTROLLER - FUNCTIONAL BLOCK DIAGRAM 12 MEMORY ALLOCATION 13 FDDI CHIP SET 14 PARSER SUBSYSTEM IN DEMFA 15 FORWARDING VECTOR 16 PARSER SUBSYSTEM BLOCK DIAGRAM 17 MEMORY MAP | 178 179 6 10 14 16 21 23 24 25 26 31 33 36 40 41 44 80 142 |

| 21            | ESP GATE ARRAY PIN DIAGRAM                                   | <b>16</b> 0 |

|---------------|--------------------------------------------------------------|-------------|

| 22            | PMC GATE ARRAY PIN DIAGRAM                                   | 162         |

| 23            | AMI GATE ARRAY PIN DIAGRAM                                   | 164         |

| 24            | PARSER GATE ARRAY PIN DIAGRAM                                | 166         |

| 25            | XMI to FDDI Adaptor Module Component Location                | 170         |

| 26            | Block Diagram of the XMI Node, Active Bulkhead, and FDDI     | 171         |

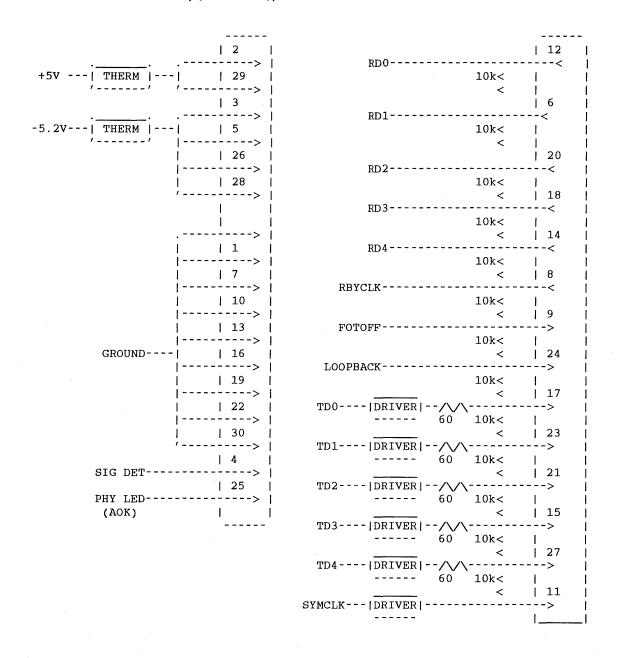

| 27            | Block Diagram of the CDCR Connections                        | 174         |

| 28            | Block Diagram of the CDCT Connections                        | 175         |

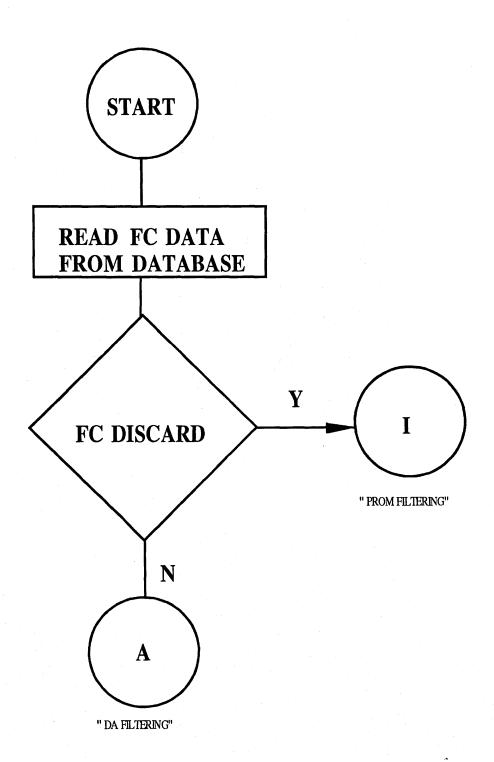

| 29            | THE PARSING ALGORITHM - FC Filtering                         | 180         |

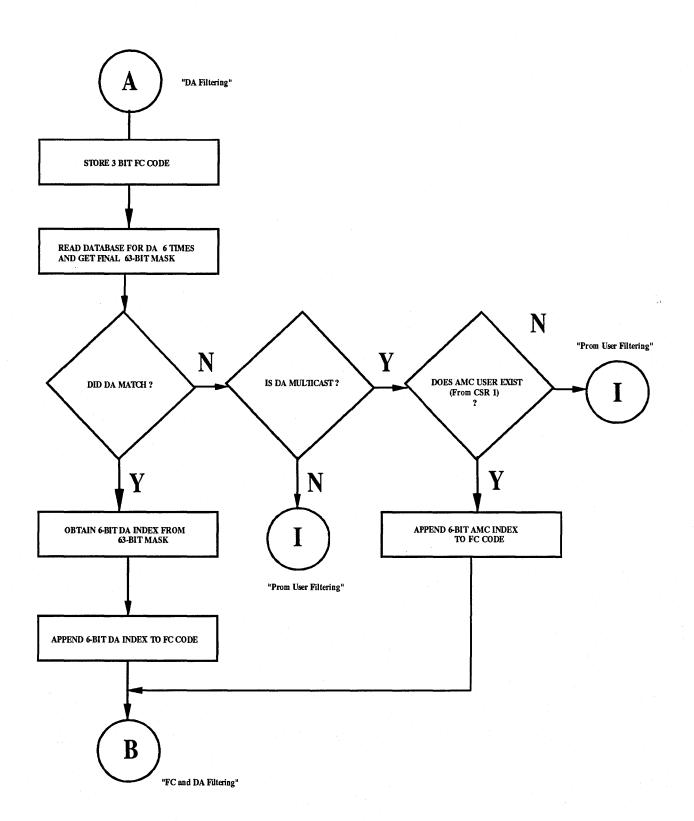

| 30            | THE PARSING ALGORITHM (CONTD.) - DA Filtering                | 181         |

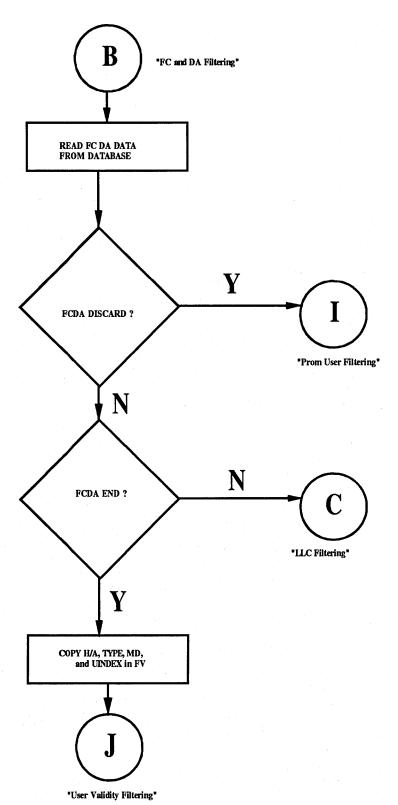

| 31            | THE PARSING ALGORITHM (CONTD.) - FCDA Filtering              | 182         |

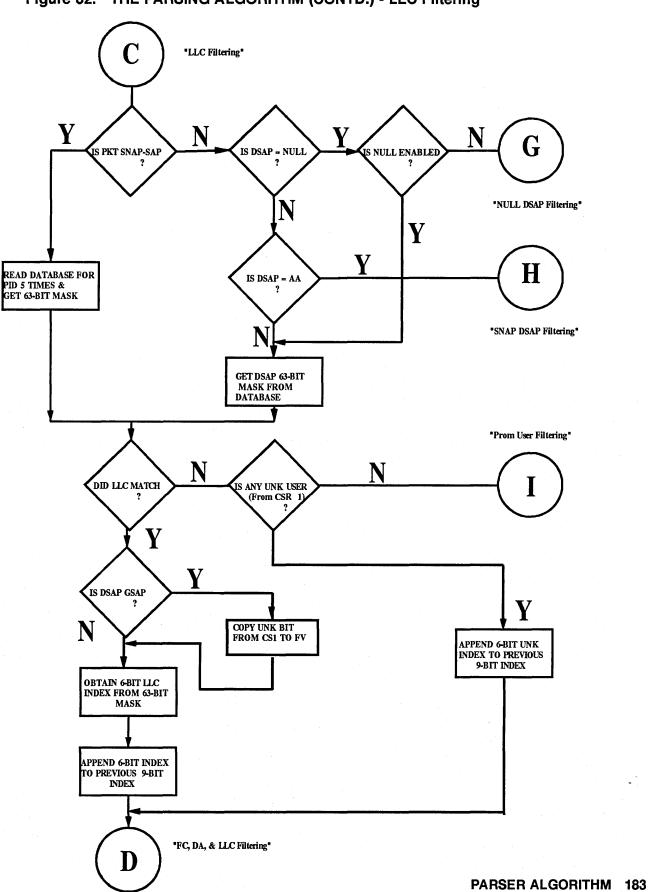

| 32            | THE PARSING ALGORITHM (CONTD.) - LLC Filtering               | 183         |

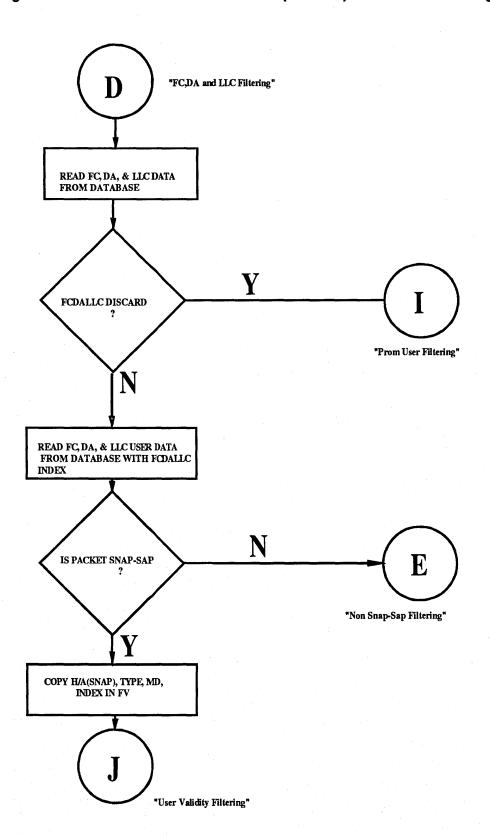

| 33            | THE PARSING ALGORITHM (CONTD.) - FCDALLC Filtering           | 184         |

| 34            | THE PARSING ALGORITHM (CONTD.) - Non SNAP SAP Filtering      | 185         |

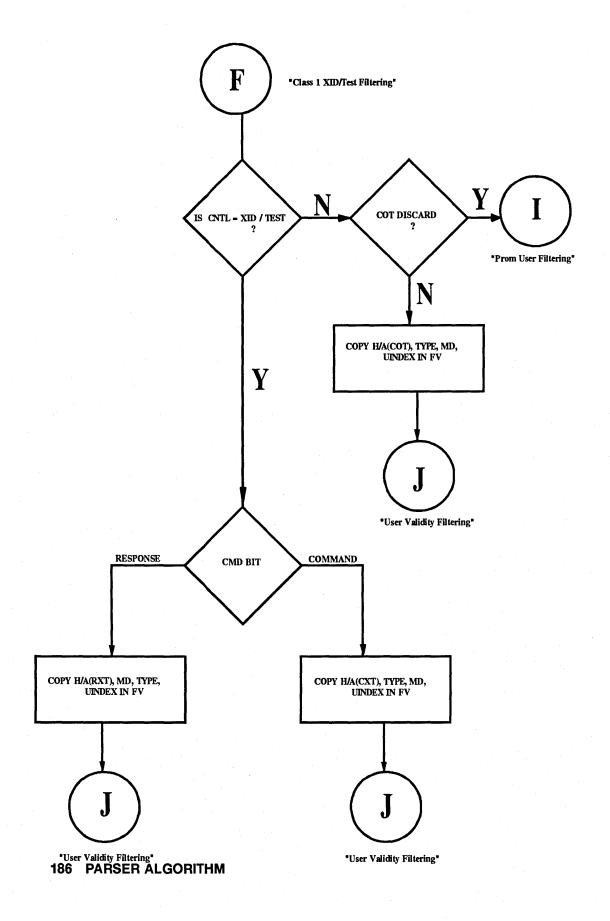

| 35            | THE PARSING ALGORITHM (CONTD.) - Class1 XID/TEST Filtering   | 186         |

| 36            | THE PARSING ALGORITHM (CONTD.) - NULL DSAP Filtering         | 187         |

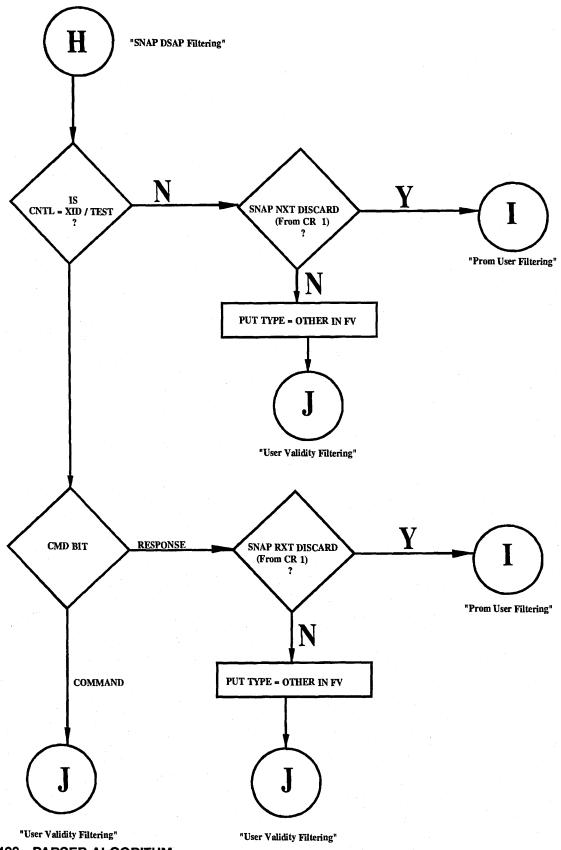

| 37            | THE PARSING ALGORITHM (CONTD.) - SNAP DSAP Filtering         | 188         |

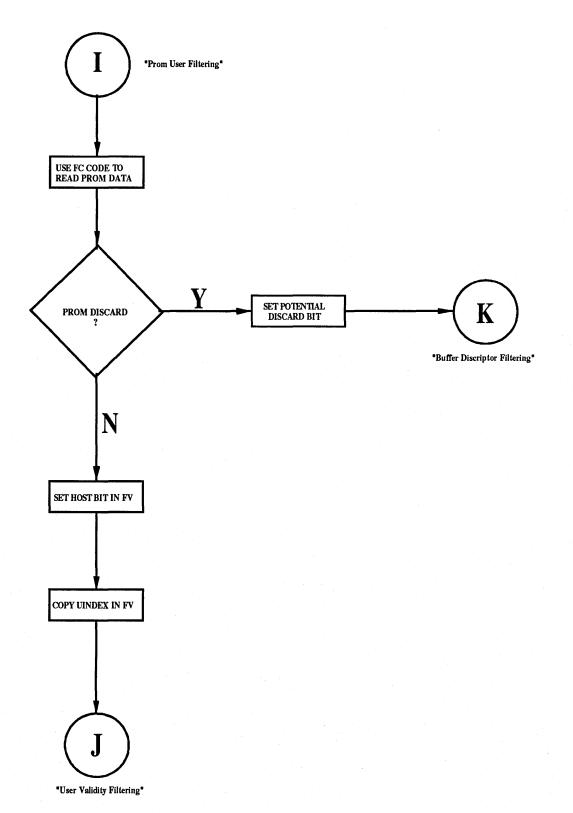

| 38            | THE PARSING ALGORITHM (CONTD.) - Promiscuous User Filtering  | 189         |

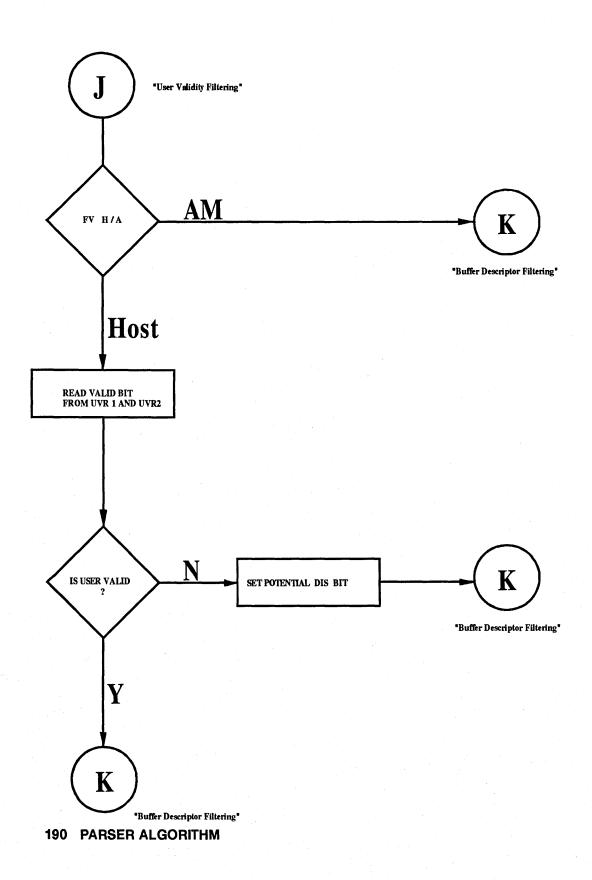

| 39            | THE PARSING ALGORITHM (CONTD.) - User Validity Filtering     | 190         |

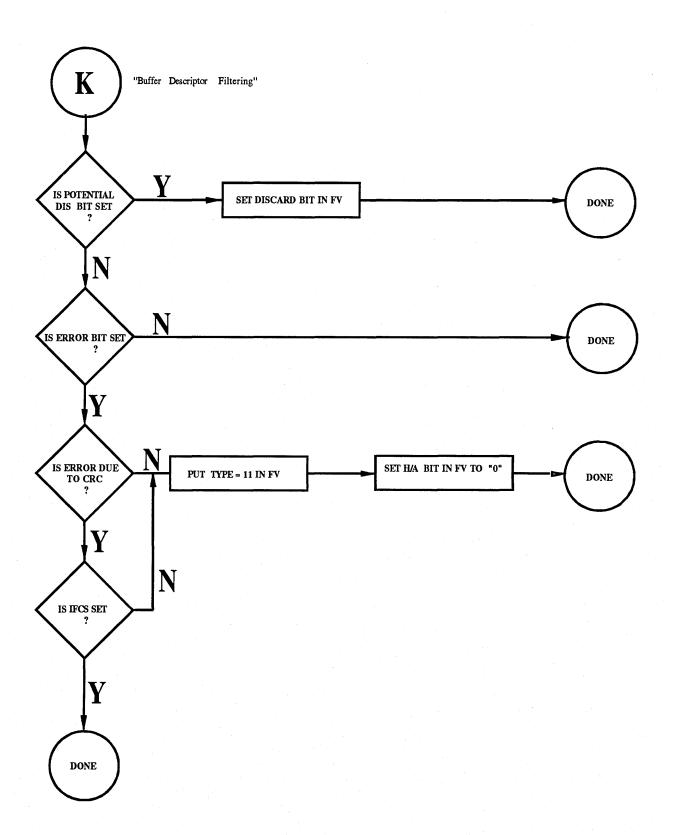

| 40            | THE PARSING ALGORITHM (CONTD.) - Buffer Descriptor Filtering | 191         |

|               |                                                              |             |

| <b>TABLES</b> |                                                              |             |

| 1             | DEMFA PERFORMANCE                                            | 12          |

| 2             | PBI INTERFACE COMMAND/ADDRESS BIT DEFINITIONS FOR DATA       |             |

|               | MOVER                                                        | 18          |

| 3             | PBI INTERFACE COMMAND/ADDRESS BIT DEFINITIONS FOR ADAPTER    |             |

|               | MANAGER                                                      | 18          |

| 4             | INTERRUPT STRUCTURE                                          | 28          |

| 5             | COLOR AND RING ASSIGNMENTS                                   | 32          |

| 6             | PMC CSR REGISTER ALLOCATION                                  | 111         |

| 7             | DEMFA MODULE STATUS LEDS                                     | 147         |

| 8             | ELECTRICAL CHARACTERISTICS                                   | 149         |

| 9             | ELECTRICAL CHARACTERISTICS                                   | 149         |

| 10            | 773 FT 3 FOR FT TO       |             |

| 11            | XMI MODULE DIMENSIONS                                        | 150         |

| 11            | OPERATING ENVIRONMENTAL REQUIREMENTS                         | 150         |

| 12            | OPERATING ENVIRONMENTAL REQUIREMENTS                         | 150<br>151  |

|               | OPERATING ENVIRONMENTAL REQUIREMENTS                         | 150         |

### CHAPTER 1

### DEMFA INTRODUCTION

This document contains the functional specification of the DEMFA, an XMI to FDDI adapter, being a description of the inherent funtionality contained within the boundary of the XMI bus and the FDDI physical medium (optical fiber). The reader of this document is presumed to have some knowledge of the DEMFA Port Architecture. No attempt is made here to duplicate Port Architecture except as it directly relates to the hardware, eg, the Host visible register set. However, a high level understanding of the DEMFA functionality may be gotten from Chapter 2, the executive summary, where no prior knowledge is assumed.

This document is intended as volume 1 of a 2 volume set, the second volume being the DEMFA Firmware Functional Specification. The Firmware Specification includes descriptions of (among others) Adapter Initialization, Adapter States, Frame and Command processing and updating firmware. These descriptions will not be duplicated in this volume.

Included for completeness in Appendix C of this volume is the Functional Specification of the active bulkhead.

### INTENDED AUDIENCE

This document is intended for the following audiences:

- Designers of the DEMFA Functional firmware

- Designers of the DEMFA Self\_Test firmware

- Designers of other DEMFA diagnostics

- Manufacturing

- CSSE

- 'Casual' Readers

### 1.2 GOALS AND NON-GOALS

It is the goal of this document to satisfy the needs of the above audiences. As such this document will contain:

- An executive summary for those readers only interested in a product overview

- A high level summary of the Port Functionality

- A high level functional description to give the reader an understanding of the major imbedded functions and their relationships.

- An exhaustive description of the Host visible registers

- An exhaustive description of the internal microprocessor visible registers

- Descriptions of the gate arrays sufficient for the intended audiences

- A summary of the Maintenance Features

- A summary of how data integrity is maintained and how errors are handled.

- The DEMFA module specification

- The Active Bulkhead specification

- Appendices containing other miscellaneous information

- Some information concerning performance

### It is *NOT* the goal of this document to:

- Provide details of the DEMFA Port Specification

- Provide descriptions of FDDI Registers

- Provide design details

- Provide details of any other 'non-functionality', eg: manufacturing, schedule, module layout, etc, etc...

### 1.3 ASSOCIATED DOCUMENTS

- DIGITAL: DEMFA Port Specification, Revision 2.0

- DIGITAL: DEMNA Port Specification, Revision 4.0, Jan-1989.

- DIGITAL: XI Data Link Architecture Specification, Version X0.1.2, Apr-1987 (Will eventually include FDDI)

- DIGITAL: Calypso Memory Interconnect (XMI), Revision 1.4, 28-Nov-1988.

- DIGITAL Network Architecture CSMA/CD Data Link Functional Specification, T2.0.0, 31-Mar-1989.

- DIGITAL NI Node Product Architecture Specification, T2.0.1, 11-Nov-1988. (Will eventually include FDDI)

- DIGITAL Network Architecture Maintenance Operations Functional Specification, T4.0.0, 28-Jan-1988.

- ANSI FDDI PMD Standard, Rev 7.3, May 20, 1988.

- ANSI FDDI PHY Standard, Rev 15, September 1, 1987.

- ANSI FDDI MAC Standard, Rev DRAFT 7/1/87.

- ANSI FDDI SMT Standard, Rev 3.0, August 1, 1987.

- IEEE STD 802.2 Logical Link Control, 1985.

- DIGITAL: Clock and Data Conversion Transmitter Chip Specification, Rev 1.1, OCT 22, 1987.

- DIGITAL: Clock and Data Conversion Receiver Chip Specification, Rev 1.2, FEB 8, 1988.

- DIGITAL: Elasticity Buffer and Link Management Chip Specification, (in progress)

- DIGITAL: Media Access Control Chip Specification, Rev 1.1, NOV. 6, 1987.

- DIGITAL: Ring Memory Controller Chip Specification, Rev 2.0, Nov 4, 1988.

- DIGITAL: ESP Gate Array Design Specification, (in progress)

- DIGITAL: PMC Gate Array Design Specification, (in progress)

- DIGITAL: AMI Gate Array Design Specification, (in progress)

- DIGITAL: PAR Gate Array Design Specification, (in progress)

- DIGITAL: DEMFA Firmware Functional Specification, Version X1.2

- DIGITAL: DEMFA Firmware Design and Test Specification (in progress)

- DIGITAL: DEMFA Performance Simulation Studies Document (in progress)

### 1.4 TERMINOLOGY

Some terms used in this document are defined here.

- FRAME and PACKET. Within this document these terms are used somewhat interchangeably. This is not strictly correct. In general, references to 'Packet' are more correctly 'Frame'.

- FDDI. Fiber Distributed Data Interface. The ANSI Specifications.

- 802. 802 refers to the class of local area networks defined in IEEE 802 specifications.

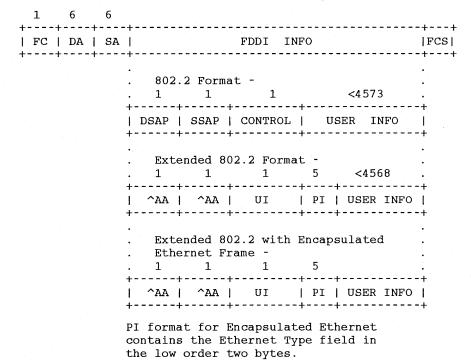

- 802 SAP. An FDDI frame using 802.2 connectionless data link layer would contain, as the first information bytes, destination and source identifiers (each called a SAP, a Service Access Point), one byte control field followed by the user data. The source SAP(SSAP) identifies the user sending the frame. The destination SAP(DSAP) identifies the user to receive the frame.

- 802 SNAP. In the case where the destination and source SAPS consists of alternating ones and zeros, AA(HEX), and the control is UI (Unnumbered Information) this is called the SNAP SAP(Subnet Acess Protocol SAP). This implies an additional five byte protocol identifier(PI) field will follow the control field. The five byte PI field identifies the particular user.

- Adapter. The adapter is the hardware and firmware entity which comprises the DEMFA module. It provides an interface between Host system Port Driver/Memory resident data structures and the FDDI ring via the XMI bus.

- Port. The port is the entity on the adapter which embodies the port architecture. It performs actions requested of it by the port driver.

- Port driver. The port driver is the software running on the host processor which directs the operation of the port. It processes tranmit and receive request from users of the operating system(or the operating itself).

- Host Ring. An Host ring is the type of data structure used to communicate buffer information between the port driver and the port. After initialization, the port driver and the port circle the ring processing commands, responses, transmit requests and received frames.

- Host Receive Ring. A ring located in host memory. After port initialization it has fixed size and location. It is used to communicate port driver receive buffers to the port for the use as repositories of frames received from the FDDI network and intended for host delivery.

- Host Transmit Ring. A ring located in host memory. After port initialization it has a

fixed size and location. It is used to communicate port driver transmit buffers to the

port. Those buffers are intended for data which the adapter transmits in a frame on

the FDDI ring.

- Host Command Ring. A ring located in host memory. After port initialization it has a

fixed size and location. It is used to communicate port driver command buffers to the

port. Those buffers are specifically commands intended for the adapter manager, for

example get statistics, use these parameters, start this user, etc.

- Host Unsolicited Ring. A ring located in host memory. After port initialization it has a fixed size and location. It is used to communicate unsolicited (ie, by the device driver) information from the Adapter to the Device Driver. eg, congestion information.

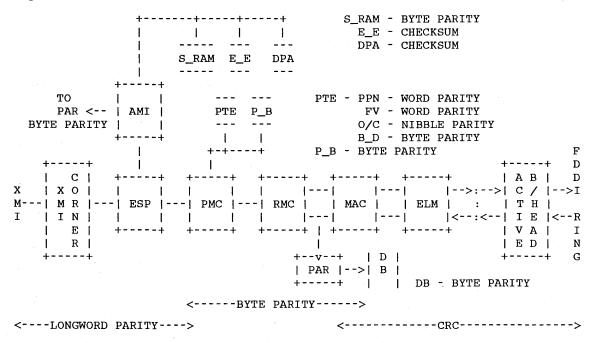

### 1.5 FDDI/802.2 Frame Format

Following is a representation of the FDDI/802.2 frame format where FC = Frame Control, DA = Destination Address, SA = Source Address and FCS = Frame Check Sequence. For a full definition of these terms refer to the ANSI MAC Specification.

## **CHAPTER 2**

### **DEMFA EXECUTIVE SUMMARY**

The DEMFA adapter is a high speed controller that connects the XMI bus to the Fiber Distributed Data Interface (FDDI). The DEMFA adapter and its associated device driver implement the FDDI NODE architecture, the FDDI Data Link architecture the DEMFA Port Specification.

The DEMFA is a single attachment station.

The DEMFA expects all host memory addresses passes to it to be physical addresses, ie, the adapter does not understand host virtual address schemes.

The DEMFA is compatible with both XMI-1 and XMI-2.

The technology chosen for two out of four gate arrays (ESP and PMC) is 1.0u Sea of Gates (SOG) and for other two gate arrays (AMI and PARSER) is 1.5u Sea of Gates (SOG). The RMC and Address CAM chips are 1.5u Hudson Semi-custom. The MAC and ELM chips are also of 1.5u Sea of Gates (SOG).

#### 2.1 **DEMFA CONTEXT**

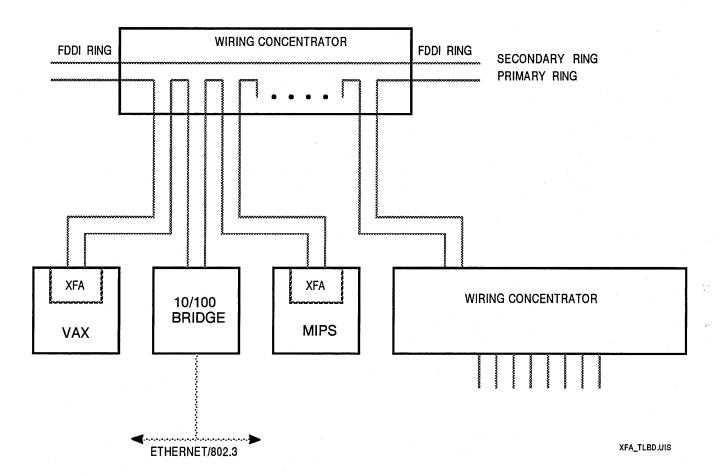

The DEMFA is being developed by VAX products and options group in Littleton. The first wave of Digital FDDI products will include an DEMFA for connecting XMI based CPUs and servers to FDDI, a bridge for connecting 10Mb/s Ethernet/IEEE802.3 LANs to FDDI and a wiring concentrator which will provide the physical connection for the DEMFA and bridge to the FDDI ring. A typical connection among DEMFA, bridge and wire concentrator is shown in Figure 1.

Figure 1: FDDI CONFIGURATION

### 2.2 DEMFA OVERVIEW

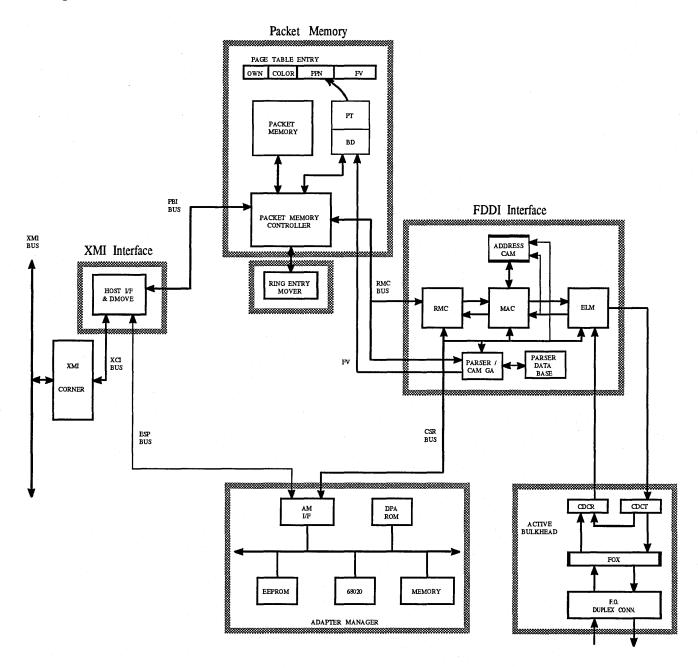

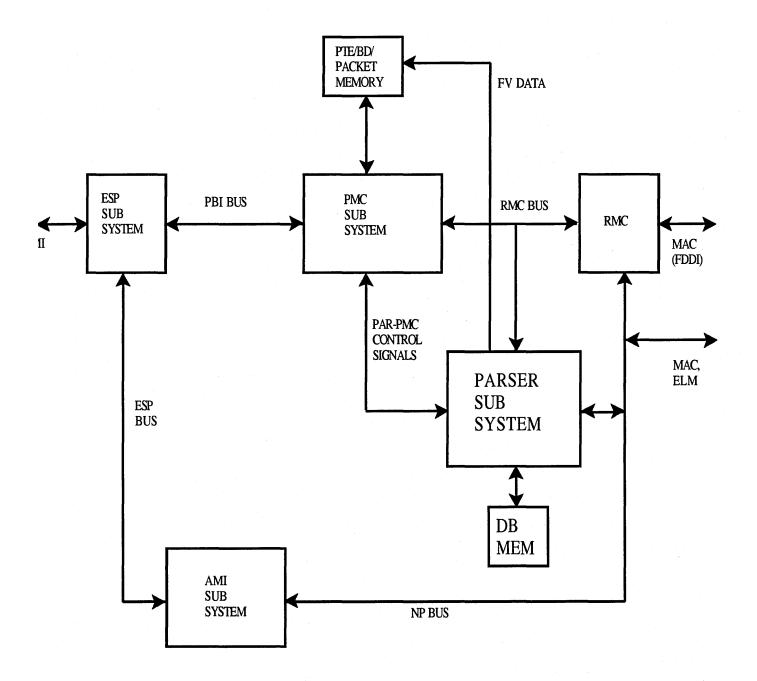

The DEMFA can be logically divided into 4 parts:

- 1. Host interface

- 2. Adapter Manager subsystem

- 3. Packet buffer memory subsystem, including the Ring Entry Mover (REM).

- 4. FDDI chipset and Parser

### 2.2.1 HOST INTERFACE

The Host interface to the XMI consists of the standard XMI corner and one Sea-of-Gates gate array (the ESP). The XMI corner contains the XMI specific XCLOCK and XLATCH chips that interface to the XMI backplane. The ESP Gate Array includes a single XMI commander and Responder, two Hexaword buffers for high speed data movement and hardware that understands how to transmit and receive packets without microprocessor intervention. The DEMFA implements Hex Writes and the More bit protocol. For more details see Chapter 3.

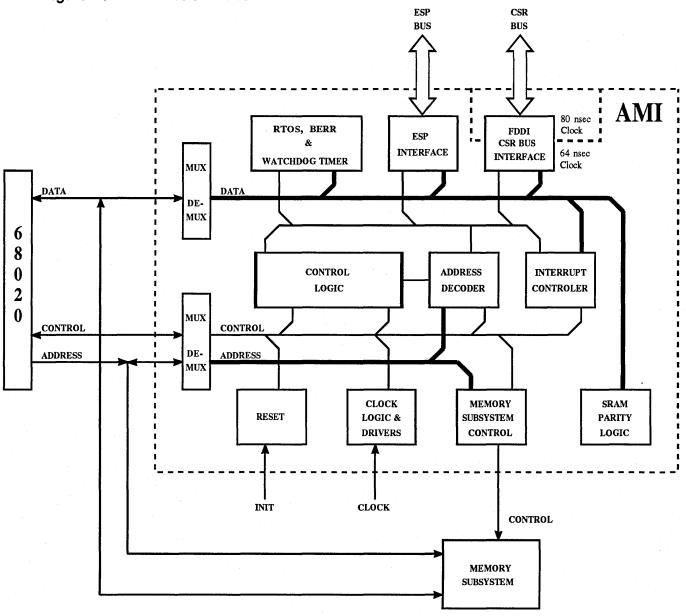

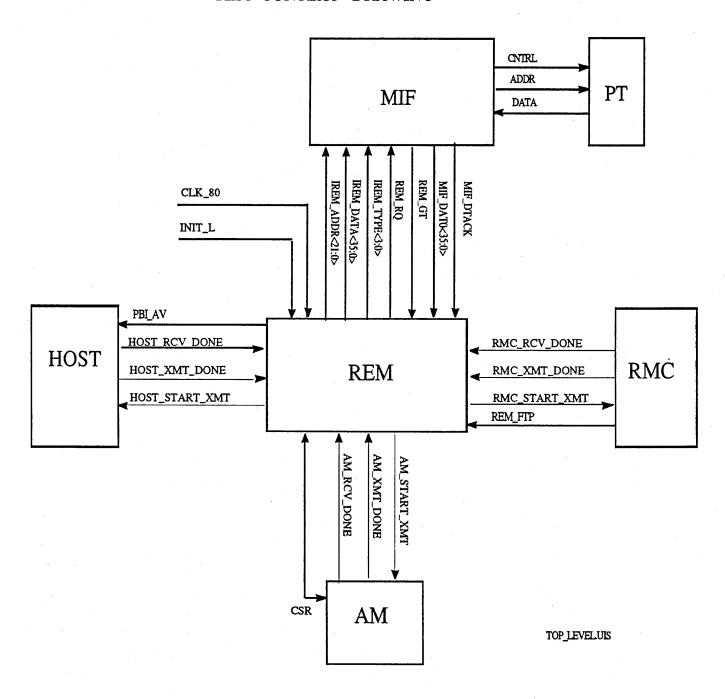

#### 2.2.2 THE ADAPTER MANAGER SUBSYSTEM

A 68020 microprocessor together with memory and a support logic gate array (the AMI gate array) provide what we call the adapter manager functions. These functions include:

- Initialization and event/error handling

- Processing and responding to device driver commands

- Processing and responding to FDDI packets not generally deliverable to the host, ie, Station Management and MOP packets.

- Local management of the FDDI MAC, PHY, and PMD sublayer entities within the DEMFA.

- Collection and Maintenance of statistics

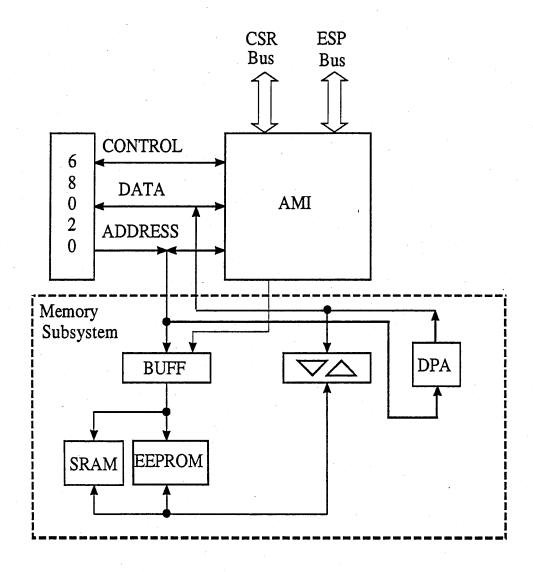

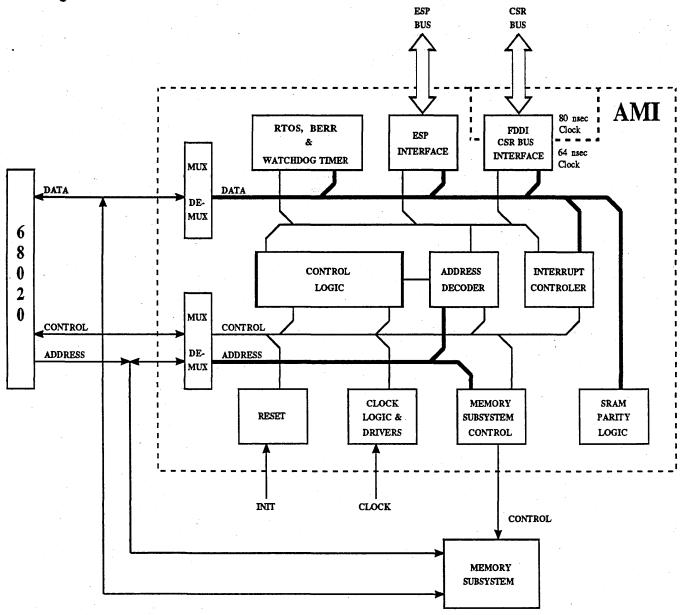

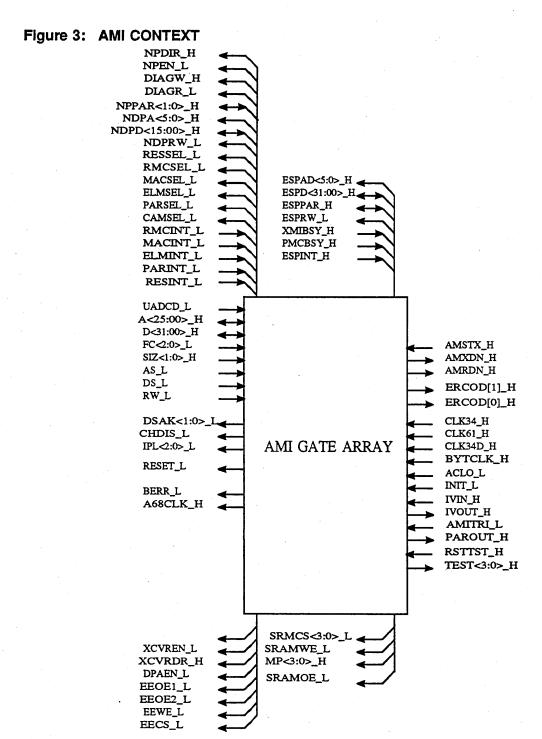

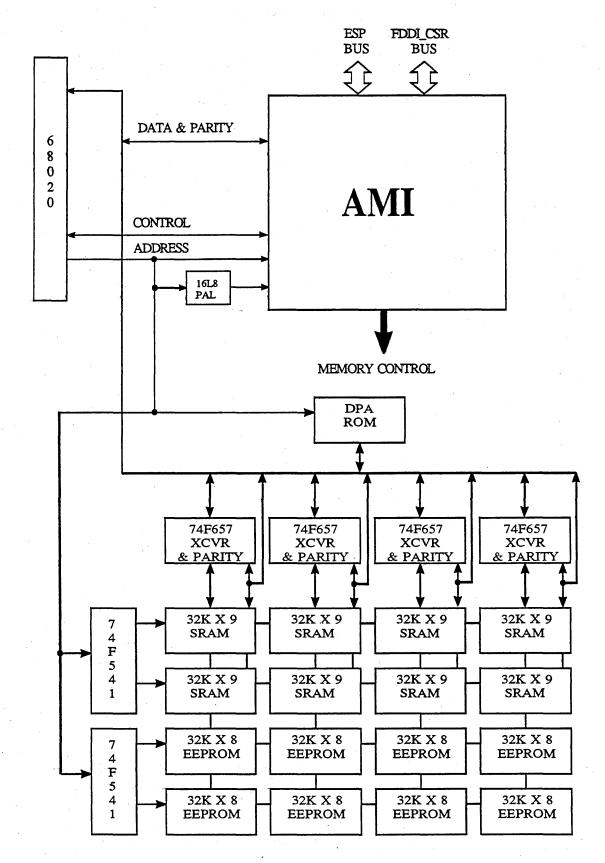

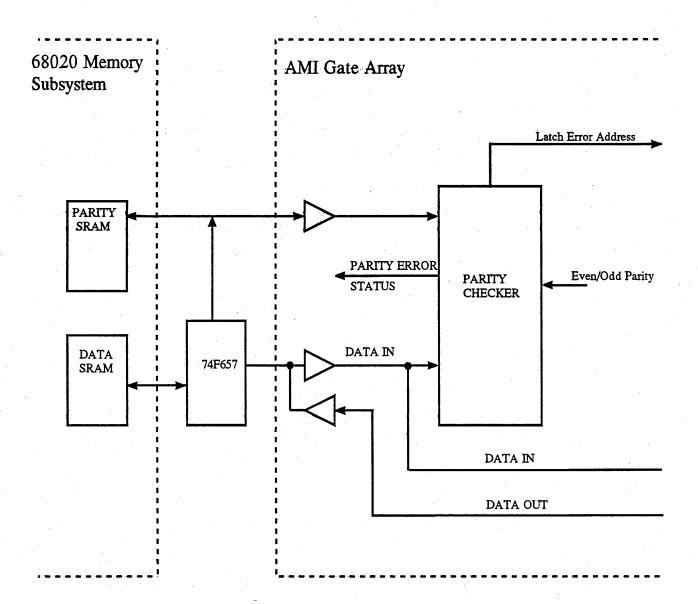

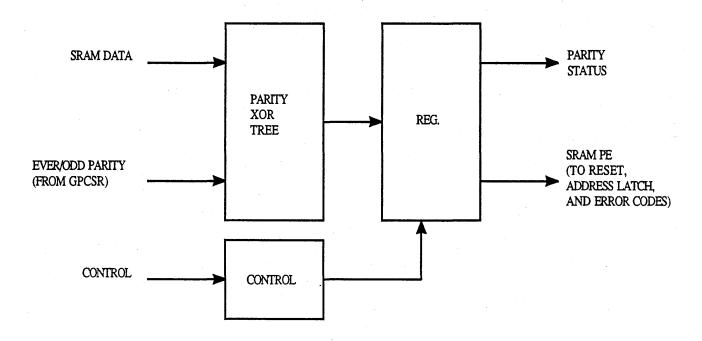

The Adapter Manager subsystem consists of a 68020 microprocessor with 256K bytes of EEPROM for functional and self-test microcode, 256K bytes of SRAM for operational code and scratch pad, a DPA ROM (Default Physical Address ROM), and the AMI gate array. The AMI gate array contains timers, interface logic to the FDDI chipset, and interface logic to the host and packet buffer memory (via the ESP gate array).

#### 2.2.3 THE PACKET BUFFER MEMORY SUBSYSTEM

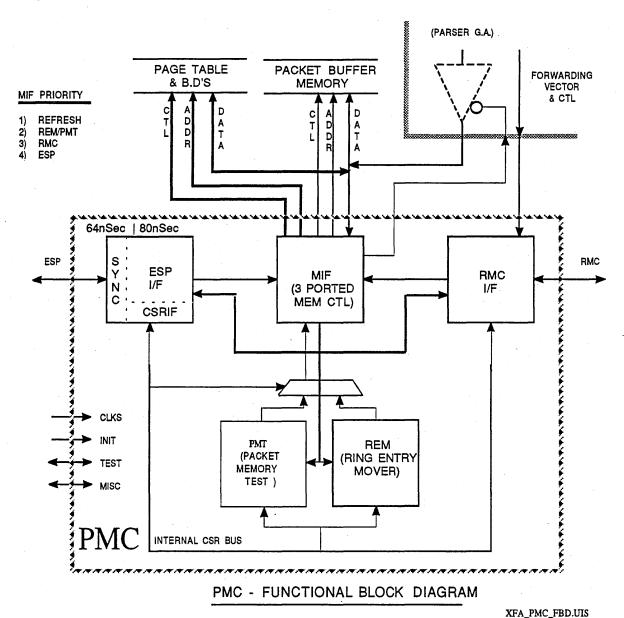

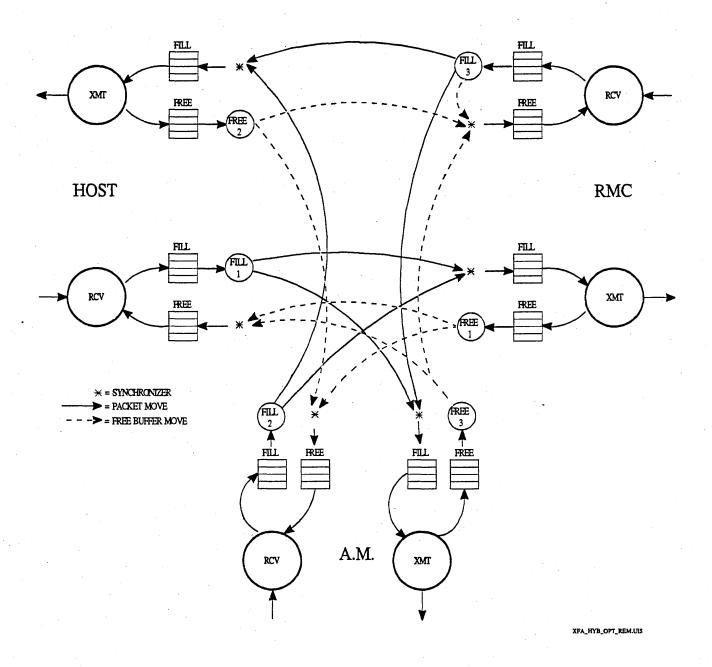

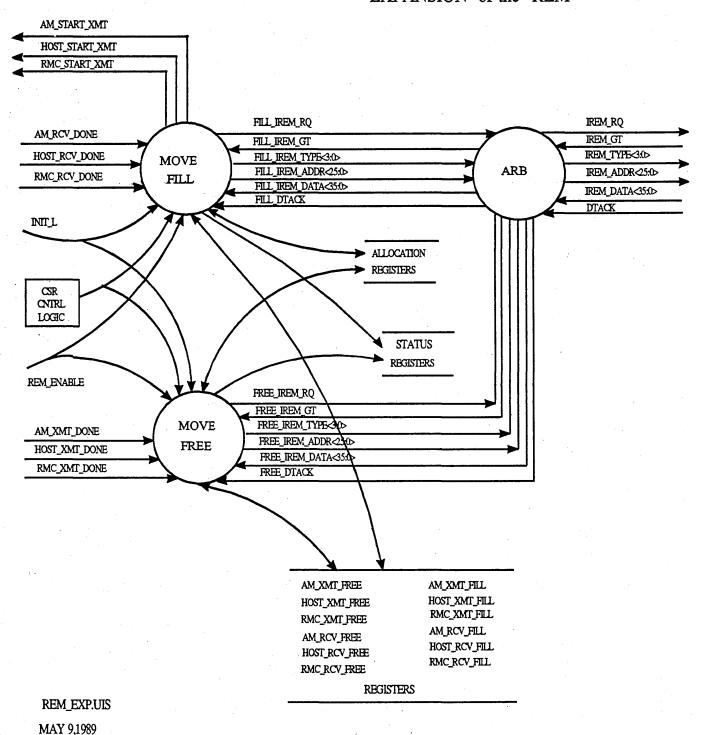

The Packet buffer memory subsystem is logically a four ported memory and physically a three ported memory. The three physical ports are the ESP, the RMC (part of the FDDI chipset) and the REM (Ring Entry Mover - a function internal to the PMC gate array). The three physical interfaces are logically identical to the RMC. Two logical ports, one for the host interface and one for the adapter manager are multiplexed across the ESP physical interface.

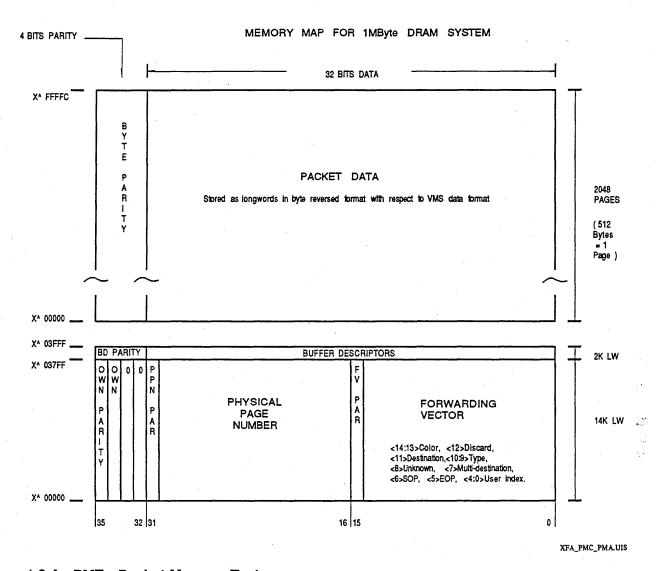

Packets exist in virtual space, being indirectly addressed through a page table lookup, pages being 512 bytes. Packets are organized in 6 groups, being a transmit group and a receive group for each of the RMC, host interface and adapter manager. Each group is controlled by a ring structure, being a circular list of control elements, each control element containing page indirection, packet specific information (length, destination, status, etc) and ownership.

The Ring Entry Mover is a programmable functional element within the PMC gate array whose function is to move packets between the various interfaces. It accomplishes this by manipulating the control elements. Packet data is never copied, ie the source interface writes the packet and the destination interface reads the packet, only control information 'moves'. For example, the RMC has moved a packet into the packet memory. Once the RMC relinguishes ownership of this page or set of pages the REM will look at some fields in the control element to determine where this page should go. The page could be discarded, sent to the adapter manager or to the host. Once the REM has moved the control information it will relinguish ownership of this page. This action makes the packet available to the

adapter manager (or the host interface) which will take the appropriate action. A detailed description of how the ring structures work can be found in the RMC chip specification.

The packet buffer memory subsystem consists of 1M bytes of DRAM for packet buffer memory, 64K bytes of SRAM for the control elements, being the Page Table Entries and Buffer Descriptors, and one Sea-Of-Gates gate array, (the PMC)

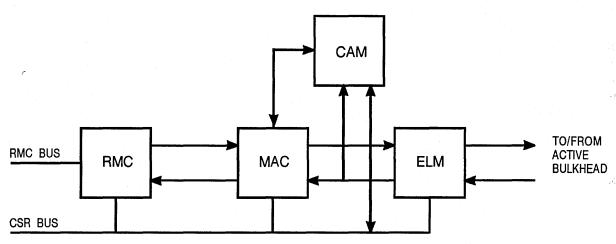

### 2.2.4 THE FDDI CHIPSET AND THE PARSER

The FDDI chipset provides the actual interface to the FDDI. The chipset consists of the Ring Memory Controller (RMC), the Media Access Controller (MAC), the Elasticity buffer and Link Manager (ELM), the transmit CDC (TX CDC), the Receive CDC (RCV CDC), and the Fiber Optic transmitter and receiver chips (FOX). These chips have been developed by NaC and will also be used by other products, such as the wiring concentrator and the bridge. Following is a list of the major features of these chips.

The major features of the RMC (Ring Memory Controller) gate array are:

- Independent transmit and receive channels

- Fragment filter to discard small "non-packets"

- 4 or 8 longword burst mode to packet buffer memory

- Circular (ring) buffer support

The major features of the MAC (Media Access Control) gate array are:

- Respond to the frame Control byte for received frames

- Destination Address filtering

- Perform CRC checking for receive packets

- Save frame status indicators

- Keep a count of the good and bad frames received

- Assemble packets for transmission

- Generate CRC for transmit packets

- Can internally generate and send Claim, Beacon, and Void frames.

The major features of the ELM (Elasticity Buffer and Link Management) gate array are:

- Elasticity Buffer (for synchronizing recovered and local clocks)

- 4B/5B encoding/decoding

- Line State Detection

- Repeat filter for MAC-less connection

- Physical Connection Management state machines

The TX CDC converts the parallel data stream into serial data stream before it sends the data to the Fiber Optic transmitter.

The RCV CDC converts the serial data stream it receives from the Fiber Optic receiver into a parallel data stream destined for the ELM chip.

The FOX is the combination of the Fiber Optic transmitter and receiver.

### **8 DEMFA EXECUTIVE SUMMARY**

The last three components, TX CDC, RCV CDC, and FOX, reside on what is called an active bulkhead module, which is attached to an I/O bulkhead plate. The I/O bulkhead plate is mounted on the I/O panel of the CPU cabinet. The fiber optic connector from the FDDI ring plugs into this I/O bulkhead plate.

The Parser gate array snoops on the RMC bus and does packet parsing based on information in a local (to the parser) data base during the receive of a packet from the RMC. It generates a Forwarding Vector which is written into the control element, Page Table Entry, associated with each page of a packet.

Figure 2: XMI - FDDI ADAPTER BLOCK DIAGRAM

XFA\_BLOCK\_DIAGRAM\_3.UIS

### 2.3 PACKET RECEPTION

Following is a brief description of how a packet is received from the FDDI physical medium and delivered to the user portal (the data link interface). Please refer to Figure 2. Photons received from the optical fiber are converted to electrical signals by the FOX.

The electrical signals are passed to the CDCR for convertion to signals suitable for a CMOS gate array, viz the ELM. The CDCR also recovers the imbedded clock.

The ELM synchronizes the data with the local clock. The ELM chip decodes the encoded data stream into data or control symbols. The decoded data is passed to the MAC chip who analyses the data stream.

In the case of packets for this endnode, the MAC recognises it as such, the MAC passes the packet to the RMC for delivery to the Packet Memory. The MAC also all the time checks the packet for good CRC. The MAC generates byte parity.

The RMC will deliver the packet to the Packet Memory in a series of data bursts and followed by a BD (Buffer Descriptor which contains the packet status and length) write then a 'clear ownership' cycle (ownership of the packet buffer is passed to the next stage of processing) and finally status is passed to the Ring Entry Mover that a packet has been completely delivered.

The Parser, who 'snoops' on the RMC bus, parses the packet and, depending on his local data base, will generate a Forwarding Vector indicating what is to be done with the packet, ie, discard, deliver to host, deliver to adapter manager, for use by the ring entry mover in the PMC gate array.

The Packet Memory Controller provides the necessary interfaces to the packet memory and the page and buffer descriptor tables. The PMC also arbitrates between the interfaces. The PMC contains the Ring Entry Mover (REM). The Ring Entry Mover is made aware of the delivery of a packet from the FDDI by the RMC. Upon receipt of this indication, the REM analyses the forwarding vector and 'moves' the packet to the appropriate place for delivery (or discards the packet). The REM also manages the buffer resources and gathers statistics on discarded packets.

In this case (packet from FDDI to Host User Interface), the REM alerts the XMI interface (the ESP) that a packet has been queued for delivery. Assuming the ESP has already got host buffer(s) for delivery of the packet, the ESP will set up his dual hexaword buffer data mover engine to deliver the packet. Upon completion of the data delivery, the ESP will deliver appropriate status and pass ownership of the packet to the device driver. If it is necessary to 'wake up' the device driver to process the packet, a host interrupt will be sent. Great care is taken not to interrupt the host unnecessarily. Upon receipt of the interrupt, the device driver will process the packet and pass it to the appropriate user via a data link portal.

### PACKET TRANSMISSION

Following is an example of a packet transmission from the User Data link interface to the FDDI physical medium. Users pass packets for transmission to the device driver via a data link portal. The device driver in turn queues the packet for transmission and, if necessary, alerts the ESP gate array of the fact. The ESP sets up the dual hexaword buffer data mover (shared with receive path) to move the data between host memory and the packet buffer.

Upon completion of the move, the ESP writes appropriate packet status to both the Host and the Packet Memory. The ESP alerts the REM that a packet has been queued in the packet buffer.

The REM understands that packets from the host are only intended (except in maintenance mode) for transmission over the FDDI. The REM therefore make the necessary 'move' by manipulating the corresponding control elements. Once the REM has completed the 'move', it informs the RMC that a packet has been queued for transmission over the FDDI.

The RMC reads the first part of the packet and passes the first four bytes of the packet to the MAC. This is the packet header and frame control information (supplied by the device driver) and provides the MAC with the necessary information to capture a token and some other packet specific information (refer to the RMC and MAC Specification for details). Once the MAC informs the RMC that the token has been captured, the RMC fetches the rest of the packet data. Upon completion of the packet transmission, the RMC, based on internal and MAC derrived information, passes packet status to the Packet Memory for storage in the appropriate buffer Descriptor(s).

The MAC, as previously alluded, is responsible for capturing an appropriate token and, upon capture, allow transmission of any packet(s) queued up to a predetermined limit. The MAC (on a per packet basis) may optionally generate CRC which is appended to the packet. The MAC passes the packet to the ELM.

The ELM encodes each nibble (symbol in FDDI parlance) according to 4B/5B encoding and passes the symbol-wide data stream to the CDCT.

The CDCT serializes the data stream and converts the signal levels to that appropriate to the FOX.

The FOX converts the electrical signals to analogus optical signals which are transmitted into the FDDI physical medium.

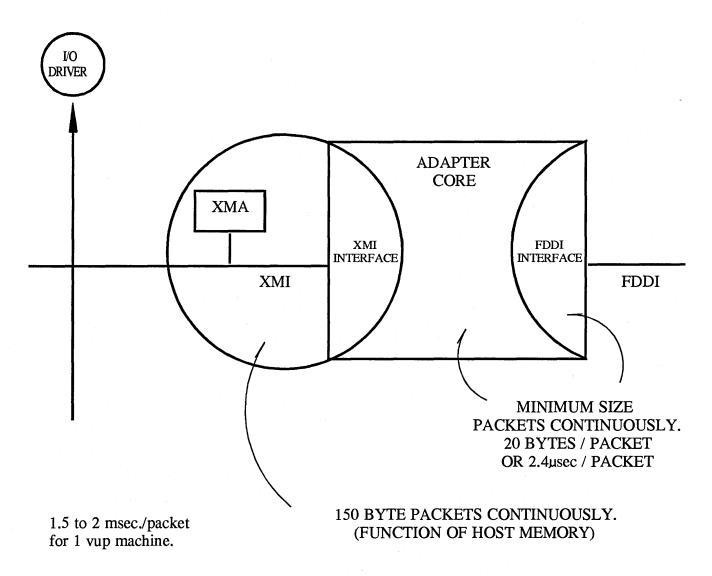

### 2.5 PERFORMANCE

Performance is summarized by the following figure, Figure 3. The figure shows three performance metrics.

Firstly, the adapter is capable of sustaining minimum packet traffic with the FDDI (up to the limit of the packet buffer).

Secondly, the following table shows the estimated performance across the XMI bus.

| Table 1: DEMFA PERFORMANCE |                                |                                 |                                 |                             |

|----------------------------|--------------------------------|---------------------------------|---------------------------------|-----------------------------|

| SYSTEM                     | Receive Packet<br>Size (bytes) | Receive Band-<br>width (MBytes) | Transmit Packet<br>Size (bytes) | Transmit Bandwidth (MBytes) |

| Calypso <sup>1</sup>       | 150                            | 11.87                           | 150                             | 11.87                       |

| Aquarius <sup>2</sup>      | 150                            | 11.87                           | 1500                            | 12.43                       |

<sup>&</sup>lt;sup>1</sup>Minimal Contention on the XMI

<sup>&</sup>lt;sup>2</sup>Minimal XMI and J\_Bus contention. Aquarius number for transmit packet size is large because number of cycles for hexaword read is relatively large

The performance given in Table 1 is calculated making some assumptions. For full details refer to the DEMFA Performance Simulation Studies document.

Thirdly, since the I/O driver can process packets at the rate of 1.5 to 2 msec per packet per VUP, this implies that packets may be transferred across the user (data link) interface at the rate of 500 packets/sec/vup approximately. Not shown in the diagram is latency. Latency is less than 20 microseconds assuming system lightly loaded, no queueing delays, first bit to last bit for a 22 byte packet (that is, first bit received from the optical fiber to last bit delivered to host memory).

Figure 3: DEMFA PERFORMANCE

### SUBSYTEM LEVEL PERFORMANCE

500 packets/sec/vup.

### CHAPTER 3

### **DEMFA FUNCTIONAL DESCRIPTION**

The DEMFA module is logically divided into four parts:

- 1. Host Interface

- 2. Adapter Manager Subsystem

- 3. Packet Buffer Subsystem, including the Ring Entry Mover