New features, as well as changes, deletions, and additions to information in this manual, are indicated by bars in the margins or by a dot near the page number if the entire page is affected. A bar by the page number indicates pagination rather than content has changed.

# **REVISION RECORD**

| REVISION                    | DESCRIPTION                                                                                      |  |  |

|-----------------------------|--------------------------------------------------------------------------------------------------|--|--|

| A                           | Corrections.                                                                                     |  |  |

| В                           | 1604 Inverter Ground Rules and Hammer Storage Card 91 pages added.                               |  |  |

| С                           | Long Line Driver and Receiver Cards CA98 and HA26 pages added.                                   |  |  |

| D                           | Corrections to card type C64 and C65.                                                            |  |  |

| E                           | Add index tabs, chapter headings, new Table of Contents addition to Appendix, type "E" and 1604  |  |  |

|                             | cards; and Delay Card P13A.                                                                      |  |  |

| F                           | Replace the following pages 3-HA18-1 and 2; 4-C62 and C-61-5 and 6; Appendix pages 5 through 10. |  |  |

|                             | Add pages 4-60, 60A, 62 and 67-1 through 3; 4-79A-1, 5-97-1 and 2, 5-E10-1. Replace page         |  |  |

|                             | 4-E12-1.                                                                                         |  |  |

| G                           | 6600 information and circuit module schematics added as volume 3.                                |  |  |

| Н                           | Volume 1, addition of revised record of revisions volume 2, addition of record of revisions.     |  |  |

|                             | Replace the following revised pages; chapter 4 contents page, 4-C62 and C61-1, 4-C62 and C61-2,  |  |  |

|                             | 4-C62 and C61-3, 4-C62 and C61-5, 4-C62 and C61-6, 4-C62 and C61-7, 4-P14A and P16A-3,           |  |  |

|                             | 5-C94-3.                                                                                         |  |  |

| J                           | Volume 1, page 2-3600 inv-3 revised. Volume 2, chapter 5, second page of contents revised, re-   |  |  |

|                             | moves pages 5-PED-1 through 5-PED-22. Chapter 6 added and Appendix 1, pages 16, 17, and 18       |  |  |

|                             | removed and new pages added.                                                                     |  |  |

| K                           | Publication Change Order 11170. Record of Revisions for volumes 1 and 2 revised. Removed         |  |  |

|                             | pages 15 through 31 of volume 2, Appendix 1 and replaced with revised pages.                     |  |  |

| L                           | Change Orders 10344 and 10708. Pages v, vi, vii, viii of volume 1 revised. Chapter 4 contents    |  |  |

| (10-5-65)                   | page, 4-HA19-3, 4-HA37 and HA43-10, 4-P14C and P16A-1, 4-P14C and P16-2, 4-P14C and              |  |  |

|                             | P16-A-3, chapter 5 contents pages, 5-C84-1, 5-C84-2, 5-C84-3 (new pages), 3, 4, 7, and 8         |  |  |

|                             | (appendix) revised. Pages 5-C60-1, 5-C60-2, 5-C60-3, 5-C97-1, 5-C97-2, and 5-C97-3 added.        |  |  |

|                             | Pages 5-HA27 and 5-HA28-1 and 5-HA27 and 5-HA28-2 revised.                                       |  |  |

| M                           | Change Order 12131. Appendix 1; pages 16 through 31 revised and pages 32 through 47 added.       |  |  |

| (12-13-65)                  |                                                                                                  |  |  |

| N                           | Publication Change Order 12940. New peripheral equipment cards added to chapter 6; ADH,          |  |  |

| (5-13-66)                   | ITA/ITB/ITC, ITD, TYA, OJB, OYA, and UJB. Revised text for page; 6-OHA-1. Revised                |  |  |

|                             | schematic for page 6-IAA, IAB-2. Appendix 1 revised. This revision obsoletes all editions        |  |  |

|                             | of pin assignments- 1604 and 3600. Printed circuit cards, publication number 60106200, which is  |  |  |

|                             | now included in this revision.                                                                   |  |  |

| P                           | Publication Change Order 13632. Pages 6-ISC-1 of chapter 6 is revised. The following new cards   |  |  |

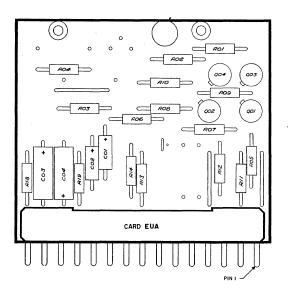

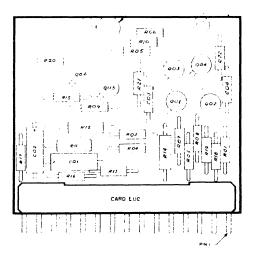

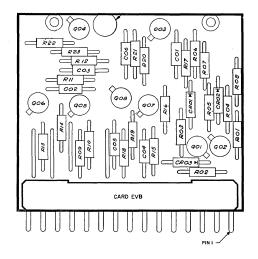

| (5-13-66)                   | are added to chapter 6; ALA, AMF, AMG, AMH, AMI, ANB, ANC, AND, AUA, EUA, EUC, EVB,              |  |  |

|                             | FCA, FCB, FDA, FGA, FHA, FIA, FJA, FKA, FLA, FLB, FMA, FNA, FPA, FRA, FSA, FTA,                  |  |  |

|                             | FUA, FVA, FWA, FYA, JBA, JCA, JDA, and OTA.                                                      |  |  |

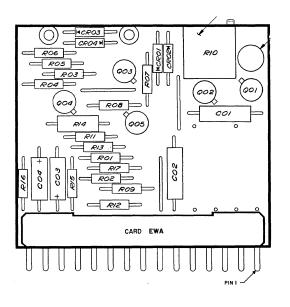

| R                           | Publications Change Order 15800. The following new cards added to chapter 6; AIB, AKA, AOA,      |  |  |

| (2-13-67)                   | ATA, ATB, AVA, AYA, BAA, BAB, BBA, BCA, EEG, EEH, EWA, EWB, EZA, FAB, FOA, FO                    |  |  |

| Publication No.<br>60042900 |                                                                                                  |  |  |

#### **REVISION LETTERS I, O, Q AND X ARE NOT USED**

Address comments concerning this manual to:

Control Data Corporation Publications and Graphics Division 4201 North Lexington Avenue St. Paul, Minnesota 55112 C

or use Comment Sheet in the back of this manual.

© 1963, 1964, 1965, 1966, 1967, 1968, 1971, 1977 by Control Data Corporation Printed in the United States of America

| REVISION                              | DESCRIPTION                                                                                       |

|---------------------------------------|---------------------------------------------------------------------------------------------------|

| R                                     | FRB, FEC, FRD, FSB, FUB, FWB, FXB, GAA, GBA, GCA, GCB, GCC, GCD, IOB, IOC, IOD,                   |

| (Cont'd)                              | JEB, JEC, ONA, OUA, OVA, UEA, UHB, UIA, UJC, UKA, and UKB.                                        |

| S                                     | Publications Change Order 16541. The following new cards are added; AHC, AMJ, AMK, AMI, AV        |

| (6-23-67)                             | AVC, AVD, AYB, BCB, BDA, BFA, BGA, BHA, BHB, BIA, BJA, EEK, EEL, EEM, EEO, EUD,                   |

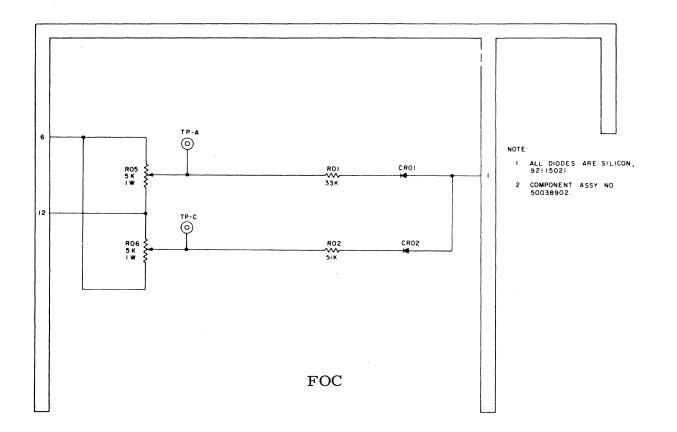

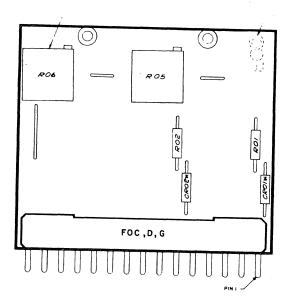

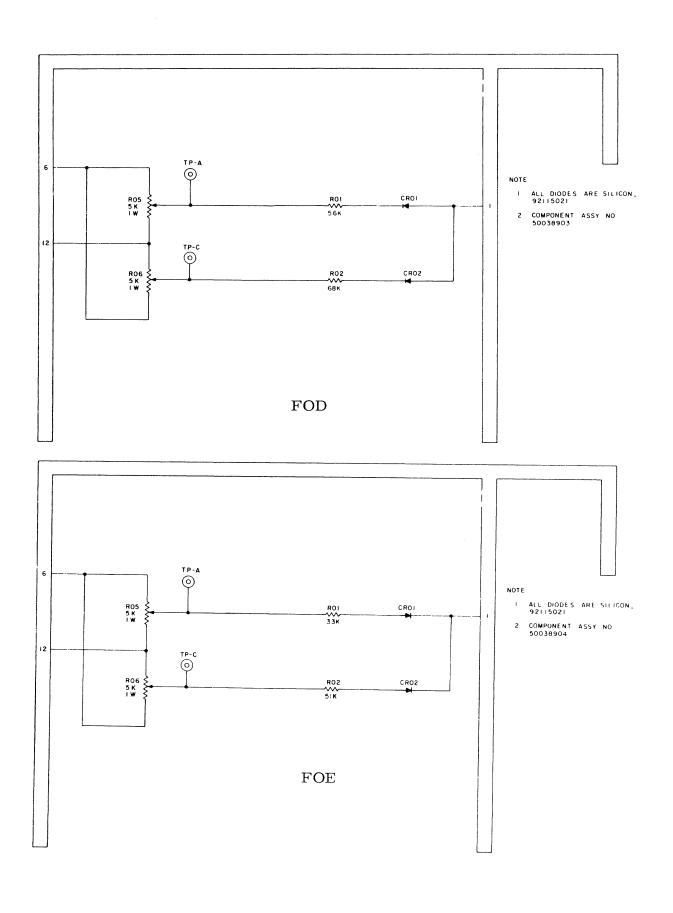

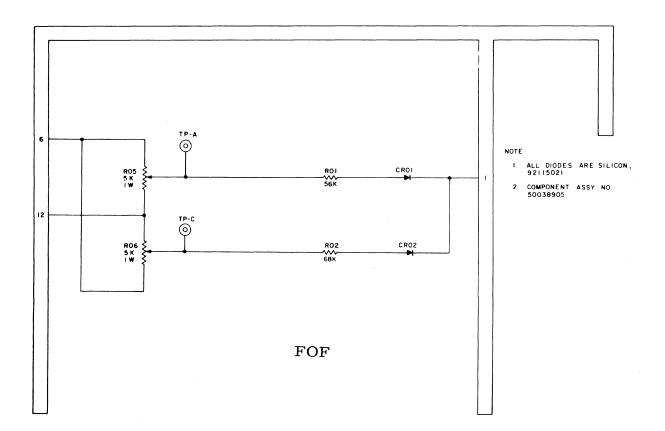

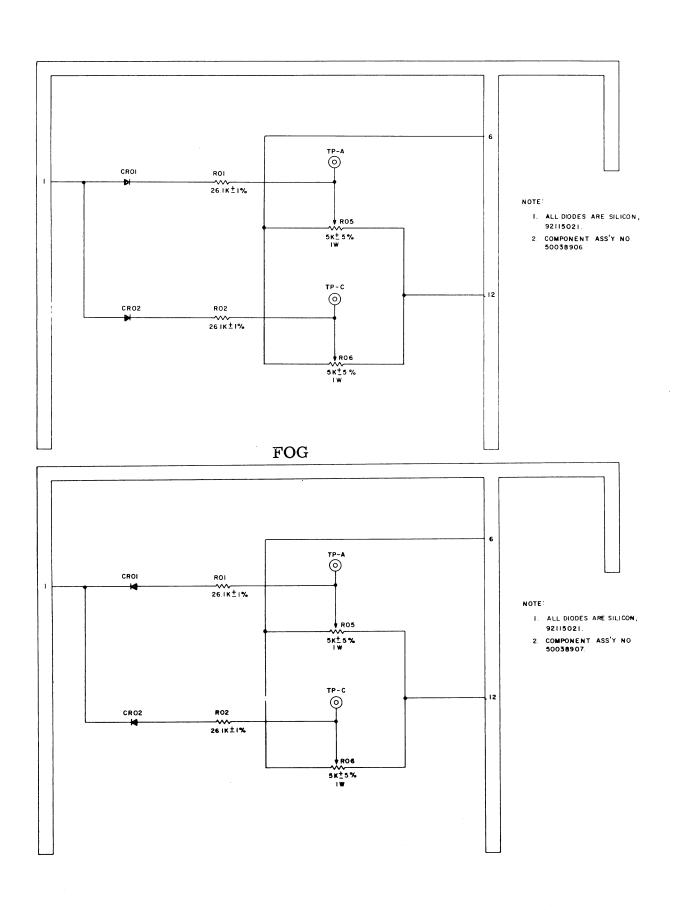

| (0 20 01)                             | EWC, FCC, FCD, FCE, FGB, FGC, FOC, FOD, FOE, FOF, FOG, FOH, FVB, FXC, GAB, GAC                    |

| ······                                | GDA, GEA, GFA, GFB, GFC, GGA, HAA, IOE, IOF, ISH, JAD, JAE, JAF, JAG, OSC, OVB, TA                |

|                                       | ULA.                                                                                              |

| т                                     | Engineering Change Order 20995, publications change only. The following new cards are added;      |

| (11-22-68)                            | Card type 144, CC10, ADG, AMM, AMN, AMO, AMP, AMQ, AUB, AUC, AZA, BEA/B, BMA,                     |

|                                       | BOA, BRA, BTA, BUA, EJA, FMB, FYB, GHA, GIA, GIB, GOA, GSB, HAB, IOG, IVA, IVB, IV                |

|                                       | JAH, JAI, JED, JEE, JFA, JHB, JJA, JLA, JOA, JPA, OGD, OWB, PJA, PJB, UPA, URA, USA               |

|                                       | The documentation for the following cards is affected by either revisions or page number changes; |

|                                       | Card type 54, 74; HA18; C07C; HA20; HA27; HA28; HA35; AMF through AML; AUA, AVA, through          |

| -                                     | AVD; FCA through FCE; FGA through FGC; FMA; FOA through FOH; FXB, FXC, FYA, HAA, IOB              |

|                                       | through IOF; JAD through JAG; UAA, UAB, UHB, ULA, pages 5, 20, and 21 under appendix 1.           |

|                                       | The following miscellaneous changes are being made: expansion from two to three volumes, re-      |

|                                       | labeling of chapter 6 tabs, and appendix 1 tab repositioned.                                      |

| U                                     | Engineering Change Order 28728, publications change only. Incorporates publications change        |

| (8-9-71)                              | from the following ECO's: 24045A, 23441, 20211, 21766, and FCO PR1168. The following pages        |

|                                       | are revised: 3-HA14-3, V5-E08-2, 5-97-1, 5-97-2, 5-HA20-1, appendix 1 page 15.                    |

| v                                     | Engineering Change Order 36403, publications change only. No effect on this publication.          |

| (6-10-75)                             |                                                                                                   |

| W                                     | Manual revised; includes Engineering Change Order 37817, publications change only. Page           |

| (2-23-77)                             | 3-HA14-3 is revised.                                                                              |

|                                       |                                                                                                   |

|                                       |                                                                                                   |

|                                       | · ·                                                                                               |

|                                       |                                                                                                   |

|                                       | ·                                                                                                 |

|                                       |                                                                                                   |

| · · · · · · · · · · · · · · · · · · · | ·                                                                                                 |

|                                       |                                                                                                   |

|                                       |                                                                                                   |

|                                       |                                                                                                   |

|                                       |                                                                                                   |

|                                       |                                                                                                   |

|                                       |                                                                                                   |

|                                       |                                                                                                   |

|                                       |                                                                                                   |

|                                       |                                                                                                   |

|                                       |                                                                                                   |

|                                       |                                                                                                   |

|                                       |                                                                                                   |

|                                       |                                                                                                   |

|                                       |                                                                                                   |

## CHAPTER 6. PERIPHERAL EQUIPMENT CARDS\* (Types A-- Thru G--)

| Relay Puller                        | АВА                                                      |

|-------------------------------------|----------------------------------------------------------|

| Photo-Diode Bias and Preamplifier   | ACA                                                      |

| Hammer Driver                       | ADA, ADB                                                 |

| Hammer Driver                       | ADC, ADD, ADE                                            |

| Hammer Driver                       | ADG                                                      |

| Clutch-Brake Driver                 | ADH                                                      |

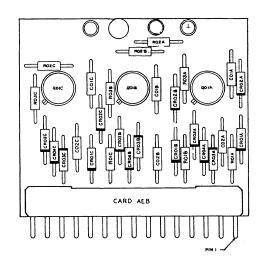

| Output Driver                       | AEB                                                      |

| Multiple Time Delay                 | AFA, AFB                                                 |

| Enable Amplifier                    | AGA                                                      |

| Flip-Flop Driver                    | АНА, АНС                                                 |

| Shift Driver                        | AIA, AIB                                                 |

| Photocell Amplifier                 | АКА                                                      |

| Power Supply                        | ALA                                                      |

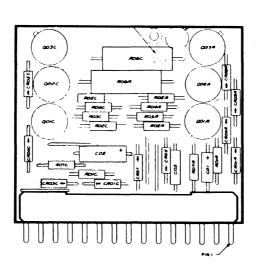

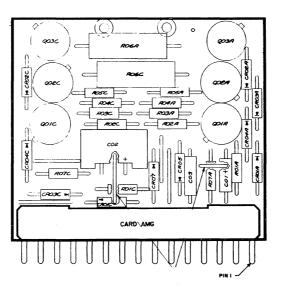

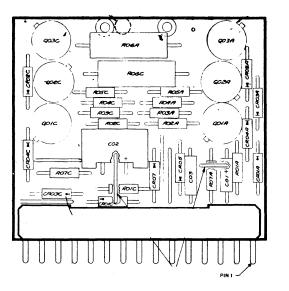

| Write/Erase Driver                  | AMF, AMG, AMH, AMI, AMJ,<br>AMK, AML, AMM, AMN, AMO, AMQ |

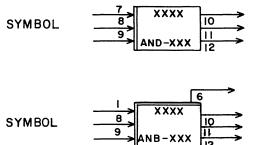

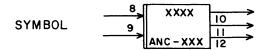

| Head Select and Write Error Checker | ANB, ANC, AND                                            |

| Exclusive OR Circuit                | AOA                                                      |

| Gated Amplifier                     | ATA, ATB                                                 |

| Power Supply Regulator              | AUA, AUC                                                 |

| Power and Clamp Voltage Supply      | AUB                                                      |

| Write Resistor Diode                | AVA, AVB, AVC, AVD                                       |

| Voltage Checker                     | AYA, AYB                                                 |

| Write Resistor                      | AZA                                                      |

| Voltage Checker                     | BAA, BAB, BBA, BCA, BCB                                  |

| Head Switch                         | BDA                                                      |

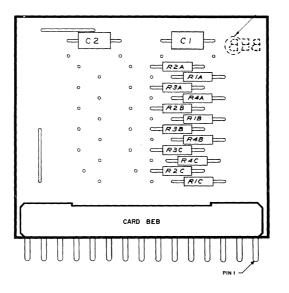

| Line Terminators                    | BEA, BEB                                                 |

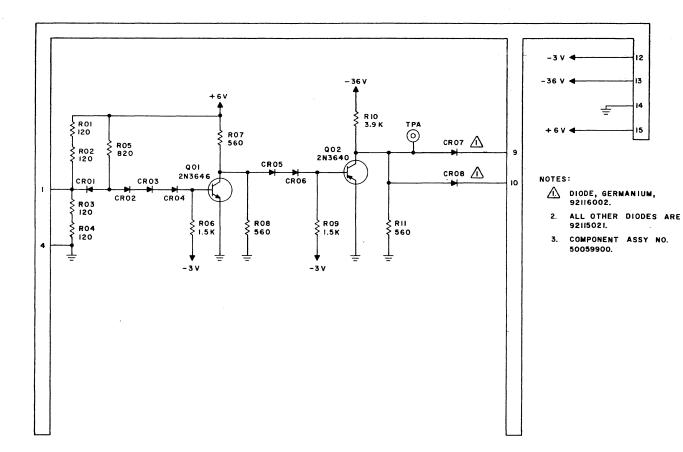

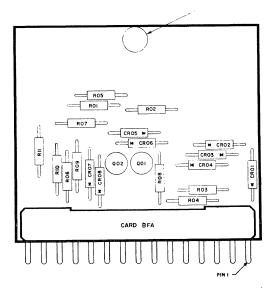

| L Type Data Receiver                | BFA                                                      |

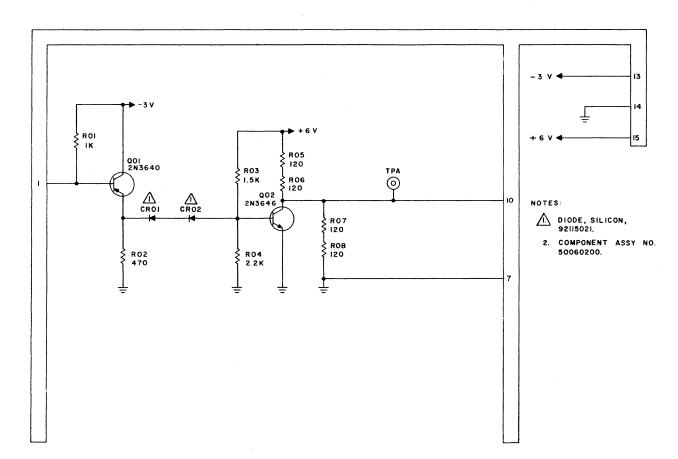

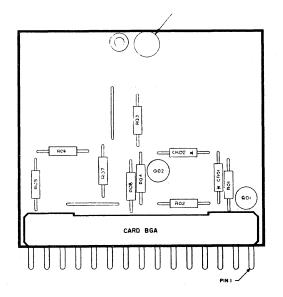

| L Type Data Transmitter             | BGA                                                      |

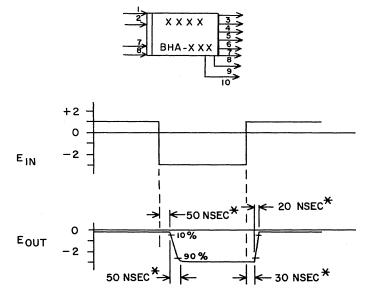

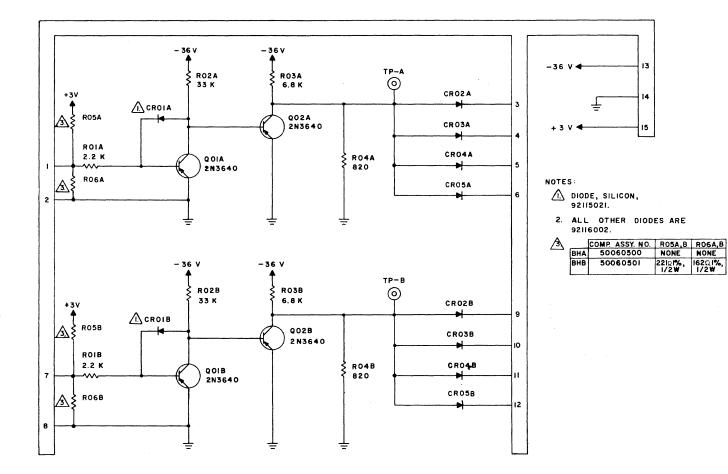

| ଦ Type Control Receiver             | BHA, BHB                                                 |

| Q Type Control Transmitter          | BIA                                                      |

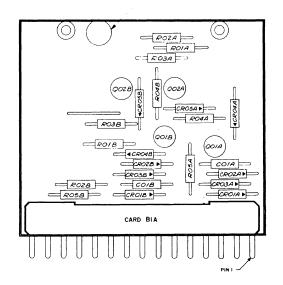

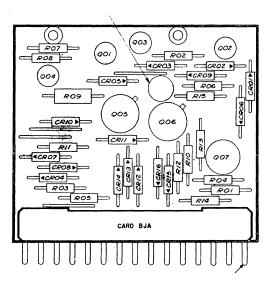

| Supply Sensor and Current Sink      | BJA                                                      |

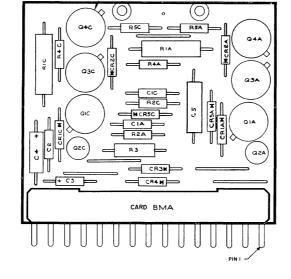

| Write Driver                        | BMA                                                      |

|                                     |                                                          |

\*Refer to Volume 3 for Card Types H-- thru Z--.

| Voltage Checker                              | BOA                     |

|----------------------------------------------|-------------------------|

| Erase Driver                                 | BRA                     |

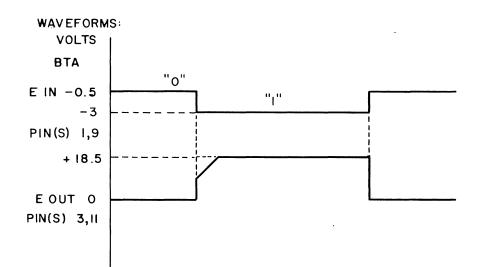

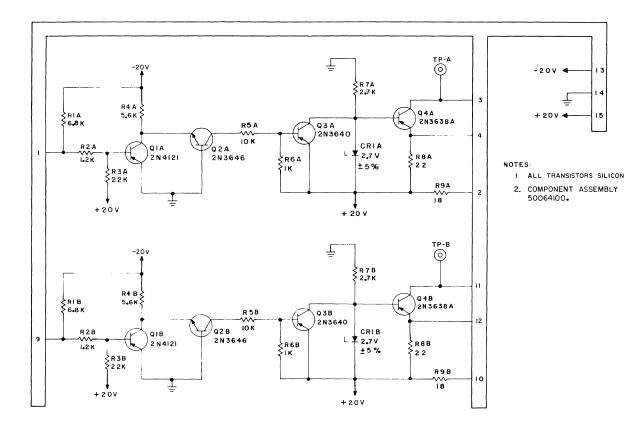

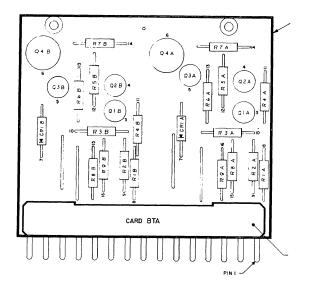

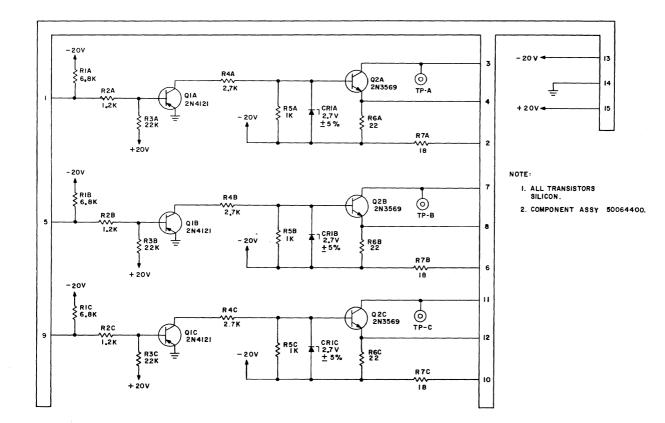

| Current Controlled Lamp Driver               | BTA, BUA                |

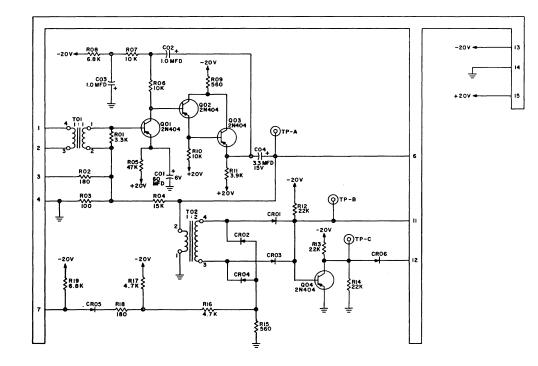

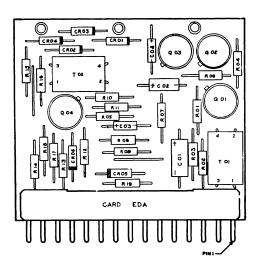

| Read Level Detector                          | EDA                     |

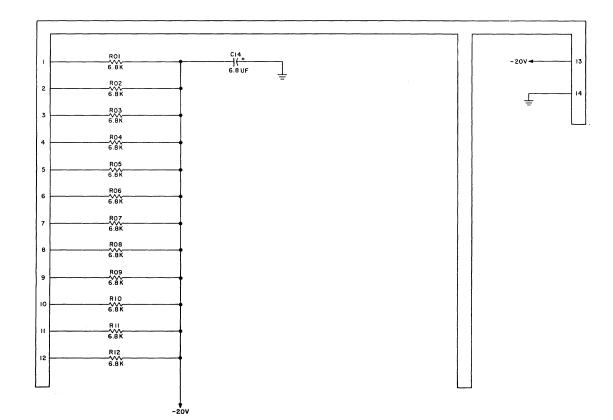

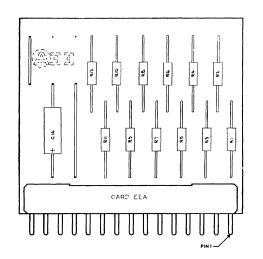

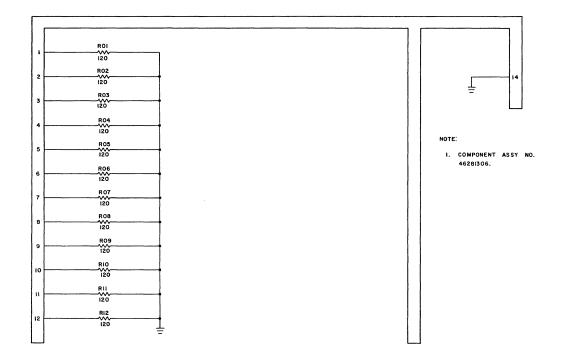

| Resistor Termination                         | EEA                     |

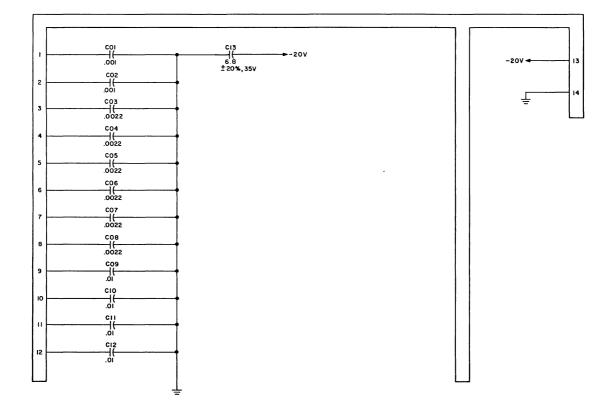

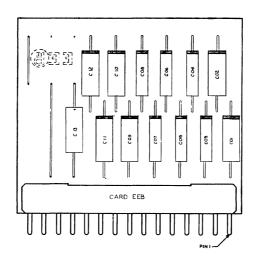

| Capacitor Termination                        | EEB                     |

| Capacitor Termination                        | $\mathrm{EEC}$          |

| Resistor Termination                         | $\operatorname{EED}$    |

| Capacitor Termination                        | EEE                     |

| Resistor Termination                         | $\mathbf{EEF}$          |

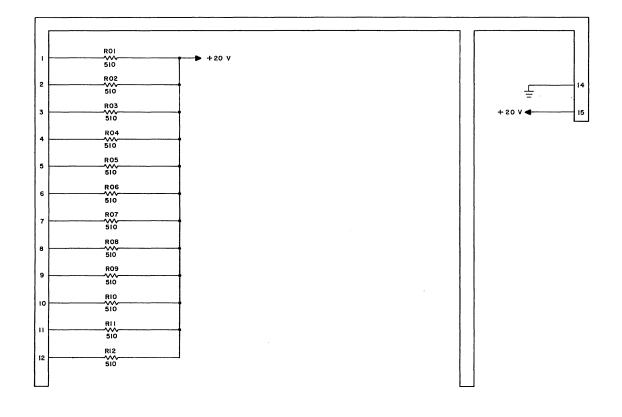

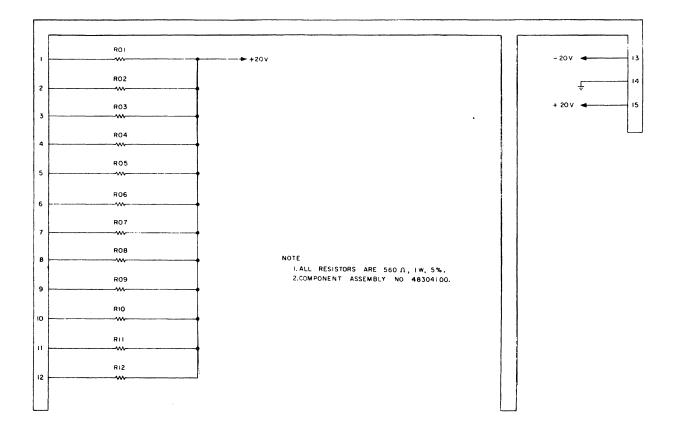

| Resistor Termination                         | $\mathrm{EEG}$          |

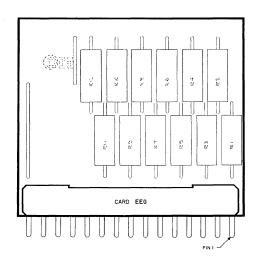

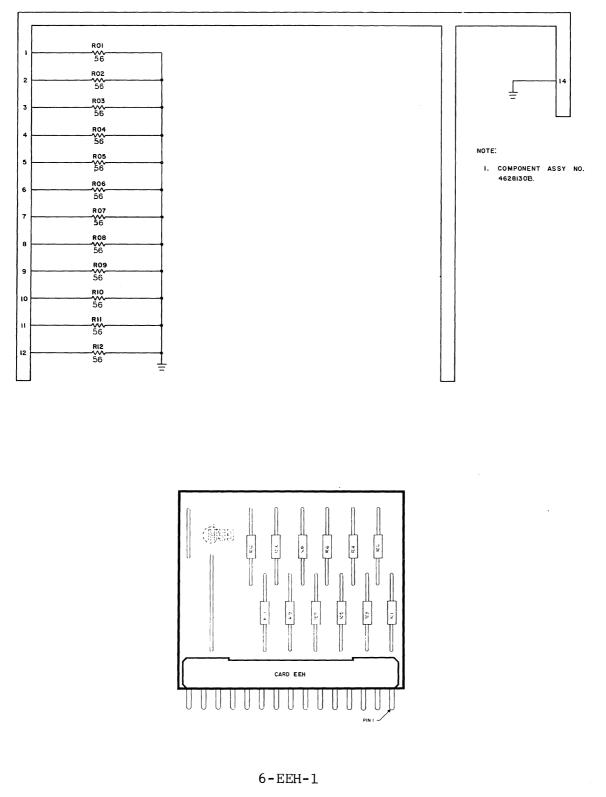

| Resistor Termination                         | ${ m EEH}$              |

| Resistor Termination                         | EEK                     |

| Capacitor Termination                        | $\mathrm{EEL}$          |

| Resistor Termination                         | $\mathrm{EEM}$          |

| Capacitor Termination                        | EEO                     |

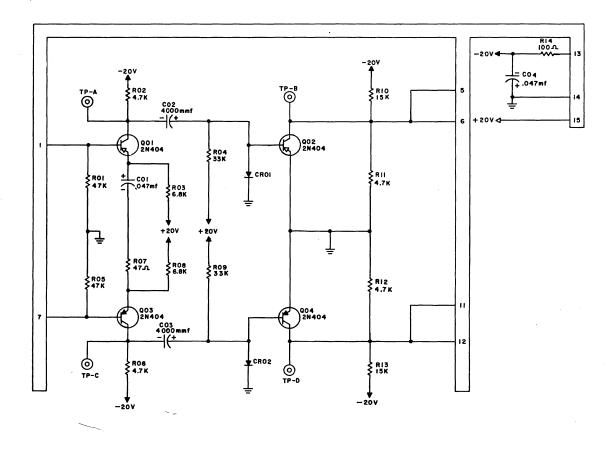

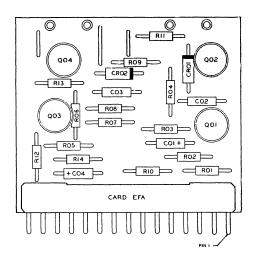

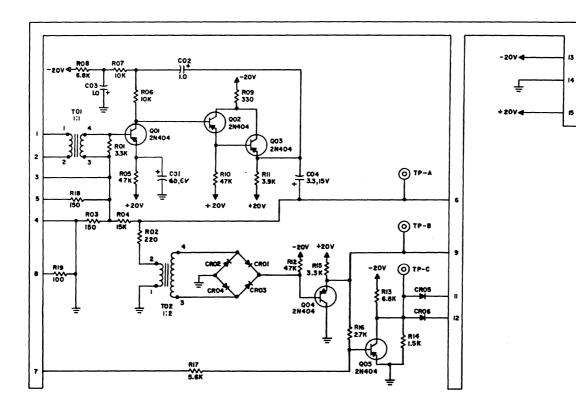

| Clock Amplifier                              | EFA                     |

| Read Level Detector                          | EGA                     |

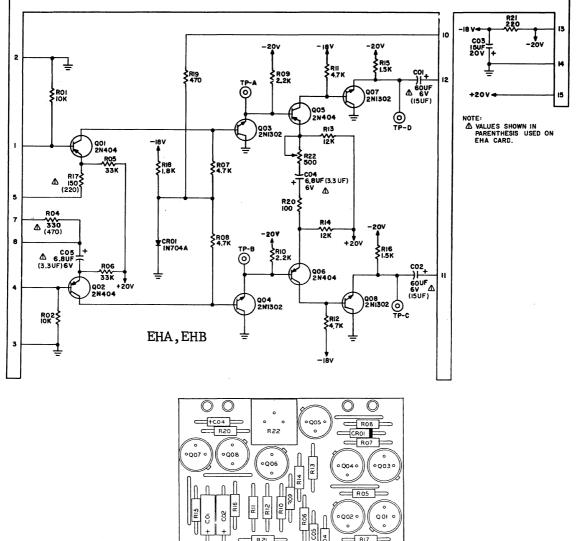

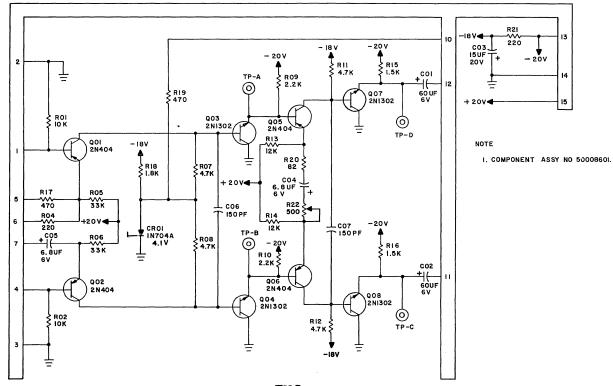

| Read Preamplifier                            | ЕНА, ЕНВ, ЕНС           |

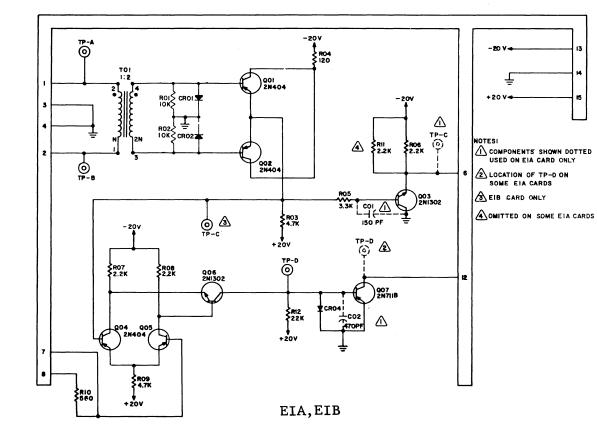

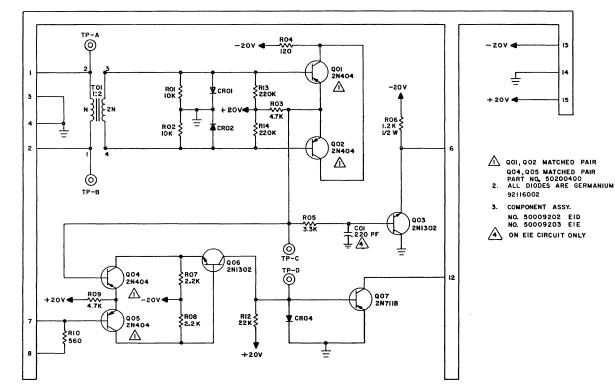

| Read Level Detector                          | EIA, EIB, EID, EIE      |

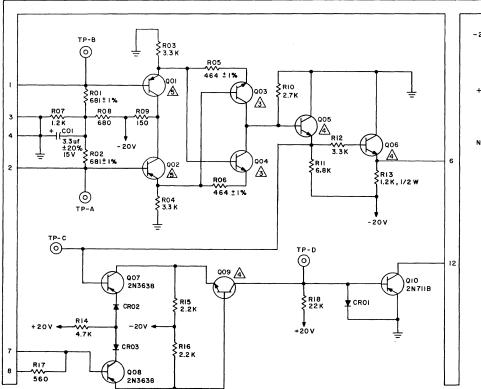

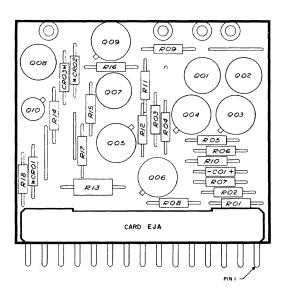

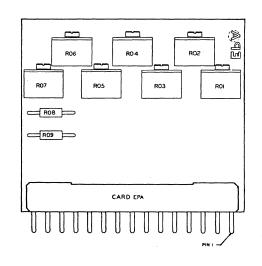

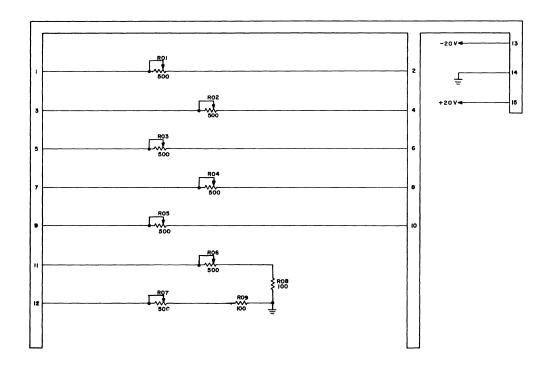

| Rectifier and Threshold Detector             | EJA                     |

| Potentiometer                                | EPA                     |

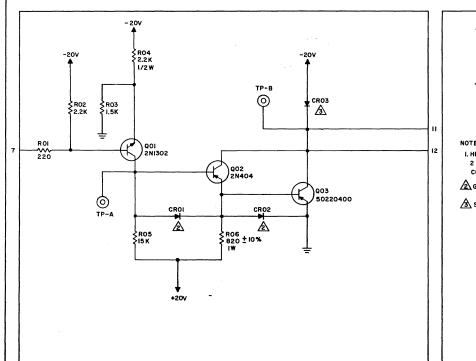

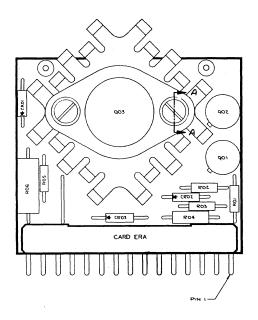

| Solenoid Driver                              | ERA                     |

| Delay Control Potentiometers                 | ESA                     |

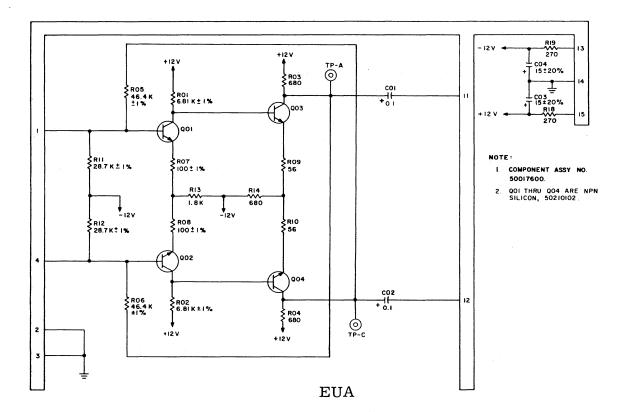

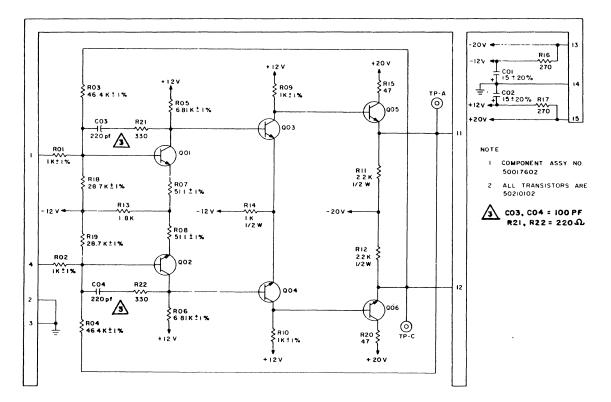

| Differential Amplifier                       | EUA, EUC, EUD           |

| Receiver Flip-Flop                           | EVB                     |

| Zero-Crossing Detector                       | EWA, EWC                |

| Peak Detector                                | $\mathrm{EWB}$          |

| AGC Attenuator                               | EZA                     |

| Shaper Flip-Flop                             | FAB                     |

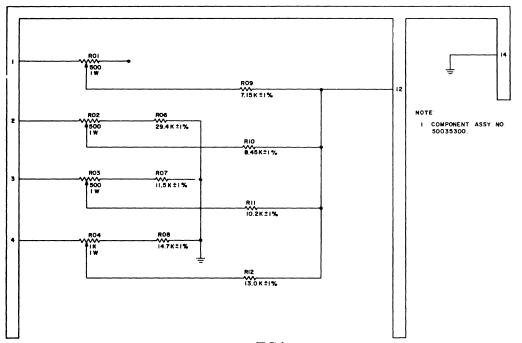

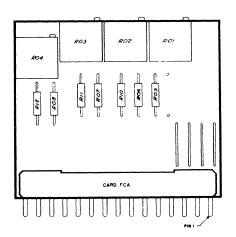

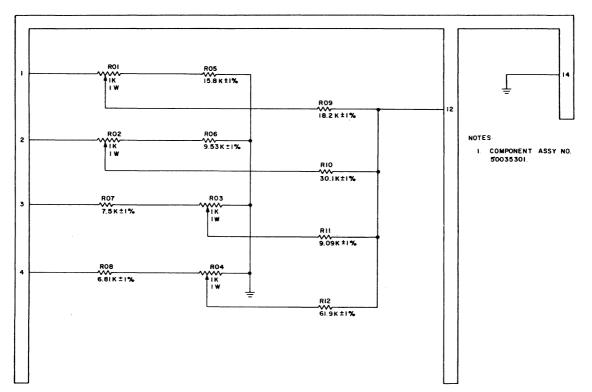

| Inner and Outer Track Select and Summing Net | tworks FCA. FCB. FCC. ] |

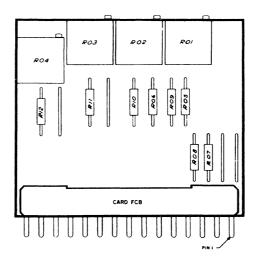

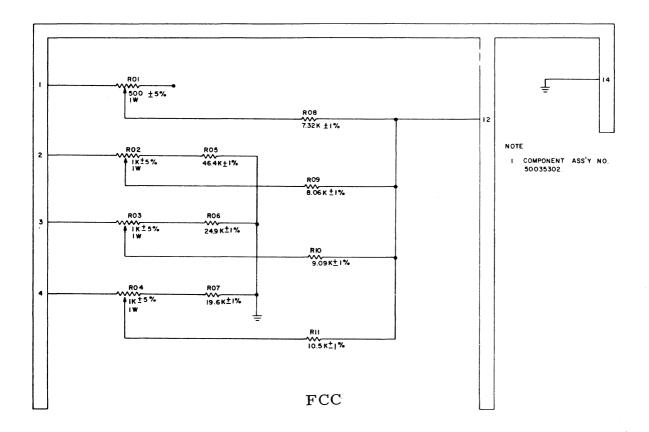

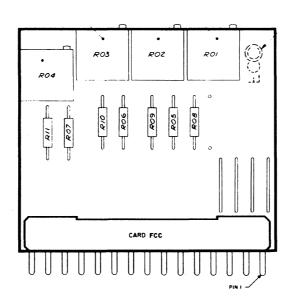

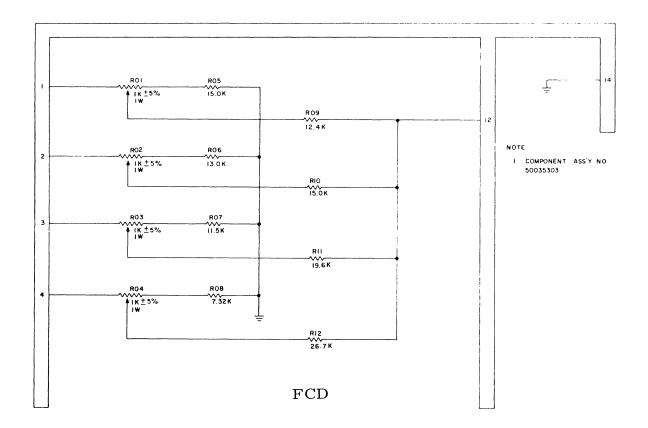

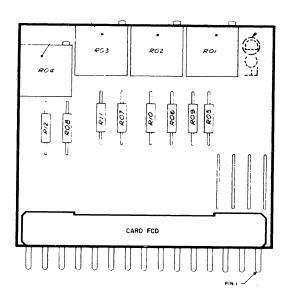

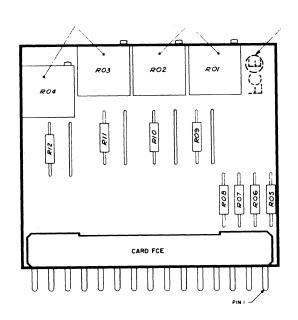

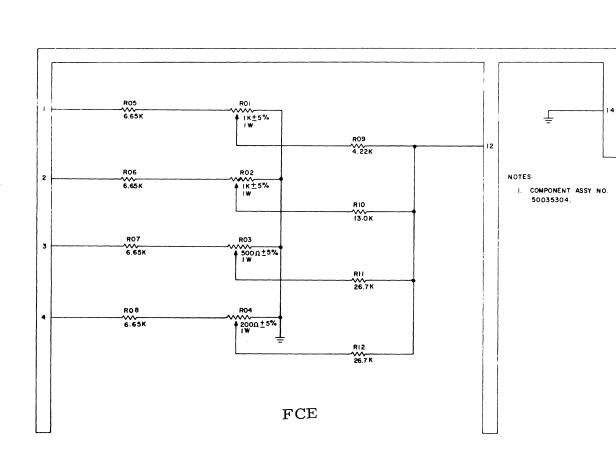

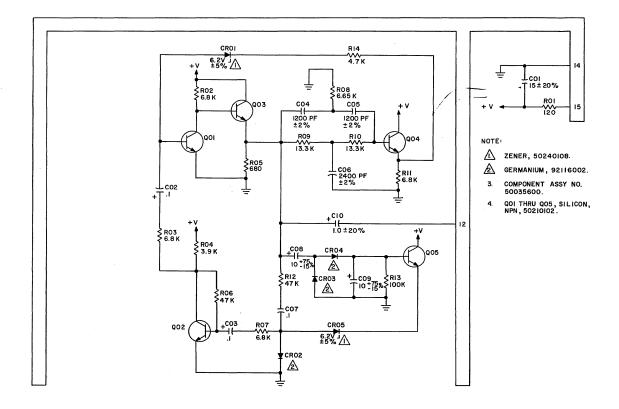

Inner and Outer Track Select and Summing Networks FCA, FCB, FCC, FCD, FCE

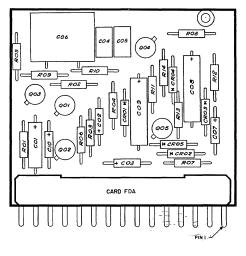

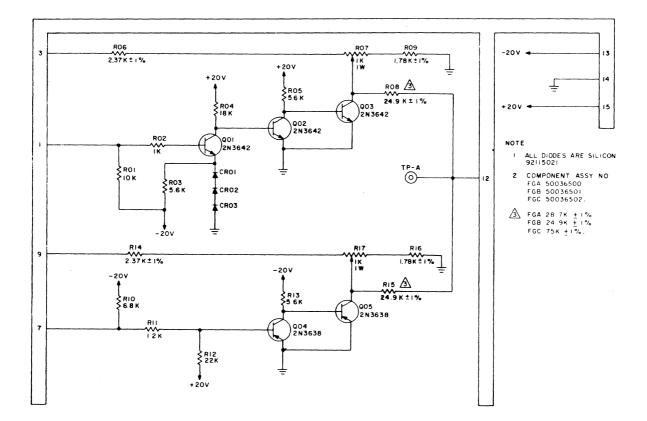

| Oscillator                                               | FDA                                       |

|----------------------------------------------------------|-------------------------------------------|

| Clamp and Summing                                        | FGA, FGB, FGC                             |

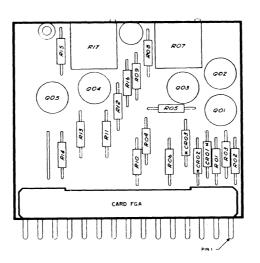

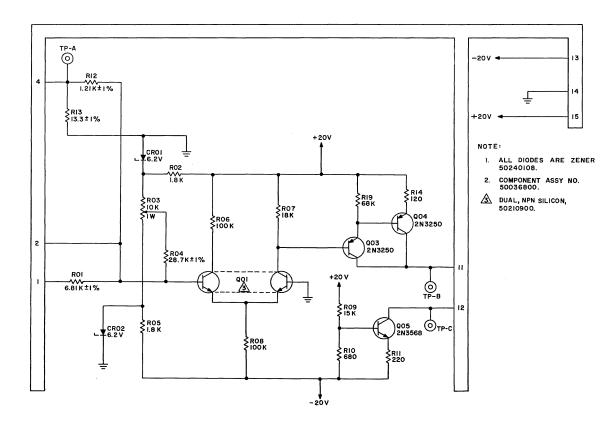

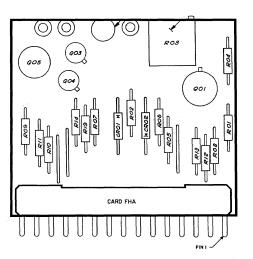

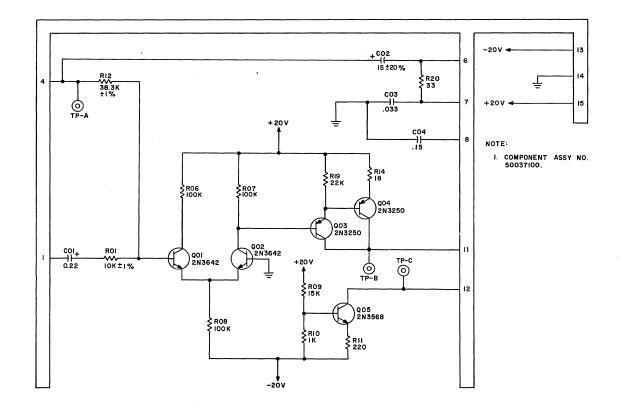

| Valve Amplifier                                          | FHA                                       |

| Power Amplifier                                          | FIA                                       |

| Servo Cycling Generator                                  | FJA                                       |

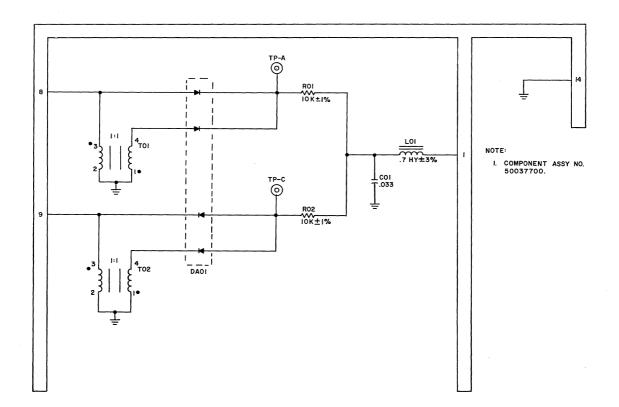

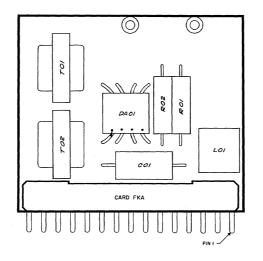

| Demodulator                                              | FKA                                       |

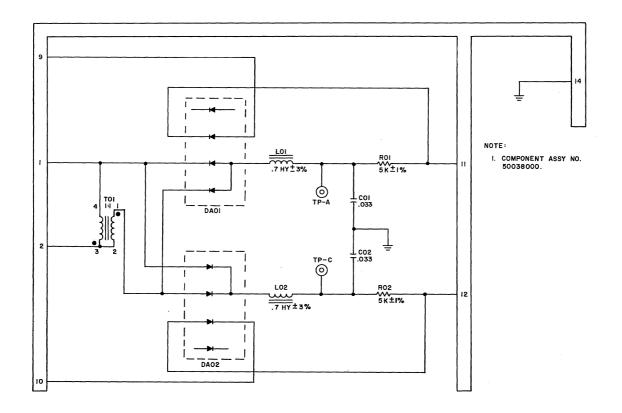

| Bridge Rectifier                                         | FLA, FLB                                  |

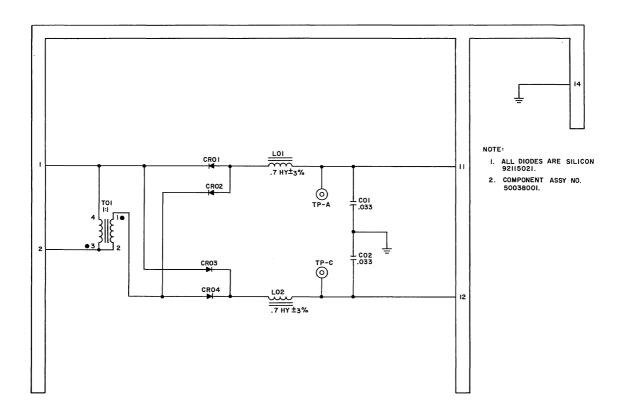

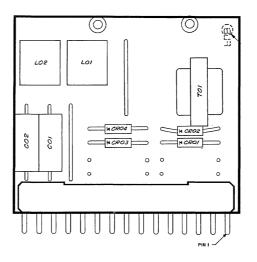

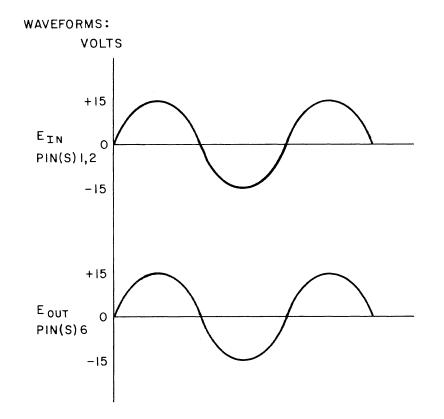

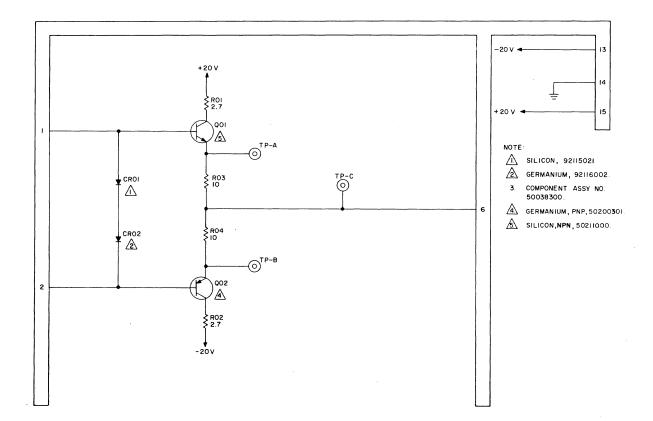

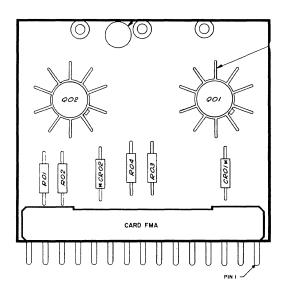

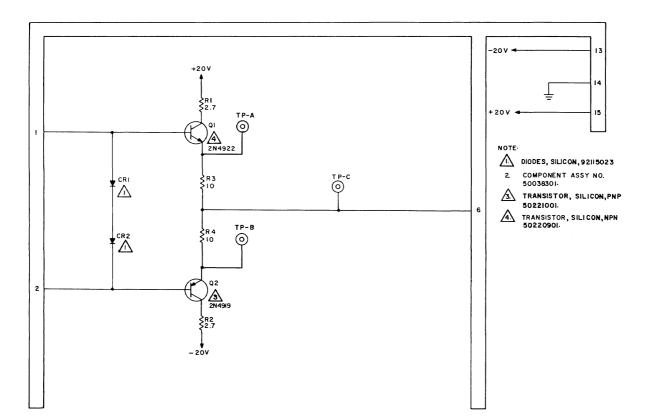

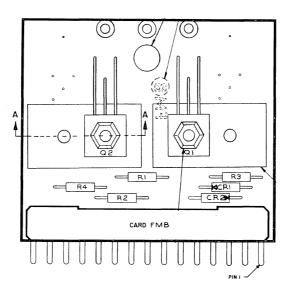

| Power Amplifier Output Stage                             | FMA, FMB                                  |

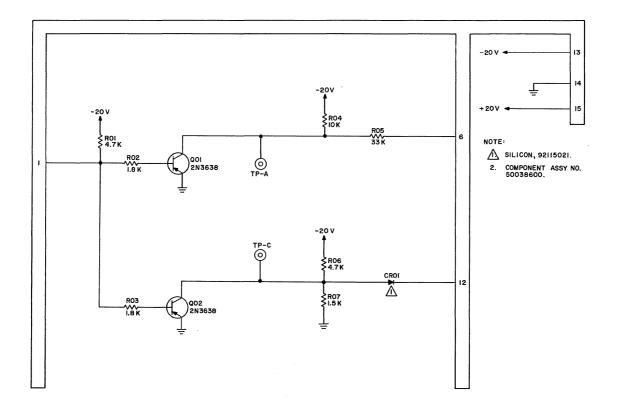

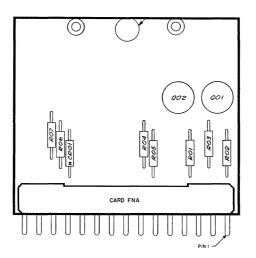

| Retract Inverter and Current Source                      | FNA                                       |

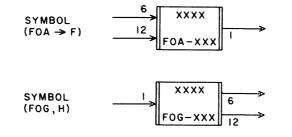

| Function Generator                                       | FOA, FOB, FOC, FOD, FOE,<br>FOF, FOG, FOH |

| Reference Amplifier                                      | FPA                                       |

| Velocity, Acceleration Summing Network                   | FRA, FRB, FRC, FRD                        |

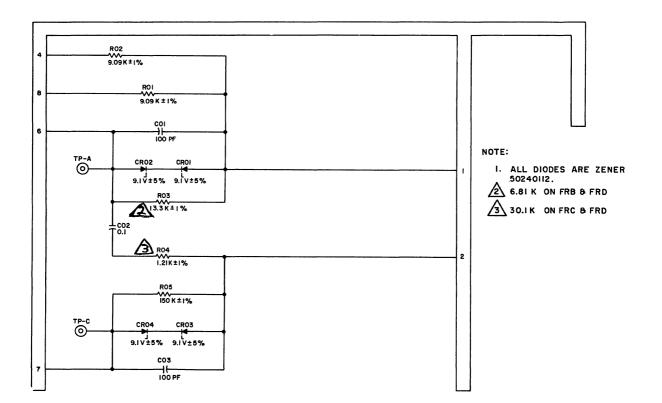

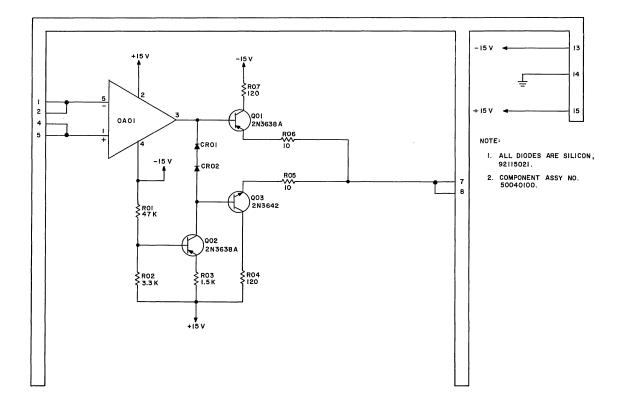

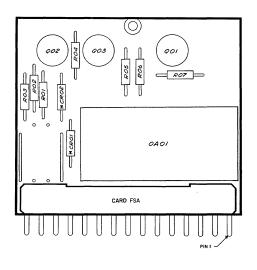

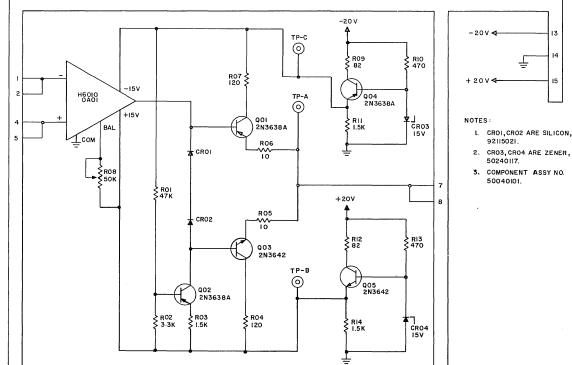

| Operational Amplifier                                    | FSA, FSB                                  |

| Velocity Summing Network                                 | FTA                                       |

| Position, Velocity, and Acceleration Summing Network     | FUA, FUB                                  |

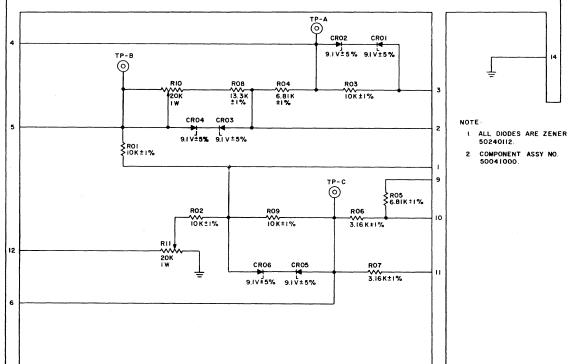

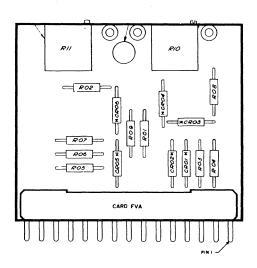

| Position and Acceleration Network                        | FVA, FVB                                  |

| Temperature Servo Amplifier                              | FWA                                       |

| Temperature Sensing Amplifier                            | FWB                                       |

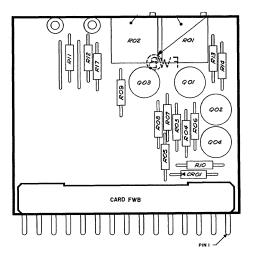

| Gated Amplifier                                          | FXB, FXC                                  |

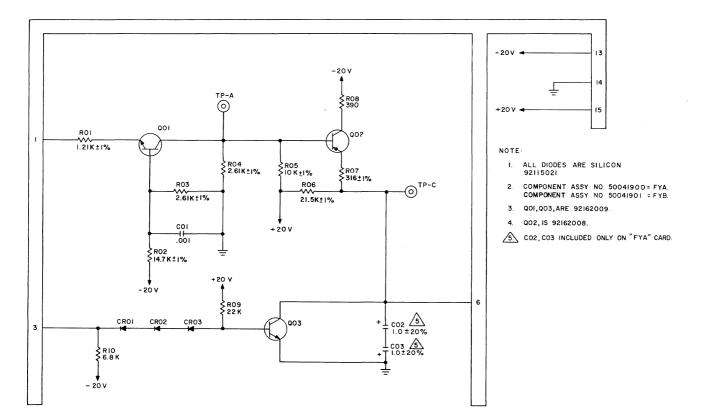

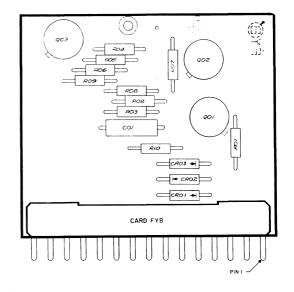

| AGC Rectifier                                            | FYA, FYB                                  |

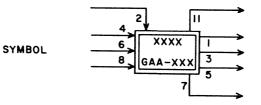

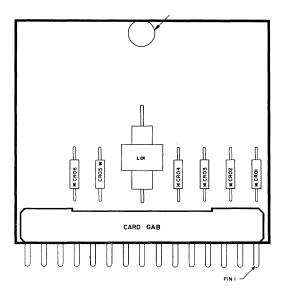

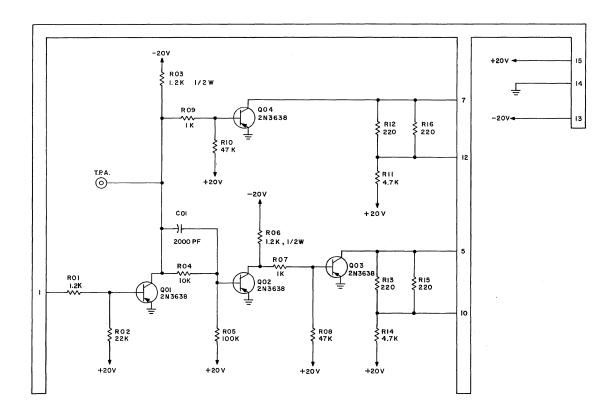

| Diode Card                                               | GAA, GAB, GAC                             |

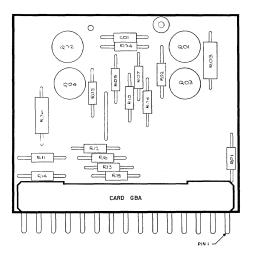

| Brake/Clutch Driver                                      | GBA                                       |

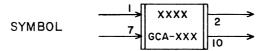

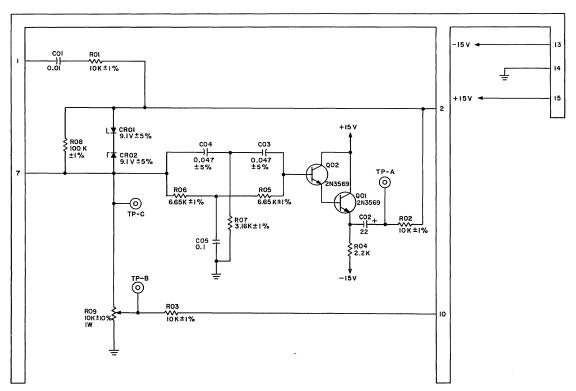

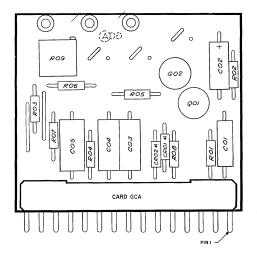

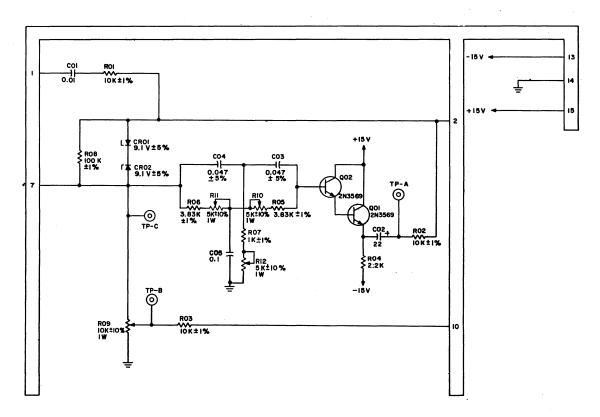

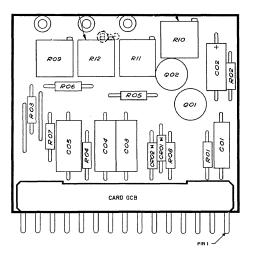

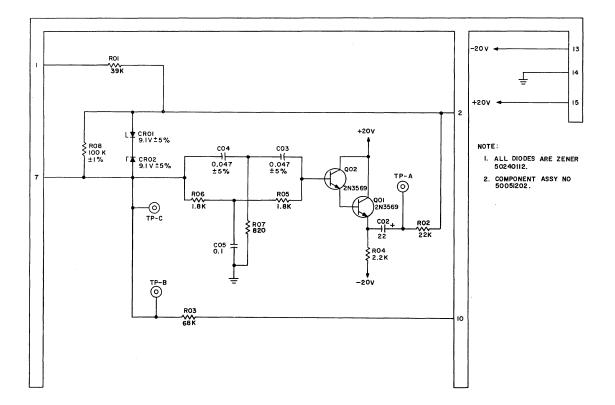

| 500 Cycle Twin "T" Notch Network                         | GCA, GCB                                  |

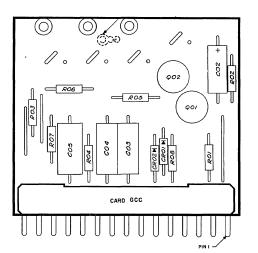

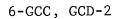

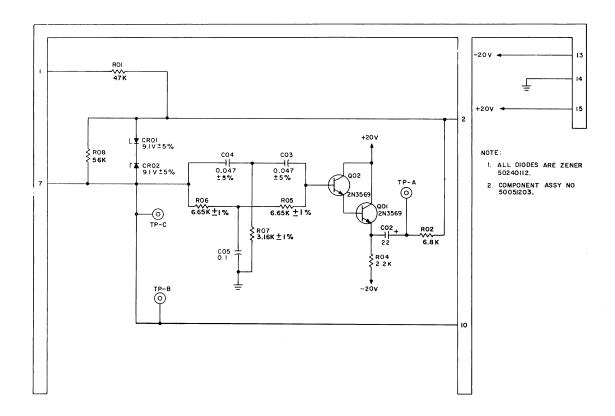

| Notch Networks                                           | GCC, GCD                                  |

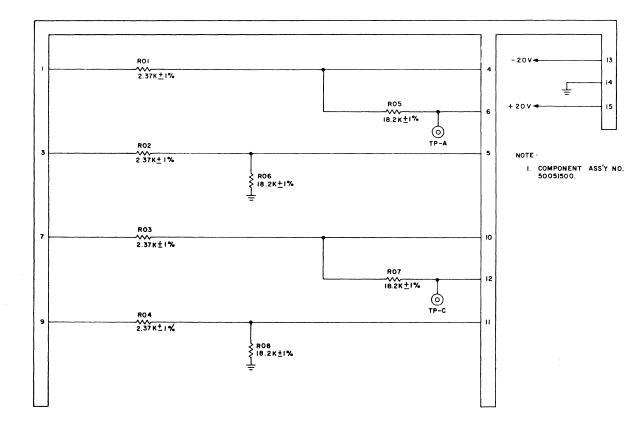

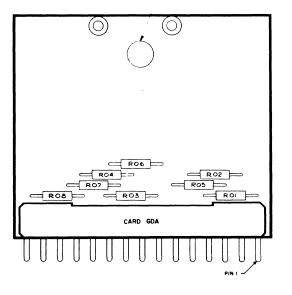

| Pressure Transducer                                      | GDA                                       |

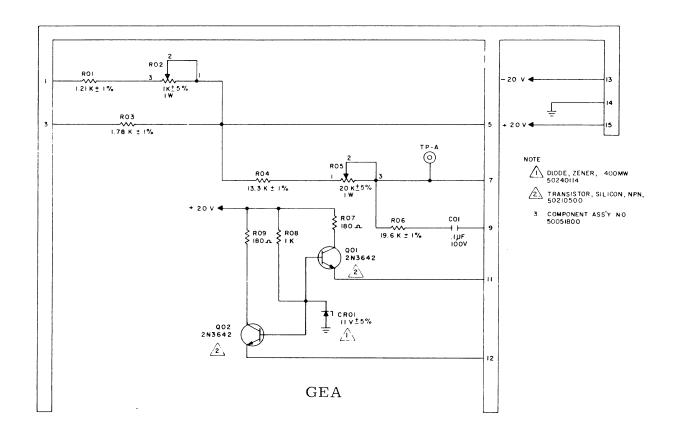

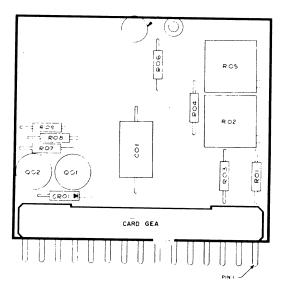

| Differential Pressure Gain and Balance                   | GEA                                       |

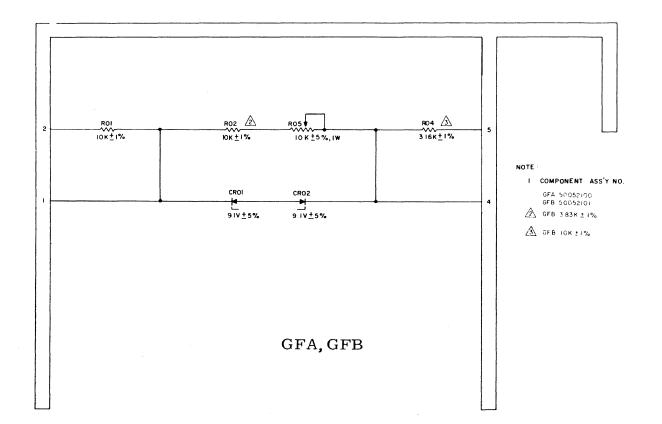

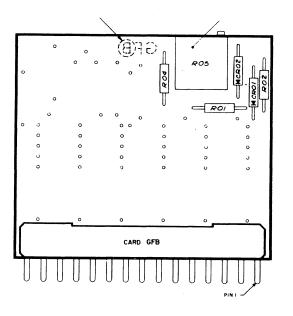

| Long Stroke Acceleration                                 | GFA,GFB                                   |

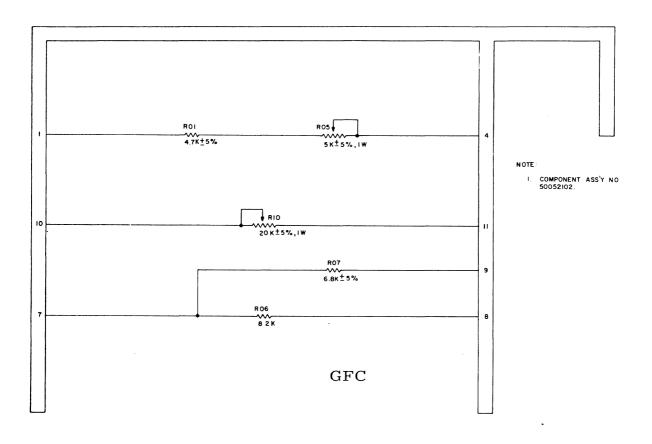

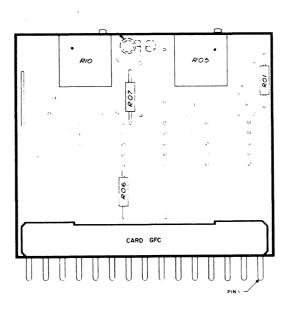

| Differential Pressure and Acceleration Crossover<br>Trim | GFC                                       |

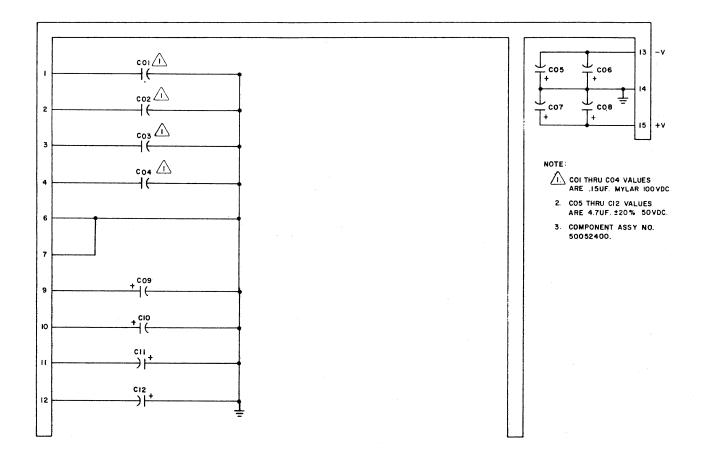

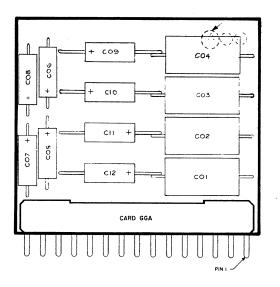

| Capacitor Card       | GGA      |

|----------------------|----------|

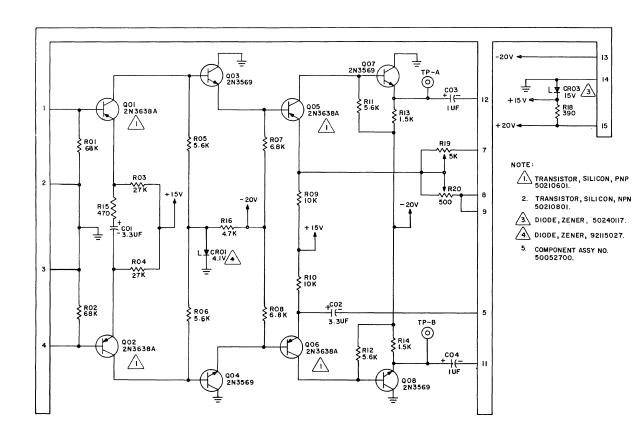

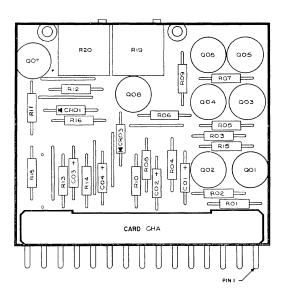

| Preamplifier         | GHA      |

| Read Level Detector  | GIA, GIB |

| 800 & 1050 Hz Filter | GOA      |

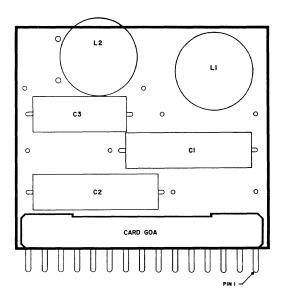

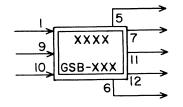

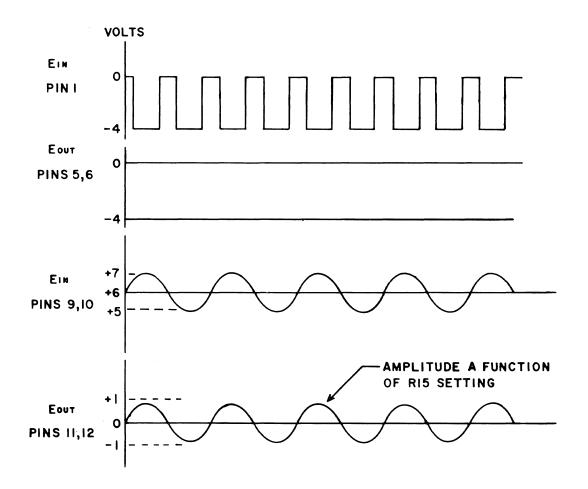

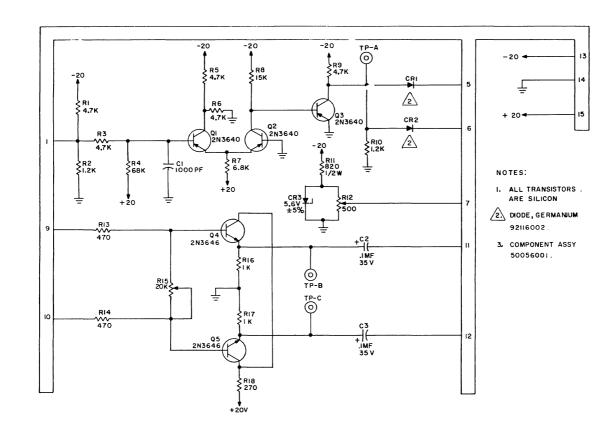

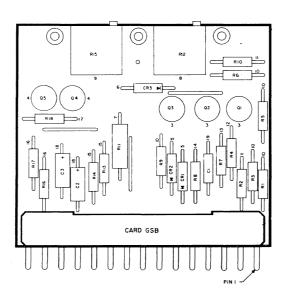

| Level Monitor        | GSB      |

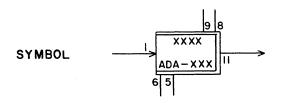

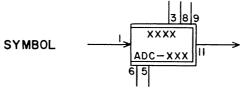

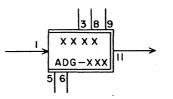

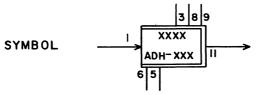

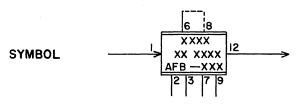

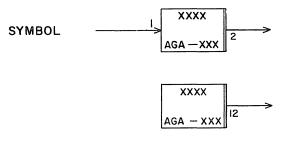

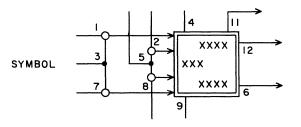

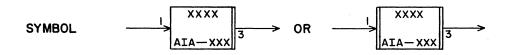

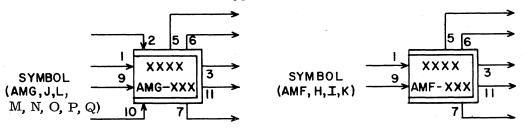

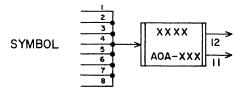

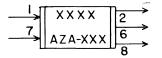

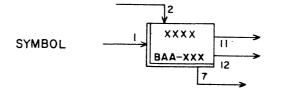

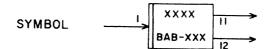

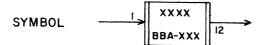

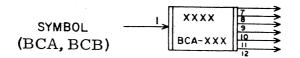

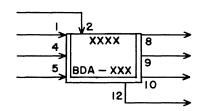

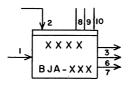

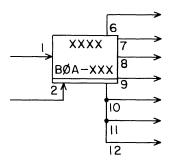

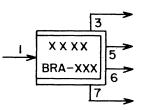

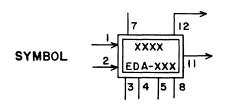

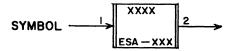

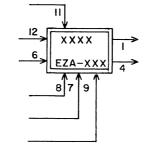

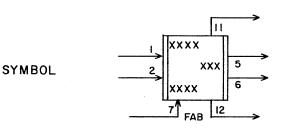

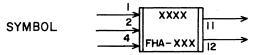

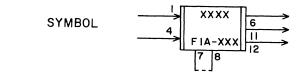

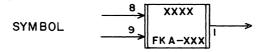

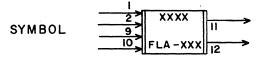

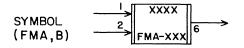

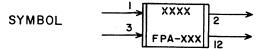

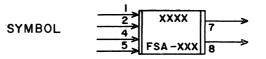

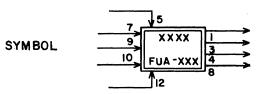

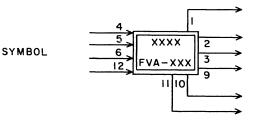

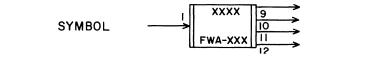

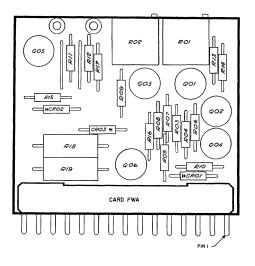

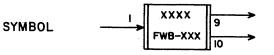

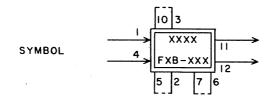

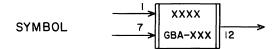

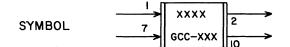

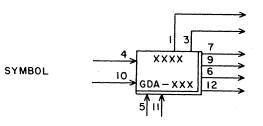

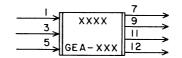

#### LOGIC SYMBOLS

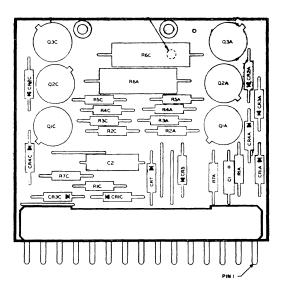

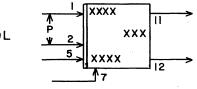

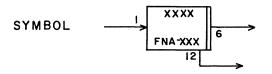

All special modules (including delays\*) are represented by rectangles. Inputs are shown with arrows normally from the left, and outputs normally extend out to the right. Other connections to the card such as jumpers and grounds, except disabled OR inputs, are shown without arrowheads. The double bar on one or more sides of the symbol is used to indicate a nonlogic voltage level.

EXAMPLE

\* Passive delays such as capacitors mounted on a card are represented by an oval symbol (see section 2).

#### MODULE DESIGNATION

Five general categories are used for classifying special purpose circuits for peripheral equipment:

A-D (AA-, AB-, .... DY-, DZ-)

E-H (EA-, EB-, .... HY-, HZ-)

I-N (IA-, IB-, .... NY-, NZ-)

O-T (OA-, OB-, .... TY-, TZ-)

U-Z (UA-, UB-, .... ZY-, ZZ-)

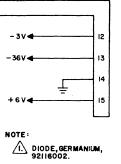

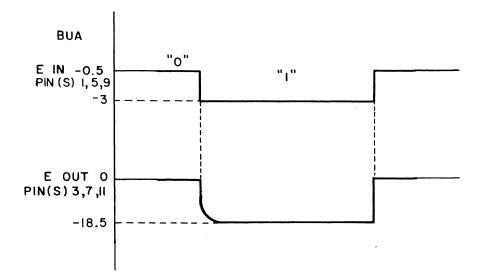

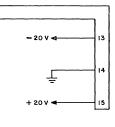

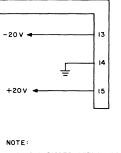

The two most significant letters (IA-, for example) define the basic circuit. The least significant letter defines slight variations with the possibility of interchange in some but not all applications. Standard power supply connections are -20v on pin 13, ground on pin 14, +20v on pin 15, and no low impedance voltage sources on other pins. Standard voltage levels on input and output are -0.5v and -3v and match internal logic of standard cards such as flip-flops and inverters (including the 10, 20, and 30 series). Nonstandard input (or output) signals indicate one or more inputs (or outputs) that may be analog or digital, but cannot generally interface with standard cards such as flip-flops and inverters.

| Category | Designation | Power Supply | Input                      | Output                     |

|----------|-------------|--------------|----------------------------|----------------------------|

| A        | AAA to DZZ  | Nonstandard  | Standard or<br>Nonstandard | Standard or<br>Nonstandard |

| E        | EAA to HZZ  | Standard     | Nonstandard                | Nonstandard                |

| I        | IAA to NZZ  | Standard     | Standard                   | Nonstandard                |

| 0        | OAA to TZZ  | Standard     | Nonstandard                | Standard                   |

| U        | UAA to ZZZ  | Standard     | Standard                   | Standard                   |

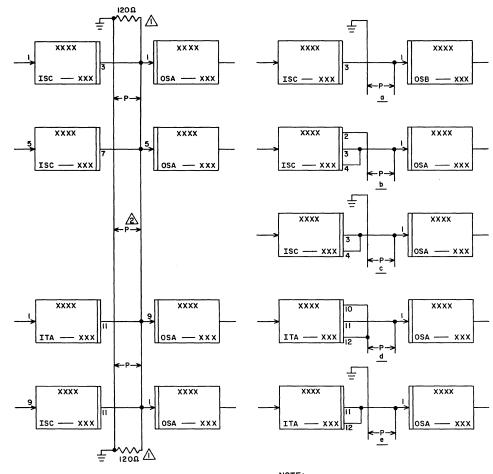

#### 601 DAISY CHAIN LINE TRANSMISSION SYSTEM

The term "601 Daisy Chain Line Transmission System" is derived from its initial application as a digital-signal connection on a time-shared line between several (8 max.) 601 Tape Transports and a 3127 Controller. The following description contains background and ground rules for this system and presents information for other possible applications.

Design criteria included the following:

- Three output amplifier circuits and three input amplifier circuits, 1604-type cards with pin assignments compatible with existing 69-and 87-type cards.

- Provision for paralleling multiple output amplifiers (transmitters) and input amplifiers (receivers) at any point on the same line, with or without power supply voltage available.

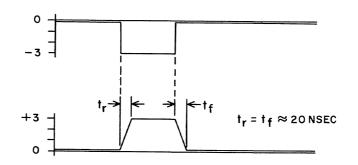

- Ability to transmit l-usec logical "1" pulses from any output amplifier through any input amplifier to set a 1604-series flip-flop (500 kc maximum transmission rate).

- 4. Ability to operate with standard 24-pin I/O cables (23 twisted pairs with one side of each pair grounded) over a length of 100 feet or more.

- 5. Simplification of terminators and bias voltages for terminators and output amplifiers.

- 6. Circuits capable of operating in 25°C to 50°C ambient air.

With the above basic design objectives, the approach was taken to simplify special output amplifier and terminator biasing requirements by employing line signals that drive away from ground. Thus both shorts and opens on a line result in a logical "O" at a receiver. Output amplifiers cannot drive a "1" on a line without power supply voltages, and both input and output amplifiers have disconnect features built in to prevent unwanted loading of the time-shared line when power supply voltages are off in some units.

The twisted-pair cable is satisfactory from an attenuation standpoint over 100-foot lengths but does present crosstalk problems unless rise and fall times are limited in volts per microsecond. A controlled rise and fall time of  $\frac{1}{2}$  usec for the 2-volt swing is used as a compromise

with speed. Crosstalk can be further reduced by using coax. However, unless bulky coax cables are used, attenuation increases and the characteristic impedance decreases; this requires greater line current (higher power levels) or lower voltage excursions, or results in reflections and ringing from improper terminations. The connector used with the 24-pin I/O cables permits the mounting of 23 terminating resistors directly to 23 pins (with one end of the resistors grounded to the remaining pin). Power in each termination is low (1/30 w for 120 ohms) for a logical "1" and essentially zero for a logical "0" on the line. This provides a terminator that can fit in the same space as a 24-pin I/O cable and still be reasonable in cost. Where module flexibility of extending cables is not required, input amplifiers with built-in terminating resistors are available; and the jumper option on the output amplifier may be employed without requiring external terminator resistors.

The voltage excursion of the output amplifier was selected to have a basic excursion that would be about five times the tolerance of the expected input amplifier switching threshold and twice the nominal switching threshold value of the input amplifier. A 2-volt excursion allows realistic tolerances in parts employed in the output and input amplifiers and a margin of safety for ringing, crosstalk, attenuation, and external interference for both logical "0" and logical "1" signals on the line. The positive excursion of the line connecting the output and input amplifiers was selected from a standpoint of circuit simplicity and cost. It is also more compatible with the newer positive logic computer circuits employing silicon components. In each circuit, two transistors are required. One transistor is used for inversion to standardize the voltage excursion over a small input threshold, and the other transistor provides current amplification.

The output amplifier, which receives its input from standard logic, was also designed to have a switching threshold tolerance that permits some noise on its input whether in the "O" or "1" state. Both stages of the output amplifier and one stage of the input amplifier use highfrequency npn silicon transistors. These provide a good compromise in voltage breakdown, power capability, and switching uniformity at moderate cost.

This system may not be ideal in each of the performance criteria,

but it does provide a useful application region within the following ground rules:

- 1. OS..series input amplifiers are designed to switch at +1.0<sup>+</sup>0.2v. System application should provide a minimum "1" line signal of +1.6v and a maximum "0" line signal of +0.3v. This allows a reserve for seldom-encountered signal interference and variable factors not usually predictable or easily measured, such as:

- a. Crosstalk from outside interference.

- b. Partial drive leakage from parallel output amplifiers not remaining completely off because of power supply coupling, for example. (This could produce an erroneous "1".)

- c. Slight changes in input amplifier switching because of aging, ambient temperature changes, or small errors in initial card testing measurements.

- d. Imperfections in ground reference points.

The minimum "1" line signal of +1.6v and the maximum "0" line signal of +0.3v shall be attainable under <u>any</u> combination of the following worst-case conditions:

- a.\* +20v power supply of IS..series or equivalent output amplifier at lowest expected value (minimum IS..series output voltage into a 60-ohm load is +2.0v with a +20v power supply and proportionably less as +20v is decreased).

- b.\* Maximum line attenuation calculated on the basis of cable type and maximum distance between any output amplifier and input amplifier.

- c.\* Maximum number of OS..or equivalent input amplifiers to be connected to a signal line. (With power on, each OS..causes a 0.03v maximum negative bias to a line terminated in 120 ohms at both ends.

- d. Maximum crosstalk from other signals in the cable. (Worst case is usually when other signals are closely in phase; position of worst-case crosstalk varies much over a cable length with cables.)

- e. Maximum ringing because of reflections of non-ideal cable and termination conditions.

- \* These conditions (a, b, and c) tend to reduce the "1" line signal margins. It may be the best compromise to increase cable termination to 150 ohms where "1" signal margins are used up before the "0" signal margins. The following 24-pin terminators are documented for production. (Pin b is the ground reference in all units.)

| Part No.          | <u>Ohms +5%</u> |

|-------------------|-----------------|

| 45948500          | 56              |

| 45948501          | 68              |

| 45948502          | 82              |

| 45948503          | 100             |

| 45948504          | 120             |

| 45 <b>9</b> 48505 | 150             |

| 45948506          | 180             |

| 45948507          | 220             |

- 2. If the rules of paragraph 1 are satisfied, up to 8 output and 8 input amplifiers may be paralleled on any signal line. They may be grouped or located at different locations. Lines should not "Y" out to several ends, although short stubs may be used to wire to input or output amplifiers. Terminators shall be placed within 3 feet of the end of each cable.

- 3. Time-shared lines are subject to a "1" coming from any output amplifier on the line. While the system is designed to work with either power on or off on inactive output amplifiers (no external bias required), power sequencing of equipment should provide one of the following during the turning on or turning off of power of any unit with an output amplifier:

- a. Disconnecting +20v from pin 15 of IS.. series cards during time any input can approach a logical "1" threshold.

b. Clamping the input of the amplifier at ground and

assuring that the +20v supply does not exceed the -20v supply by more than 20 percent.

- c. Disabling the AND gates at the output of all input amplifiers (receivers).

- d. Providing a program that can repeat an operation when errors are received because of erroneous "1" signals coming from power sequencing operations.

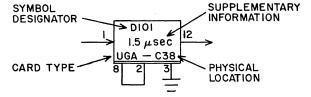

- 4. The following card types are the present family of cards using this transmission system:

- a. ISA Output Amplifier (3 circuits) -- preproduction

version of the ISC, but with less predictable turnoff

time from "1" to "0".

- b. ISC Output Amplifier (3 circuits) -- 0.5 ±0.15 usec rise and fall times. Optional 120-ohm termination to ground for each of the three circuits by using external jumpers. For best results, use caution on loading test point.

- c. ITA Pulse Delay and Output Amplifier (1 circuit) -- pins 1 - 8 perform delay function of UGA. Pins 11 and 12 are output and optional 120-ohm termination respectively.

- d. ASA Quantizer and Output Amplifier (3 circuits) --Quantizing point is designed for about -6v but usable above and below this value with variations in fall time. Circuit is generally less uniform in output waveform than ISC. A 120-ohm terminating resistor is permanently wired to the output. Therefore, the circuit is designed to be located only at one of two ends of a line.

- e. OSA Input Amplifier (3 circuits) -- No input termination resistor available. Input is single-ended to ground and output of each circuit has 3 AND diodes to match standard logic.

- f. OSB Input Amplifier (3 circuits) -- Like the OSA except with 120-ohm input termination to ground. Therefore, the circuit is designed to be located only at one of the

two ends of a line. The OSB does not include all the line-loading disconnect features of the OSA when power is turned off.

As required in future systems, the family of cards may be expanded to include the following:

- a. Output amplifier with fast rise and fall times.

- b. Output amplifier with 2 or 3 OR inputs but with only 2 circuits.

- c. Input amplifier with differential input stage for common-mode interference rejection on twisted-pair lines.

- d. Input amplifier with 0.7v nominal switching point for longer impedance terminations.

601 DAISY CHAIN WIRING SHOWING 4 OUTPUT AND 4 INPUT AMPLIFIERS ON A TIME ---- SHARED LINE NOTE: ALTERNATE WAYS OF TERMINATING A LINE ARE SHOWN IN a,b,c,d, and e. TWISTED PAIR

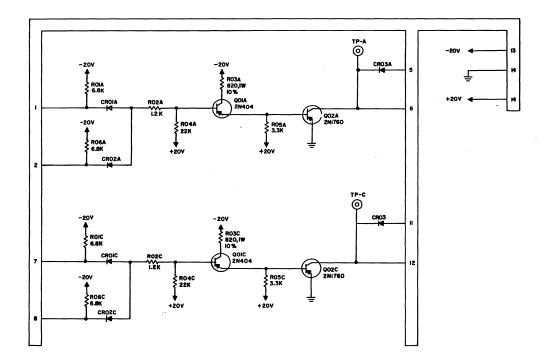

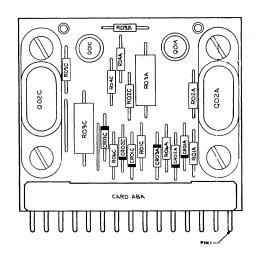

#### RELAY PULLER ABA

This circuit is used to drive high surge current loads such as lamps or the discharge of capacitors, or inductive loads such as relays and solenoids. It is particularly useful in driving loads up to 0.6 amp which are terminated at negative voltages between -5v and -36v.

The relay puller circuit can also be used as a slow speed L--- card. The input-output voltage levels are the same for both cards.

This circuit is similar to the IAA relay puller, but has an added "OR" input on each of the two circuits as well as a clamping diode available on pins 5 and 11 to limit the negative excursion when inductive loads are switched off.

The input stage of the relay puller circuit has its transistor connected as an emitter follower with the collector returned to -20v through a limiting resistor, R03. The first stage emitter follower current does not flow through the load as it does in circuits such as the 55 card, thereby limiting collector voltage on Q01 to -20v; Q02 may have excursions to -50v. The only current flowing to the load in the turnoff condition is the leakage current of the output transistor. Turnon time is 5 usec maximum and turnoff switching is 25 usec maximum.

6-ABA-2

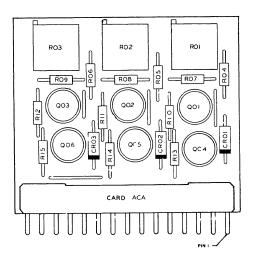

### PHOTODIODE BIAS AND PREAMPLIFIER

ACA

The photocell amplifier is designed to receive inputs from photodiodes or silicon solar cells. The output of the amplifier may be terminated by the input of a standard inverter or an "M" card. The output from the standard inverter or "M" card is a "l" when the photocell is illuminated and a "0" when unlighted. A potentiometer is provided because of the low level signals normally available from the solar cells and the wide range of sensitivity of photodiodes. This allows optimum centering of the switching point of the amplifier to compensate for the overall photocell excitation, sensitivity, and amplifier tolerance.

The first stage of amplifier A consists of an inverting amplifier, Q01. This transistor is turned on by drive current flowing through R04 from potentiometer R01. One lead of the photodiode is connected to pin 1 and the other lead is connected to a positive voltage source. Light on the photodiode causes its conductivity to increase and the photodiode current counteracts the turnon current of R01. CR01 limits the base to emitter voltage of Q01. When using solar cells, the positive terminal is normally connected to pin 1, and the output current of the solar cell counteracts the turnon current of R01.

SYMBOL

6-ACA-2

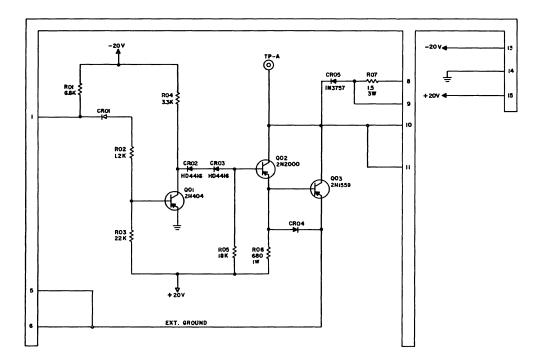

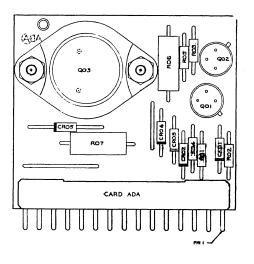

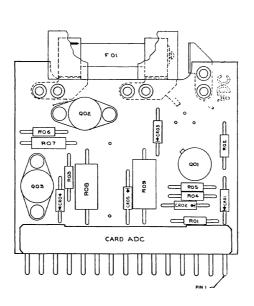

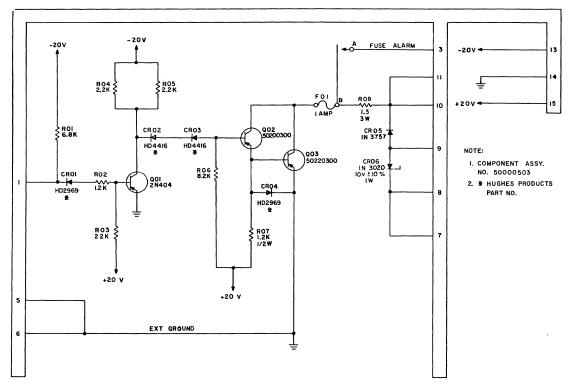

## HAMMER DRIVER CARD ADA, ADB

These cards are intended for low-speed switching of high current pulses of 1.5 to 4.5 msec duration into an inductive load such as the hammers, clutch, or brake in a 501 Printer. An open circuit on pin 1 or -3 volts will keep the circuit off. Driving pin 1 to within -0.5 volt of ground allows a current pulse to flow up to 10 amp for the ADA and 7 amp for the ADB. The duty cycle should be no greater than 12 percent, to avoid excessive heating. The minimum input pulse width needed to reach 2 percent of the maximum current level with an inductive load should be about 4 times the L/R time constant of the load. The total collector circuit resistance should be sufficient to limit the load current to 10 amp maximum for the ADA. The ADB has a 4-ohm resistor mounted on the card in the collector circuit of Q03. With a purely resistive load, the current rises to the 10 amp level in 20 usec typically.

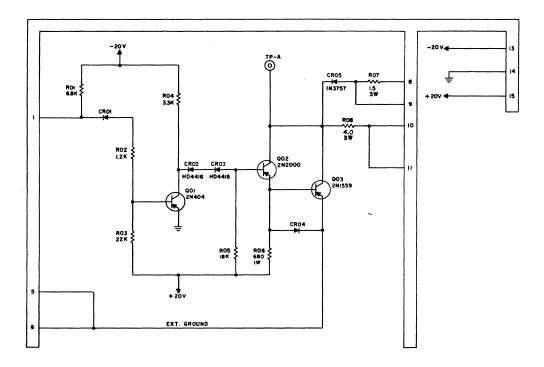

For normal operation of the circuit, the following connections are made (see circuit schematic). One side of the load plus the limiting resistor (for the ADA) is connected to pin 10 or 11. The other side is connected to the high current negative supply which can have a maximum value of -38 volts but is nominally -36 volts. Pin 8 is also connected to the -36v supply. This returns a suppression circuit consisting of CR05 and R07 to the emitter of Q03 via the power supply (-36v) common at pins 5 and 6. For good inductive spike supression, it is evident that the -36 volt lines and power supply impedance must be low. The suppressed pulse is about 10v greater than the power supply voltage. The usual + and -20 volt supplies must also be furnished to the circuit. Normally, the logic ground and high current ground are tied together at the card connector. This is done to minimize the tendency for the circuit to oscillate.

Referring to the schematic, the circuit operates as follows. Transistors Q02 and Q03 comprise a Darlington pair in a collector-loaded switch circuit. This pair is normally off with pin 1 at -3 volts. Transistor Q01 conducts when pin 1 is -3v; its collector is then at ground. This establishes  $\pm 1.2$  volts on the base of Q02 due to current flow from the  $\pm 20$  supply through R05 and silicon diodes CR02 and CR03 to ground. The emitter of Q02 and hence the base of Q03 is at  $\pm 0.5$  volt due to current from  $\pm 20$  volt through R06 and CR04 to ground. Both Q02 and Q03 are therefore off because of the reverse base voltages.

When the input goes to within -0.5 volt of ground, transistor Q01 goes off due to the divider action of R02, R03, and CR01, i.e., the base becomes positive. With Q01 collector unclamped, base current begins to flow in Q02 and Q03 from ground to the -20v supply by way of the collector load resistor R04. This turns on the Darlington circuit and lets load current flow.

In the on state and with a 10 amp load on the ADA card, the collector to emitter voltage of Q03 is about 0.5 volt. With a 12 percent duty cycle the power dissipated in Q03 is about 0.75 watt. In free air (i.e., natural convection) this dissipation causes Q03 to attain 135°F case temperature in 80°F ambient.

It is recommended that these cards be placed in moving air and away from any temperature sensitive circuits.

ADA

6-ADA, ADB-3

ADB

6-ADA, ADB-4

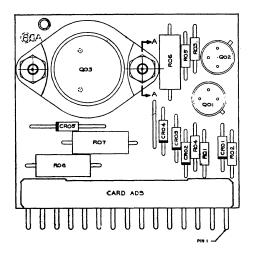

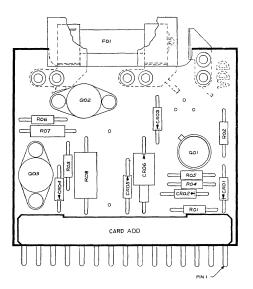

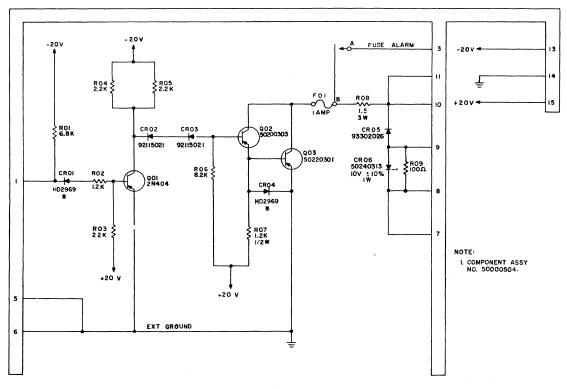

# HAMMER DRIVER ADC, ADD, ADE

The ADC, ADD, and ADE cards are used in the 501 Printer to supply 5 amp (ADC) and 7 amp (ADD, ADE) current pulses of 1.3 msec duration to the basically inductive hammer coils. An open circuit on pin 1 or -3 volts will keep the circuit off. Driving pin 1 to within -0.5 volt of ground lets the load current rise to its 5 or 7 amp levels. The maximum duty cycle of 3 percent must not be exceeded in order to keep the average transistor dissipation to a safe level.

For normal operation of the circuit, the following connections are made (see circuit schematic). One side of the hammer coil is connected at pin 10 or 11 and the other side is connected to the high-current negative power supply. The negative supply voltage is nominally -29 volts for the ADC and -36 volts for the ADD and ADE. Pin 7 or 8 is also connected to this negative supply for suppression of the inductive kick pulse. Since the suppression circuit is returned to the circuit common via the line and supply impedances, these must be kept low to insure reduction of the voltage spike across Q03. The suppressed pulse across Q03 on the hammer driver cards is limited to about 10 volts. The inductive kick pulse is brought out to pin 9. This may be used in conjunction with the OLA card in error checking systems. The pulse is about 100 usec wide with the ADC and 1 msec with the ADD and ADE cards.

Referring to the schematic, the circuit operates as follows. Transistor pair Q02 and Q03 make up a Darlington switching circuit. The pair is normally off when pin 1 is at -3 volts on the base of Q02 due to current flow from the  $\pm 20$  supply through R06 and silicon diodes CR02 and CR03 to ground. The emitter of Q02 and hence base of Q03 is at  $\pm 0.5$  volt due to current flow from  $\pm 20$  volts through R07 and CR04 to ground. Both Q02 and Q03 are therefore off because of the reverse base voltage.

When the input goes to within -0.5 volt of ground, transistor Q01 goes off due to the divider action of R02, R03, and CR01, i.e., the base becomes positive. With Q01 collector unclamped, base current begins to flow in Q02 and Q03, from ground to the -20v supply by way of collector load resistors R04 and R05 in parallel. This turns on the

$\sum_{i=1}^{n}$

C C

Darlington pair and allows the load current to flow.

In the on state and with a 3 percent duty cycle, the average dissipation in the collector load resistor with 7 amp and 3 percent duty cycle is about 2 watts. This gives a temperature on the resistor of about 180° F. This necessitates placing the card in moving air to eliminate damage to the card.

ADC

6-ADC, ADD, ADE-2

ADD

6-ADC, ADD, ADE-3

ADE

6-ADC, ADD, ADE-4

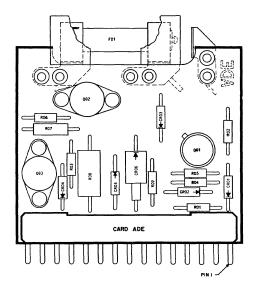

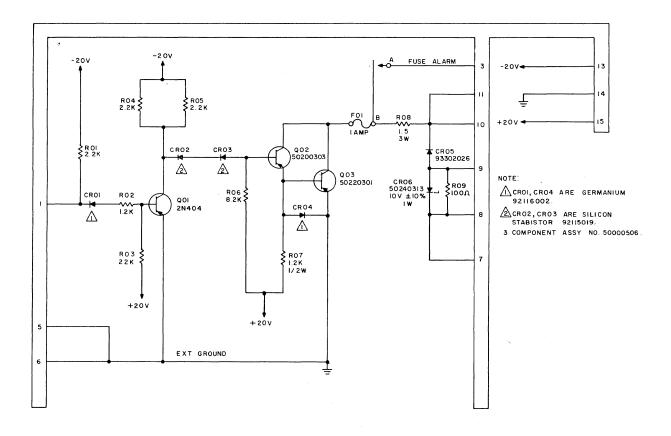

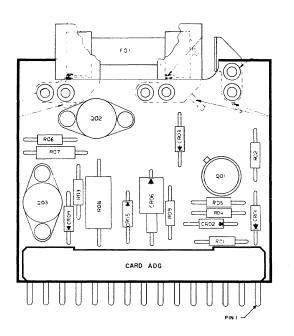

## HAMMER DRIVER ADG

The ADG is designed to minimize the possibility of turn on during controller power down. Except for a value of 2.2K ohms for R01 and the use of a different diode for CR02 and CR03, the ADG is similar to the ADE in circuit operation, application information, and output current.

6-ADG-2

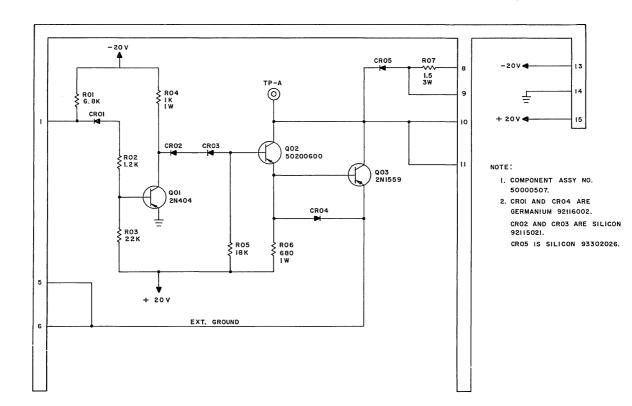

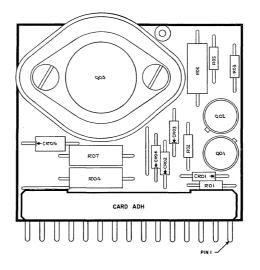

#### CLUTCH-BRAKE DRIVER ADH

This card is used for low-speed switching of high current pulses of 4.5 msec duration into an inductive load such as the clutch or brake in a 501 printer. An open circuit on pin 1 or -3 volts will keep the circuit off. Driving pin 1 to within -0.5 volts of ground allows a current pulse up to 15 amperes to flow. The duty cycle should be no greater than 12 percent. The minimum input pulse width needed to get 15 amperes into an inductive load should be about 4 times the L/R time constant of the load. An external resistor has to be added to limit the current to 15 amperes maximum. With a resistive load, the minimum input pulse width should be as great as the rise time of the circuit - in this case, 50 usec.

For normal operation of the circuit the following connections are made (see circuit schematic). One side of the load plus the limiting resistor is connected to pin 10 or 11. The other side is connected to the high current negative supply, which can have a maximum value of -38 volts but is nominally -36 volts. Pin 8 is also connected to the -36v supply. This returns a suppression circuit consisting of CR05 and R07 to the emitter of Q03 via the power supply (-36v) common at pins 5 and 6. For good inductive spike suppression, it is evident that the -36 volt lines and power supply impedances must be low. The suppressed pulse is about 10v greater than the power supply voltage. The usual + and -20 volt supplies must also be furnished to the circuit. Normally the logic ground and high current ground are tied together at the card connector, (i.e., jumper pins 5 and 14).

Referring to the schematic, the circuit operates as follows. Transistors QO2 and QO3 comprise a Darlington pair in a collector-loaded switch circuit. This pair is normally off with pin 1 at -3 volts. Transistor QO1 conducts when pin 1 is -3v; its collector is then at ground. This establishes +1.2 volts on the base of QO2 due to current flow from the +20 supply through RO5 and silicon diodes CRO2 and CRO3 to ground. The emitter of QO2 and hence the base of QO3 is at +0.5 volts due to current from +20v through RO6 and CRO4 to ground. Both QO2 and QO3 are therefore off because of the reverse base voltages. When the input goes to within -0.5 volts of ground, transistor Q01 goes off due to the divider action of R02, R03, and CR01, i.e., the base becomes positive. With Q01 collector unclamped, base current begins to flow in Q02 and Q03 from ground to the -20v supply by way of the collector load resistor R04. This turns on the Darlington circuit and lets load current flow.

In the on state and with a 15-ampere load, the collector to emitter voltage of Q03 is about 1.2 volts. With a 12 percent duty cycle, the average power dissipated in Q03 is about 2 watts. In free air (i.e., natural convection) at room temperature of  $80^{\circ}$ F, this dissipation causes Q03 to attain  $175^{\circ}$ F case temperature. With this high temperature on the card, it is suggested that the card be located in moving air and away from any temperature sensitive circuits.

.

This output driver is used to operate on a common line with other equipment having similar output drivers attached to the same common line. The driver meets the common line requirement that it disconnect itself from signals on the common line whether power is on or off. This power off requirement is satisfied only if a positive voltage of 5 volts or more remains on pin 15. For these particular circuits the internal machine plus 20v is "ORed" with a plus 15v bus from the controller.

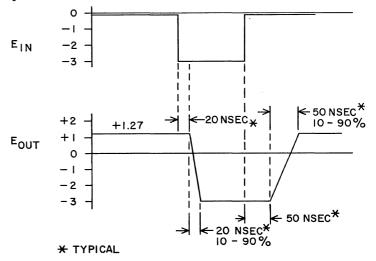

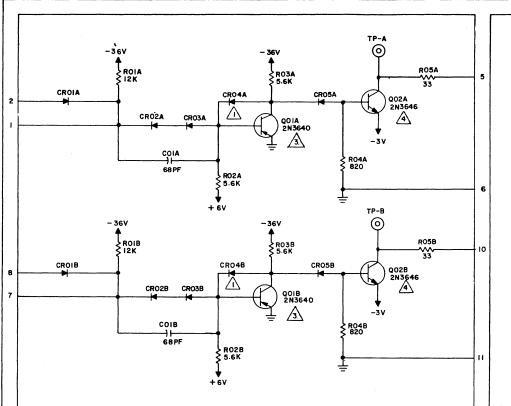

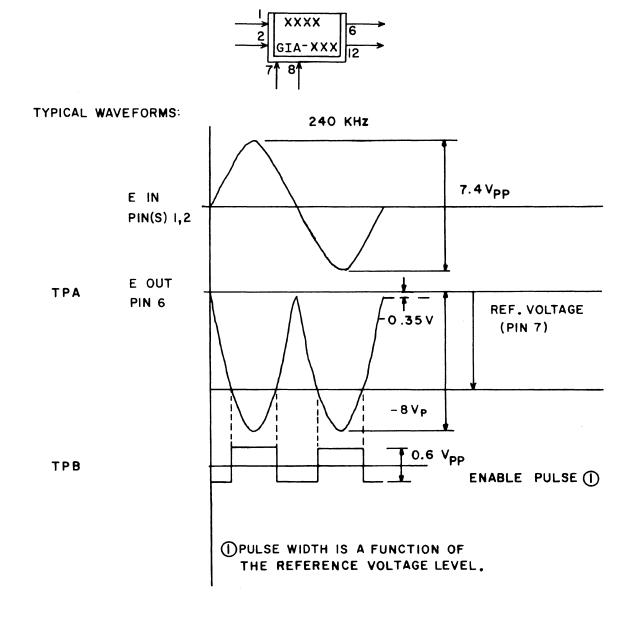

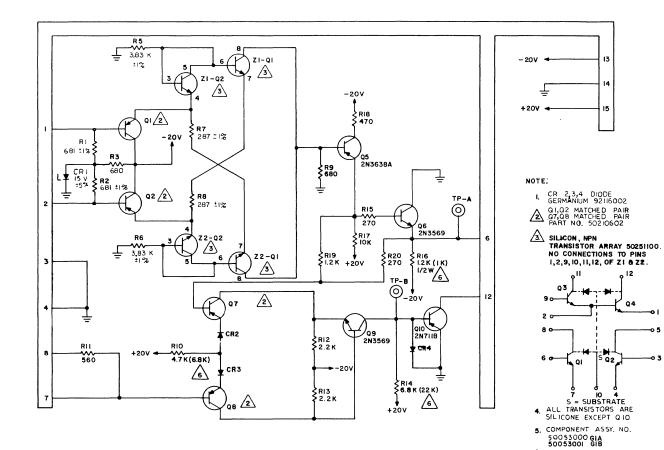

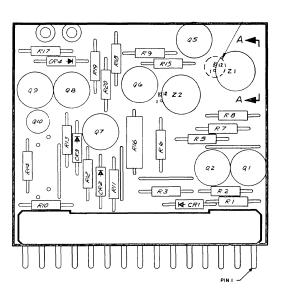

The circuit is designed around the type and length of interconnecting cable (100 ft. max) to provide optimum rise (0.35 to 1.0 use) and fall time (0.30 to 0.65 usec).

The circuit is a switching type inverter with certain variations. RO1 reflects twice the usual load to the previous circuit. CRO1 and CRO2 are forward biased silicon diodes to improve the efficiency of the base divider of QO1. Capacitors CO1 and CO2 provide the proper combination of feedback to achieve the desired rise and fall times. Diode CRO3 is connected to a minus 8-volt clamp to obtain the desired negative excursion of 8 volts. Diode CRO4 prevents loading of this circuit in a negative direction when another signal is on the common line. Diode CRO5 prevents loading of this circuit in a positive direction when another signal is on the common line.

A total of 85 ma output current is available for the receiver load, for charging the line capacity, and for driving small shunt leakages in parallel drivers on the same common line.

SYMBOL

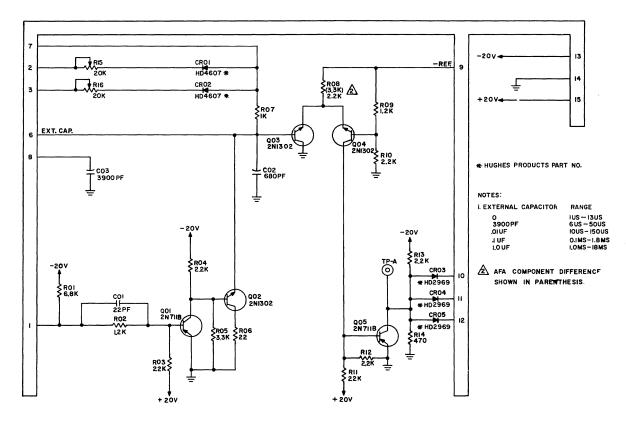

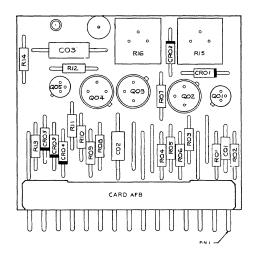

## MULTIPLE TIME DELAY AFA, AFB

The multiple time delay card is used to delay the positive transition of an input (logic level) signal an amount of time determined by the RC time constant in the circuit. The resistance portion of the time constant includes a linear variable resistor which can be preset to give a particular delay time. More than one preset variable may be used to control the delay time of the circuit, but only one should be connected at a time. An electronic switch can be used to switch the proper resistor into the circuit (enable amplifier, type AG-series).

The delay circuit is armed by having a "1" input on pin 1 for 0.5 usec or more for a total delay capacitance of 5000 pf. The delay time accuracy is within <sup>+</sup>2 percent over a temperature range of 0° to 50°C. For 5000 pf delay capacitance, the delay from an input "1" to an output "1" does not exceed 0.1 usec.

A signal on the input (pin 1) switching from a logical "1" to a "0" causes Q01 to turn off. Its collector goes to about -12v allowing emitter follower Q02 to cease conducting. Capacitor C02 (and the external capacitor if connected) starts charging through resistor R07, diode CR01, and variable resistor R15 to a negative reference voltage (pin 2). A small amount of charging current flows through transistor Q03. At the predetermined delay time, the voltage at capacitor C02 reaches the same voltage (-10v) that appears at the junction of resistors R09 and R10. The voltage supplied to resistor R09 is from the same negative reference as that supplied to R15. The differential amplifier, Q03 and Q04, switches state so that Q03 is now nonconducting and Q04 is conducting. This causes the base of transistor Q05 to go negative and start conducting, thus switching the output from "1" to "O"。 Similar operation is achieved using variable resistor R16 (pin 3) in the charging circuit and grounding R15 (pin 2). The diode connected to the grounded resistor serves to isolate the resistance from the timing circuit being used during the delay period.

Recovery of the circuit is accomplished by returning the input to a "1". Transistor Q01 turns on, thus grounding (-0.2v) the base of Q02. The emitter of Q02 follows, discharging capacitor C02 (and ex-

ternal capacitor) through Q02 and resistor R06. Resistor R06 limits the current thus protecting transistor Q02 from burnout. Differential amplifier, Q03 and Q04, returns to its original state with Q03 on and Q04 off. Resistor R11 reverses the base current to transistor Q05 allowing the output to return to a "1".

6-AFA, AFB-2

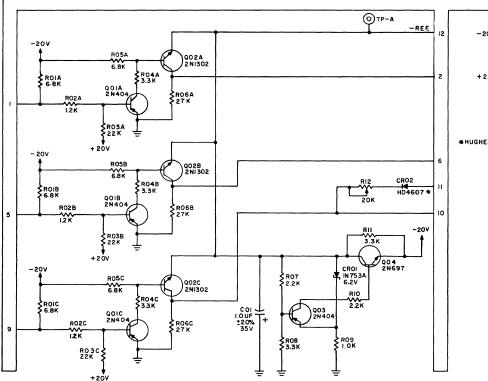

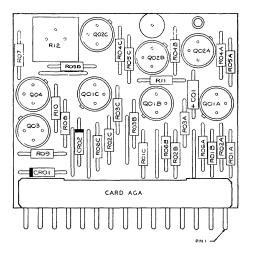

## ENABLE AMPLIFIER AGA

The enable amplifier card is used to select the proper variable resistor and provide a reference voltage for the time delay circuit (AFseries). There are three switching circuits per card.

A logical "O" applied to the input pin (three identical circuits) causes transistor Q01 to turn off, allowing its collector voltage (through R04 and R05) to go more negative than the reference voltage at the emitter of Q02. Thus, Q02 is turned off allowing its collector voltage (output) to be at ground potential.

A logical "1" applied to the input pin causes transistor Q01 to turn on, grounding its collector (-0.2v) and turning on Q02 by providing base current through R04. The collector (output) of Q02 then goes to the reference voltage (about -15v). Thus, an external circuit element may be switched to the reference voltage when a "1" is applied to the enable amplifier and returned to ground when a "0" is applied.

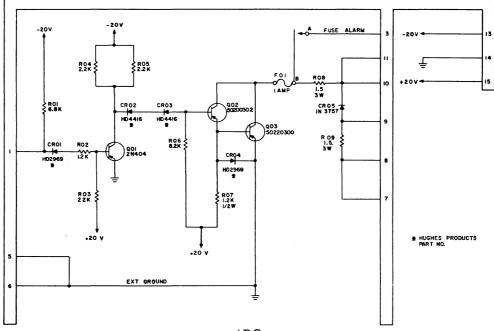

The reference voltage section supplies a regulated and filtered current at -15v. This voltage is supplied to both the variable resistor and the differential amplifier on the time delay card (AF-series). The voltage is regulated in the following manner. Resistor Rll supplies starting current to the bridge composed of R07, R08, R09, and CR01. Transistor Q03 senses any voltage difference between the two legs of the bridge and changes the current to the base of transistor Q04 in proportion to the error in voltage. This allows Q04 to supply more or less current to the bridge and load such that the voltage returns to the normal value. Voltage regulation is in the order of  $\pm 2\%$  for load current up to 100 ma (instantaneous).

+HUGHES PRODUCTS PART NO.

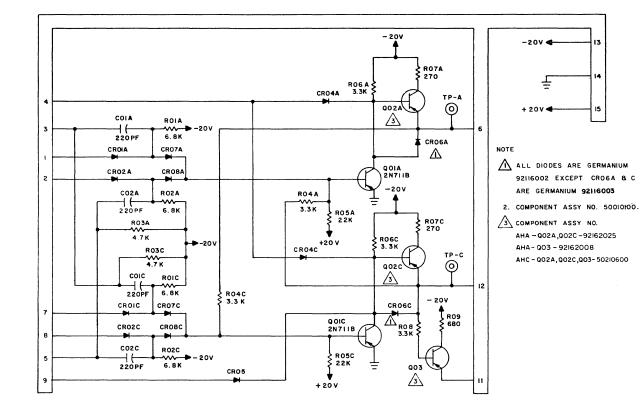

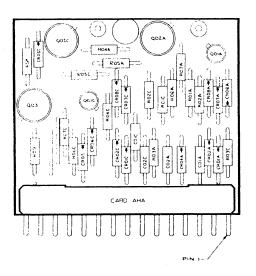

# FLIP-FLOP DRIVER AHA,AHC

These flip-flop drivers are a special circuit designed for economical shift registers used in large quantities in optical character reading equipment. Capacitor coupled inputs allow a single rank of flip-flops to be used in a shift register with shifting possible in both directions. An output excursion of -3/4v to -12v with 20 ma drive provided in both directions eliminates the need for an external buffer driver to operate a resistor matrix load. A 10v, 15 ma lamp in an external display may also be operated from a lamp driver output. The circuit also lends itself to operation as a toggle flip-flop.

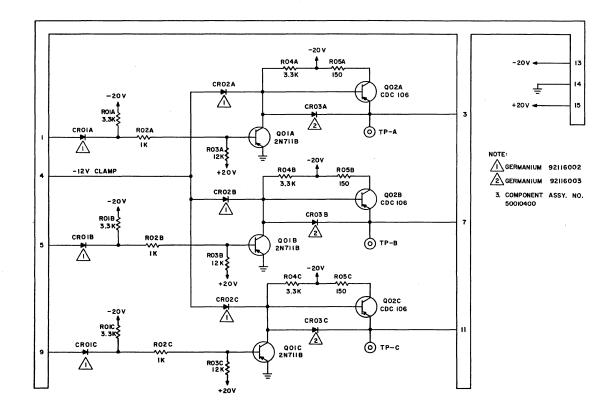

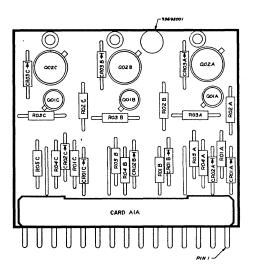

Flip-flop operation is as follows. The bistable circuit is composed of transistors Q01A, C and Q02A, C. Q01A, C provide drive in the positive direction. Q02A, C provide drive in the negative direction. R04A, C provide direct coupling between the two basic inverters to maintain either of two stable states. Q03 acts as an emitter follower to operate a low wattage lamp such as the #344 (10v, 15 ma). The positive excursion of the output is determined by the saturation resistance of Q01A, C and CR06A, C. The negative excursion is determined by the voltage on pin 4 which limits the negative-going excursions at the base of Q02A, C. When the output is negative, the output current is limited by R07A, C in the collector of Q02A, C are turned on.

Triggering of the flip-flop is as follows. Assume Q01C is conducting (Q02A conducting and Q02C and Q01A nonconducting). If pin 7 is driven within -1/4 to -1v of ground, then a positive-going excursion of about 10v on pin 3 would cause a positive pulse to be coupled through C01C and CR07C to the base of Q01C. This positive signal would overcome the negative voltage supplied by R04C and cause Q01C to turn off. In about 0.1 usec after Q01C turns off, Q01A will be turned on and have changed the flip-flop to its other stable state. Q01C could also have been turned off in a similar manner by having pin 8 near ground and applying a positive-going excursion to pin 5 through C02C and CR08C. When Q01A is on, it may be turned off to change the flip-flop state by a similar combination of signals on pins 1 and 3 or pins 2 and 5. Input signals on pins 1, 2, 7, and 8 should be equivalent in excursion to the output of pins 6 and 12 of the card.

<u>\_\_\_\_</u>

C

Thus, a positive-going pulse on pin 3 makes the flip-flop assume a state dependent on the levels present on pins 1 and 7 (assuming they are complimentary). Similiarly, a positive-going pulse on pin 5 makes the flip-flop assume a state dependent on the levels present on pins 2 and 8. By interconnecting the cards logically, they can be wired to shift up or down in a shift register by using one of two shift pulse lines from circuits such as the AIA which can interface with standard logic.

For clearing a counter or shift register, a clear line on pin 9 may be used. This operates from a signal from 0 to -1v and large numbers of AHA's may be cleared by one high current driver. Each card may require 7-25 ma (depends on load) to clear when in the set condition (lamp driver on) or 3 ma when in the clear position. The clear line should be biased between -12v and -20v when a clear is not desired.

While the circuit is specifically designed for an excursion of -1/2v to -12v, clamping pin 4 to a different voltage will change the negative excursion proportionally. Lower voltages significantly reduce output drive in the positive direction and more negative voltages reduce it in the negative direction. The lamp driver circuit of Q03 is also significantly affected by such a change.

Shift pulses should have positive-going rise times of 0.150 usec or less with an excursion of 10 to 12 volts. Larger excursions with rise times this fast can cause faulty operation as can low amplitude slow rise time pulses.

AHA, AHC

6-AHA, AHC-3

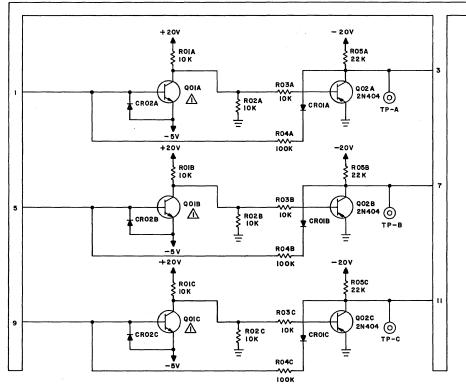

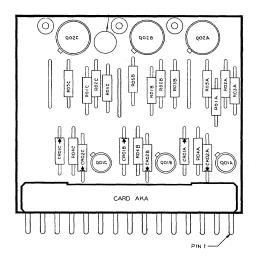

# SHIFT DRIVER AIA, AIB

The shift driver is designed to supply shift pulses and input signals for the AHA and similar circuit requirements. It provides output drive in both the positive and negative direction similar to a 3600 inverter. The output excursion is determined by the clamp voltage on pin 4 which is designed for -12v. Its input may operate from either standard 1604 logic levels or from logic levels that have greater negative excursions. However, if the negative excursion of the input is less than -5.0v, the output drive in the positive direction is reduced from a normal 70 ma to 25 ma at normal 1604 logic inputs. For positive input excursions ranging from 0 to -3/4v, the output drive in the negative direction is 45 ma maximum using a -12v clamp on pin 4. Output drive in the negative direction also reduces proportionably as the difference between -20v and the clamp voltage is reduced. Conversely, it increases if a lower clamp voltage is used. The negative voltage excursion for various loads is within 0.5v of the negative clamp voltage on pin 4. The positive excursion ranges from -0.5v at light load to a maximum of -1.0v at full load.

# PHOTOCELL AMPLIFIER AKA

The AKA Photocell Amplifier is designed for use on the 350 and 370 Paper Tape Readers to digitize photo diode or photo transistor signals.

The output of the amplifier is normally terminated by the input of a standard "M" card, such as the 87. In the dark condition, external bias potentiometers supply current from a negative source to the input diode keeping both stages turned off, resulting in an output of -16v dc. In the illuminated state, the photocell provides positive current to the input base over-riding the bias current to turn on both stages. This results in an output of 0 to -1v dc.

The circuit consists of two direct coupled inverting stages and a feedback circuit. The positive feedback through CRO1 and RO7 from output to input provides hysteresis or "snap action" to the turn-on and turn-off process. This insures the absence of Class A signals on the output during those times when the photocell is left in a partially illuminated state. Diode CRO7 is intended to prevent a reverse feedback current from flowing when the photo diode is dark. Internal leakage in CRO7 does allow a slight amount of positive feedback when connected to a "M" card, but this would be reduced even further if terminated by a standard inverter.

SYMBOL

A SILICON 50210102

2. ALL DIODES ARE GERMANIUM 92116002 3. COMPONENT ASSY NO. 50011000.

AKA

Rev. R

6-AKA-2

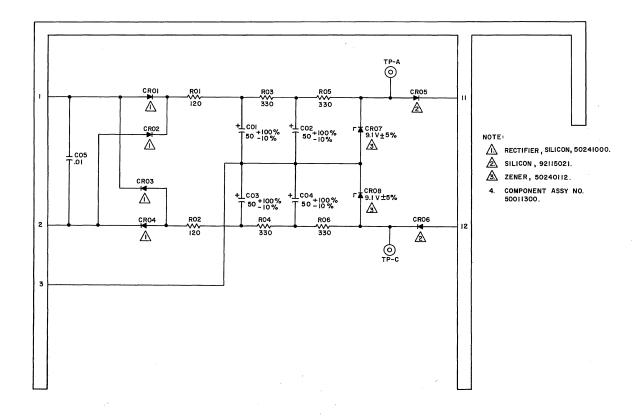

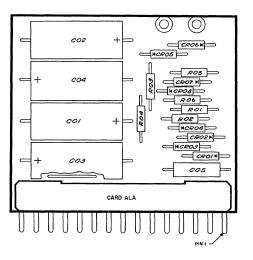

# POWER SUPPLY ALA

The ALA card contains a floating power supply. It is used with the FOA and FOB function generator cards in the disk file servo actuator.

The circuit is supplied by an externally mounted 40v rms 60 cycle center tapped transformer. The transformer is connected to pins 1, 2, and 3. Pin 3 is the center tap and circuit common.

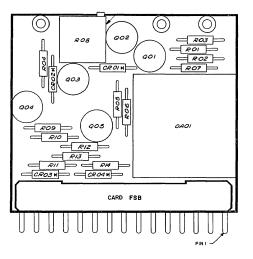

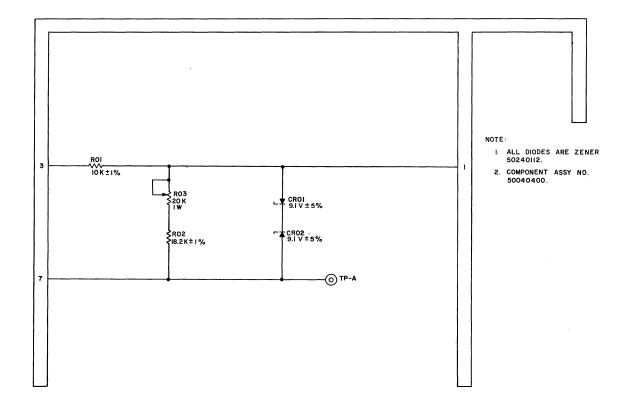

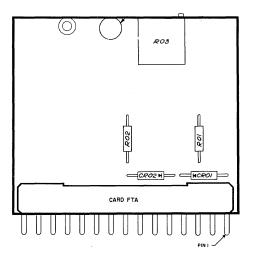

The circuit consists of two full wave rectifier circuits connected for plus and minus voltage, and the filter networks as shown on the schematic. Zener diodes CR07 and CR08 regulate the output voltages to 9.lv nominally. The maximum load is approximately 18 ma. NOTE: This card requires two card slots.

SYMBOL

XXXX H

6-ALA-2

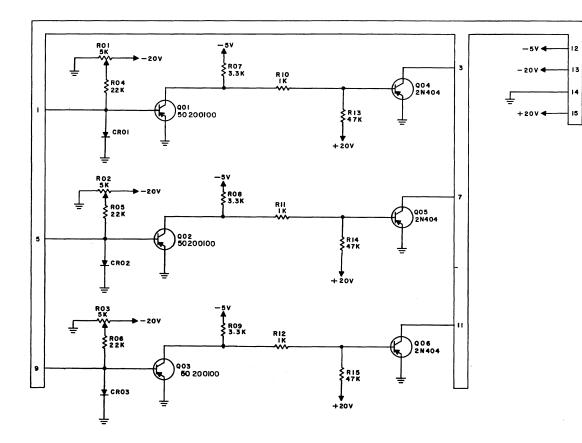

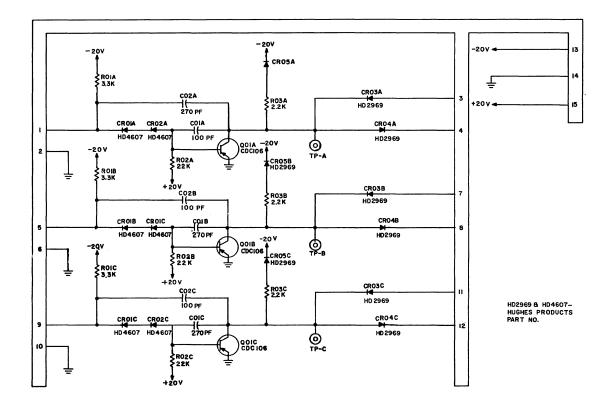

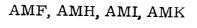

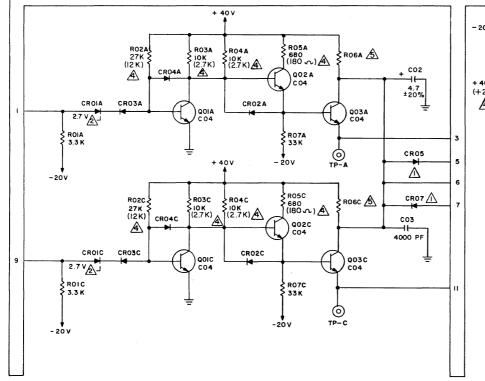

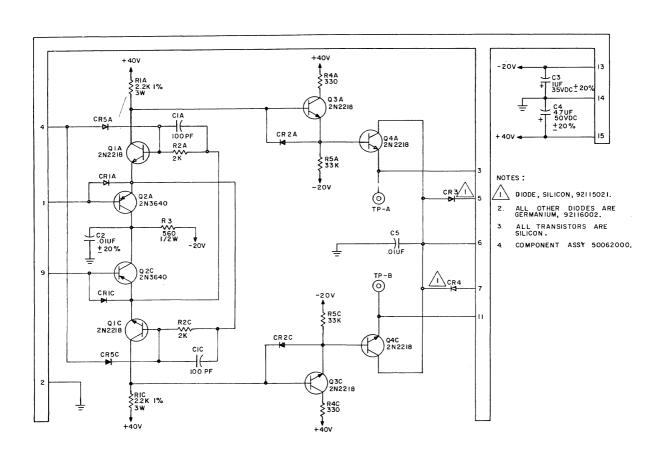

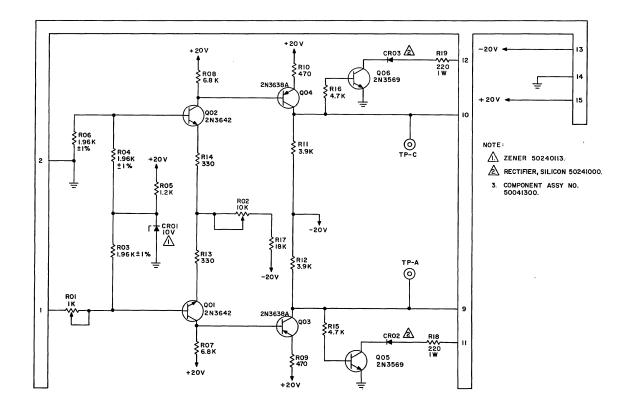

### WRITE/ERASE DRIVERS

## AMF THRU AMQ

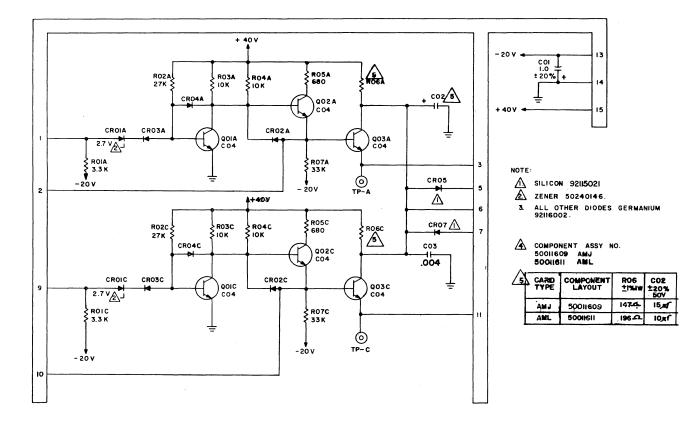

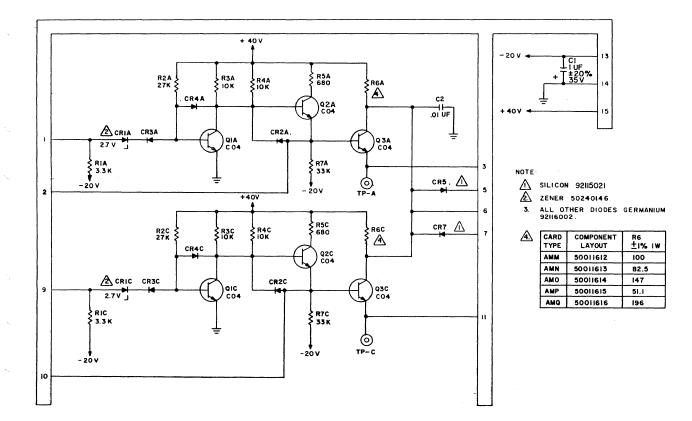

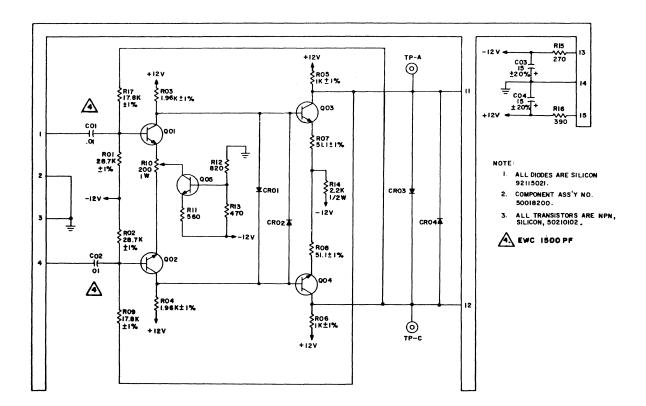

The AM-- series cards are used as high speed current switches to control the current to the write or erase heads. The magnitude of the current is determined by the collector resistors of Q03A and Q03C and the emitter resistors external to the card. Except for the variation in collector- and emitter-resistor values according to the current requirements of a particular head, all AM-- series cards are similar. These cards are intended to be driven by toggle flip-flops such as the EVB or the UKB.

| CARD     | TYPICAL CURRENT<br>AT EACH OUTPUT |

|----------|-----------------------------------|

| AMF      | 100 ma                            |

| AMG, AMM | 125 ma                            |

| AMH, AMN | 125 ma                            |

| AMI      | 300 ma                            |

| AMJ, AMO | 85 ma                             |

| AMK, AMP | 100 ma                            |

| AML, AMQ | 60 ma                             |

When transistor Q01 is on, it holds transistors Q02 and Q03 off. Zener diode CR01 is used for level translation. Diode CR03 keeps noise at the input from coupling through the capacitance of CR01 to the base of Q01. Diode CR04 is an anti-saturation diode. Resistor R06 develops a voltage drop proportional to the drive current which is used to check for proper operation (see cards ANB, ANC, AND, and AOA). Diodes CR05 and CR07 are part of the checking circuitry. Diode CR02 allows Q01 to provide turn-off current directly to Q03.

Except for the AMG, AMJ (15 uf), the AML (10 uf), and the AMM thru AMQ (.01 uf), the value of capacitor C02 is 4.7 uf. This provides a longer time constant to ensure correct operation of the error checking circuits in the Disk Storage Drives.

The AMI card is designed to operate at +20v rather than +40v in order to reduce power dissipation. This was necessary because both circuits on the card are on at the same time.

With "1" (-3v) at the input, transistors Q02 and Q03 permit the current to flow from +40v (+20v, AMI card) toward ground. With "0" (ground) in, the output is open. The magnitude of the current is determined by an external resistor in series with the load.

#### CAUTION

These cards should not be removed from the chassis while +40v is applied.

6-AMF THRU AMQ-1

| 20 V 🛶      | COI<br>1.0<br>± 20% | +             | 13    |                   |          |

|-------------|---------------------|---------------|-------|-------------------|----------|

| 40V         | ÷                   |               | 15    |                   |          |

| 4           |                     |               |       |                   |          |

| ΝΟΤΕ        |                     |               |       |                   |          |

| $\triangle$ | SILICON             | 921150        | 21.   |                   |          |

| Ł           | ZENER               | 502401        | 46.   |                   |          |

| 3.          | ALL 01<br>9211600   |               | ÓDES  | GERMAN            | UM       |

| A           | VALUES              |               | ENTHE | SIS ARE           | USED     |

| ◬           | CARD<br>TYPE        | COMPO<br>LAYO |       | R06 A,            | С        |

|             | AMF                 | 500116        | 605   | 19617=1% IV       | ~        |

|             | АМН                 | 500116        | 07    | 82.5 <u>n</u> ±1% | w        |

|             | AMI                 | 500116        | 808   | 16.2A±1%11        | <u></u>  |

|             | АМК                 | 50011         | 510   | 51.In±1%14        | <u> </u> |

|             |                     |               |       |                   |          |

AMG

6-AMF THRU AMQ-3

## AMJ, AML

## 6-AMF THRU AMQ-4

AMM, AMN, AMO, AMP, AMQ

6-AMF THRU AMQ-5

### HEAD SELECT AND WRITE ERROR CHECKER

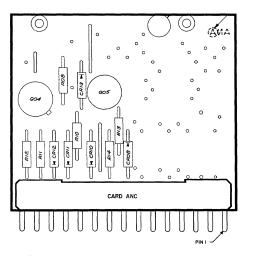

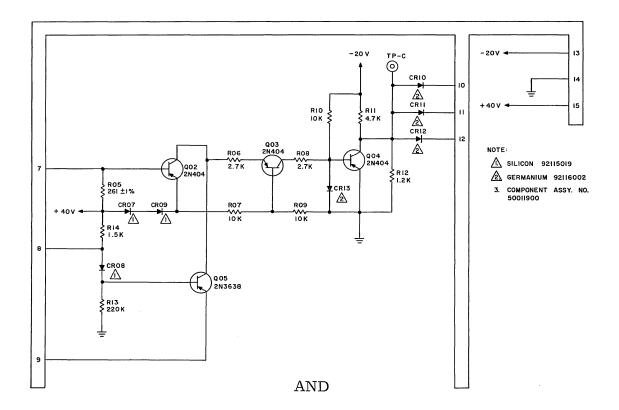

AND

This card is used in conjunction with write driver cards AMF and AMG, and head selector card IOB to check for proper operation.

(A) R05, CR07, CR09, and Q02 are used to determine if more than one head select circuit is on. Pins 5 and 11 of all the IOB cards are tied to pin 7. Each transistor Q03 on the IOB cards which is turned on (in saturation), draws approximately 4 ma through R05. When the voltage drop across R05 is greater than 1.6v ( $\pm$ 0.15v), which is the sum of the voltage drops across CR07 and CR09 in series plus V<sub>be</sub> of Q02, transistor Q02 will turn on. This will turn off transistor Q04. When Q04 goes off, an error has been detected. Resistor R05 is used so if one IOB card is on, Q02 will stay off. However, if two IOB cards are on, Q02 will turn on.

(B) R13, R14, CR08, and Q05 are used to determine if the current flowing out of each of a group of drivers is approximately the same. This will assure that none of them have shorts or opens. Pin 7 on both AMF or AMG cards are tied to pin 8. Pin 5 on both AMF or AMG cards are tied to pin 9. Since R06A and R06C are in parallel on the AMF or AMG card, the voltage across them is a function of the total current flowing through Q03A and Q03C. Capacitor C02 integrates this voltage. Therefore, it doesn't fluctuate with individual write cycles.

Assume that Q03A on driver number 1 becomes shorted. The current will then flow through Q03A all of the time, as well as part of the time through Q03C as dictated by input logic. The voltage at pin 6 of driver number 1 will then be more negative than the voltage at pin 6 of driver number 2. This will pull the voltage at pin 8 of the AND card more negative through CR07 on driver number 1. The voltage at the base of Q05 on card AND will stay one diode drop more negative than at pin 8. If the base of Q05 gets approximately 1.5v negative, with respect to pin 6 of driver number 2, Q05 will be turned on via CR05 on driver number 2. When Q05 turns on, Q04 turns off and an error is indicated. However, if the voltage at the collector of Q03 on driver number 1 is close enough to the voltage at collector Q03 on driver number 2, Q05 will not turn on. If these voltages are called  $V_1$  and  $V_2$ , Q05 will turn on if the absolute

Rev. P

value of  $V_1$  minus  $V_2$  is greater than 1.77 volts. Transistor Q05 will not turn on if the absolute value of  $V_1$  minus  $V_2$  is less than 1.27 volts.

# HEAD SELECT AND WRITE ERROR CHECKER

ANB

The (B) portion of the AND card description applies to card ANB. The circuits containing QO1 and CR14 are used in conjunction with card AOA to test head selects. If more than approximately 0.8 ma flows from a combination of AOA cards into pin 1, QO1 will turn off indicating an error. R15 and CR14 act as a reference voltage supply for the AOA cards.

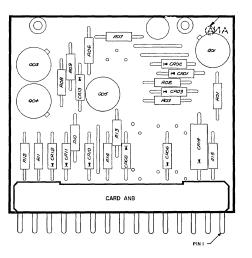

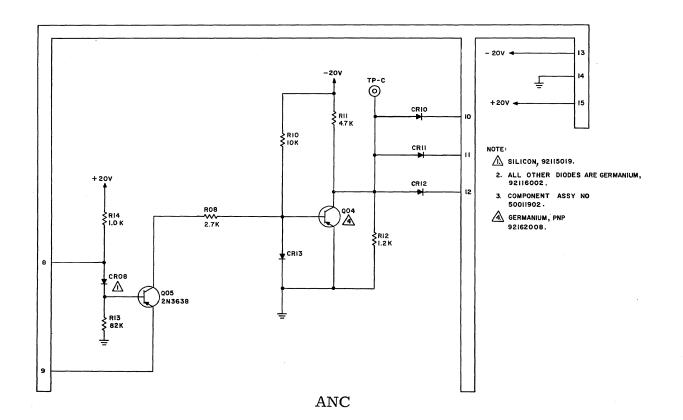

## ERASE ERROR CHECKER ANC

The ANC card is essentially the same as the (B) portion of the AND card description. The ANC card has been modified to test drivers that operate on +20v (AMI card) rather than +40v.

The outputs of cards ANB, ANC, and AND go to logical "1" (-3v) if an error has been detected. If the outputs are at logical "0" (ground), no error has been detected.

Rev. P

ANB

6-ANB, ANC, AND-3

Rev. P

6-ANB, ANC, AND-4

6-ANB, ANC, AND-5

Rev. P

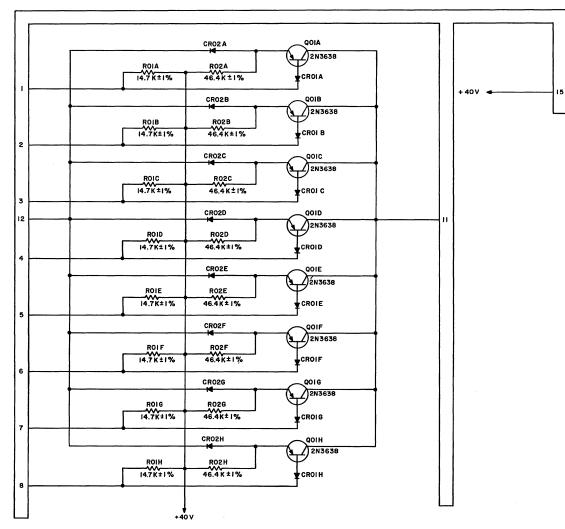

## EXCLUSIVE OR CIRCUIT AOA

The AOA card delivers +0.4 ma to an ANB card for each head select circuit (turned on) it is monitoring.

Pins 5 and 11 on the IOB cards are tied to pins 1 through 8, with only one Head Select circuit at each input pin. A total of eight Head Select circuits are tested by each AOA card, in conjunction with an ANB card. If the Head Select circuit tied to pin 1 is turned on, QOIA will be turned on, and it will allow approximately 0.4 ma to flow out pin 11 to the ANB card. The voltage at pin 1 is compared to the voltage at pin 12. If the Head Select circuit tied to any other pin of pins 1 through 8 is on, the associated transistor on the AOA card will also turn on, in the same manner at QOIA. This transistor will also allow approximately 0.4 ma to flow out pin 11 to the ANB card.

Four AOA cards are used in conjunction with one ANB card. Pin 11 on the AOA card goes to pin 1 on the ANB card; pin 12 on the AOA card goes to pin 3 on the ANB card. Thus, 32 Head Select circuits are being checked by one ANB circuit. If more than one QO1 on the four AOA cards is on, there will be 0.8 ma (or more) entering the ANB card at pin 1.

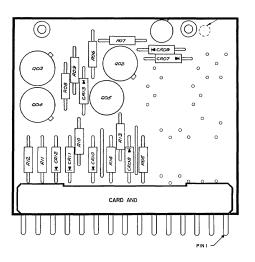

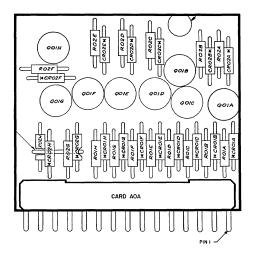

6-A0A-1

AOA

6-A0A-2

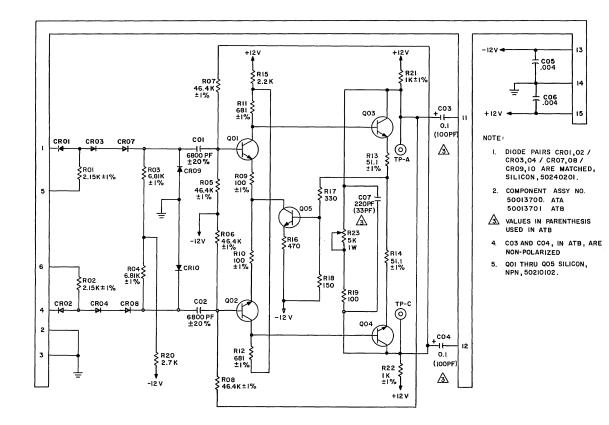

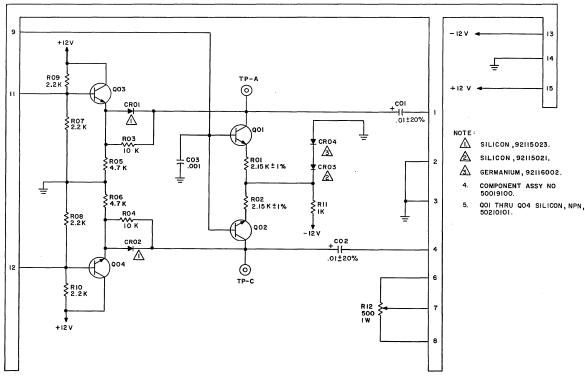

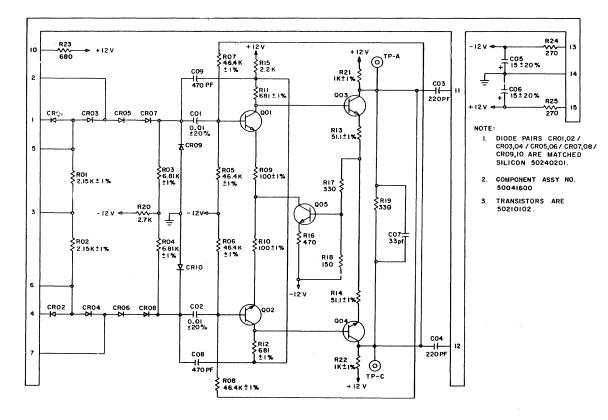

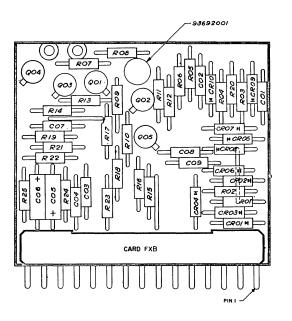

# GATED AMPLIFIER ATA, ATB

This circuit has a read gate and a linear preamplifier. The read gate is comprised of diodes CR01-CR10, and resistors R01-R04 and R20. Pins 1 and 4 go through an external diode on each side, pointing the same way as CR01-02 and then to the outer terminals of the read head. CR05 and CR06 are replaced by jumpers for use with disc paks.

If pins 5 and 6 are at +5V or more positive, the circuit amplifies a signal put in on pins 1 and 4 from a center-tapped, grounded read head. If pins 5 and 6 are near ground, signals at pins 1 and 4 are ignored.

Pins 5 and 6 are connected through a balancing potentiometer to an ISC card, which is used as the gate control. When the ISC input is at ground, the emitter follower output of the ISC is off, which is equivalent to having pins 5 and 6 floating. Under these conditions, whether the center-tap of the head is at +40v (unselected) or at ground (selected), diodes CR01-CR08 are not conducting, and thus represent a large impedance between the read head and the amplifier. Also, CR09 and CR10 are conducting through R03, R04, and R20, and represent a short circuit across the input to the amplifier for any signal that might leak through the other diodes. While writing is in progress, the outside terminals of the head will experience  $\pm 20v$  excursions due to L  $\frac{di}{dt}$ . The gate portion of the circuit attenuates these voltages, so that resulting disturbances in the read chain are minimized.

When the ISC turns on, current flows through CR01, CR02, and the two external diodes through the read head to ground via the Head Select. Current also flows through CR03-08 to R03, R04, and R20. Thus CR01-CR08 are foward biased and present a low dynamic impedance to the signal. When CR03-08 are on, CR09 and CR10 are turned off, and thus do not put a short circuit across the input to the amplifier.

The amplifier is a two stage differential amplifier, with some dc feedback from output to input for stabilization through R07 and R08. C07 controls the high-frequency gain, and R23 controls the overall gain. +12v must be supplied at pin 15, and -12v must be supplied at pin 13. Bandpass is from 10Kc to 5Mc. This card is designed to drive EUA, EUC, or a similar load of about 1K.

The ATB card is the same as the ATA, except that some component values are changed since the desired gain vs. frequency characteristics are different. Band pass is from 50 Kc to 5Mc.

SYMBOL

ATA

6-ATA, ATB-3

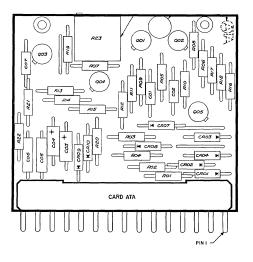

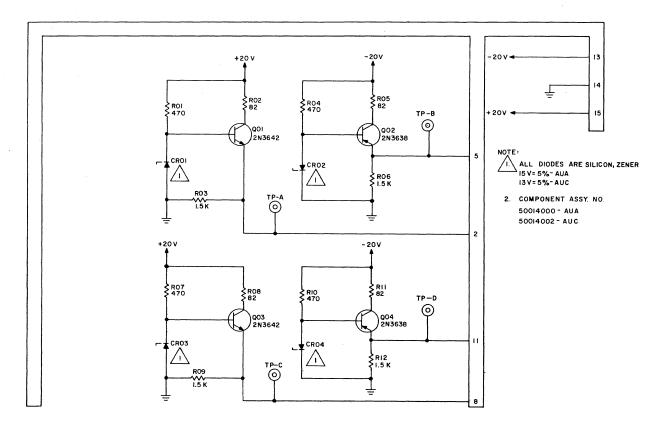

## POWER SUPPLY REGULATORS AUA

This card provides a regulated  $\pm 15v$  to an operational amplifier (such as the FSA used in the servo actuator for the disk file). There are two identical  $\pm 15v$  stages and two identical -15v stages on the card.

Each circuit is an emitter follower with a 15v zener diode from base to ground. The maximum load current possible before the zener comes out of conduction, assuming a 10% low power supply voltage, is 33 ma. This corresponds to an equivalent load resistance of 455 ohms.

The output impedance is approximately the  $r_e$  of the transistor in the Tee parameters. This is also equal to  $26/I_e$ . For these circuits,  $I_e$  is approximately 10 ma, resulting in an output impedance of 2.6 ohms.

### AUC

The AUC provides a regulated  $\pm 12v$  to the timing arm read preamplifiers. There are two identical  $\pm 12v$  stages and two identical -12v stages on the card.

Each circuit is an emitter follower with a 13v zener diode from base to ground. The base-emitter diode drop produces an output voltage of approximately 12.3 volts. The maximum load current that is available before the zener comes out of conduction, assuming a 10% low power supply voltage, is 35 ma. This corresponds to an equivalent load resistance of 345 ohms.

### 6-AUA, AUC-1

AUA, AUC

# 6-AUA, AUC-2

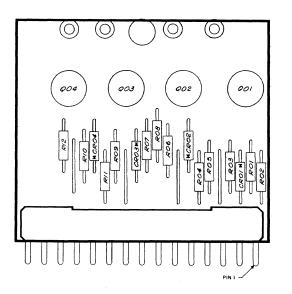

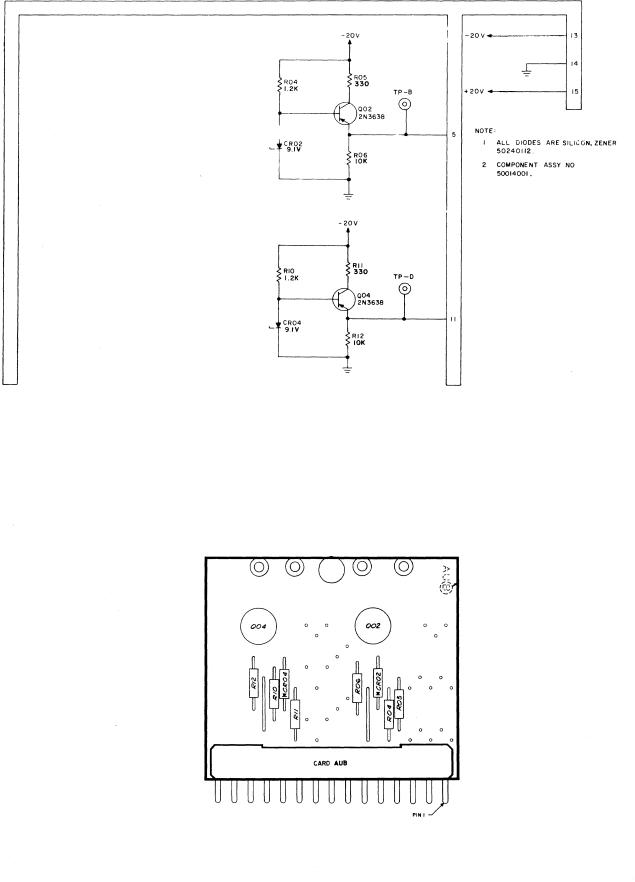

# POWER AND CLAMP VOLTAGE SUPPLY AUB

The AUB has two identical regulating circuits providing clamp voltages of -8. 4v to the AIB. The circuit basically consists of an emitter follower with a PNP transistor and a 9. 1v zener diode. The anode of the zener diode is connected to the base of the transistor and the cathode is tied to ground. The zener diode is held in conduction by current flow through resistor R4 (R10) to the -20v supply. Assuming 10% low power supply voltage, a maximum load current of 25 ma is possible without causing the zener diode to stop conducting. This corresponds to an equivalent load resistance of approximately 330 ohms. Collector resistors are used to provide the transistor with some protection against short circuits on the output.

C J

Rev T

6-AUB-2

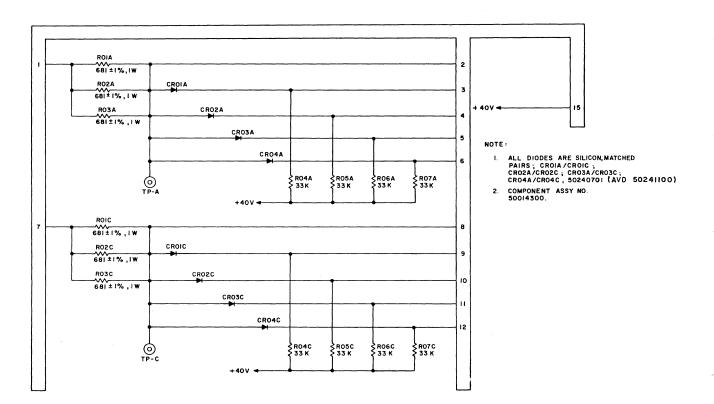

# WRITE RESISTOR/DIODE CARDS AVA, AVB, AVC, AVD

These cards connect between the erase/write drivers and the read/write heads. The read amplifier connects to the head via this card. There are two identical sections per card.

### AVA, AVD

On these, each section of the card contains one input connected to a single resistor or a resistor/diode combination.

The resistor determines the magnitude of the erase/write connect; the diode(s) provide isolation.

### AVB

This card is similar to the AVA; however, only the R01, R02, and R03 resistors are present. The isolation diodes and resistors R04 - R07 are not used on the AVB card.

### AVC

This card is similar to the AVA; however, only the resistors are present on this card. There are no diodes on the AVC card.

SYMBOL 7 AVA-XXX 5 6

AVA, AVD

6-AVA, AVB, AVC, AVD-2

$\mathbf{Rev} \ \mathbf{S}$

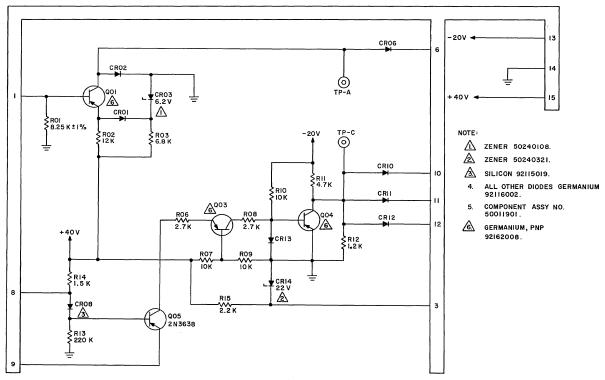

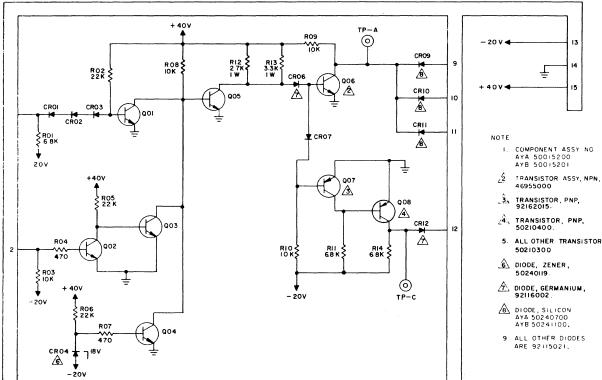

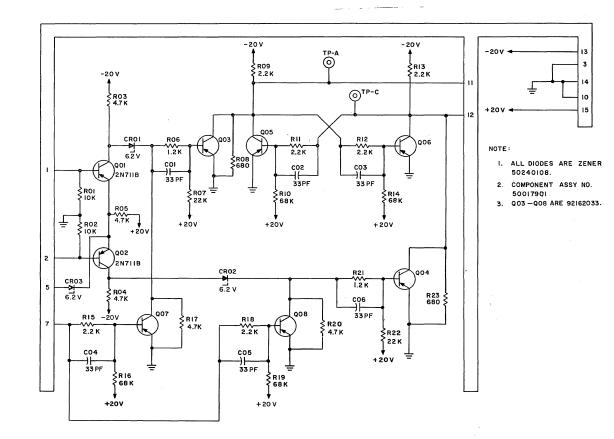

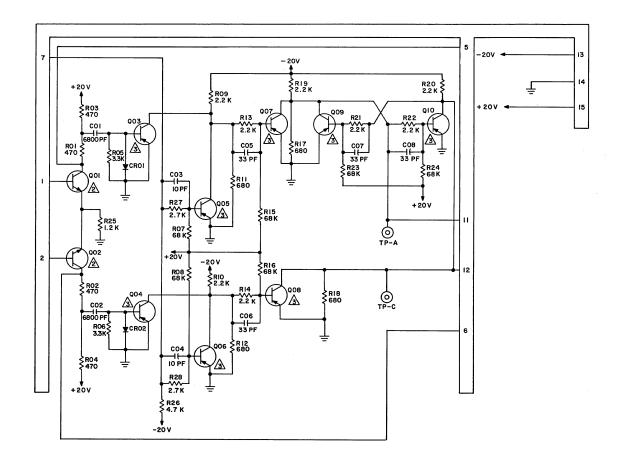

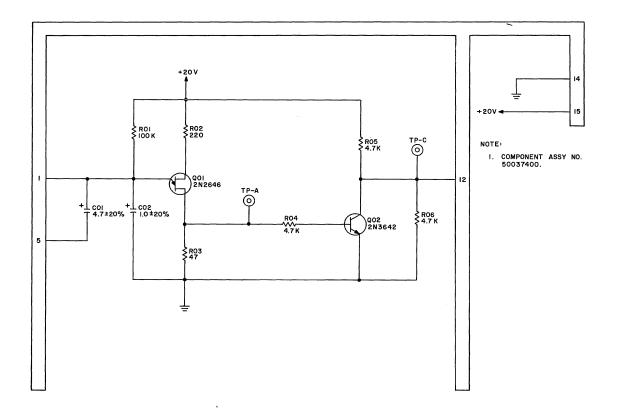

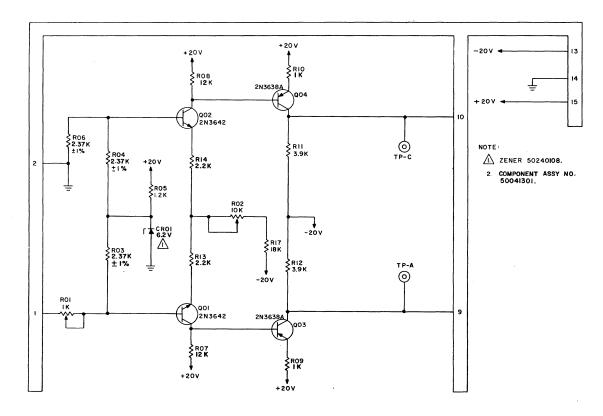

# VOLTAGE CHECKER AYA, AYB

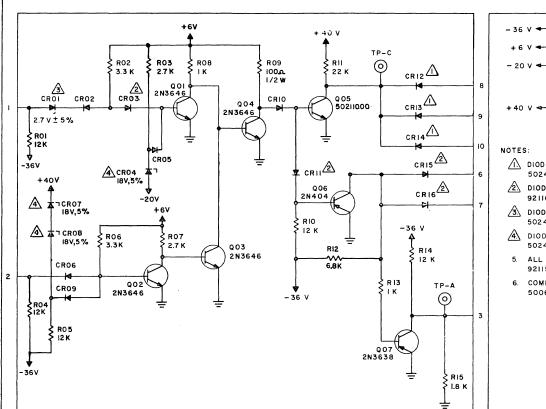

These cards keep and erase current from reaching write and erase heads if one or more of the following conditions is true: 1) If +20V drops below +17.6V nominal. 2) If -20V gets closer to ground than -17.2V nominal. 3) If an external logic signal goes to logic zero (-0.5V). A logic output goes to logic zero.

If pin 1 goes to logic zero, QO1 turns on. This turns off QO5, which turns QO6 on, and forces TP C toward -20V. QO6 absorbs up to 500 ma. CR09, 10, 11 are to isolate the AYA card and the write and erase heads from each other when the AYA card is off.

Pin 2 senses the state of the +20V supply. If it gets to +17.6  $\pm$  0.9V, Q02 turns off and Q03 turns on. This has the same effect as Q01 turning on. Q04 turns on if -20V supply gets to -17.2V  $\pm$  0.9V. This has the same effect as Q01 turning on. If more than one of these three sensing circuits respond at one time, the effect is the same as if only one was on.

XXXX SYMBOL AYA-XXX

ΑΫΑ, ΑΥΒ

6- AYA, AYB-2

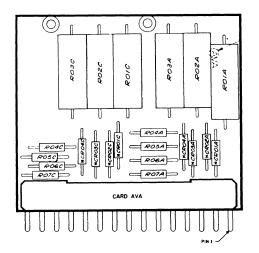

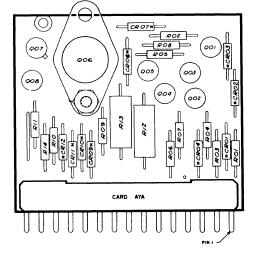

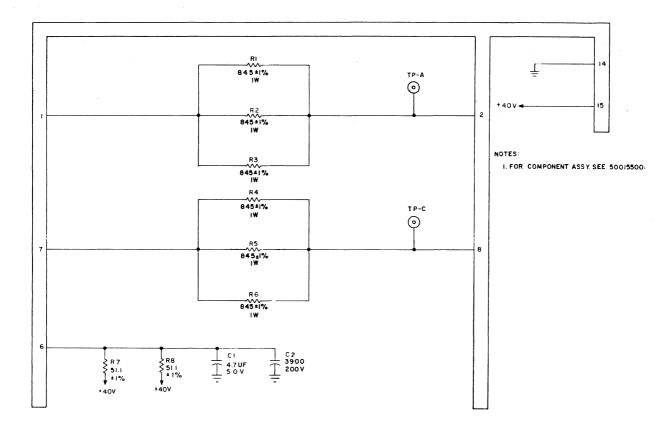

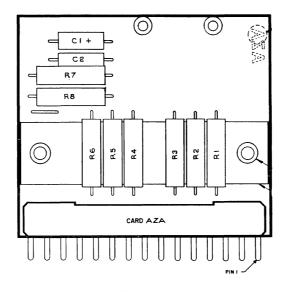

# WRITE RESISTOR AZA

This card (follows the BMA write driver in the write chain) controls the amplitude of the write current in the disk file R/W head. It also supplies +40v power to the output stage of the write driver. This current is supplied through two parallel resistors to produce a voltage drop proportional to the write current which is used in error checking. The power output from AZA to the write driver is filtered by two capacitors in parallel, C1 and C2.

Rev T

6-AZA-2

## VOLTAGE CHECKER

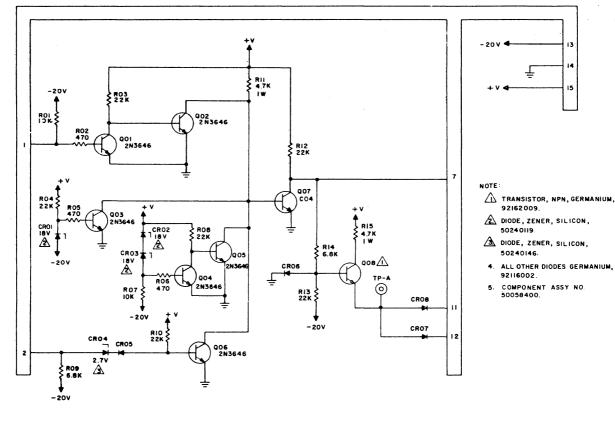

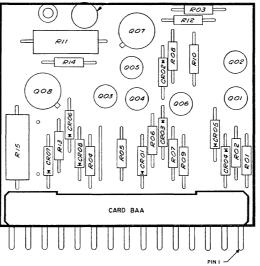

## BAA, BAB, BBA, BCA, BCB

These cards keep write current and erase current from reaching write heads and erase heads, if one or more of the following conditions are true: 1) +40v drops below +35.0v nominal. 2) +20v drops below +17.6V nominal. 3) -20v gets closer to ground than -17.2v nominal. 4) An external logic signal goes to zero (-0.5v). Logic outputs go to logic zero.

The BAA card has an input on pin 1 from the GAA card, indicating the state of  $\pm 20v$  supply. If the  $\pm 20v$  supply is at  $\pm 17.6v$  ( $\pm 0.9v$ ), Q01 will turn off and Q02 will turn on. This will turn Q07 off, giving a logic zero out at pins 11 and 12. The Q03 circuit tests the -20Vsupply. If the -20v is at -17.2v ( $\pm 0.9v$ ), Q03 will turn on, which has the same effect as Q02 turning on. The Q04-Q05 circuit tests the  $\pm 40v$ supply. If the  $\pm 40v$  supply is at  $\pm 35.0v$  ( $\pm 1.8v$ ), Q04 will turn off and Q05 will turn on. This has the same effect as Q02 turning on. If the input at pin 2 goes to logic zero (-0.5v), Q06 will turn on. This also has the same effect as Q02 turning on. If more than one of these four sensing circuits respond at one time, the effect is the same as if only one was on.

The BAB card is the same as the BAA card, except that the Q04, 5, and 6 circuits are left off, and R04, 12, and 16 are changed to allow operation from +20v on pin 15.

The BBA card has QO1 turned on if QO7 on the BAA card is turned off. An external resistor to  $^{+}V_{s}$  is required from pin 10. The BCA card has QO1 turned on if QO1 on the BBA card is turned on. Diodes CR07-12 are to isolate the BCA cards and the write and erase heads from each other when the BCA cards are off.

As used in the 807 Disc File, one BAA and BBA drive six BCA cards. Each BCA card then absorbs up to 0.8 amperes of write or erase current. These cards operate from a special  $+V_s$  on pin 15, to allow operation if either +20v or +40v fails.

6 - BAA, BAB, BBA, BCA, BCB-1

6-BAA, BAB, BBA, BCA, BCB-3

Rev S

BAA

6 - BAA, BAB, BBA, BCA, BCB-4

BAB

## Rev S

BBA

$\left( \right)$

001

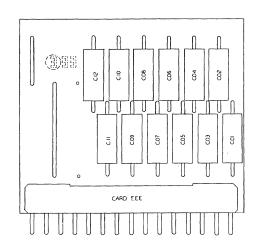

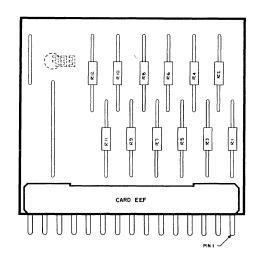

CARD

6 -BAA, BAB, BBA, BCA, BCB-5

Rev S

6-BAA, BAB, BBA, BCA, BCB-6

BCA, BCB

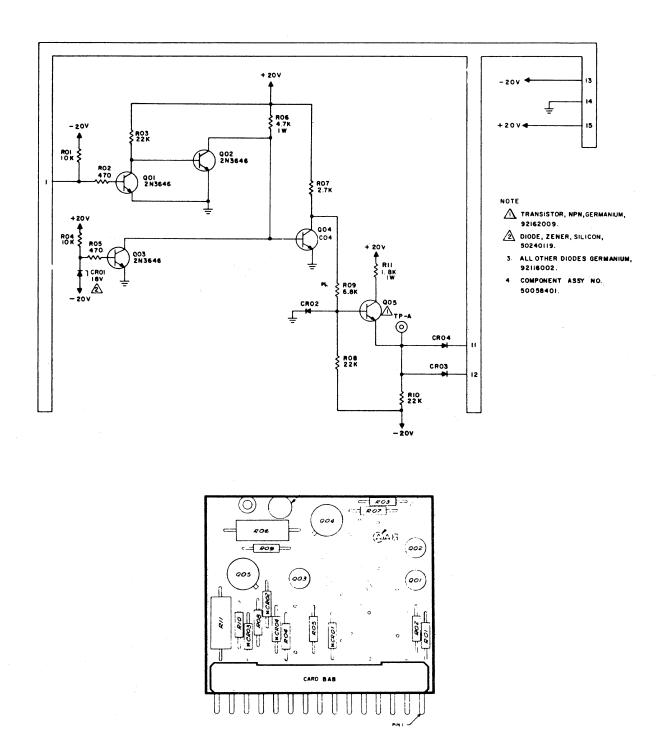

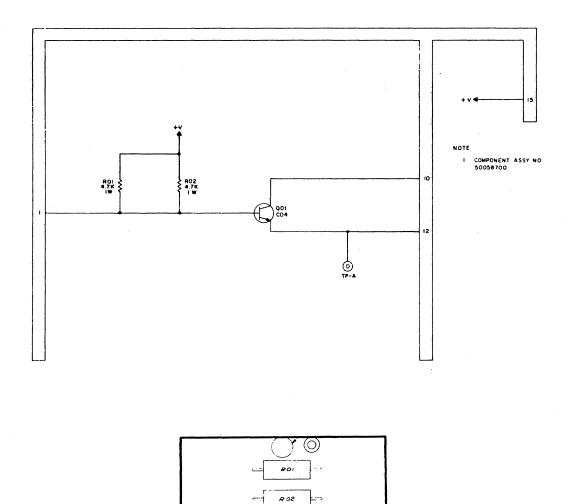

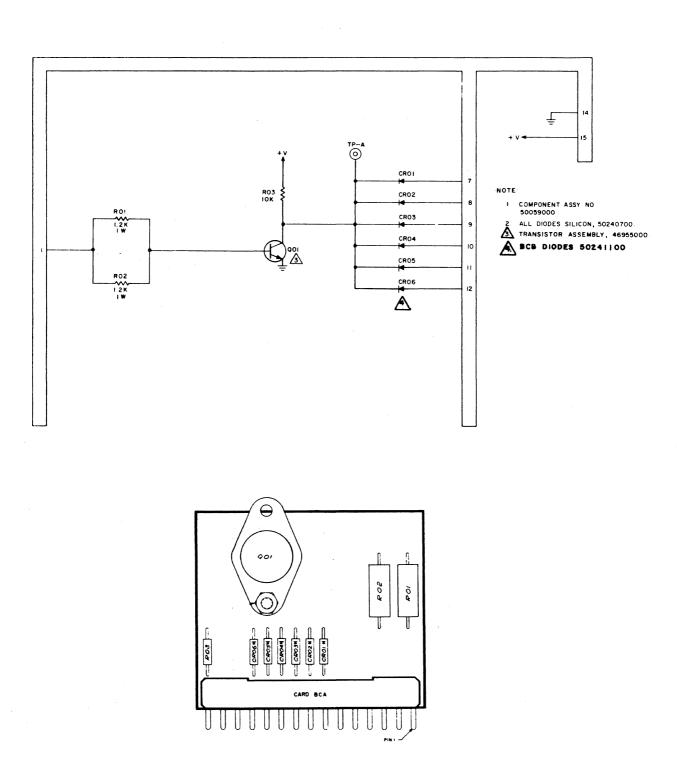

#### HEAD SWITCH

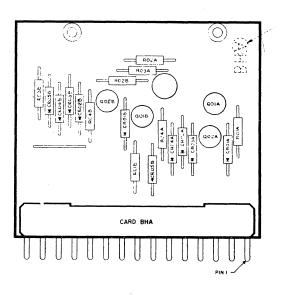

#### BDA