# Burroughs B 7700 SYSTEMS

CHARACTERISTICS MANUAL

## Burroughs B 7700 INFORMATION PROCESSING SYSTEMS

**CHARACTERISTICS MANUAL**

**COPYRIGHT© 1973**

Burroughs Corporation believes the information contained in this manual to be accurate and reliable, and much care has been taken in its preparation. However, the Corporation cannot accept any responsibility, financial or otherwise, for any consequences arising out of the use of this material. The information contained herein is subject to change. Revisions may be issued to advise of such changes and/or additions.

٨.

Correspondence regarding this document should be forwarded using the Remarks Form at the back of the manual, or may be addressed directly to Burroughs Corporation, Technical Information Organization, 200 W. Lancaster Avenue, Wayne, Pennsylvania 19087.

## **TABLE OF CONTENTS**

#### TITLE

| Introduction                                           | v                 |

|--------------------------------------------------------|-------------------|

| Section 1 General Description of B 7700 System         | 1-1               |

| The B 7700 System                                      | 1-1               |

| Distinguishing Features                                | 1-1               |

| Section 2 System Configuration                         | 2-1               |

| Maximum Configuration                                  | $\frac{2-1}{2-3}$ |

| Maximum Configuration                                  | 2-3<br>2-3        |

| Typical Configuration with Full Fail-Soft Capabilities | 2-5<br>2-5        |

| Section 3 Components and Subsystems                    | 2-ə<br>3-1        |

| Control Processor Module                               | 3-1<br>3-1        |

| Central Processor Module                               |                   |

| Input/Output Subsystem                                 | 3-4               |

| Memory Subsystem                                       | 3-9               |

| Maintenance Diagnostic Unit                            | 3-11              |

|                                                        | 3-12              |

| Disk File Subsystem                                    | 3-12              |

| Data Communications Subsystem                          | 3-14              |

| Power Subsystem                                        | 3 - 15            |

| Section 4 Software                                     | 4-1               |

| Master Control Program (MCP)                           | 4-1               |

| System Startup                                         | 4-3               |

| Hardware Interrupts                                    | 4-3               |

| Storage Control                                        | 4-4               |

| Control of Jobs                                        | 4-5               |

| Scheduling and Initiation of Jobs                      | 4-5               |

| Execution of Jobs                                      | 4-6               |

| Software Interrupts and Events                         | 4-7               |

| Termination of Jobs                                    | 4-8               |

| Input/Output Control                                   | 4-8               |

| File Handling                                          | 4-8               |

| Transfer of Data                                       | 4-8               |

| Data Communications                                    | <b>4-9</b>        |

| Communication Between User and MCP                     | 4-9               |

|                                                        | 4-10              |

| Sogmentation (Virtual Memory)                          | 4-10              |

| Segmentation (Virtual Memory)                          | 4-10              |

| Dinding                                                | 4-10              |

| Binding                                                | 4-10<br>4-10      |

| Data Communications Software                           | 4-10<br>4-11      |

| Utility Programs                                       |                   |

| Confidence and Diagnostic Programs                     | 4-11              |

| Applications Programs                                  | 4-11              |

.

## LIST OF ILLUSTRATIONS

| FIGURE     | TITLE                                                                                               | PAGE       |

|------------|-----------------------------------------------------------------------------------------------------|------------|

| 1-1<br>2-1 | B 7700 Exchange                                                                                     | 1-2<br>2-4 |

| 3-1        | Input/Output Subsystem (Showing Theoretical<br>Connectivity of Devices in a Typical Two-IOM System) | 3-5        |

## LIST OF TABLES

#### TABLE

#### TITLE

#### PAGE

| 2-1 | Central Components of the B 7700 System                         | 2-1    |

|-----|-----------------------------------------------------------------|--------|

| 3-1 | Characteristics and Features of the Central Processor Module    | 3-1    |

| 3-2 | Characteristics and Features of the Input/Output Module         | 3-6    |

| 3-3 | Characteristics and Features of the Memory Module               | 3-9    |

| 3-4 | Characteristics and Features of the Maintenance Diagnostic Unit | 3-11   |

| 3-5 | Characteristics and Features of the Head-per-Track              |        |

|     | Disk File Memory Module                                         | 3-13   |

| 3-6 | Characteristics and Features of the Disk Pack Memory Module     | 3-13   |

| 3-7 | Characteristics and Features of the Disk File Optimizer         | 3-14   |

| 3-8 | Characteristics and Features of the                             |        |

|     | Data Communications Processor                                   | 3 - 15 |

| 3-9 | Characteristics and Features of the Power Subsystem             | 3-16   |

## INTRODUCTION

This volume covers the characteristics (both hardware and software) of the Burroughs B 7700 Information Processing System--the most advanced, the largest, and the most powerful member of the Burroughs family of 700 systems.

The four sections of this characteristics manual are as follows.

Section 1, General Description of B 7700 System: an introduction to the idea of the interaction of independently operating computing, input/output, and memory modules through an exchange and to the features that account for the high throughput and availability of the system.

Section 2, System Configuration: a discussion of the range of configurations of the B 7700.

Section 3, Components and Subsystems: summaries of the characteristics and features of the principal components and functional subsystems of the B 7700.

Section 4, Software: an introduction to the standard software of the B 7700, including a brief functional description of the master control program (MCP)--the unique executive program that automatically makes optimum use of all system resources.

The term "software" as used in this manual applies to that category of Burroughs Program Products defined as "Systems Software".

v

Other categories of Burroughs Program Products are:

Application Program Products Program Product Development Aids Program Product Conversion Aids

#### THE B 7700 SYSTEM

The Burroughs B 7700 Information Processing System is a large-scale, truly general-purpose, balanced, flexible, multiprogramming and multiprocessing computing system that is suitable for such diverse applications as time sharing, scientific problem solving, and business data processing. Carrying forward ideas proven successful in the Burroughs B 5700 and B 6700 information processing systems, the B 7700 is, in fact, fully code compatible with the B 6700 and affords Burroughs users the opportunity for growth without reprogramming or recompiling. In other words, object code of users' programs that can be executed successfully on the B 6700 can be executed without modification on the B 7700, and object code that can be executed on the B 7700 can be executed without modification on the B 6700. Nevertheless, the B 7700 is designed to satisfy the increasingly complex data processing needs of the years to come. The system is able to handle complex data structures and sophisticated program structures dictated both by higher-level languages now in use and by the requirements of advanced problems. is able to manage efficiently the massive online and archival storage requirements of large data bases, and is able to accommodate vast networks of data communications devices.

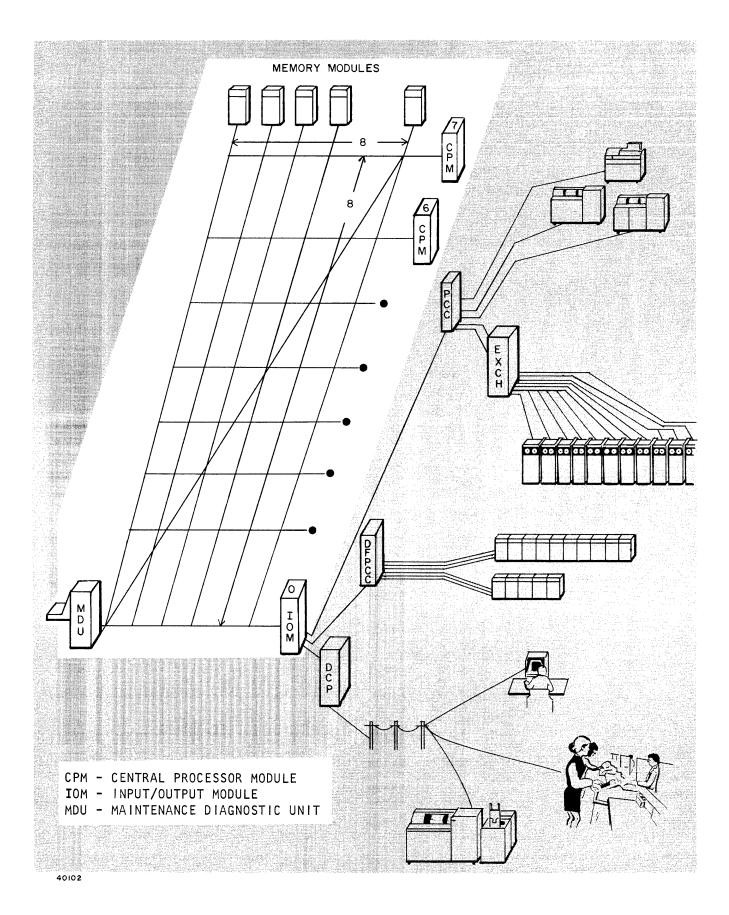

A very fast, modular parallel processing system with exceptional versatility in configuration, the B 7700 can be tailored to the processing needs of a user by arranging central processor modules, input/output modules, and memory modules on an electronic grid, or exchange (figure 1-1), in a variety of ways depending upon the exact needs of the user. If the high performance and adaptability of the B 7700 could be attributed to a single factor, it would be to the balance attained by means of controlled interaction of independently operating computing, input/output, and memory modules through the exchange. Thus, the throughput of the system as a whole is maximized, and the performance of no single element of the system is maximized to the neglect or detriment of others.

The key to the efficient and balanced use of the system is the Burroughs master control program (MCP)--a unique executive software oper-

### SECTION 1 GENERAL DESCRIPTION OF B 7700 SYSTEM

ating system that automatically makes optimum use of all system resources. It is this operating system that makes multiprogramming and multiprocessing both functional and practical by dynamically controlling system resources and by scheduling jobs in the multiprogramming mix. In use, the master control program allocates system resources to meet the needs of the programs introduced into the computer. It continually and automatically reassigns resources, starts jobs, and monitors their performance.

Further implications of the modularity and flexibility of the system are its expandability (a capacity to add hardware modules without reprogramming) and its increased reliability (and thus increased availability to the user). This reliability is achieved by the use of fail-soft techniques that (in addition to providing for error detection and error correction, redundancy of data paths, and independence and redundancy of power supplies) exclude faulty modules from the system and permit processing to continue (again, without reprogramming) even with a temporarily reduced configuration.

Even though it is very large and immensely complicated and thus able to perform complex computations, the B 7700 is, nevertheless, comprehensible to the persons who use it: programming is done only in higher-level, problem-oriented languages; the control language used in entering jobs into the system is a simple, freeform, English-like language; and the messages that pass between the system and the operator are brief, clear, and easy to learn.

#### DISTINGUISHING FEATURES

Although the balanced use of the principal components of the system as a whole under the control and coordination of the master control program is the key to the high throughput of the B 7700, the high performance of the system is in large part achieved by improving the speed of execution of instructions, by reducing or masking the overhead associated with references to memory, by freeing the central processor from concern with input/output operations, and by employing fail-soft measures that minimize system degradation.

Figure 1-1. B 7700 Exchange

Because system main-frame hardware has been designed and built strictly according to stringent circuit and wiring rules and proven design and packaging techniques and because its processing elements incorporate monolithic integrated circuits, the B 7700 system performs consistently at high operating frequencies: the central processor module at a clock rate of 16 megahertz and the remainder of the system at 8 megahertz.

By combining the following features with the high internal operating frequencies, the performance of the system is further enhanced.

- 1. The parallel and independent operation of the three main sections (program, execution, and storage) of the central processor module. This parallelism (coupled with the high clock rate) makes possible the speeding up of arithmetic computations and data manipulations and the overlapping of these computations and manipulations with memory references.

- 2. A special high-speed integrated circuit memory (program, stack, and associative data buffers). This high-speed local memory permits multiword transfers between the central processor and main memory and makes possible the anticipation of the need for program and data words. Hence, the time spent waiting for the completion of transfers to and from memory is reduced and at times virtually eliminated.

- 3. The four-way interleaving of addresses in main memory and the capability for phased multiword transfers of information to and from memory in groups of up to four words. Consequently, memory access times for each user of memory are reduced, and memory is thus made more accessible to all users.

- 4. The asynchronous performance of input/ output operations by the input/output module independent of the central processor, which is therefore freed to do other useful work.

The three goals of the fail-soft features of the B 7700 are to keep the system running 100 percent of the time, to minimize system degradation, and to provide the user with tools for performing his own data recovery. These goals are achieved by the artful combination of hardware and software throughout the system.

The first goal--to keep running--is achieved as follows.

- 1. By the high reliability of system hardware.

- 2. By the incorporation of error detection circuits throughout the system.

- 3. By single-bit error correction of errors in memory.

- 4. By recording errors for software analysis.

- 5. By modular design, by use of separate power supplies and redundant regulators for each module, and by use of redundant buses.

- 6. By the ability of the master control program to reconfigure the modules of the system to temporarily exclude a faulty one.

In short, the detection and reporting of errors is done by hardware, analysis of errors is done by software, and the reconfiguration of the system is done dynamically by software. Because of the modularity of power supplies and the use of redundant regulated supplies for critical voltages, the impact of a malfunctioning dc supply is minimized and does not result in a catastrophic failure.

The second goal--to minimize system degradation--is achieved by providing diagnostic programs and equipment for rapidly identifying and repairing faults and for reestablishing confidence in a repaired module before it is returned to the user's system. The diagnostic programs of the B 7700 system identify a faulty module. By the use of the maintenance diagnostic unit, a fault in any main-frame module or in a disk file optimizer is narrowed to a single clock period and to a flip-flop and its associated logical circuits. Finally, by the use of the card tester on the maintenance diagnostic unit, the faulty integrated circuit chip is identified. The third goal--to provide the user with tools for performing his own data recovery--is achieved by the use of such features as installation allocated disk, protected disk files, duplicated disk files, and fault statements in the higher-level programming languages used on the system.

Installation allocated disk allows the user to specify the physical allocation of his critical disk files in order to facilitate the maintenance

۱

and reconstruction of these files. Protected disk files allow a user to gain access to the last portion of valid data written in a file before an unexpected system halt. The use of duplicated disk files is to avoid the problem of fatal disk file errors. The master control program maintains more than one copy of each disk file row, and, if access cannot be gained to a record, an attempt is made to gain access to a copy of the record. By the use of fault statements, the user can stipulate the actions to be taken by his programs in case certain errors occur.

## SECTION 2 SYSTEM CONFIGURATION

Physically, the components of the B 7700 system fall into three categories, as follows:

- 1. Central components of the B 7700 system--the central processor module, the input/output module, the memory module, the maintenance diagnostic unit, and the operator's console (see table 2-1).

- 2. Standard Burroughs cabinets that contain peripheral controls and exchanges, the disk file optimizer, the data communications processor, and ac power supplies.

- 3. Standard peripheral devices that are joined to the central system by means of

standard Burroughs peripheral controls, adapters, and exchanges and standard remote devices that are joined to the central system by means of line adapters and the data communications processor.

The arrangement of these components into a system and the size of the system depend on the application and workload of the user. In the following paragraphs, the range of configurations of the B 7700 --the maximum configuration, the minimum configuration, and the typical configuration with full fail-soft capabilities--is described.

| Name                                | Description                                                                                                                                                                                                                                                            |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Basic system                        | One 16-megahertz, parallel processing central processor module                                                                                                                                                                                                         |

|                                     | One asynchronously-operating input/<br>output module containing four<br>multiword channels for disk file<br>controls, 20 word channels for<br>peripheral controls, four word<br>channels for data communications<br>processors, and one disk file optimizer<br>adapter |

|                                     | Processor/memory exchange                                                                                                                                                                                                                                              |

|                                     | Operator's console and control                                                                                                                                                                                                                                         |

|                                     | One maintenance diagnostic unit                                                                                                                                                                                                                                        |

| Additional central processor module | See above.                                                                                                                                                                                                                                                             |

| Additional input/output module      | See above.                                                                                                                                                                                                                                                             |

| Multiword channels                  | Four multiword channels for disk file<br>controls and one disk file optimizer<br>adapter                                                                                                                                                                               |

|                                     |                                                                                                                                                                                                                                                                        |

|                                     | Basic system<br>Additional central processor module<br>Additional input/output module                                                                                                                                                                                  |

Table 2-1. Central Components of the B 7700 System

| Style Number | Name                                   | Description                                                                     |

|--------------|----------------------------------------|---------------------------------------------------------------------------------|

| B 7001-2     | Memory module                          | 786,432 eight-bit bytes (131,072 words)<br>of core memory storage               |

|              |                                        | 1.5-microsecond cycle time                                                      |

|              |                                        | Two-way interleaving that permits<br>two-word transfers to and from<br>memory   |

| B 7001-4     | Memory module                          | 1,572,864 eight-bit bytes (262,144<br>words) of core memory storage             |

|              |                                        | 1.5-microsecond cycle time                                                      |

|              |                                        | Four-way interleaving that permits<br>four-word transfers to and from<br>memory |

| B 7341       | Additional operator's display control  | Controls a maximum of eight operator's display terminals                        |

| B 9342-1     | Additional operator's display terminal |                                                                                 |

| B 9951-7     | Console display stand                  | Low, without work table                                                         |

| B 9951-8     | Console display stand                  | High, without work table                                                        |

| B 9951-9     | Console display stand work table       | Right or left                                                                   |

| Table 2-1. | Central Com | ponents of the l | 3 7700 S | vstem (Cont) |

|------------|-------------|------------------|----------|--------------|

| 10010 2 1. | coma com    |                  |          | ,            |

#### MAXIMUM CONFIGURATION

Figure 2-1 illustrates the theoretical maximum configuration of the B 7700 system. As many as eight memory modules may be arranged on the exchange with a combined total of up to eight requestors of memory--central processor modules and input/output modules. Any single requestor of memory may address and gain access to the entire contents of high-speed main memory (1,048,576 words, or 6,291,456 eight-bit bytes). On the maintenance bus (which services the memory control modules, central processor modules, input/output modules, and disk file optimizers) one or two maintenance diagnostic units may be placed.

At rates of up to 6.75 million bytes per second, a single input/output module is capable of transferring data simultaneously between main memory and 28 peripheral controls (including eight high-speed controls) and between main memory and as many as four data communications processors. It is also capable of handling as many as four disk file optimizers (devices) that are used in improving the rate of transfer of data between main memory and disk files). At present, the maximum number of highspeed, medium-speed, and low-speed peripheral devices that may be attached through controls and exchanges to a single input/output module or that may be included in the input/output subsystem of the B 7700 is 255. (Each card reader, pseudoreader, card punch, line printer, paper tape reader, paper tape punch, operator's display terminal, and free-standing magnetic tape unit; each station on a magnetic tape cluster: and each electronics unit in a disk file subsystem is considered a device.) By suitable cross-connection through exchanges, it is possible to establish pathways between disk files, disk packs, or magnetic tape units and more than one input/output module; hence, these peripheral devices can be shared between the input/output modules in the system.

Among the peripheral devices available are disk file and disk pack memory modules that constitute a virtual memory that in effect greatly expands the storage capacity of the main memory of the system; these modules, which are interfaced with one input/output module through controls are as follows:

- 1. Head-per-track disk file modules that are combined under the control of disk file optimizers to form optimized-access memory banks capable of storing from 450 million to 8 billion eight-bit bytes of information per input/output module and whose access time is as low as 2 to 6 milliseconds or 4 to 10 milliseconds.

- 2. Head-per-track disk file modules that are combined (without the control of the optimizer) into random-access memory banks of from 15 million to 16 billion eight-bit bytes per input/output module and whose average access time is 23 or 40 milliseconds (dependent on the type of storage unit).

- 3. Disk pack memory modules that are combined into random-access memory banks with a capacity of from 121 million to many billions of eight-bit bytes of storage per input/output module and whose average access time is 30 milliseconds.

Besides the 255 peripheral devices that may be included in the input/output subsystem, there is a vast network of remote terminals, remote controllers, and remote computers that can be accommodated by the up to 1024 remote lines serviced by the four programmable data communications processors that can be controlled by a single input/output module. Normally, each line handles a number of remote devices, and, naturally, systems that have more than one input/output module can have more than one data communications network. The maximum number of data communications processors that may be included in a B 7700 system is 28.

#### MINIMUM CONFIGURATION

The smallest possible B 7700 system is composed of the central components listed below.

| Central Components                | Quantity |

|-----------------------------------|----------|

| Central processor<br>module (CPM) | 1        |

| Input/output module (IOM)         | 1        |

Figure 2-1. Maximum Configuration of the B 7700 System

| Central Components                                                  | Quantity          | Central Components                                | Quantity       |

|---------------------------------------------------------------------|-------------------|---------------------------------------------------|----------------|

| Memory module                                                       | 1                 | Central processor<br>module (CPM)                 | 2              |

| Memory control<br>module (MCM)                                      | 1 ,               | Input/output module                               | 2              |

| Memory storage<br>cabinet (MSC)                                     | 1                 | (IÕM)                                             |                |

| Memory storage                                                      | 2                 | Memory module                                     | 4              |

| unit (MSU)                                                          |                   | Memory control<br>module (MCM)                    | 4              |

| Maintenance diagnostic<br>unit (MDU) and its<br>associated magnetic | 1                 | Memory storage<br>cabinet (MSC)                   | 8 (2 per MCM)  |

| tape unit                                                           |                   | Memory storage 1<br>unit (MSU)                    | .6 (2 per MSC) |

| Operator's console                                                  | 1                 | Maintenance diagnostic<br>unit and its associated | 1              |

| Besides these central compone                                       | ents, the minimum | magnetic tape unit                                |                |

configuration must contain a disk file memory subsystem at least large enough to hold the master control program, a card reader, a line printer, a magnetic tape unit, peripheral controls, and ac power cabinets. In practice, other peripheral devices and their controls are used with this minimum configuration.

Naturally, this minimum system lacks the redundancy and power of larger configurations. First (lacking redundancy of main-frame modules) this configuration does not take full advantage of the fail-soft features possible with the B 7700 and second (because each memory control module controls but two storage units) two-word transfers, not four-word transfers, to and from memory are possible.

#### TYPICAL CONFIGURATION WITH FULL FAIL-SOFT CAPABILITIES

The power, speed, flexibility, and reliability of which the B 7700 is capable are fully realized in a system that includes the following central components. Besides these central components, this typical fail-soft configuration must contain two disk file memory subsystems (one for each input/ output module) or a single disk file subsystem that is shared by means of exchanges by the two input/output modules, peripheral controls, and ac power cabinets. Naturally, a complement of peripheral devices and their controls and exchanges, data communications processors, and remote devices suited to the application and workload of the system is also needed.

2 (1 per IOM)

Operator's console

A system of the proportions described above incorporates fully the fail-soft features of the B 7700 and takes complete advantage of its capability of handling four-word transfers of data to and from main memory.

## SECTION 3 COMPONENTS AND SUBSYSTEMS

The following paragraphs and tables contain very brief and general descriptions of the principal components and functional subsystems that—under the control of the master control program and arranged in configurations suited to particular data processing needs—make up a B 7700 system. These components and subsystems are as follows.

- 1. Central processor module.

- 2. Input/output subsystem.

- 3. Memory subsystem.

- 4. Maintenance diagnostic unit.

- 5. Operator's console.

- 6. Disk file subsystem.

- 7. Data communications subsystem.

- 8. Power subsystem.

#### CENTRAL PROCESSOR MODULE

Table 3-1 highlights the characteristics and features of the central processor module, the computational element of the B 7700 system.

| Characteristics and Features | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock rate                   | 16 megahertz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Number per system            | At least 1, at most 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Parallel processing          | Three major, independent, asynchronously-operating<br>sections—the program section, the execution section,<br>and the storage section—make up the central<br>processor module. Communication between these<br>sections is carried out by means of queues of<br>operations. Because of the parallelism of the central<br>processor module, arithmetic computations and data<br>manipulations, the calculation of addresses, and the<br>transferring of data to and from memory may go on<br>at the same time.                                                                                                                          |

| Local buffering              | The use in the central processor module of special<br>high-speed integrated circuit memories—the program<br>buffer, the stack buffer, and the associative data<br>buffer—reduces and at times virtually eliminates the<br>time spent waiting for the completion of transfers of<br>data to and from main memory. Because these<br>buffers are filled autonomously (two or four words<br>at a time, depending on the configuration of main<br>memory) on the principle of anticipation rather than<br>that of need followed by demand, the replenishment<br>of their contents takes full advantage of normal<br>main memory idle time. |

| Program buffer               | The program buffer, local storage for up to 32<br>program words, permits tight loop capture of<br>program loops of 30 words or less. A loop once in<br>the buffer may be executed repeatedly without<br>further fetching of program words from main<br>memory.                                                                                                                                                                                                                                                                                                                                                                        |

| Table 3-1. | <b>Characteristics</b> | And | Features | Of 1 | The | Central | Processor | Module |

|------------|------------------------|-----|----------|------|-----|---------|-----------|--------|

|            |                        |     |          |      |     |         |           |        |

| Characteristics and Features                                                                                                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Stack buffer                                                                                                                             | The 32-word stack buffer provides local storage for<br>(and hence quick access to) descriptors, variables,<br>and control words at the top of the stack of a job<br>that is being executed.                                                                                                                                                                                                                                                                                                                                                                        |

| Associative data buffer                                                                                                                  | The associative data buffer, which is composed of 16<br>words, provides local high-speed storage for the<br>operands and descriptors of a job that are most<br>often used but that are not close enough to the top<br>of the stack to be in the stack buffer.                                                                                                                                                                                                                                                                                                      |

| Hardware stack mechanism                                                                                                                 | The stack structure of the B 7700 system is not<br>merely a software fabrication imposed upon<br>uncongenial hardware. Rather the hardware mechanism<br>for structuring and manipulating the stack is intrinsic<br>to the central processor module. This hardware stack<br>mechanism makes possible the efficient handling of<br>temporary storage and permits the control of subordinate<br>routines, communication between processes, and the<br>servicing of interrupts to be treated in a uniform<br>and efficient way.                                        |

| Memory protection                                                                                                                        | Memory protection (preventing a program's gaining<br>access to or altering data not assigned to it) is made<br>possible by a combination of hardware and software<br>mechanisms. The hardware mechanisms include<br>automatic detection of a program's attempt to index<br>beyond an assigned data area and the use of control<br>bits (set by software) that prevent a user program's<br>changing program words, data descriptors, segment<br>descriptors, memory links, indirect reference words,<br>control words, and tables of the master control<br>program. |

| Instruction set of four families of<br>operators<br>Arithmetic operators<br>Word operators<br>Control word operators<br>String operators | The operators of the central processor module act<br>upon vectors, entire words, characters, groups of<br>bits, and single bits. The same set of operators is<br>used in performing both single-precision and double-<br>precision arithmetic.                                                                                                                                                                                                                                                                                                                     |

Table 3-1. Characteristics And Features Of The Central Processor Module (Cont)

| Characteristics and Features                                                                                                                                                                                                                                                                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Representation of data<br>Single-precision and double-<br>precision operands<br>Strings of eight-bit EBCDIC, eight-<br>bit USASCII, six-bit BCL (Burroughs<br>common language), and four-bit<br>packed numeric characters<br>Descriptors, control words, indirect<br>reference words and program words | Each B 7700 word contains 48 bits of information:<br>three control, or tag, bits; and a variable number of<br>parity bits and other error-checking bits. The control<br>bits serve to distinguish the types of words.                                                                                                                                                                                                             |

| Largest positive integers that can be expressed                                                                                                                                                                                                                                                        | The set of integers is symmetrical with respect to 0.<br>Thus, the negative integer corresponding to any valid<br>positive integer may also be expressed.                                                                                                                                                                                                                                                                         |

| Single precision                                                                                                                                                                                                                                                                                       | 549,755,813,887                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Double precision                                                                                                                                                                                                                                                                                       | 302,231,454,903,657,293, 676, 543                                                                                                                                                                                                                                                                                                                                                                                                 |

| Range of positive normalized real numbers that can be expressed                                                                                                                                                                                                                                        | The set of real numbers is symmetrical with respect<br>to 0. Thus, the negative real number corresponding<br>to any valid positive real number may also be<br>expressed.                                                                                                                                                                                                                                                          |

| Single precision                                                                                                                                                                                                                                                                                       | (8 <sup>13</sup> -1) x 8 <sup>63</sup> to 8 <sup>-51</sup> and 0                                                                                                                                                                                                                                                                                                                                                                  |

| Double precision                                                                                                                                                                                                                                                                                       | (1-8 <sup>-26</sup> ) x 8 <sup>32780</sup> to 8 <sup>-32755</sup> and 0                                                                                                                                                                                                                                                                                                                                                           |

| Handling of hardware interrupts                                                                                                                                                                                                                                                                        | Interrupt conditions detected by the central processor<br>module, the input/output module, or the memory<br>control module are processed by the central<br>processor module, which prepares the stack for entry<br>into the interrupt-handling procedure of the master<br>control program, places the needed parameters in the<br>stack, and causes entry into the interrupt-handling<br>procedure of the master control program. |

|                                                                                                                                                                                                                                                                                                        | Thus, by automatically discontinuing (either<br>temporarily or permanently, depending on the<br>interrupt condition) the process being executed at<br>the time the interrupt condition occurs, the B 7700<br>system is able to deal with nearly every condition<br>(both normal and abnormal) that may arise in the<br>multiprogramming, multiprocessing environment.                                                             |

#### Table 3-1. Characteristics and Features of the Central Processor Module (Cont)

| Characteristics and Features      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| States of operation               | The central processor module operates in either of<br>two states: control state, used by the master control<br>program, or normal state, used by both user<br>programs and the master control program. The<br>interrupt-handling procedure of the master control<br>program is always executed in the control state. The<br>differences between the two states are that in<br>control state the processing of interrupt conditions<br>arising outside the central processor module (external<br>interrupts) is inhibited whereas in normal state it is<br>not so inhibited and that in control state the central<br>processor may execute privileged instructions<br>(including Set Interval Timer, Idle Until Interrupt,<br>Set Memory Inhibits, and Set Memory Limits) that<br>it may not execute in normal state. |

| Modes of operation                | In addition to the two states, the central processor<br>module can operate at any one of four interrupt<br>management levels: normal mode, control mode 1,<br>control mode 2, and control mode 3. The central<br>processor operates in normal mode until an interrupt<br>condition is detected. The three control modes allow<br>for repeated attempts to enter the hardware<br>interrupt routine with different environments. If an<br>interrupt is detected while the central processor is in<br>control mode 3, the processor is halted.                                                                                                                                                                                                                                                                          |

| Detection and reporting of errors | The use of residue checking in all arithmetic<br>operations and address calculations and of parity<br>checking in data transfers greatly facilitates the<br>detection of errors within the central processor<br>module. If a failure occurs within the central<br>processor module, a processor internal interrupt is<br>produced and the cause of the failure is denoted by<br>the contents of the fail register of the processor.                                                                                                                                                                                                                                                                                                                                                                                  |

Table 3-1. Characteristics and Features of the Central Processor Module (Cont)

#### INPUT/OUTPUT SUBSYSTEM

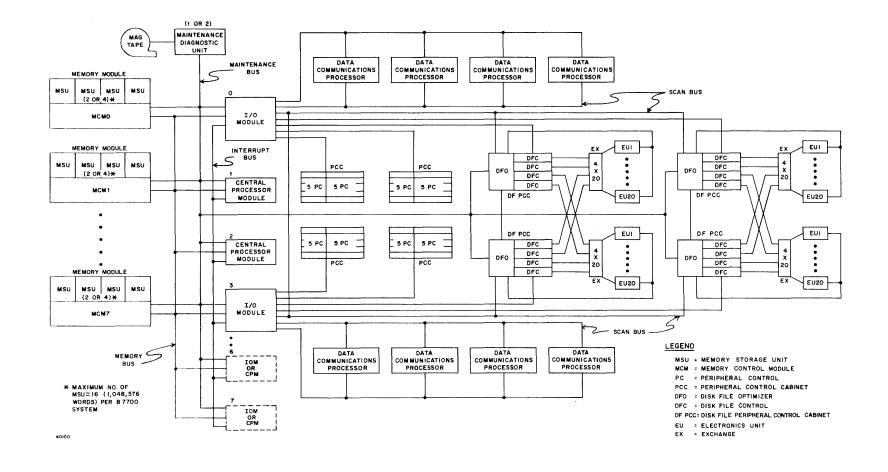

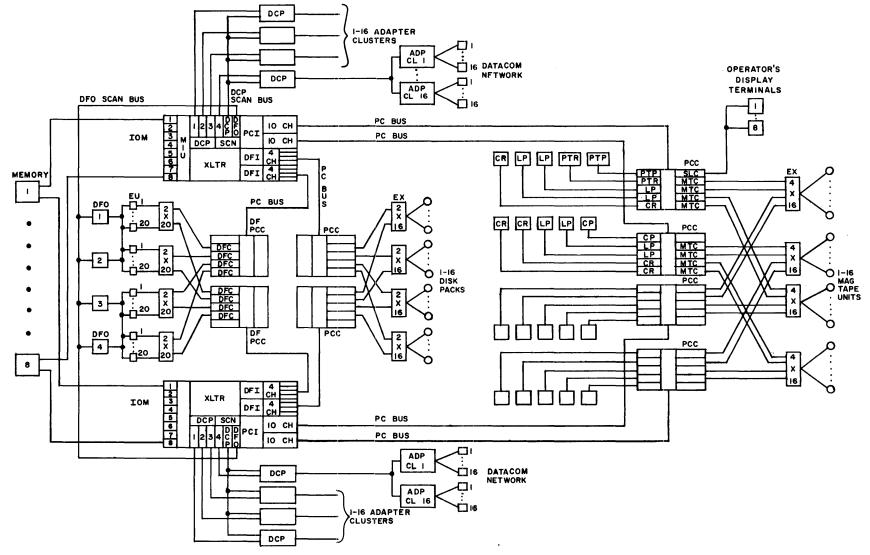

The input/output subsystem (see Figure 3-1) of the B 7700 may include from one to seven input/output modules (see table 3-2); low-speed and medium-speed peripheral devices and their controls and exchanges; the high-speed disk file subsystem; and the data communications subsystem, which is made up of as many as 28 data communications processors with associated adapters and remote devices.

Figure 3-1. Input/Output Subsystem (Showing Theoretical Connectivity Of Devices In A Typical Two-IOM System)

ω-5

40103

| Characteristics and Features                                                                                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock rate                                                                                                                              | 8 megahertz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Number per system                                                                                                                       | At least 1, at most 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Number of peripheral<br>devices(including disk file optimizers<br>but excluding data communications<br>processors and remote terminals) | A maximum of 255 per input/output module: a maximum of 255 per input/output subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Number of data communications processors (see table 3-8)                                                                                | Maximum of 4 per input/output module; a maximum of 28 per input/output subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Number of disk file optimizers (see table 3-7)                                                                                          | A maximum of 4 per input/output module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Asynchronous operation independent<br>of the central processor module                                                                   | The central processor module under the control of<br>the master control program queues requests for<br>input and output operations in a job stack in main<br>memory and alerts input/output modules to the need<br>for input and output operations; the input/output<br>modules service these requests asynchronously and<br>independent of the central processor module. In fact,<br>if a number of input and output requests for the<br>same peripheral device are queued in main memory,<br>these requests are linked in such a way that only<br>one interruption of the input/output module is<br>needed for the servicing of all these requests. Hence,<br>once a request for input or output has been queued,<br>the central processor module is free to perform<br>other useful work while the input/output module is<br>performing input and output operations. |

| Connectivity and throughput                                                                                                             | The data transfer rate of the input/output module<br>equals the throughput capability of its memory port.<br>This speed is achieved principally by concentrating<br>the high-speed disk files on double-buffered channels<br>that communicate with main memory in two-word<br>phased transfers and by permitting the simultaneous<br>transfer of data to 20 low-speed and medium-speed<br>peripheral devices and to eight high-speed peripheral<br>devices and to four data communications processors.                                                                                                                                                                                                                                                                                                                                                                  |

| 32 channels                                                                                                                             | 20 channels for low-speed and medium-speed<br>peripheral devices, 8 for high-speed disk file<br>subsystems, and 4 for data communications<br>processors. Also, 4 disk-file-optimizer interfaces are<br>provided.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Maximum data-transfer rate between<br>main memory and peripheral devices<br>and data communications processors                          | 6.75 million bytes per second (with all data service<br>adapters and with a phased, 1.5-microsecond memory<br>subsystem)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Table 3-2. Characteristics And Features Of The Input/Output Module

| Characteristics and Features                                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Peripheral device compatibility                                    | Standard Burroughs peripheral devices and controls,<br>exchanges, disk file optimizers, and data<br>communications processors used with the B 6700 are<br>compatible with the input/output module of the<br>B 7700 system.                                                                                                                                                                                                  |

| Diversity of paths to and from peripheral devices                  | Through exchanges and redundant peripheral<br>controls, alternative ways of gaining access to a<br>peripheral device are provided.                                                                                                                                                                                                                                                                                          |

| Unique data and control paths and<br>asynchronous control sections | There is a unique bus between each input/output<br>module and each memory control module. There are<br>also unique data and control buses from an input/<br>output module to each peripheral control cabinet<br>under its control and a unique memory data bus for<br>each data communications processor. Moreover, there<br>are unique asynchronous control sections for each<br>interface within the input/output module. |

| Code translations                                                  | The input/output module is capable of performing the following code translations:                                                                                                                                                                                                                                                                                                                                           |

|                                                                    | EBCDIC to USASCII                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                    | EBCDIC to BCL external                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                    | USASCII to BCL external                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                    | USASCII to EBCDIC                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                    | BCL internal to BCL external                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                    | BCL external to BCL internal                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                    | BCL external to USASCII                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                    | BCL external to EBCDIC                                                                                                                                                                                                                                                                                                                                                                                                      |

| Interrupts generated by the input/<br>output module                | The input/output module generates interrupts in response to the following conditions:                                                                                                                                                                                                                                                                                                                                       |

| Channel interrupts (related to specific requests and devices)      | The completion of an input/output operation, if the<br>software has requested that an interrupt be<br>generated; otherwise, because the central processor<br>module and the input/output module operate<br>independently and asynchronously, this condition<br>does not trigger an interrupt.                                                                                                                               |

|                                                                    | A change in peripheral status from a single-line control device                                                                                                                                                                                                                                                                                                                                                             |

|                                                                    | The need of a data communications processor for the attention of a central processor module                                                                                                                                                                                                                                                                                                                                 |

#### Table 3-2. Characteristics And Features Of The Input/Output Module (Cont)

| Characteristics and Features                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                       | The detection of an error that is related to an<br>input/output request or to a peripheral device, for<br>example, a parity error on a magnetic tape unit.<br>Errors of this type are reported in a result<br>descriptor, prevent further servicing of the device<br>on which the error occurred, and trigger interrupts<br>only as requested by software.                                                                                                                                                                                             |

| IOM error interrupts (not related<br>to a specific request or device) | The detection of an error that is not related to a specific input/output request or peripheral device. Errors of this type are reported in the fail register of the input/output module, the contents of which are placed in a result descriptor.                                                                                                                                                                                                                                                                                                      |

| Detection and reporting of errors                                     | There are facilities for detecting errors that may<br>occur in any operation in which data are transferred<br>into or out of the system. Among the error<br>detecting features of the input/output module are<br>parity checking of data transfers, residue checking<br>of all arithmetic operations, parity checking of all<br>local memory operations, timeout on memory<br>transfers and scan bus operations, memory bounds<br>checking, detection of illegal commands and<br>conditions, and parity checking of register-to-register<br>transfers. |

| -                                                                     | Particular care is taken in addressing main memory:<br>residue checks are made in the calculation of memory<br>addresses, and bounds checks are made each time<br>an attempt is made to gain access to main memory.                                                                                                                                                                                                                                                                                                                                    |

|                                                                       | When a failure occurs in the input/output<br>subsystem, it is reported in a result descriptor that<br>pinpoints the fault. If the fault is not related to a<br>specific request or device, an IOM error interrupt is<br>produced.                                                                                                                                                                                                                                                                                                                      |

#### Table 3-2. Characteristics And Features Of The Input/Output Module (Cont)

#### MEMORY SUBSYSTEM

As many as eight memory modules (see table 3-3) with a maximum of 1,048,576 words of storage may make up a memory subsystem. A

memory module may consist either of one memory control module and one memory storage cabinet or of one memory control module and two memory storage cabinets. These two types of memory modules may be intermixed in a memory subsystem.