# DATA SET 205C2 **TRANSMITTER-RECEIVER IDENTIFICATION AND OPERATION**

# 1. GENERAL

1.01 This section contains descriptive and operational information for the Data Set 205C2. This section does not include information regarding the business machine used with the data set.

1.02 This section is reissued to expand the coverage. Due to extensive changes, change arrows have been omitted.

**1.03** For the purpose of this practice, reference to a business machine should be interpreted to mean any customer equipment whose input and output signals are in accordance with EIA Standard RS-232-A or Military Standard 188B.

1.04 Data Set 205C2 is a phase modulated transmitting and receiving data terminal designed for use on 4-wire private line facilities. It includes provision for possible 2-wire use. Detailed descriptions and testing for the 2-wire mode are not provided in this section. No telephone set is associated with the data set.

1.05 The data set provides synchronous serial binary data transmission and reception capability at 2400 bps over telephone facilities available under Type 4B (type 3004 channel) tariffs. The first application will be in Switching System No. 307.

1.06 Operation over long haul facilities with significantly poorer end-to-end transmission characteristics than those defined as Type 4B, is possible if two data sets are connected as a regenerative repeater and inserted into the facility at some intermediate point.

1.07 A long term error rate of better than one error in 10<sup>5</sup> bits, when transmitting random data at 2400 bps between two data sets, may be expected on facilities which meet Type 4B requirements.

- 1.08 Transmitter and receiver timing signals accurate to 0.0005 percent are generated This stability of the clock within the data set. signal insures an outage holdover capability in excess of six seconds. Oscillator adjustment at three year intervals is necessary if the six second holdover requirement is to be maintained.

- 1.09 Customer requirements for optional serial binary data transmission capability at a 1200 bps rate is also provided by Data Set 205C2. Transmit and receive clock signals at the selected data rate are provided. The transmission rate is selected by a control signal applied to the customer interface connector. The 2400 or 1200 bps transmission rate may not be selected independently in each direction of transmission.

- 1.10 The data set transmitter may be timed internally or externally.

1.11 Data Set 205C replaces Data Set 205A which is rated Manufacture Discontinued. The 205C can directly replace the 205A providing interface pin 11 is connected either to a negative voltage or to ground.

#### 2. DESCRIPTION

2.01 The data set interface connectors designated CUSTOMER A and CUSTOMER B are for the customer business machine. CUSTOMER A connector carries data and clock interface circuits and a clock speed selection circuit. CUSTOMER B connector carries all control, data, and clock interface circuits, and a clock selection circuit. Terminal assignments, as defined by the EIA Interface Specification RS-232-A, are used where applicable.

#### SECTION 592-017-102

2.02 All interface circuits, except four, meet EIA electrical specifications. Circuits for Send Data (SD), Receive Data (RD), Serial Clock Transmit (SCT), and Serial Clock Receive (SCR) meet the intent of Military Standard 188B. These four circuits are designed to generate (or accept, in the case of Send Data) waveforms with longer rise and fall times than permitted using EIA specifications. This has reduced crosstalk between signalling leads by a significant amount.

2.03 The Dibit Clock Transmit (DTI) interface lead is used during data set testing. This circuit is an EIA driver with very fast rise and fall times. If crosstalk within the cord connecting the data set to the business machine is a problem because of DTI, the DTI lead may be shielded.

#### A. Physical Description

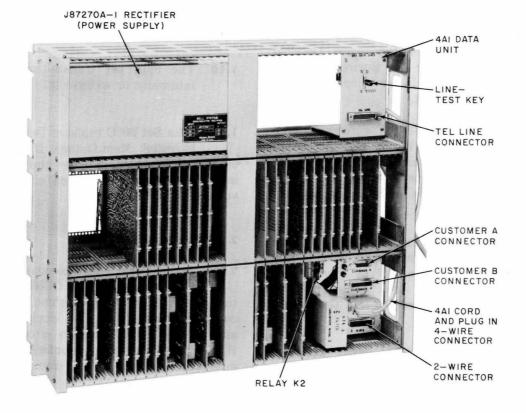

2.04 The Data Set 205C2 is a 23-inch wide rack mounted set that requires 18-inches of vertical rack mounting space. The set is 8 inches deep.Fig. 1 is a front view of the data set with circuit pack retaining covers removed.

2.05 The data set contains 33 circuit packs consisting of 12 types of specialized circuits and an oscillator required to provide the electronic functions of the data set. The circuit pack number and reference location number on the data set are shown in Table A. The equipment location numbers and the last three digits of the printed wiring board numbers are stamped on the circuit pack retaining covers.

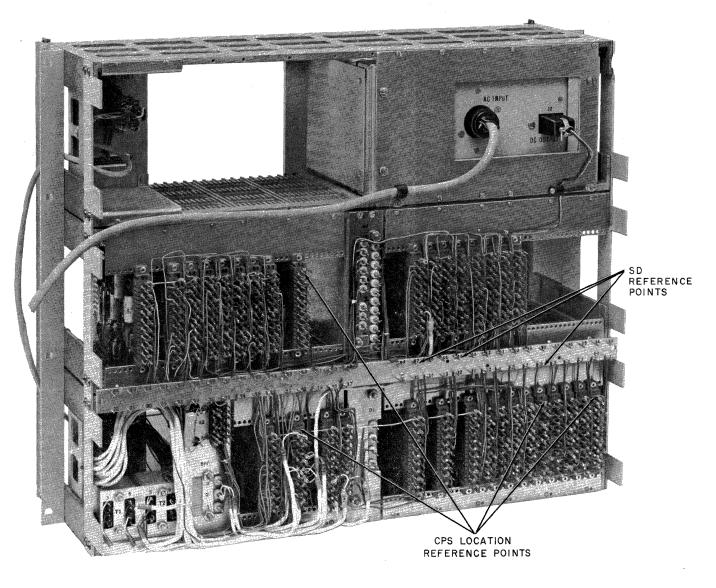

**2.06** Fig. 2 is a rear view of the data set showing card reference location numbers and reference points shown on the schematic drawings.

- 2.07 The Data Set 205C2 weighs 56 pounds.

- **2.08** The Data Set 205C2 contains the following 12 major circuit catergories:

- (1) Line Connector and Transmit-Receive Switch

- (2) Interface Connectors and Remote Test

- (3) Speed Select

- (4) Oscillator and Common Countdown

Fig. 1—Data Set 205C, Front View

#### TABLE A

#### CARD AND REFERENCE INFORMATION

| TYPE OF<br>CIRCUIT BOARD     | IDENTIFICATION<br>NO. | NO. OF<br>CARDS | EQPT. LOCATIONS<br>ON DATA SET                              | CIRCUIT PACK<br>NO. FOR<br>ORDERING |

|------------------------------|-----------------------|-----------------|-------------------------------------------------------------|-------------------------------------|

| NOR Gate                     | 175                   | 11              | 001, 006, 007, 009,<br>038, 039, 043, 050,<br>054, 057, 058 | AR85                                |

| Flip-Flop                    | 176                   | 11              | 002, 003, 005, 037, 040,<br>041, 042, 049, 053, 055,<br>056 | AR86                                |

| Monopulser                   | 177                   | 1               | 008                                                         | AR91                                |

| Automatic Gain<br>Control 1  | 178                   | 1               | 017                                                         | AR88                                |

| Automatic Gain<br>Control 2  | 179                   | 1               | 016                                                         | AR89                                |

| Demodulator                  | 180                   | 2               | 012, 014                                                    | AR96                                |

| Transmit-Receive<br>Switch   | 181                   | 1               | 019                                                         | AR95                                |

| Transmitter Output           | 182                   | 1               | 044                                                         | AR90                                |

| Single Frequency<br>Detector | 183                   | 1               | 010                                                         | AR87                                |

| Remote Test<br>Circuit       | 184                   | 1               | 021                                                         | AR93                                |

| EIA Interface                | 185                   | 1               | 059                                                         | AR92                                |

| MIL. STD 188<br>Interface    | 186                   | 1               | 060                                                         | AR94                                |

| Oscillator                   | 65A                   | 1               | 051                                                         |                                     |

(5) Transmitter Timing

- (6) Data Transmitter

- (7) Analog Receiver

- (8) Digital Data Receiver

- (9) Receiver Timing

- (10) Control Timing

- (11) Single Frequency Detector

- (12) Prepare Receiver Timing

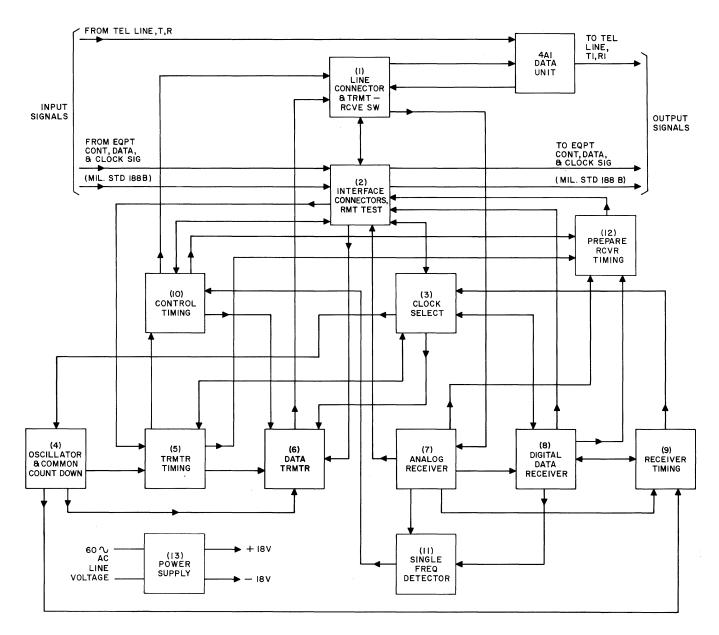

2.09 A block diagram illustrating the interconnections between data set functions is shown in Fig.3. A brief description of each block in numerical sequence is presented in the following paragraphs.

### 2.10 (1) Line Connector and Transmit-Receive

Switch: These circuits provide connectors for the telephone line pairs T, R, and T1, R1, and a continuity circuit for the line and test key (part of the 4A1 Data Unit). Connectors P1 and P2 are used to provide the operational mode of the data set. When the 4A1 connecting cord jack is inserted into P1 (2 WIRE) the data set is conditioned for the 2-wire operational mode. Conversely, inserting the jack into P2 (4 WIRE) conditions the data set for the 4-wire operation ac mode. The Transmit-Receive Switch on circuit pack 181/019 controls the application of the transmitter line signal to the telephone line.

Fig. 2—Data Set 205C2, Rear View

# 2.11 (2) Interface Connectors and Remote Test:

These circuits consist of the CUSTOMER A jack (J62), CUSTOMER B jack (J61), the remote test (RMT) circuit pack, and relay K2. 'The data set is interconnected with a business machine through CUSTOMER A and CUSTOMER B connectors. Remote test circuits, together with remote test relay K2, permit remote testing of Data Set 205C2 from a 904-type Data Test Center. The data set may be placed in the remote test mode by a customer provided signal through the interface connection (when in the 4-wire operational mode). **2.12** (3) Clock Select: The clock select circuit generates the selected interface timing signals for either the 1200- or 2400-bps mode of terminal operation or for regenerative repeater operation.

2.13 (4) Oscillator and Common Countdown: The common countdown circuits generate square-wave timing signals for data set operation from a crystal controlled oscillator operating at 230.4 kHz. These signals are required to operate both the transmitter and receiver timing circuits.

2.14 (5) Transmitter Timing Circuits: The transmitter timing circuits generate the timing waveforms used in the (6) Data Transmitter Circuits. The timing circuits are provided with options for internal or external timing. The basic transmitter timing circuit functions are to:

- (a) Generate square-wave input signals to the phase modulated channel counters.

- (b) Generate square-wave input signals for the interface driver circuits.

- (c) Generate a pulse train used to sample SD.

- (d) Generate accurate square-wave signals for encoding purposes.

- (e) Generate square-wave input signals to operate the pulse modulators.

- (f) Generate six pulse trains to operate the phase logic channel counter transfer gates and perform other 'set' or 'clear' functions.

- (g) Generate a pulse train to operate the control timing circuits.

2.15 (6) Data Transmitter: The data transmitter circuits encode serial binary data as a band-limited signal suitable for transmission over telephone lines. Modulation, or encoding, is accomplished by using applied data bits in pairs (or dibits) to phase-modulate the transmitted line signal. The transmitter circuits also internally generate the repeated 1000 code used for initial synchronization of data sets.

2.16 (7) Analog Receiver: The analog receiver circuits (a) amplify the received band-limited line signal to a fixed level, and (b) convert the received line signal into two parallel signals which constitute demodulated data.

2.17 (8) Digital Data Receiver: The basic functions of the digital data receiver circuits are:

- (a) Convert the demodulated data wave form to standard logic signals

- (b) Generate axis-crossing pulses for the timing recovery circuit operation

- (c) Generate a serial binary data waveform for customer use from the demodulated data

**2.18** (9) Receiver Timing: The receiver timing circuits are used to recover synchronization timing signals for sampling, regeneration and parallel-to-serial conversion of the received data.

2.19 (10) Control Timing: Timing functions and modes of operation are controlled by the Request-to-Send (RS) interface signal. After the data set becomes synchronized with another Data Set 205C2, a Clear-to-Send (CS) signal is generated by the control timing circuits and indicates to the connected business machine that the Send-Data (SD) will be processed correctly. CS signal transitions are coincident with positive transitions of the Serial Clock Transmit (SCT) signals. A serial binary digit initiated in coincidence with the rise of the CS signal will be processed by the data set.

2.20 (11) Single Frequency Detector: The single frequency detector circuits detect the repeated 1000 code in the Receive Data sequence and provide control timing circuits with the signal required to enable and initiate Clear-to-Send timing. 2.21 (12) Prepare Receiver: The prepare receiver circuit is provided, in the Data Set 205C2, to allow operation with encryption equipment on circuits that have propagation delays in excess of 50 milliseconds. This circuit gives an ON indication when it detects the presence of steady positive voltage level on the received data lead for greater than 86 milliseconds.

**2.22** (13) Power Supply: The power supply is mounted in the top rack of the data set. The power supply contains a J87270A-1 rectifier which has no controls, switches, or adjustments. Operation is instantaneous when connected to a commercial 60 ( $\pm 0.8$ ) Hz power source. The power supply is provided with the necessary connecting cords required for ac power input and dc power outputs to the data set. Two rectifier outputs provide the  $\pm 18.0 (\pm 1.0)$  vdc (on pin 3) and  $\pm 18.0$  $(\pm 1.0)$  vdc (on pin 5) required to operate the data set. Other connections between the power supply and the data set provide a common (rectifier) ground (on pin 4) and a frame ground or ac power third-wire ground (on pin 6).

2.23 The Data Set 205C2 provides the following two grounds: (1) Frame Ground (FG) is common to both chassis ground and the ac power third-wire ground, and (b) Signal Ground (SG) is used as a reference for all data, timing, and control signals. Signal Ground is connected to Frame Ground when terminal E1 is strapped to terminal E2 in the data set, or when the customer connects Signal Ground to Frame Ground through a CUSTOMER connector.

The data set contains a 4A1 Data Unit to 2.24 interface between the data set circuits and the telephone line. The telephone line pairs T. R. and T1. R1 are wired to the TEL LINE connector on the 4A1 Data Unit. A two position line and test key (in LINE position) provides continuity between the TEL LINE connector and the 4A1 connecting cord jack. The jack mates with either 2-WIRE plug (P1), or the 4-WIRE plug (P2). The remaining line and test key position is TEST, which terminates the telephone line pairs into 600-ohms and provides a loop-back feature between transmitter and receiver sections of the data set when the 4A1 connecting cord jack is mated with 4-WIRE plug (P2).

2.25 An interface signal which the business machine may not have provision for terminating is the External Clock signal input (SCTE). This lead may be optionally strapped to ground by using the appropriate terminals on the Transmit-Receive Switch circuit pack (181/019) board.

2.26 Data Set 205C2 interface connectors designated CUSTOMER A and CUSTOMER B connect the customer business machine to data set circuitry. The 15-pin CUSTOMER A interface connector carries data, clock, and clock speed selection circuits for special ancillary equipment. The 25-pin CUSTOMER B interface connector carries all control, data, clock, and clock speed selection circuits.

# 3. OPERATION

**3.01** Data Set 205C2 can transmit and receive simultaneously over a 4-wire facility. Calls between stations are made on a full duplex basis.

**3.02** Operating voltages are provided by the rectifier contained in the data set power supply.

3.03 Transmitter timing is derived from either (1) the data set crystal oscillator (internal timing); (2) externally from a clock signal supplied by the customer (using interface SCTE lead); or (3) from a second Data Set 205C2 (connected as a regenerative repeater).

3.04 When the data set is internally timed, accurate timing signals in the receiver allow it to maintain synchronization with an associated transmitter for a minimum of six seconds in the absence of data transitions or in the event of a circuit interruption. If the data set is externally timed, maximum holdover time will depend on the accuracy of the external clock signal, but cannot exceed 6 seconds.

3.05 The data set uses a "zero crossing" clock recovery system that requires the number of "crossings" per second of the Send Data (SD) to be greater than some minimum value to maintain receiver synchronization in the presence of clock variations and noise, and to restore the receiver clock after a dropout. The term "crossing" and the crossing rate requirements are defined in Data Set 205C2; Transmitter Receiver; Supplementary Information (Section 592-017-152).

3.06 Incoming serial data bits are applied to the

data set transmitter through the Send-Data circuit. The data transitions are synchronous with the positive-going transitions of the transmitter clock (SCT). Send-Data signals are used to control the four-phase modulation of the transmitted line signal.

3.07 Selection between "continuous carrier" or "carrier controlled by Request-to-Send" operation is provided through terminals 1 and 2 on the Transmit-Receive Switch printed wiring board (181/019). Placing a strap between terminals 1 and 2 will provide continuous carrier. With no Strap between terminals 1 and 2, the data set carrier is controlled by Request-to-Send.

**3.08** During "continuous carrier" operation, the transmitter is always ON and a continuous Clear-to-Send (CS) ON signal is provided to the customer from the data set. For "carrier controlled by Request-to-Send" operation, the transmitter is turned ON and OFF by the Request-to-Send (RS) signal from the customer within limits controlled by the Confirm (CON) circuits.

**3.09** The Confirm signal to the data set from the control equipment determines the time interval between the RS indication from the customer and the CS indication from the data set:

(a) With Confirm OFF, a quad-bit synchronizing code "1000" is transmitted for 640 milliseconds after RS is turned ON. After the synchronizing code time interval, the CS ON indication is provided to the customer.

(b) With Confirm ON, the "1000" code is transmitted after RS is turned ON, but the

640 millisecond interval will not start and time out until a "1000" code has been received and detected from the distant data set. The transmitted "1000" code ends 640 milliseconds later and a CS indication is provided to the customer.

3.10 The purpose of the synchronizing code referred to in 3.09 (a) and (b) is to provide a line signal which produces data crossings in the distant data set receiver. The data crossings provide the means for synchronizing the phase of the receiver clock with the demodulated data. The method of encoding the transmitter does not produce demodulator output zero-axis crossings at the receiver for a steady one, zero, or dotting pattern.

**3.11** The transmitter output level may be set at 0; -3; -6; or -9 dbm by selecting the proper strap conditions on the Transmitter Output circuit pack (182/044) board.

**3.12** The receiver circuits contain an AGC circuit with a 30 db dynamic range and a maximum input sensitivity of  $-39 \ (\pm 1.0)$  dbm. Attenuation pads of 0; 5; 10; and 15 db at the receiver input may be strapped to reduce the sensitivity.

**3.13** The data carrier detector (COO) circuit is also affected by the receiver attenuation pads. The COO circuit provides an ON signal to the business machine when received line power is above a minimum threshold level. the maximum input sensitivity of the COO circuit is  $-39 \ (\pm 1.0)$  dbm. Excessive line noise, speech, and other signals, as well as carrier, can operate this circuit. therefore, the attenuation pads at the receiver input reduce the input sensitivity of the COO circuit by the amount of attenuation inserted.

3.14 When two Data Sets 205C2 are interconnected to make a 4-wire regenerative repeater, each data set transmitter derives external timing from the receiver of the other data set. Receive-Data (RD) signals from each receiver are applied to the Send-Data (SD) input of the other transmitter.

3.15 The data set may be remotely tested over 4-wire facilities with a 904-type Data Test Center. The customer must apply an ON signal to the Remote Test (RMT) interface lead to place the data set in the remote testing mode. To return the data set to normal operation, the customer must change the RMT signal to OFF.

3.16 When using CUSTOMER B interface connector only, the Data Set Ready (DSR) circuit in the data set will provide an ON indication to the customers business machine when power is applied and the data set is not in a test mode. If CUSTOMER A interface connector is used, the same function is provided on the DSRX2 lead.

**3.17** Operational limits are specified as data set ambient temperature range of +50 to  $+120^{\circ}$ F and a relative humidity range of 20 and 95 percent.

**3.18** Supplementary information regarding Data Set 205C2 operational limits and maintenance

procedures is provided in Data Set 205C2, Transmitter-Receiver, Supplementary Information (Section 592-017-152).